First page

|

Course code: EITF20 Credits: 7.5 Activity term: HT2 Teacher (lectures): Liang Liu, liang.liu(at)eit.lth.se Lectures: 10 x 2 hours; First lecture Day 2019-11-05 (13.00-15.00) E:C Laborations: 4 x 4 hours; (1st lab: 2019-11-19, 08-12, 4118 & 4119) |

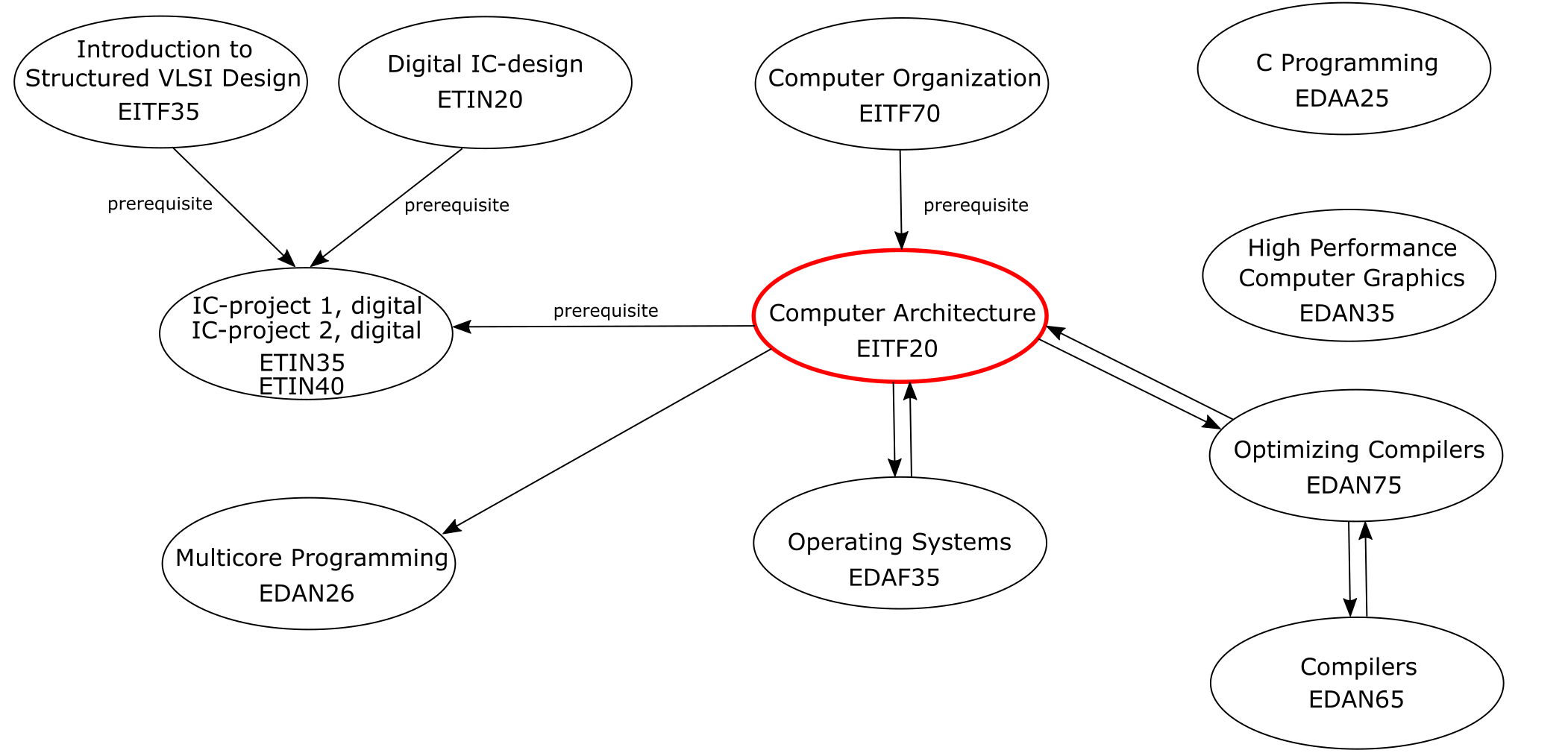

Course environment and dependencies:

Course related questions:

How can Gene Amdahl help you decide which enhancement is the best?

Is a larger cache better than higher clock frequency?

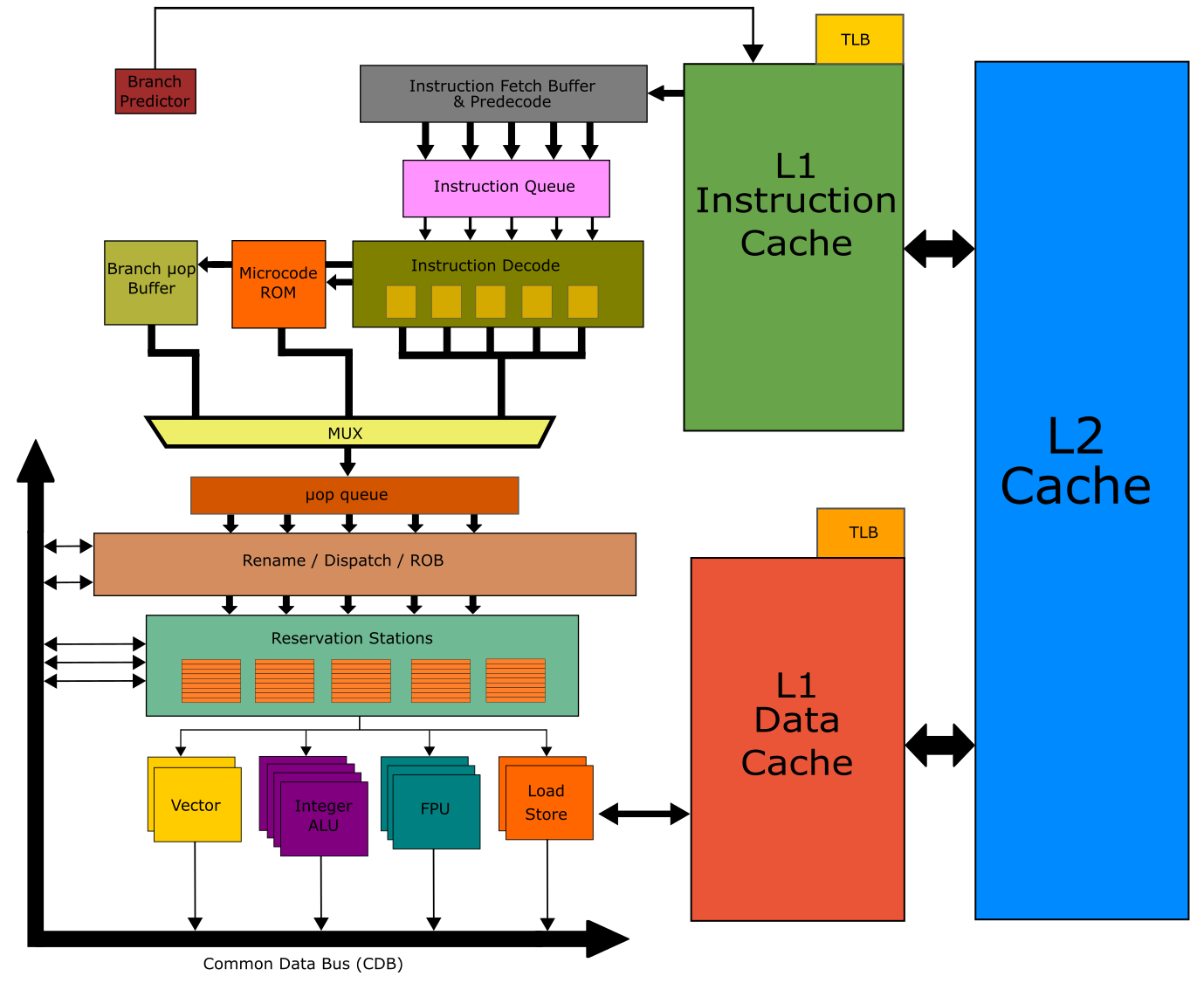

What is a superscalar CPU?

What is the difference between a direct-mapped cache and a set-associative one?

Why is a TLB is essential to virtual memory efficiency?

What is pipelining?

Is out-of-order execution really possible?

How can the hardware rearrange your program and why would it do so?

Why does pipelinng lead to a faster implementation? Is there a limit to this?

Is cache memory heirarchy beneficial?

What does bus snooping mean? What are its applications?

Is the ARM ISA a RISC?

How much memory bandwidth does a modern CPU need?

How to ensure cache coherence in a multi-core system?