Master's Thesis

# Vertical Heterostructure III-V Nanowire MOSFETs

Adam Jönsson

# Vertical Heterostructure III-V Nanowire MOSFETs

Adam Jönsson adamkaffi@gmail.com

Department of Electrical and Information Technology Lund University

Supervisors: Lars-Erik Wernersson & Olli-Pekka Kilpi

August 31, 2016

Printed in Sweden E-huset, Lund, 2016

### **Abstract**

IITF cars had developed as fast as processors they would go at 470,000 mph, **■** get 100,000 miles to the gallon, and cost 3 cents" claims Paul Ottelini, Intel CEO 2005-2013. This serves as a reminder of how fast the field of nanoelectronics is developing due to constant demand for faster and more energy efficient integrated circuits. The still ongoing electronics revolution was accelerated by the innovation of one simple and elegant device, namely the Si-based metal-oxidesemiconductor-field-effect-transisor MOSFET in 1959. The pillar of economic growth has since been based on downscaling the MOSFET and increasing the density of transistor per chip area. Downscaling of the transistor has favourably led to more efficient and faster devices. MOSFETs today are approaching sizes which only include few monolayers of atoms, basically dimensions of a few nanometer. Conventional electronics has thus been pushed into the quantum realm forcing future improvements to be based on innovation rather than simply downscaling. To win the battle against Heisenberg's uncertainty leading to leakage currents and various other effect due to reduced size, new 3d geometries has been introduced. Amongst these new geometries is the bottom up approach utilizing vertical nanowires. The vertical geometry also enables easier integration of alternative high mobility semiconductor materials on a Si substrate. A potential canditate for integration on Si is the III-V compound semiconductors due improvements in charge carrier transport capabilities.

To further motivate a switch in transistor geometry the full infrastructure of devices need to be present, not only satisfying the logical domain. Therefore, in parallel to the digital branch, a wish for developing better analog RF-transistors is present. The requirements for an RF-transistor are quite different where stability and high frequency signal gain is of importance. In an RF circuit power dissipation can be sacrificed for increased performance, lending more room for new innovations.

In this thesis the use of the vertical nanowire geometry for MOSFET is further investigated by implementing a III-V, InAs/InGaAs, graded heterostructure, inside the channel, optimized for increased stability and low resistance ohmic-contacts. A Si-substrate with grown III-V nanowires, on top of a InAs buffer layer, is provided and afterwards processed into a complete set of devices. The orientation of the grading is chosen with an abrupt junction from the InAs buffer layer to InGaAs slowly graded back to InAs at the top, by implementing 550

nm long nanowires. The measured DC-characteristics indicates a presence of the heterostructure due to good saturation, low output conductance  $g_d \approx 2~\mu\text{S}/\mu\text{m}$  at  $V_{ds} = 0.5V$  and  $V_{gs} = 0.5V$ . Amplification and current does not reach intended values because of large access resistance,  $R_c \approx 1500~\Omega\mu\text{m}$ , with transconductance  $g_{m,max} = 280~\mu\text{S}/\mu\text{m}$ . Good gate control is indicated with devices showcasing low sub-threshold swing SS down to 80~mV/dec.

Motivation of introducing a heterostructure is clear due to higher breakdown and increased linearity but the choice of the grading orientation is not. Contact resistance is mostly originating from the source side, which means that there is large room for improvement by tweaking the process. The nanowires also had a tendency to collapse which decreased the performance. In other words the theory of implementing a heterostructure with abrupt junction for larger breakdown voltage and increased linearity is promising and cannot yet be disregarded.

# Populärvetenskaplig Sammanfattning

hastighet på 760,000 km/h, gå 42 000 km per liter och kosta 25 öre" hävdar Paul Ottelini, Intel VD mellan 2005-2013. Detta påminner oss om vilken rasande fart utvecklingen har inom nanoelektronik branschen där elektroniska kretsar ständigt blivit billigare samt mindre under det senaste halvseklet. Miniatyriseringen har fördelaktigt gått hand i hand med ökad prestanda. Den huvudsakliga beståndsdelen som används i dessa kretsar, som exempelvis en processor, är en transistor. Uppgiften för en transistor är att styra strömmar på så sätt att de kan stängas av eller på.

Transistorn består av tre huvudsakliga elektroder, där elektrisk spänning kan appliceras. Mellan två av elektroderna kan en ström färdas såsom igenom ett vanligt motstånd. Med den tredje, som brukar kallas gate, kan resistansen manipuleras vilket ändrar strömmen som färdas mellan de två övriga elektroderna. I en dator krävs det att transistorn ska fungera som ett relä, helt enkelt en effektiv av/på knapp. Här är prestandan väldigt beroende av hur många transistorer, logiska kretsar, som får plats på ett chip för att i slutändan kunna utföra många beräkningar samtidigt.

För analoga applikationer däremot, i till exempel radiosändare och mottagare, ställs andra krav. Här kan det räcka med endast ett fåtal transistorer som effektivt kan tolka och förstärka en signal som varierar över tiden. När frekvensen på signalen som ska sändas, eller mottagas, ökar kan även mer information transporteras. I framtiden krävs därmed pålitliga transistorer som hinner tolka snabba strömändringar på grund av signal-frekvenser på flera 100 GHz.

I den digitala världen har den pågående miniatyriseringen av de logiska kretsarna lett till att många dimensioner endast är tiotals atomer. Därmed uppkommer flera utmaningar vid vidare miniatyrisering av kretsarna som leder till att man fullkomligt förlorar kontrollen över gaten. För fortsatt utveckling tittar man då på alternativa material samt andra utformningar av transistorerna. Det tål att nämnas att det som sker i den digitala världen självklart påverkar den analoga sfären.

I detta arbete har möjligheten att skapa transistorer av stående cylindriska pelare, även kallade nanotrådar, undersökts. På dessa nanotrådar kan gaten lindas runt själva tråden för att få bästa möjliga kontroll av strömmen. Dessutom är olika material blandade inuti tråden för att uppnå gynnsamma villkor. Dessa villkor är att elektroner enkelt ska kunna färdas genom materialet samtidigt som transistorn ska vara pålitlig vid ett stort omfång av applicerad spänning på elektroderna. Därför har en blandning av indiumarsenid, som bidrar med hög rörlighet för elektroner, och indiumgalliumarsenid använts. Det sistnämnda materialet bidrar med extra pålitlighet. Den färdiga transistorn uppvisade god kontroll av strömmen med aningen begränsad prestanda. Notera att dessa transistorer är, i grund och botten, skapade ovanpå ett kiselprov, vilket gör denna teknologi överförbar till industriell skala.

## Acknowledgements

"Now this is not the end. It is not even the beginning.

But it is perhaps the end of the beginning."

Sir Winston Leonard Spencer-Churchill

My time as a student at Lunds University is coming to an end, or perhaps, a new beginning. When my interests of continuing on the academic path where flailing, a few people made me realise my potential. Among these people there are a two professors in particular, namely Dan Hessman and Lars-Erik Wernersson. The pursuit itself is priceless and the end result is necessarily not the most important. This is the way of the researcher. So from the bottom of my heart I would like to thank you for all your support.

I would also like to extend my gratitude to my practical coach Olli-Pekka, who tirelessly taught me a very long and complicated process, and Johannes Svensson, who had to developed an all new nanowire growth recipe. I am greatly humbled by the skill level possessed by these individuals.

My family has always been a source for inspiration and pushing me to pursue my dreams, therefore I thank Lars, Charita and Max.

Agan for

# Abbreviations & symbols

#### **Abbreviations**

ADC analogue-to-digital converter

ALD atomic layer deposition

$Al_2O_3$  aluminium oxide

Ar argonAs arsenicAsH<sub>3</sub> arsineAu gold

BOE buffered oxide etchBTBT band-to-band tunneling

C carbon

**DR** double row array

**EBL** electron beam litography

GAA gate all-aroundGaAs gallium arsenideGaN gallium nitrideGaSb gallium antimonide

**Ge** germanium

HBT heterojunction bipolar transistorHEMT high electron mobility transistor

HF hydro fluorideHfO<sub>2</sub> hafnium dioxide

**HSQ** hydrogen silsesquioxane

**ICP-RIE** inductively coupled plasma reactive-ion etching

In indium

**InAs** indium arsenide

InGaAs indium gallium arsenideInP indium phosphideInSb indium antimonide

**IPA** 2-propanol

MESFET metal-semiconductor field effect transistor

MOSFET mteal-oxide-semiconductor field effect transistor

MOVPE metalorganic vapour phase epitaxy

N<sub>2</sub> nitrogenNi nickelNW nanowire

**NWFET** nanowire field effect transistor

O oxygen

**PMMA** poly(methyl methacrylate)

RF Radio frequency RIE reactive-ion etcher

**SEM** scanning electron microscopy

Si silicon

SiO<sub>2</sub> silicon dioxide SiO silicon monoxide

Sn tin

**TESn** tetraethyltin

TFET tunnel field effect transistor

**TiN** titanium nitride

**TMAH** tetramethylammonium hydroxide

TMGa tetramethylgallium TMIn tetramethylindium

**UV** ultraviolet

UVL ultraviolet litography

VLS vapor-liquid-solid

W tungsten

### Physical constants

$\epsilon_0$  vacuum permittivity  $8.854 * 10^{-12}$  F/m  $k_B$  boltzmanns constant  $8.617 * 10^{-5}$  eV/K e eulers number 2.718 elementary charge  $1.602 * 10^{-19}$  C

### Symbols

| а                | lattice constant            | m                |

|------------------|-----------------------------|------------------|

| $\boldsymbol{A}$ | area                        | $m^2$            |

| $A_v$            | open circuit amplification  | -                |

| $C_{ox}$         | intrinsic oxide capacitance | F/m <sup>2</sup> |

| $C_{gd}$         | gate-drain capacitance      | F/m <sup>2</sup> |

| $C_{gs}$         | gate-source capacitance     | F/m <sup>2</sup> |

| ď                | distance                    | m                |

| $D_{it}$         | density of interface traps  | $m^{-3}$         |

| $E_C$            | conduction band energy      | eV               |

| $E_F$            | fermi-level                 | eV               |

| $E_g$            | band gap                    | eV               |

| $E_V$            | valence band energy         | eV               |

| $f_t$            | cut-off frequency           | Hz               |

| 8d               | output conductance          | S                |

| $g_m$            | transconductance            | S                |

| $I_{ds}$         | drain-source current        | A                |

| $I_{on}$         | on-state current            | A                |

| $I_{on}$         | off-state current           | A                |

| $N_d$            | donors                      | $m^{-3}$         |

| $N_a$            | acceptors                   | $m^{-3}$         |

| $V_{ds}$         | drain-source voltage        | V                |

| $V_{gs}$         | gate-source voltage         | V                |

| $V_t$            | threshold voltage           | V                |

| $R_{ch}$         | channel resistance          | $\Omega$ m       |

| $R_d$            | drain resistance            | $\Omega$ m       |

| $R_c$            | access resistance           | $\Omega$ m       |

| $R_{on}$         | on-resistance               | $\Omega$ m       |

| $R_s$            | source resistance           | $\Omega m$       |

| SS               | sub-threshold slope         | mV/dec           |

| $\mathcal{E}_r$ | relative permittivity           | _                  |

|-----------------|---------------------------------|--------------------|

| K               | dielectric constant             | F/m                |

| $\mu_e$         | electron mobility               | $cm^2V^{-1}s^{-1}$ |

| $\mu_p$         | hole mobility                   | $cm^2V^{-1}s^{-1}$ |

| $\phi_B$        | Schottky barrier potential      | V                  |

| $\phi_M$        | metal work function             | V                  |

| $\phi_s$        | semiconductor work function     | V                  |

| χ <sub>c</sub>  | semiconductor electron affinity | V                  |

# **Table of Contents**

| Intro |                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1   |                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.2   | Background & Future of MOSFET                                                                                                                          | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| MOS   |                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.1   | On-resistance                                                                                                                                          | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2.2   | ·                                                                                                                                                      | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| _     |                                                                                                                                                        | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|       |                                                                                                                                                        | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| _     |                                                                                                                                                        | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| _     |                                                                                                                                                        | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2.7   | Cut-off Frequency                                                                                                                                      | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| MOS   | SFET Evolution                                                                                                                                         | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| MOS   | SFET Fabrication                                                                                                                                       | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4.1   | Nanowire Growth                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4.2   | Top Metal Deposition                                                                                                                                   | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.3   | Drain Pad and Bottom Spacer                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4.4   | Gate Deposition                                                                                                                                        | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.5   | Via Holes and Top Contact                                                                                                                              | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Res   | ult & Analysis                                                                                                                                         | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.1   | Processing                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5.2   | Measurements                                                                                                                                           | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.3   | Benchmarking                                                                                                                                           | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.4   | Breakdown                                                                                                                                              | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Con   | clusion & Outlook                                                                                                                                      | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ferer | ices                                                                                                                                                   | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Bato  | ch #1 metrics                                                                                                                                          | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|       | 1.1<br>1.2<br>MOS<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>MOS<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>Res<br>5.1<br>5.2<br>5.3<br>5.4<br>Con | MOSFET Performance Metrics  2.1 On-resistance 2.2 Output Conductance 2.3 Transconductance 2.4 Threshold Voltage 2.5 Voltage Gain 2.6 Subthreshold Swing 2.7 Cut-off Frequency  MOSFET Evolution  MOSFET Fabrication 4.1 Nanowire Growth 4.2 Top Metal Deposition 4.3 Drain Pad and Bottom Spacer 4.4 Gate Deposition 4.5 Via Holes and Top Contact  Result & Analysis 5.1 Processing 5.2 Measurements 5.3 Benchmarking 5.4 Breakdown  Conclusion & Outlook  ferences |

# List of Figures

| A simplified sodium crystal containing only three atoms to model the total potential seen by the charge carriers. The valence electrons in the structure are shared, and can move between atoms. (a) The potential for the free charge carriers can be modelled by a simple square potential where local potential shift originating from the atomic nucleus is neglected. This modelling is sufficient to introduce the concept of effective mass. (b) Another layer is added to the model where a periodic pertubation, depending on lattice constant $a$ , is added. Crucial for the derivation of energy band gap seen by free charge carriers                       | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A typical shift in fermi-level $E_F$ during different doping. The intrinsic Fermi level $E_{F,i}$ resides in the middle of the band gap meaning that few free carriers are available and the material is highly resistive. The amount of free carriers $n$ or $p$ at room temperature is inversely dependant on the band gap $\frac{1}{E_g}$ . When adding donors $N_d$ to the semiconductor the fermi level is shifted upwards to $E_{F,n}$ and in this case reaches above degenerate limit meaning that chemical potential is inside the conduction band. The same shift occurs downwards in energy when adding acceptors $N_a$ and the potential ends up at $E_{F,p}$ | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Dense version of the periodic table with atoms involved in high speed electronic devices. III-V compounds with typical dopants Sn or Si can give both p and n-doping. <i>Source: Wikimedia Commons</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| The formed Schottky barrier, according to Schottky-Mott rule, in a metal-semiconductor junction. The height of the barrier is determined by the difference between metal work function $\phi_M$ and electron affinity of the semiconductor $\chi_s$ , see equation 1.1. Work function of the semiconductor $\phi_s$ is also given. Notice that $W$ depicts the width of the depletion region in the semiconductor in which the band bending takes place.                                                                                                                                                                                                                 | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | the total potential seen by the charge carriers. The valence electrons in the structure are shared, and can move between atoms. (a) The potential for the free charge carriers can be modelled by a simple square potential where local potential shift originating from the atomic nucleus is neglected. This modelling is sufficient to introduce the concept of effective mass. (b) Another layer is added to the model where a periodic pertubation, depending on lattice constant $a$ , is added. Crucial for the derivation of energy band gap seen by free charge carriers |

| 1.5 | Overview of how a MOSFET typically works. Depicting a planar n-transistor with no gate overlap (a) with the symbol describing a MOS transistor (b) in a circuit schematic. The schematic is used here to highlight relative position of terminals gate, drain and source in the band diagrams. The band simulations shows both off- (c) and on-state (d). Below threshold voltage $V_{gs} < V_t$ the biasing is insufficient for creating an n-channel and the potential barrier quenches the thermionic emission of electrons. Above threshold $V_{gs} > V_t$ the charge carriers can move past the potential barrier | 6  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

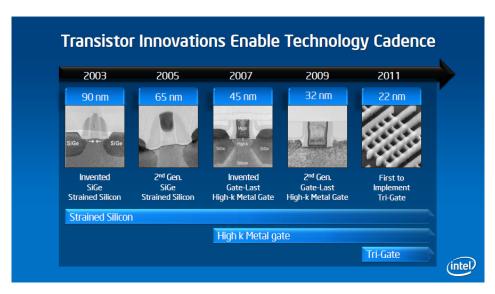

| 1.6 | Innovation flow in commercial logic transistors presented by <i>Intel</i> [18]. Change in high $\kappa$ was implemented in order to increase gate-thickness supressing leakage currents. 3d structures (lateral nanowires) for increased electrostatics has also already been introduced.                                                                                                                                                                                                                                                                                                                              | 7  |

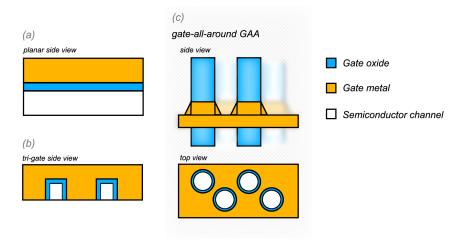

| 1.7 | Cross-sectional illustration of different gate geometries including planar, tri-gate and gate-all-around (GAA). (a) Side view of the conventional planar layout creating a sandwich of layers. (b) 3d implementation of lateral nanowires by tri-gate leading to better gate coverage, thus increased electrostatics compared to planar. (c) Complete overview of a GAA geometry, created with vertical nanowires, where ratio between gate width and cross-sectional channel area is maximized optimizing electrostatic control                                                                                       | g  |

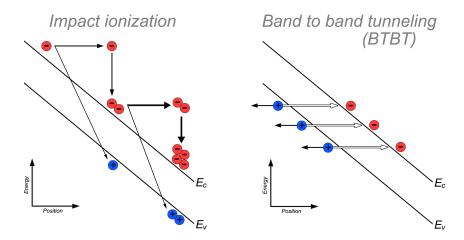

| 1.8 | Effects during high bias conditions. In impact ionization electrons in the conduction band gain enough energy, due to an external electric field, to create extra electron-hole pairs during a scattering event. With BTBT (band-to-band-tunneling) the potential barrier is sufficiently thin to allow quantum tunneling, also generating extra electron hole-pairs                                                                                                                                                                                                                                                   | 11 |

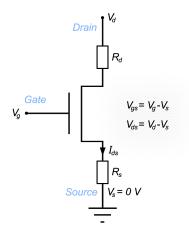

| 2.1 | A schematic of a MOSFET indicating the biasing points for an intrinsic device with added series resistance. Source is normally connected to ground as a reference which means that biasing is controlled through the gate $V_{gs}$ and drain $V_{ds}$ electrodes. Biasing results in pulling a current from drain to source $I_{ds}$                                                                                                                                                                                                                                                                                   | 13 |

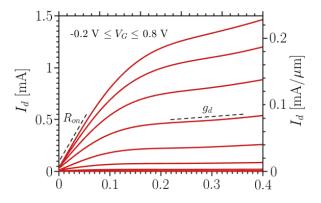

| 2.2 | Output conductance of an actual MOSFET, illustrating extraction of $g_d$ and $R_{on}$ . Notice that on-resistance $R_{on}$ is extracted below the saturation region and given as the inverse of the derivative                                                                                                                                                                                                                                                                                                                                                                                                         | 14 |

| 2.3 | A typical example of transfer characteristics for an enhancement mode MOSFET, in linear (a) and logarithmic scale (b). Example extracted from an actual measured transistor. $g_m$ represents the derivative of the $I_d$ - $V_{ds}$ characteristics. $V_t$ extrapolation carried out with the tangent of the voltage that yields maximum $g_m$ . $SS$ is given by the slope of the exponentially increasing sub-threshold, $V_{gs} < V_t$ , segment. $I_{on}$ is defined as one drive voltage $V_{dd} = 0.5V$ above a fixed $I_{off}$ current of 100 nA/ $\mu$ m                                                      | 15 |

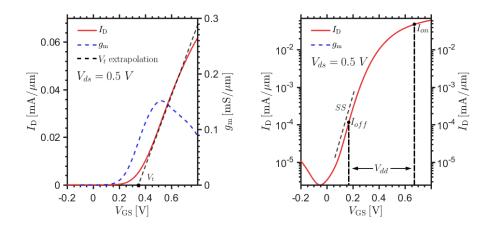

| 3.1 | a) The conventional "drain last" process developed by Sofia Johansson. b) Comparison done with self aligned gate process, "drain first", outlined by Martin Berg [46, 47]. Schematic used, with permission, from doctoral thesis by Martin Berg                                                                                                                                                        | 17 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

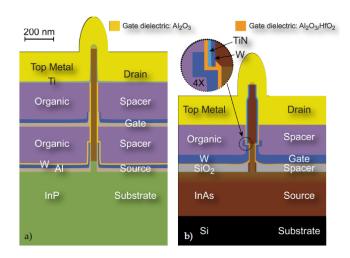

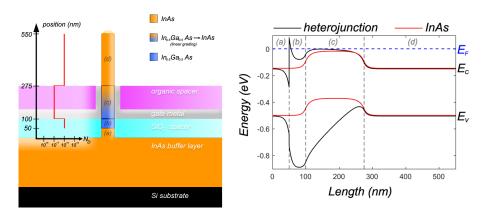

| 3.2 | Showing the benefits, by band-structure simulation, of incorporating InGaAs [50]. Schematic used, with permission, from doctoral thesis by Jun Wu                                                                                                                                                                                                                                                      | 18 |

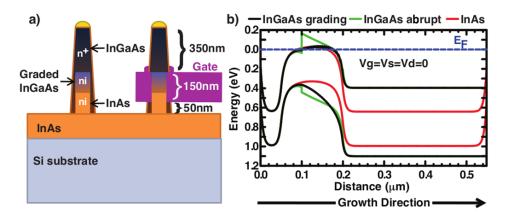

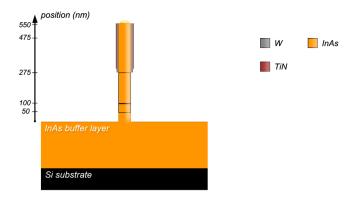

| 3.3 | A sketch for the nanowire MOSFET optimized for high breakdown, processed in this thesis. Bottom contact consists of the substrate (a) and top contact will cover the (d) segment                                                                                                                                                                                                                       | 19 |

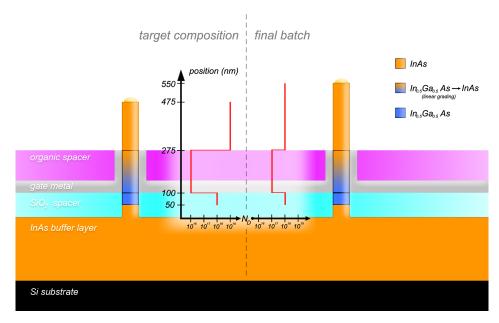

| 3.4 | A sketch for composition of the nanowires processed in this thesis. Due to limitations and variations during growth there is a difference between the target composition and final batch                                                                                                                                                                                                               | 20 |

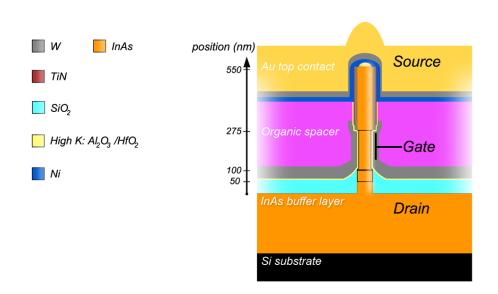

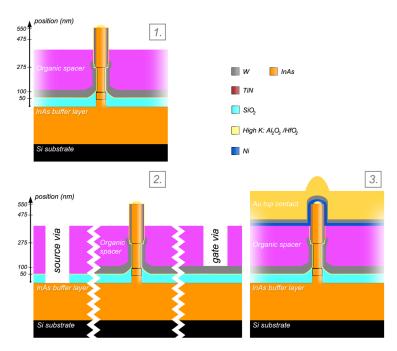

| 4.1 | An overview of the finished transistor in top ground configura-<br>tion. The structure can also be bottom grounded meaning that<br>the source and drain contacts, in this case, are switched. The<br>choice of the optimal configuration, top ground, is motivated by<br>band-simulations, see Fig 3.3                                                                                                 | 21 |

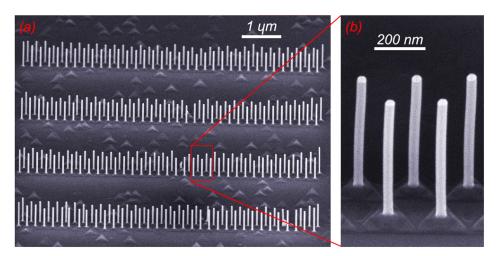

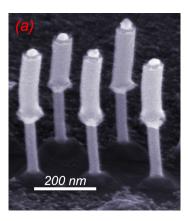

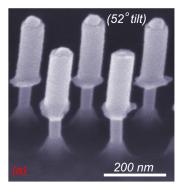

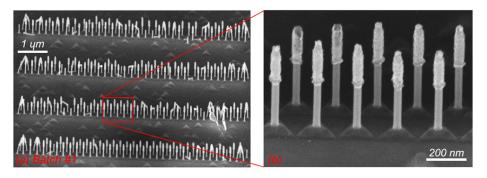

| 4.2 | High resolution SEM images of the grown nanowires. Gold particle diameter defined by EBL is 28 nm. (a) A full set of double row arrays with internal spacing of 200 nm. (b) Zoom in of a few nanowires in the array to highlight the smooth surface which indicates good crystal quality                                                                                                               | 22 |

| 4.3 | A schematic image depicting the top contact deposited by sputtering and ALD.                                                                                                                                                                                                                                                                                                                           | 23 |

| 4.4 | The finished top metal deposition, see schematic in Fig 4.3. Notice the unwanted residues left on the surface. Showing double row array (a) and single (b) nanowire structure.                                                                                                                                                                                                                         | 24 |

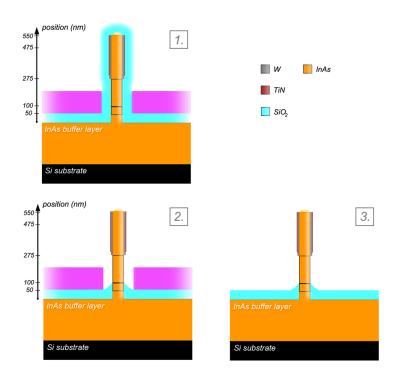

| 4.5 | The creation of the first spacer. $\boxed{1}$ A SiO $_2$ spacer is first applied via ALD. Organic resist is later spun onto the sample and thinned down via O $_2$ dry etching. $\boxed{2}$ The SiO $_2$ spacer is etched via HF (1:100 H $_2$ O) wet etch with the organic spacer acting as a etch mask. $\boxed{3}$ The resist spacer is removed with acetone leaving only the finished first spacer | 25 |

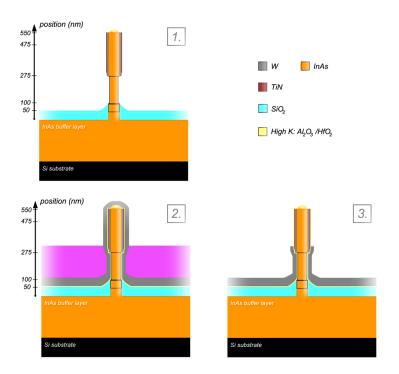

| 4.6 | Deposition of the gate contact. 1 Etching is performed targeting the exposed semiconductor effectively thinning it below 30 nm of diameter. 2 60 nm of tungsten is sputtered onto the sample. A                                                                                                                                                                                                        |    |

|     | organic spacer is created via spun on resist and dry etching. $\boxed{3}$ The exposed tungsten is removed via SF <sub>6</sub> dry etch. The organic spacer is afterwards removed via aceton                                                                                                                                                                                                            | 26 |

| 4.7 | The result of the gate length definition. Showing a double row array (a) after high- $\kappa$ deposition and (b) post gate etch                                                                                                                                                                                                                                                                        | 27 |

| 4.8 | Deposition of the second spacer and top contact. $\boxed{1}$ An organic spacer is spun onto the sample, permanently baked and thinned down via $O_2$ dry etching. $\boxed{2}$ Via holes are etched with sacrificial resist layer acting as etch mask where via holes are exposed, one at a time, via UV litography. $\boxed{3}$ Top contact is sputtered consisting of Ni, W and Au                                                                                                                                                                                       | 28<br>28 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

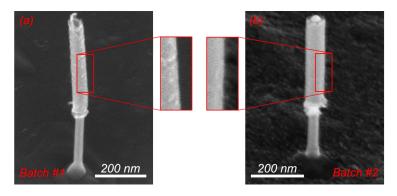

| 5.1 | Two single nanowire structures after removal of the temporary HSQ spacer. Highlighting the metal surface roughness for com-                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

| 5.2 | The damage after fabricating the top metal in batch #1. Hollow top                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 31       |

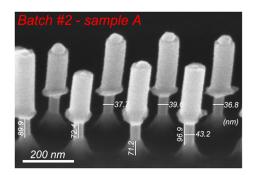

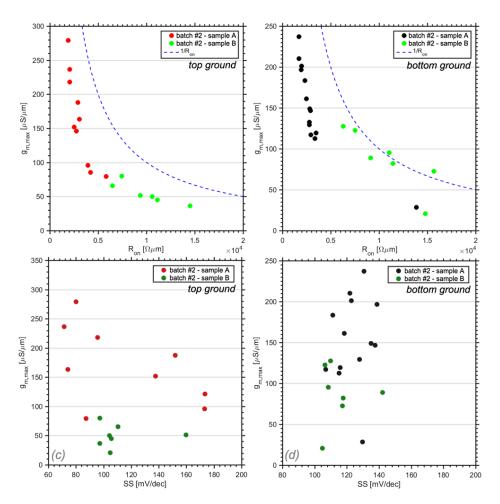

| 5.3 | metals are visible and the metal surface roughness is clearly shown. Nanowires after digital etch and high- $\kappa$ deposition for both samples in batch #2. High- $\kappa$ thickness is 4.5 nm according to SEM inspections, thus the mean diameter of the specific array in <i>Sam</i> -                                                                                                                                                                                                                                                                               | 31       |

| 5.4 | ple A is 29 nm and 35 mn in Sample B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 31       |

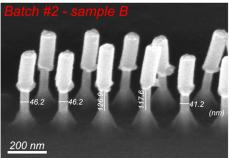

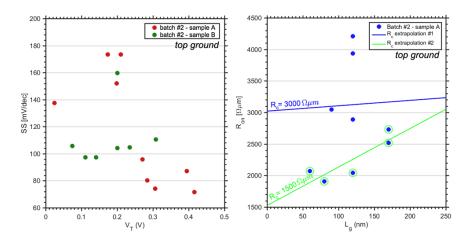

| 5.5 | expected exponential trend when decreasing the total resistance. (c)-(d) Outlines $SS$ dependence of $g_{m,max}$ , showing no clear trend. Exhibiting the $SS$ - $V_t$ and $R_{on}$ - $L_g$ dependence. Attempts for extrapolating the access resistance, $R_c = R_s + R_d$ , are performed with taking all values into account (#1) and a selected few (#2) that are highlighted. A smaller ratio of collapsed nanowires seem to be present in the highlighted devices. Note that the $L_g$ values are based on estimates from SEM pictures that, in this case, might be | 33       |

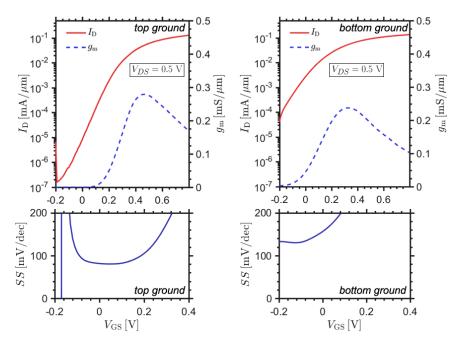

| 5.6 | insufficient due to large thickness variation of the bottom spacer  Transfer characteristics, plotted in logarithmic scale, for the hero                                                                                                                                                                                                                                                                                                                                                                                                                                  | 34       |

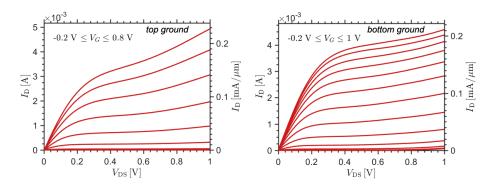

| 5.7 | device found batch #2. Metrics compiled in Fig 5.2.1 Output characteristics for the hero device found batch #2. Metrics                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 35<br>36 |

| 5.8 | compiled in Fig 5.2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 38       |

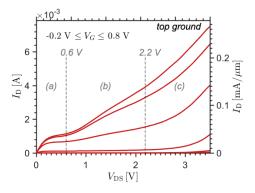

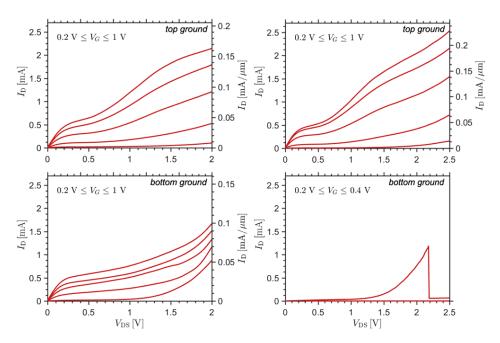

| 5.9 | Comparing output characteristics for top and bottom ground configuration in a representative, double row, device. The device is found batch #2-sample A. The transistor breaks at 2.2 V in bottom ground. Different segments can be identified with (a) being well saturated and (b) showing impact ionization that accelerates                                                                                                                                                                                                                                           |          |

|     | further in (c)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 39       |

# List of Tables

| 1.1 | Comparing dielectrics materials that are generally used for MOS-FET. Both large offset $\Delta E_{c,InAs}$ and bandgap is crucial for reduction of leakage. [24]                                                                                                                                                                                                                             | 8  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Outlining important material parameters for selected IV and III-V semiconductors. Superior transport $\mu_n$ is shown for the III-V compounds compared to silicon. Parameters taken from [37]. Notice that the injection velocity for electrons $v_{inj,e}$ is extracted from virtual source modelling with $L_g=30$ nm [34]                                                                 | 10 |

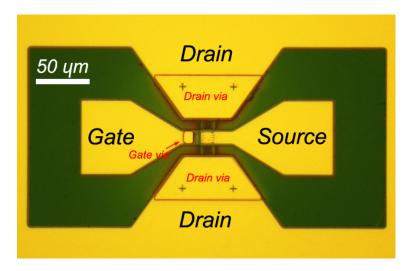

| 5.1 | A quick comparison between processed samples. $^1$ Top contact quality and gate alignment greatly improved between batches, with the first batch having $\sim$ 20 nm of ungated channel area. $^2$ All processing was optimized for the double row (DR) arrays in the second batch. The gate length is varying between devices due to both the bottom spacer and position of the top contact | 30 |

| 5.2 | A measurement overview showing the best devices from each processed batches. $L_g$ and diameter is inspected via SEM. $g_{m,max}$ and $SS_{min}$ are extracted from measurements. Notice that $g_{m,max}$ is normalized via inspections which is a quite crude method                                                                                                                        | 32 |

| 5.3 | Outlining all metrics for the best device in batch #1. Values are extracted from SEM inspections. All data is normalized to the total circumference of the nanowires. $^1\text{Bias}$ conditions are chosen in active region of the transistor at $V_g=0.5$ and $V_{ds}=0.5V.\ldots$ .                                                                                                       | 36 |

| 5.4 | A comparison with mainly other work from the research group (Nanoelectronics Group), created in the same lab using mostly the same equipment. V highlight the vertical orientation of the device, other devices utilize a lateral geometry. Notice that all V-NW devices are integrated on silicon while the both the HEMT and record device are based on an InP(III-V) substrate.           | 37 |

|     |                                                                                                                                                                                                                                                                                                                                                                                              |    |

A.1 Outlining all metrics for the best device in batch #1. Values are extracted from SEM inspections. All data is normalized to the total circumference of the nanowires.  $^1A$  mean value has been extracted from SEM inspections of other pads  $^2B$ ias conditions are chosen in active region of the transistor at  $V_g = 0.5$  and  $V_{ds} = 0.6V$ . 47

\_ Chapter

### Introduction

In the year 1925 Julius Edgar Lilienfeld filed a patent for the field effect transistor FET, describing the basics of what later would be known as the metal-oxide-semiconductor field effect transistor MOSFET [1]. Due to high purity semiconductors not being available the concept was experimentally confirmed decades later by Bell Labs in 1948. Further development was, at the time, not pursued due to problems connected to the surface of the semiconductor. Instead the germanium based point-contact transistor, invented in 1947, stole the show and became commercially available for use in the early pocket radios, replacing the bulky vacuum tubes [2]. Connected to improvement in semiconductor quality and advent of integrated circuits (ICs) based on silicon in the 1960s the dreams of the MOSFET once again resurfaced. At this point the interface problems had been resolved by means of taming the strong native oxide found in silicon. The emergence of the computer industry further pushed the revolution with constant demands for faster and more energy efficient circuits.

Gordon E. Moore released his predictions (Moore's law) in 1965 stating that the number of transistors per chip area will roughly double every 24 months via geometrical downscaling [3]. The predictions was based on the fact that increased packing density leads to exponential increase in performance as well as lower power dissipation of the circuits. Moore's law was followed strictly up until 2002 when the downscaling became constricted by power dissipation of 100 W/cm<sup>2</sup> [4]. To avoid overheating increase of performance was now pursued with multi-core systems and parallelization of computer tasks rather than speed.

Today the industry is in a place where things are shaken up with uncertainty. Improvements in transistor technology is now heavily dependent on innovations rather than downscaling. The technology demands has also changed with the upcoming era of IoT (Internet of things) setting up new standards for RF-transistors used in wireless communications [5]. A potential candidate for meeting the demands is to integrate III-V high speed material, on silicon substrates, utilizing a nanowire geometry with gate all-around (GAA) configuration. This alternative is further examined in this thesis. The needed background for absorbing and understanding the benefits of the work in this thesis is given in this chapter.

#### 1.1 Semiconductor Physics

To grasp the concept of transistor technology it is important to have a fundamental understanding of its building blocks, namely the semiconductor. Normally a semiconductor consists of a solid chemical element or compound, for example III-V semiconductors, and is used for integrated circuits due to its ability to conduct electricity during some circumstances but not others. To explain this behaviour concepts of chemical potential and band gap are introduced. An intrinsic semiconductor has its chemical potential, described by Fermi-Dirac statistics, placed inside the band gap typically ranging from 0.5 up to 8 eV. Few charge carriers are typically available in a semiconductor leading to poor conductance. To circumvent this issue doping is introduced increasing the amount of charge carriers inside the conduction band. The concepts are further explained in this chapter.

#### 1.1.1 The Origin of Band Structure

In a single atom the energy levels for orbiting electrons (fermions) are quantized maintaining a unique quantum number, described by the Pauli Principe [6]. Charge of the nucleus determines the amount of orbiting electrons, and size of the electron cloud, which controls the properties of the atom. In case of a semiconductors the atoms align in form of a crystal. When the atoms become tightly packed (lattice constant order of magnitude  $a \sim A$ ) hybridization occurs, wave functions overlap and mutual orbits for electrons are created. Pauli principle still applies, therefore the orbits spread in energy, see Fig 1.1. Two electrons can still have the same relative energy but will not share the same spin. The size of the bands depend on the energy of the bound states where the electrons originated from. To decide if a solid is in fact a semiconductor, metal or even an insulator the concept of a chemical potential, Fermi-level  $E_F$ , is introduced showing the statistical energy of the free charge carriers inside the crystal. Definitions of conduction and valence band are also introduced, with the valence band being the last filled energy band and conduction band being the next band with higher energy. Thus a metal has a Fermi level placed inside the conduction band and a semi-conductor has its potential placed inside a band gap, meaning that there are no free carriers inside the conduction band at absolute zero temperature 0 K. In reality there is always carriers inside the conduction band due to thermal excitation.

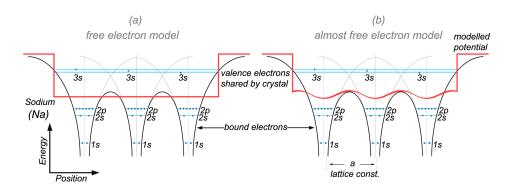

A general concept is that the crystal structure shares electrons that can move "freely" inside the crystal lattice [7]. But since the electrons are moving inside a cluster of charge this is modelled by introducing a different effective mass  $m^*$  for the charge carriers, see Fig 1.1 (*free electron model*). The potential of each atomic nucleus can be seen as a periodic perturbation in the free electron model, thus at certain wave vectors  $\vec{k} = n\pi/a$  ( $n \in \mathbb{Z}$ ) the periodicity of the carriers will resonate with the perturbation effectively shifting the kinetic energy of the carriers creating a band gap (*nearly free electron model*).

**Fig 1.1:** A simplified sodium crystal containing only three atoms to model the total potential seen by the charge carriers. The valence electrons in the structure are shared, and can move between atoms. (a) The potential for the free charge carriers can be modelled by a simple square potential where local potential shift originating from the atomic nucleus is neglected. This modelling is sufficient to introduce the concept of effective mass. (b) Another layer is added to the model where a periodic pertubation, depending on lattice constant *a*, is added. Crucial for the derivation of energy band gap seen by free charge carriers.

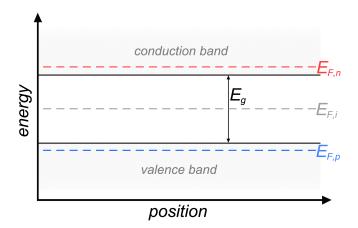

**Fig 1.2:** A typical shift in fermi-level  $E_F$  during different doping. The intrinsic Fermi level  $E_{F,i}$  resides in the middle of the band gap meaning that few free carriers are available and the material is highly resistive. The amount of free carriers n or p at room temperature is inversely dependant on the band gap  $\frac{1}{E_g}$ . When adding donors  $N_d$  to the semiconductor the fermi level is shifted upwards to  $E_{F,n}$  and in this case reaches above degenerate limit meaning that chemical potential is inside the conduction band. The same shift occurs downwards in energy when adding acceptors  $N_a$  and the potential ends up at  $E_{F,p}$ .

#### 1.1.2 Doping

To manipulate the placement of the chemical potential, thus changing the electrical properties of the semiconductor, impurities are introduced effectively doping the crystal, see Fig 1.2 [8]. Doping means that few atoms inside the crystal lattice of a semiconductor is substituted with compatible atoms from another material to create an abundance (n-type) or absence (p-type) of electrons. Absence of electrons can be modelled as quasi-particles called holes, normally with higher effective mass  $m^*$  compared to electrons. Substituted atoms lending extra electrons are called donor states  $N_a$  and respectively when removing electrons they are called acceptor states  $N_d$ .

În this work a n-doping is used in the order of  $N_d \approx 10^{18}$  cm<sup>-3</sup>, for comparison the concentration of atoms in a crystal is approximately  $1/a^3 \approx 10^{21}$  cm<sup>-3</sup>. III-V compounds, in many cases, have quite large lattice constant, small atom density, compared to Si which means that relatively small doping leads to degenerate Fermi-level [9]. A semiconductor overview and comparison is given in Table 1.2.

| Group→ 13<br>↓Period |    | 14 | 15 |

|----------------------|----|----|----|

| 3                    | 13 | 14 | 15 |

|                      | Al | Si | P  |

| 4                    | 31 | 32 | 33 |

|                      | Ga | Ge | As |

| 5                    | 49 | 50 | 51 |

|                      | In | Sn | Sb |

**Fig 1.3:** Dense version of the periodic table with atoms involved in high speed electronic devices. III-V compounds with typical dopants Sn or Si can give both p and n-doping. *Source: Wikimedia Commons*

In this thesis III-V compound InGaAs are doped during epitaxial growth, called in-situ doping, with Sn to add donors  $N_d$ . Seen from Fig 1.3 the gallium(Ga) or indium(In) atoms in InGaAs compound need to be substituted with impurities in order to achieve n-doping.

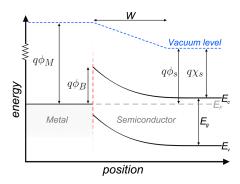

#### 1.1.3 Schottky Barrier

Necessary for further understanding of transistor device physics is the formation of Schottky barriers in metal-semiconductor junctions, see Fig 1.4. In early studies it was believed that the height  $\phi_B$  of the formed potential barrier was only dependent on the difference between metal work function  $\phi_M$  and electron affinity  $\chi_s$  of the semiconductor, described by the Schottky-Mott rule [10]

$$q\phi_B \approx q(\phi_M - \chi_s) \tag{1.1}$$

where q is the elementary charge. The length of the depletion region W, inside the semiconductor, can be reduced with higher doping according to

$$W \sim \frac{1}{\sqrt{N_d}}. ag{1.2}$$

A thinner barrier allows higher chance of tunneling events which translates to less resistance in the junction [36].

**Fig 1.4:** The formed Schottky barrier, according to Schottky-Mott rule, in a metal-semiconductor junction. The height of the barrier is determined by the difference between metal work function  $\phi_M$  and electron affinity of the semiconductor  $\chi_s$ , see equation 1.1. Work function of the semiconductor  $\phi_s$  is also given. Notice that W depicts the width of the depletion region in the semiconductor in which the band bending takes place.

In practice the characterisation of the junction is much more complex because the height of the Schottky barrier is heavily dependent on surface states, known as metal induced gap states (MIGS), formed at the surface in between materials [11]. Therefore certain semiconductors exhibit different degrees of Fermi level pinning, meaning that the Fermi level of the semiconductor pins to certain positions relative to the chemical potential of the metal. Basically the gap states gets charged and drive the band lineup to a new equilibrium state. The Fermi level pinning needs to be taken into account when choosing transistor material.

### 1.2 Background & Future of MOSFET

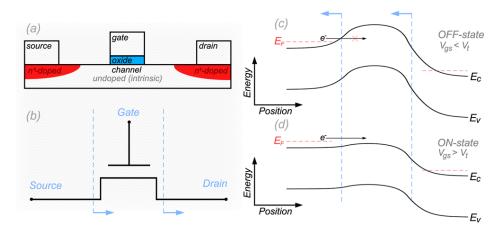

MOSFET uses manipulation of energy-barriers to either quench or conduct a current, toggling between on- and off-state [13]. The transistor is comprised of normally four different terminals; gate(G), drain(D), source(S) and body(B). The body terminal consists of the substrate itself in planar cases but when utilising the geometry of a NWFET the substrate is not a part of the active region effectively making it into a three terminal device. Active region of the MOSFET is called channel which is controlled via the gate terminal through a metal-oxide-semiconductor MOS interface, using an oxide as insulator. The MOS structure gives rise to a capacitance that makes it possible to control the potential of the free charge carriers inside the semiconductor channel. Different regimes are therefore defined to further describe the state of the charge carriers in the channel under different bias conditions applied to the gate electrode  $V_{gs}$ , namely accumulation, depletion and inversion. During accumulation the charge carriers, that constitutes the majority, are attracted to the semiconductor surface, along the oxide interface,

and in depletion these carriers are instead greatly reduced. When increasing the degree of depletion, by modulating the gate bias above a certain threshold voltage  $V_{gs} > V_t$ , new minority charge carriers are being generated effectively inverting the channel, thus inversion is achieved.

**Fig 1.5:** Overview of how a MOSFET typically works. Depicting a planar n-transistor with no gate overlap (a) with the symbol describing a MOS transistor (b) in a circuit schematic. The schematic is used here to highlight relative position of terminals gate, drain and source in the band diagrams. The band simulations shows both off- (c) and on-state (d). Below threshold voltage  $V_{gs} < V_t$  the biasing is insufficient for creating an n-channel and the potential barrier quenches the thermionic emission of electrons. Above threshold  $V_{gs} > V_t$  the charge carriers can move past the potential barrier.

At the two ends of the channel the source and drain terminals are situated and used to control the electric field, by  $V_{ds}$ , in the direction of the channel, hence controlling the passing current  $I_{ds}$ . If there is an energy barrier present inside the channel, due to difference in doping levels between channel and source/drain terminals, the current will not be able to flow from D- to S-terminal without external bias, called an enhancement mode device [14]. An example of a n-type enhancement mode device is depicted in Fig 1.5, where accumulation of electrons inside the channel turns the device on [15].

Compared to other transistors the MOSFET offers low leakage current from the gate electrode due to the insulating oxide in the MOS interface [16]. Maintaining a low off-state leakage is key for reaching higher energy-efficiency in logical circuits where the amount of transistors is correlated to increased processing power. Available field effect transistor without the metal-oxide-semiconductor interface is for example high-electron-mobility-transistor HEMT or metal-semiconductor-field-effect-transistor MESFET. A HEMT uses a wide bandgap material, as substitute for a dielectric, between metal and channel which leads to good quality semiconductor interfaces sacrificing energy-efficiency for improved carrier transport properties [17]. These characteristics are beneficial for transistors used in RF

applications.

#### 1.2.1 Importance of High- $\kappa$ Oxides

**Fig 1.6:** Innovation flow in commercial logic transistors presented by *Intel* [18]. Change in high  $\kappa$  was implemented in order to increase gate-thickness supressing leakage currents. 3d structures (lateral nanowires) for increased electrostatics has also already been introduced.

The on-going down scaling outlined by Moore's Law has started to reach a certain limit where several quantum effects cannot be disregarded [12]. Amongst these effects are quantum tunneling, through the gate, which means that the oxide insulator inside the MOS structure is so thin that the wave-function of the charge carriers start to reach beyond the oxide, leading to an unwanted gate-leakage current [36]. In industry today silicon (Si) is widely used due to its availability, but also its native oxide SiO<sub>2</sub>. Due to silicon having a strong native oxide (SiO<sub>2</sub>), the interface created between the materials has low density of interface traps  $D_{it}$  [19]. SiO<sub>2</sub> also acts as a good insulator with sufficiently high permittivity  $\varepsilon_r \varepsilon_0 \equiv \kappa$ .

A simple expression for the oxide capacitance  $C_{ox}$  [F/m<sup>2</sup>] is given as

$$C_{ox} = \frac{\varepsilon_r \varepsilon_0}{d} \equiv \frac{\kappa}{t_{ox}}$$

with  $t_{ox}$  as the thickness of the dielectric. According to this simple formula tunneling effects, gate leakage, can be circumvented by keeping a thick oxide ( $\sim$  nm) and change to another dielectric material with higher  $\kappa$  to preserve electrostatics, see Table 1.1. A typical oxide with high  $\kappa$ -value is HfO<sub>2</sub> and is presently used by Intel instead of SiO<sub>2</sub> see Fig 1.6 [22]. When introducing new oxide materials, issues regarding interface traps  $D_{it}$  are more prominent due to dangling bonds and point defects [23]. In this work III-V semiconductors are utilized which lacks

good native oxides. Implementing a high- $\kappa$  oxide on III-Vs can hence lead to insufficient electrostatic control [20]. To minimize interface states, bi-layers can be utilized with for example  $Al_2O_3$  as a buffer layer between semiconductor and  $HfO_2$ . Another source of  $D_{it}$  is doping of the semiconductor, where in-situ doping can degrade the crystal quality and therefore also the high- $\kappa$  interface [21].

**Table 1.1:** Comparing dielectrics materials that are generally used for MOSFET. Both large offset  $\Delta E_{c,InAs}$  and bandgap is crucial for reduction of leakage. [24]

| Dielectric      |                  | $\kappa/\varepsilon_0$ | Bandgap [eV] | $\Delta E_{c,InAs}$ [eV] |

|-----------------|------------------|------------------------|--------------|--------------------------|

| Silicon dioxide | SiO <sub>2</sub> | 3.9                    | 9            | 4.1                      |

| Silicon Nitride | $Si_3N_4$        | 7                      | 5.3          | 2.7                      |

| Hafnium dioxide | HfO <sub>2</sub> | 25                     | 5.8          | 2.5                      |

| Aluminium oxide | $Al_2O_3$        | 9                      | 8.8          | 3.6                      |

| Zirconium oxide | $ZrO_2$          | 25                     | 5.8          | -                        |

#### 1.2.2 Benefits of NWFET and III-Vs

Due to the nature of the vertical nanowire geometry, strain between different crystal planes (lattice mismatch) can more easily be relaxed [26]. This creates vast opportunities of mixing different materials in so called heterojunctions to improve transistor performance. III-V nanowires can thus be integrated on top of a Si-substrate creating a more industry compatible and sustainable process [28]. Predictions have already been made stating that III-V compounds will be integrated on Si in commercial CMOS to benefit from the good transport properties, see Table 1.2, in order to improve energy efficiency and speed. The vertical geometry leads to increased packing density with the footprint area decoupled from the gate length  $L_g$  with corresponding metal contacts [27]. III-V wafers are small, brittle and expensive compared to Si-wafers, III-V materials are also less abundant in the earths crust making it crucial to still use Si-wafers [25].

Main benefit of changing to a more complex 3D structure is to improve electrostatic control with wrap-around gate configurations such as tri-gate (Fig 1.6) and gate-all around (GAA). This means that ratio between cross-sectional area of the channel and gate width is large, compared to its planar counterpart, maximizing gate control, see Fig 1.7. Continued downscaling of MOSFET devices has increased packing density and reduced drive voltage, in other words overall improvement of performance and cost per device. However, in the last decade, shrinking dimensions has also lead to undesirable short channel effects (SCE) such as drain induced barrier lowering DIBL and increased subthreshold swing SS, especially at  $L_g \leq 30$  nm [29]. Switching from Si to III-V semiconductors will mean that drive voltage can be lowered without further downscaling of the gate length  $L_g$ , due to superior mobility [30]. With better transport properties, the mean free path for charge carriers is increased which can potentially make the device oper-

**Fig 1.7:** Cross-sectional illustration of different gate geometries including planar, tri-gate and gate-all-around (GAA). (a) Side view of the conventional planar layout creating a sandwich of layers. (b) 3d implementation of lateral nanowires by tri-gate leading to better gate coverage, thus increased electrostatics compared to planar. (c) Complete overview of a GAA geometry, created with vertical nanowires, where ratio between gate width and cross-sectional channel area is maximized optimizing electrostatic control.

ate in the ballistic regime, with no scattering events occuring inside the channel. Intel has already improved transport properties (~ 70%) by implementation of strained silicon as channel material, see Fig 1.6 [31].