Master's Thesis

## **High Level Synthesis for Design** of Video Processing Blocks

Ayla Chabouk Carlos Gómez

Department of Electrical and Information Technology, Faculty of Engineering, LTH, Lund University, March 2015.

HIOD.S

166

IAT

Department of Electrical Engineering and Information Technology Master of Science Thesis

## High Level Synthesis for Design of Video Processing Blocks

Authors: Ayla Chabouk Carlos Gómez

> Supervisors: Joachim Rodrigues Thomas Lenart

March 20, 2015

Printed in Sweden E-huset, Lund, 2015

### Abstract

Nowadays the technology is progressing continuously. The designers are developing products with new features and always giving to the user an innovative technological solution for the society problems. The standard methods to design new devices are becoming slower for the demand of the products. Due to this growing complexity, some possible substitutes of the traditional Register Transfer Level (RTL) design flow has been appeared. This situation is becoming a bigger problem which needs to be solved and that is why many opened researches exist about it.

In the early 90s started the idea of High Level Synthesis (HLS) and in the actual market is getting more relevance like a substitution of the standard designing methods. In a brief description, High Level Synthesis is an automatic compilation technique that translates a software program to a hardware circuit. The critical step to jump to this new field is if High Level Synthesis will give to the designers, at least, the same design possibilities and the same quality of results as handwritten hardware design. During the last ten years many companies and academic organizations has emerged which have been developing new tools for High Level Synthesis.

The scope of this Master's Thesis is to evaluate one of these commercial tools (Catapult from Calypto), to understand the possibilities and the limitations of it. The purpose of the thesis is to study, analyze and test the tool with reference models (video blocks) provided by ARM Sweden. The handwritten RTL description of the models, were provided by ARM to be used to verify and compare the correctness and the QoR (Quality of Results) of the RTL generated by the HLS tool, Catapult.

After developing the Master's Thesis, Catapult obtained the same functionality, the same performance and the same operating frequency with all the blocks worked with. However, the principal limitation of Catapult that was experienced during the work, is the total area of the generated RTL in more complex designs. The two larger designs developed in Catapult resulted in a larger area score result after synthesis compared with the handwritten RTL. Apart from this issue, HLS gives a huge advantage in comparison with handwritten RTL: the short time it takes to develop a complete hardware design and the possibility to explore different area/performance trade-off.

### Acknowledgement

This Master's Thesis would not be possible without the support and guidance of both of our supervisors. We would like to thank to Thomas Lenart, our supervisor at ARM, for all the daily meeting and for his valuable comments and advices during the thesis work. He was always available for help with the countless problems that we faced during the last months. His attention and inspiration dedicated to us during the time we spent working with him is invaluable. We would also like to thank to Joachim Rodrigues, our supervisor at LTH, for encouraging our ideas and for the many insightful suggestions. He was always trying to get the best of us. All we have learnt through the master's program and the thesis is something that we will never forget.

We would like to thank to ARM for having trust on us and giving us the possibility of doing the thesis with them. We want to thank them for making our stay over the last six months comfortable and for proving us the latest and advanced tools and access to all the facilities.

We would like to thank to Calypto for all the support, clarifications and guidance that they have given to us during the thesis.

We would like to express our gratitude to all the person involved in our education in both universities, LTH and ETSIT, that have helped us to improve our skills and our knowledge during the last 6 years. We are really thankful with them due to giving us the opportunity of living this great experience.

Finally, we would like to say that all these would not be possible without the love and support of our families and friends.

Ayla Chabouk Jokhadar Carlos Gómez González

## Contents

| Ab  | stract |         |                           | i    |

|-----|--------|---------|---------------------------|------|

| Ac  | knowl  | edgem   | ent                       | iii  |

| Ta  | ble of | Conte   | nts                       | v    |

| Lis | t of F | igures  |                           | ix   |

| Lis | t of T | ables_  |                           | xi   |

| Ab  | brevia | tions_  |                           | xiii |

| 1   | Intro  |         | n                         | 1    |

|     | 1.1    | 0       | round                     | 1    |

|     | 1.2    | •       | ult                       | 3    |

|     | 1.3    |         | scope and objectives      | 4    |

|     | 1.4    | Thesis  | organization              | 4    |

| 2   | HLS    | design  | and Catapult flow         | 7    |

|     | 2.1    | Archit  | ecture                    | 8    |

|     |        | 2.1.1   | Communication by channels | 8    |

|     |        | 2.1.2   | Bit-accurate data types   | 10   |

|     |        | 2.1.3   | Memory implementation     | 12   |

|     | 2.2    | Catapı  | ult flow                  | 13   |

|     |        | 2.2.1   | Catapult tasks            | 15   |

|     |        | 2.2.2   | Output files              | 26   |

|     |        | 2.2.3   | Verification              | 27   |

|     |        | 2.2.4   | Synthesis                 | 31   |

|     | 2.3    | Catapı  | ult Library Builder       | 32   |

|     |        | 2.3.1   | Cell Library              | 32   |

|     |        | 2.3.2   | Memory libraries          | 34   |

| 3   | Refe   | rence [ | Designs                   | 35   |

|     | 3.1    | Simple  | e blocks                  | 36   |

|   |      | 3.1.1   | DBL filter H.264                                               |

|---|------|---------|----------------------------------------------------------------|

|   |      | 3.1.2   | DBL filter HEVC                                                |

|   |      | 3.1.3   | DBL filter Real                                                |

|   | 3.2  | Compl   | lex blocks                                                     |

|   |      | 3.2.1   | DBL SAO                                                        |

|   |      | 3.2.2   | HEVC Controller block                                          |

| 4 | Impl | ementa  | ation                                                          |

|   | 4.1  |         | opment of simple blocks                                        |

|   | 4.2  |         | opment of DBL SAO                                              |

|   |      | 4.2.1   | Structure development                                          |

|   |      | 4.2.2   | Constraints Set                                                |

|   | 4.3  | Develo  | opment of the HEVC Controller Block                            |

|   | 4.4  | Refine  | ment of simple blocks                                          |

|   |      | 4.4.1   | No-channel solution                                            |

|   |      | 4.4.2   | Refinement for latency reduction                               |

|   | 4.5  | Refine  | ment of the DBL SAO                                            |

|   |      | 4.5.1   | First comparison                                               |

|   |      | 4.5.2   | Second comparison                                              |

|   |      | 4.5.3   | Improvements                                                   |

|   |      | 4.5.4   | Flat design comparison                                         |

|   |      | 4.5.5   | Final comparison                                               |

|   | 4.6  | Refine  | ment of the HEVC Controller Block                              |

|   | 4.7  | Proble  | ems                                                            |

|   |      | 4.7.1   | Multiple calling to the top level block in the testbench       |

|   |      | 4.7.2   | Using of the function available inside two nested loops        |

|   |      | 4.7.3   | Bidirectional communication in channel                         |

|   |      | 4.7.4   | Constant values in the size of an array and the slice function |

|   |      | 4.7.5   | Throughput value                                               |

|   |      | 4.7.6   | Two blocks reading from the same memory                        |

|   |      | 4.7.7   | Use of if and else if                                          |

|   |      | 4.7.8   | Reducing area                                                  |

|   |      | 4.7.9   | Synthesis                                                      |

|   |      | 4.7.10  | DirectInput                                                    |

|   |      | 4.7.11  | Shift left operator                                            |

|   |      | 4.7.12  | Loops with non-constant number of iterations                   |

| 5 | Resu |         |                                                                |

|   | 5.1  | •       | e blocks                                                       |

|   | 5.2  | Compl   | lex blocks                                                     |

|   |      | 5.2.1   | DBL SAO                                                        |

|   |      | 5.2.2   | HEVC Controller Block                                          |

| 5 | Con  |         |                                                                |

|   | 6.1  | Advan   | tages                                                          |

|   | 6.2  |         | vantages                                                       |

|   | 6.3  | Final c | conclusion                                                     |

Bibliography\_\_\_\_\_ 77

# List of Figures

| 1.1  | Catapult flow from the input C code to the generated RTL code. $\ .$ .   | 3  |

|------|--------------------------------------------------------------------------|----|

| 2.1  | Parts of an ac_channel                                                   | 9  |

| 2.2  | Dialog of Architecture step in the selection of memories                 | 14 |

| 2.3  | Complete Catapult flow.                                                  | 14 |

| 2.4  | Catapult's steps involved in the RTL generation                          | 15 |

| 2.5  | Window of Catapult where the input files has to be added                 | 16 |

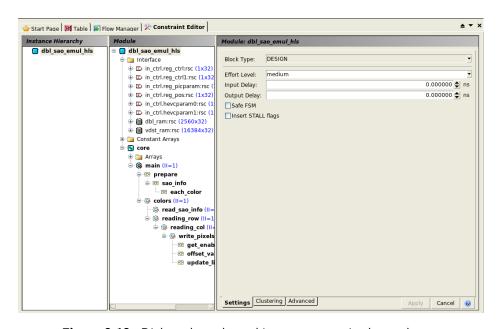

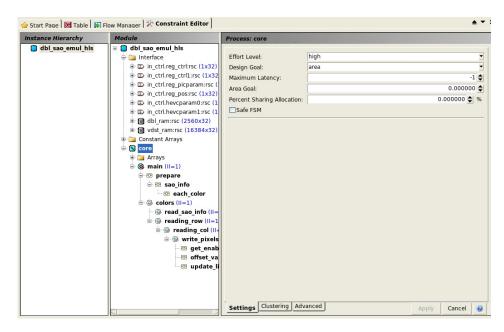

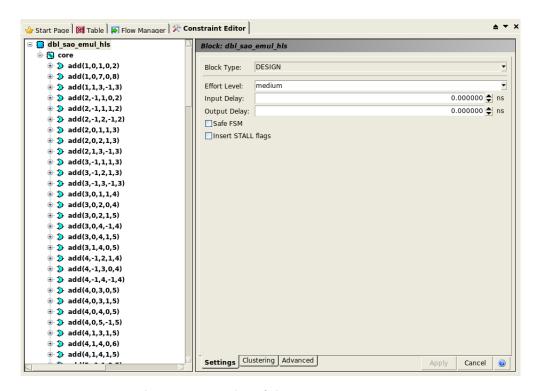

| 2.6  | Hierarchy Constraint Editor dialog of Catapult                           | 17 |

| 2.7  | Dialog of the Library step where the libraries are selected              | 18 |

| 2.8  | Mapping settings: clock frequency, duty cycle, offset                    | 19 |

| 2.9  | Mapping advanced settings: enable and reset signals                      | 19 |

| 2.10 | Mapping dialog in the step of choosing the kind of block: DESIGN         | 19 |

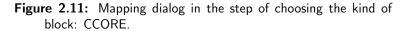

| 2.11 | Mapping dialog in the step of choosing the kind of block: CCORE          | 20 |

| 2.12 | Dialog where the architecture constrains has to be set up, in particular |    |

|      | the module tab                                                           | 21 |

| 2.13 | Architecture step's window in the Interfaces/resources tab               | 22 |

| 2.14 | Architecture step's window in the core tab                               | 23 |

| 2.15 | Architecture step's window in the loop tab                               | 24 |

| 2.16 | Dialog of the Resources step.                                            | 25 |

| 2.17 | Schedule dialog.                                                         | 26 |

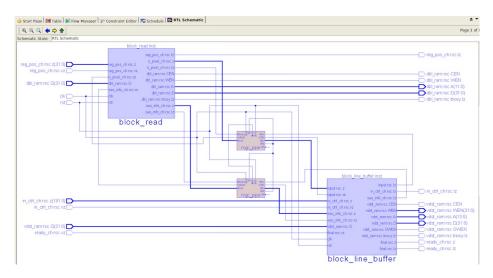

| 2.18 | Schematic view of an RTL                                                 | 27 |

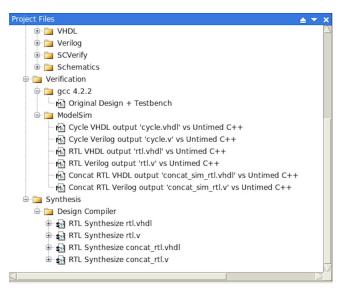

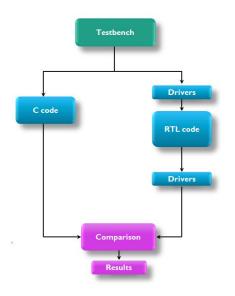

| 2.19 | Verification files for C and RTL simulation                              | 28 |

| 2.20 | Catapult verification process                                            | 29 |

| 2.21 | Catapult library builder window                                          | 33 |

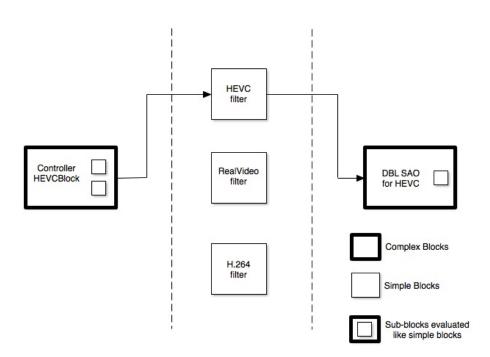

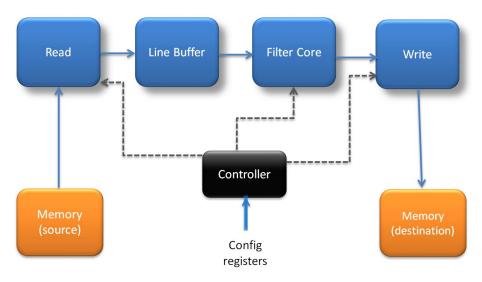

| 3.1  | Schema of the filtering process where are included the studied blocks    | 36 |

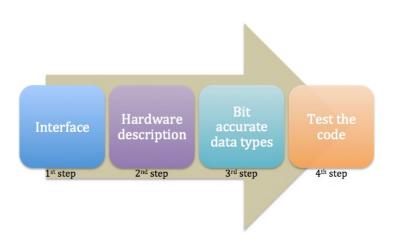

| 4.1  | Steps followed to modify the original C model code into a HLS C code.    | 41 |

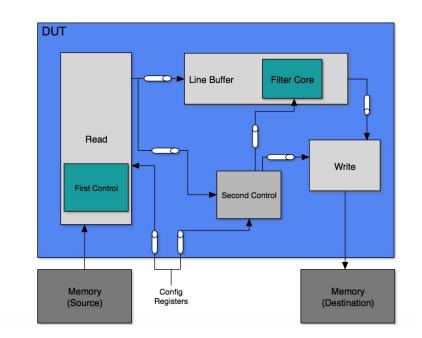

| 4.2  | Schematic view of the DBL SAO architecture.                              | 44 |

| 4.3  | Schematic view of the HEVC controller block developed with 4 sub-        |    |

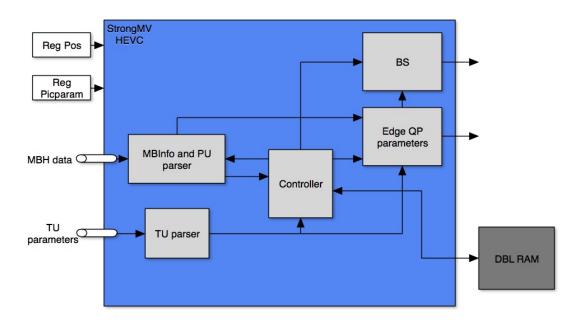

|      | blocks and the controller like the top function                          | 47 |

| 4.4  | Schematic view of the DBL SAO developed like 6 hierarchical blocks       |    |

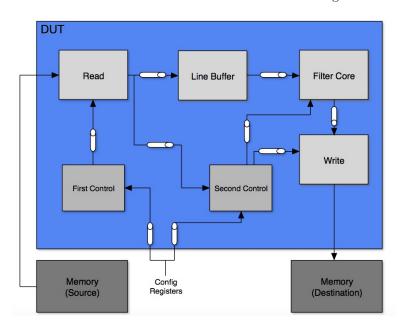

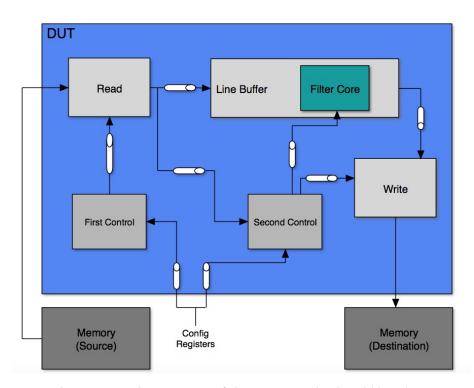

|      | with the communication between them with channels.                       | 51 |

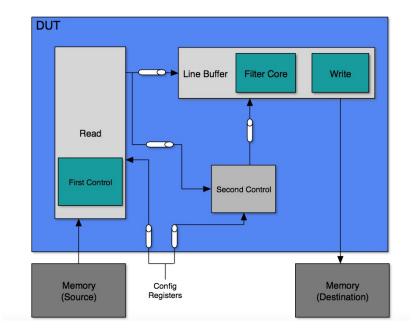

| 4.5  | Schematic view of the DBL SAO developed like 5 hierarchical blocks.      | 54 |

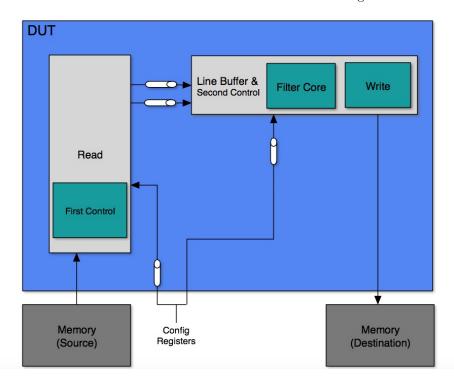

| 4.6<br>4.7<br>4.8 | Schematic view of the DBL SAO developed like 4 hierarchical blocks.<br>Schematic view of the DBL SAO developed like 3 hierarchical blocks.<br>Schematic view of the DBL SAO developed like 2 hierarchical blocks. | 55<br>55<br>56 |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

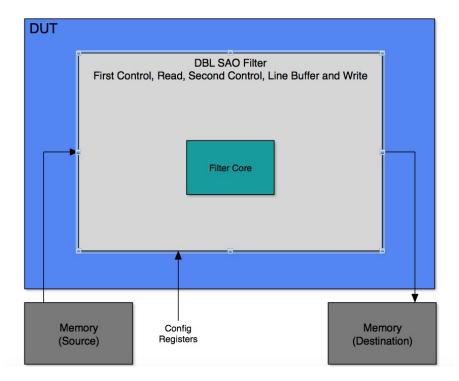

| 4.9               | Schematic view of the DBL SAO developed like a flat design without channels.                                                                                                                                      | 57             |

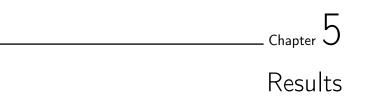

| 5.1               | Graph with the sequential, combinational and total area                                                                                                                                                           | 68             |

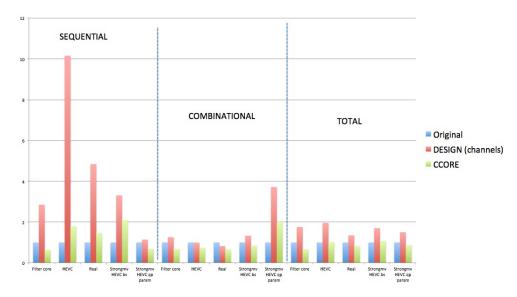

| 5.2               | Graph where the area progress in the DBL SAO block is shown in bars.                                                                                                                                              | 70             |

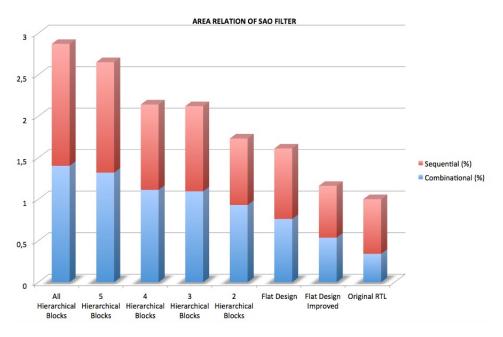

| 5.3               | Graph where the area progress in the HEVC Controller block is shown                                                                                                                                               |                |

|                   | in bars                                                                                                                                                                                                           | 72             |

## List of Tables

| 2.1 | Basic C/C++ data types and corresponding representation in high-<br>level synthesis [3]. | 12 |

|-----|------------------------------------------------------------------------------------------|----|

| 5.1 | Comparison between original RTL design and HLS RTL with the chan-<br>nel implementation  | 67 |

| 5.2 | Comparison between original RTL design and HLS RTL without chan-                         |    |

|     | nels                                                                                     | 68 |

| 5.3 | Progress of the DBL SAO's area from the first design until the flat                      |    |

|     | design                                                                                   | 69 |

| 5.4 | Relation of area in each sub-block                                                       | 71 |

| 5.5 | Progress of the HEVC Controller block area from the first design until                   |    |

|     | the last design                                                                          | 71 |

## Abbreviations

| ASIC       | Application Specific Integrated Circuit |

|------------|-----------------------------------------|

| BS         | Boundary Strength                       |

| DBL        | De-blocking                             |

| FIFO       | First In First Out                      |

| FPGA       | Field Programmable Gate Array           |

| FSM        | Finite State Machine                    |

| HDL        | Hardware Description Level              |

| HEVC       | High Efficiency Video Coding            |

| HLS        | High Level Synthesis                    |

| HLS C code | C code used in HLS tool                 |

| Model C    | C code provided by ARM                  |

| RTL        | Register Transfer Level                 |

| QoR        | Quality of Results                      |

| SAO        | Sample Adaptive Offset                  |

# \_ Chapter 📕

### Introduction

#### 1.1 Background

Back in the early 1990s started the idea of changing the hardware design methods, looking for another programming language that can substitute to the tedious Hardware Description Languages (HDL).

The principal limitation of handwritten Register Transfer Level (RTL) was and continues being the time the designers spend writing code, and because of this, High Level Synthesis (HLS) is becoming more relevant although it has not yet obtained the same results and same quality as the RTL obtained by the hardware designers with HDLs. A detailed description of the hardware in the traditional RTL coding takes long time for the whole process of design, but also it gives more options in terms of timing. By long time we mean that many steps are involved, for example:

- Before coding the RTL, the designer normally creates a reference model, test its behavior to make sure it matches the functionality desired.

- The hardware architecture needs to be developed to write hardware description of the design and check its functionality against the reference to make sure it meets the initial requirements.

Because of this, HLS has emerged as a possible substitution of the RTL description, to shorten the development time of new hardware devices. HLS is a process that transforms an algorithmic description of a desired behavior into a hardware implementation. The input code is analyzed, architecturally constrained and scheduled to generate RTL. This means that the designer can use a higher level functional description, avoiding some hardware details, to get the same design with the same architecture. The HLS flow uses a serie of steps which are allocation, scheduling, binding and RTL generation. Allocation is the step deciding how much resources are needed; scheduling divides the software behavior into the steps that define the finite state machine (FSM); binding maps the variables and instructions to hardware components; and finally the RTL generation creates HDL code that can be synthesized. These steps make debugging of HLS tools complicated. For example a small change in the schedule produces a significant impact on the generated RTL.

HLS techniques have been studied for more than 20 years. The first HLS tools that appeared in the early 1990s took a less detailed HDL and translated it to gate-level circuit description. The use of high level programming languages like C or C++ started later, in the late 1990s [1]. This trend started to grow because of the following reasons:

- The execution of C/C++ codes is faster than HDL, because it contains less details.

- C had a large code base.

- There were more software developers than hardware developers.

However, this idea of HLS has not yet reached the popularity expected at the beginning, even though it seems to have a lot of advantages. One of the advantages that HLS gives to the designers when C or C++ is used as input language, is that they are untimed designs and that make them easier to write. As mentioned, the scheduling step is in charge of making it timed, assigning a small piece of code to each step that can be executed in one single clock cycle. The main advantages of untimed models are:

- Have less detail thus they simplify the test and verification process.

- Can be easily redesigned for different architectures to get other design goals because they are more generic than hardware modules.

- Large number of untimed models have already been designed. Although they can not be synthesized immediately to obtain a high quality RTL, they can be converted with less effort to be suitable for HLS than making a new timed design.

Even though C gives some advantages, being a high level description language requires some hardware aspects to be described to generate a correct RTL with HLS. Examples of these are:

- All the non-software elements has to be described, for example: line buffers and access to memory.

- Variables and signals need to be bit accurate.

- Memory access and patterns should be defined.

- The synchronous communications has to be described.

Despite of this, HLS has not found its place in the industry developing process and has not replaced RTL design yet but on the market the users can find commercial HLS tools like for example:

- Catapult [4].

- Vivado HLS [5].

- Bluespec [6].

- C-to-Silicon [7].

- Cynthesizer [8].

- Synphony C [9].

#### 1.2 Catapult

Catapult is a HLS tool that from C and C++ code generates RTL code.

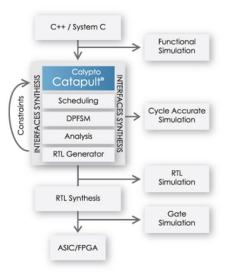

Figure 1.1: Catapult flow from the input C code to the generated RTL code.

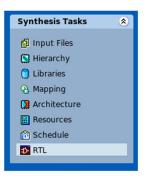

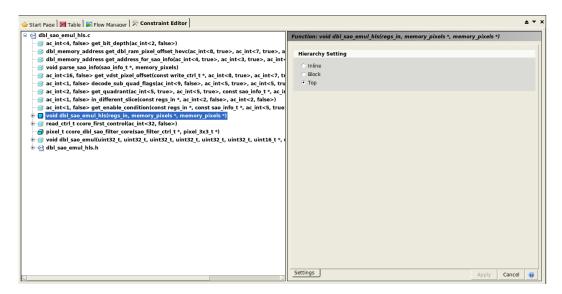

Figure 1.1 describes the Catapult workflow and how it generates RTL from C code. After developing the C code, a testbench can be included in Catapult flow to run a C simulation to check if the behavior implemented is correct. Once this simulation works, the user starts to execute different steps in the tool to set some constraints and configuration parameters (scheduling, DPFSM, analysis...). Once all the steps are done, it generates the RTL and reuses the same testbench as the one used in the C simulation to verify C/RTL consistency.

The comparison between C and the RTL is done in a simulation software, in our case using Questasim. Catapult also includes a synthesis flow to give the user the possibility of generating the scripts for correctly used synthesis tools. Thus Catapult gives the user the possibility to develop functional RTL that can be synthesized for either FPGA or ASIC technology.

#### 1.3 Thesis scope and objectives

This thesis has been developed in ARM's office in Lund in collaboration with the video team. All the hardware and support we have needed has been provided by ARM during this time, and we have also received very useful help from Calypto during the thesis to understand the tool better. Two versions of Catapult have been used during the thesis, starting with 7.2a, but during the development of the thesis we changed to the version 8.0 to solve some issues with the synthesis process.

The main objective of this Master's thesis is to evaluate, Catapult, for the design of video process blocks.

These are the objectives of the work:

- Get started and familiar with a commercial HLS tool.

- Verify the quality of the auto-generated hardware compared with the handwritten RTL, in terms of area, latency and throughput.

- Evaluate if the design process with HLS is easier and faster than traditional hardware design.

- Study the quality of the generated RTL in terms of area, operating frequency, functionality and performance.

- Asses which are the types of designs that are more suitable to obtain better results than hand-made RTL code.

We have accomplished all these objectives by testing different blocks and designs. To make a fair comparison, ARM has provided us with handwritten RTL code for each evaluated block which have been used as a reference to evaluate and compare.

The first step has been to evaluate some simple blocks to learn the different configuration parameters and the limitations of the tool; in other words, to get familiar with the tool. Once this was done, a larger design (SAO filter block), which is compounded by smaller blocks, has been tested in Catapult. Finally, to get more reliable results another "complex" block (HEVC controller block) has been designed. This report describes how to write the input C code for HLS, the main uses of Catapult, and how the development of the small blocks and large blocks have been done through the tool.

#### 1.4 Thesis organization

The thesis is organized as follows:

Chapter 2 describes how HLS code should be written to obtain high quality RTL. Also this chapter explains some of the most useful options and features of Catapult C, as well as the process we have followed to use the tool properly.

Chapter 3 explains the behavior and functionality of the blocks developed in Catapult like the de-blocking HEVC filter, the de-blocking real filter and the SAO filter for HEVC.

Chapter 4 describes the implementation of each of these blocks in HLS, as well as how we have improved the blocks when not obtaining the expected results. The problems we have found and its solutions have been written in this chapter.

The results obtained in the thesis are presented in the chapter 5.

Finally, we discuss future work in this field and the conclusions in chapter 6.

Chapter 2

## HLS design and Catapult flow

Although in HLS the source code is described in C, C++ or System C language, the goal is to create an RTL description. Therefore the C code needs to be written in a different way as a purely behavioral C program. During the development of the input code for the HLS tool, there area some structural hardware constructs that could be skipped in standard C but not in the hardware world [2], for example:

- Non-software modules: such as caches.

- Memory access to write or read from a memory.

- Bit-accurate interfaces and variables.

To use a non-HLS C program in Catapult we have to change the input and output interface, but if the goal is to obtain a high quality RTL, it is necessary to improve also the content, avoiding for example multiple and inefficient access to memories or the use of many static variables. The input code should be written in the most efficient way giving as much details and information as possible.

This chapter will discuss some of the most important coding rules that should be followed and it will also define a small guide of how Catapult works with a description of every steps with its options.

This chapter is divided into the following sections:

- Architecture: this section describes how to write a HLS C code to get high quality RTL, the types for communication between blocks, bit-accurate data types that are included in HLS, and how the memories are implemented in a design.

- Catapult Flow: this part describes how the RTL is generated in Catapult, which are the steps to generate it, how to verify the C code and the RTL and the generation of the netlist with a synthesis tool.

- Catapult Library Builder: the section introduces and explains another tool provided by Catapult characterize a custom standard cell library, a library valid for Catapult and also how to generate a library for a specific memory.

#### 2.1 Architecture

To write the input C code for the HLS tool is necessary to follow some rules to generate high quality RTL. The most important aspect is that a HLS C code will not have the same structure as a normal C program.

The C algorithm should be split in the same way as a hardware design is structured. Each block that appears in the architecture of the hardware design, should appear in the C code. It can appear as a hierarchical block, as a CCORE or even as an inline function. These options will be described later. Each block (big or small blocks) has to be implemented as a function and that function can call other functions. Similar to RTL, HLS must define a top function, which connects the rest of the blocks and describes the interface of the complete design.

The blocks of a design need to communicate. If the blocks are hierarchical blocks, the communication should be done with the type ac\_channel, which will be explained in the section 2.1.1. By hierarchical blocks, we mean blocks that, for example, one of them needs information from other block to get started and it will not start until that information has arrived. The communication between two hierarchical blocks is recommended to be synchronous.

If the communication is done with a block in a lower hierarchical level, the communication can be done in the same way as a standard C code, calling the function of the lower hierarchical block in the upper function. If this is done, a handshake communication will not be implemented between the blocks.

The communication between two hierarchical blocks is done in the top function where the call to both blocks is done, but the communication between one block and for example, an inline function, is done inside the same block, as a function call.

It is very important to make a diagram before starting to code to properly understand which is the top level module of the design (there can only be one) and which are the rest of the blocks that are going to compound the design, what is the functionality of all of them and how the communication between them will be managed. In this case the user does not have to think like a C code developer, the user should think like a hardware designer.

#### 2.1.1 Communication by channels

The ac\_channel is a type used by Catapult to communicate between two hierarchical blocks. The ac\_channel class is essentially a FIFO (First In First Out) that guarantees that reading and writing of data between blocks occurs in the right order. It implements, in RTL, a handshake communication between the blocks and therefore the ac\_channel is the most reliable connection between hierarchical modules. In each hierarchical block, its inputs and its outputs are defined like channels. Inputs coming from the outside can sometimes be defined like "direct inputs" to avoid the input register generation, but if an input is defined like a DirectInput, it is necessary to provide the design with another signal to make the synchronization with the rest of the blocks possible. Also it is not possible to use a channel and a DirectInput in the same block, the block does not get a correct synchronization and the RTL verification fails.

The main problem of the channel is that involves the generation of three signals and a FIFO pipe, which means that the resources used by the design increases. The channel creates a FIFO pipe because the producer can write data in it even though the consumer does not read it. The signals that are involved in a channel interface are:

- The data signal: this signal connects the first block with the FIFO pipe and the FIFO pipe with the second block and it is used for transmitting the data.

- Control signals:

- Ready signal: the sender block is notified that the receiver block is ready to accept and read new data.

- New data signal: the sender block notifies the receiver block that new data has been written in the FIFO.

Figure 2.1 shows the signal implementation of a channel.

Figure 2.1: Parts of an ac channel.

The channel provides hand-shake communication between the blocks and during the RTL generation process the user can select the size of the FIFO pipe. If the user knows that the receiving block is always *ready* to read the data, the FIFO pipe size can be set to 0, so it will never be implemented. In this case, every time the producer writes, the consumer has to read it and the producer can not write more until the consumer reads. If the user does not set any size of the FIFO pipe, Catapult will automatically give them the minimum size to get the design working, but this is not always as efficient as desired. For a better implementation, it is better to define the size if the maximum value is known. Last thing to mention about a channel is that it is not a bidirectional communication, bidirectional communication requires two channels.

The declaration of a channel is done in this way:

#### ac\_channel<type of data> channel\_name.

There is no limitation on the data types that can be used to send through the channel, but if the user wants to send more than one type of data, a struct should be declared with those types and then the struct will be the data to send through the channel.

Furthermore ac\_channel type provides some useful functions to check the availability of the channel before it is read. These functions are just applicable to input channels. The functions provided by ac\_channel are:

• available(): this function gives as a result if there are items available, at least one, in the FIFO pipe in a specific channel. This function should be always called when a channel is read, because read from an empty channel is not allowed in Catapult and will cause a stall. Here is an example of how to use it:

```

if(input_channel.available(1)){

variable = input_channel.read();

...

output_channel.write(data);

}

```

It is also possible to specify how many items you want to be available in the channel before reading them: input\_channel.available(number\_items).

• size(): this function returns the number of items that are stored in the FIFO pipe. It is also useful if the design needs to wait until some amount of data is stored in the pipe. Here is an example of how to use it:

```

if(input_channel.size() == number_items){

variable = input_channel.read();

...

output_channel.write(data);

}

```

The main problem of using channels in the communication between blocks is that channels not only generates all the signals mentioned before, a channel implementation also generates an input register in the receiving block and that means more area in the design.

#### 2.1.2 Bit-accurate data types

C, C++ and System C can be the sources of a HLS code but when the C code is written, it just describes the functionality of the design. The C code in Catapult has to give enough information to be able to synthesize efficient and correct RTL code and for example it must give some information about the number of bits used in the interfaces, signals or in the intermediate variables. For making this possible, apart from the usual libraries of C, Catapult uses libraries that contain data types like ac\_int<> and ac\_fixed<> that allows bit accurate integer and fixed point numbers respectively, both signed and unsigned.

• <u>ac\_int<int width</u>, <u>bool signed></u>: it will generate a signal with the number of bits as defined with "width" and setting the boolean "signed" to false it will be unsigned and vice versa. For example:

> ac\_int<8, false> a; => unsigned variable of W=8 bits. 0<= a <= 2<sup>W</sup> - 1 by increments of 1. ac\_int<32, true> b; => signed variable of W=32 bits. -(2<sup>W-1</sup>)<= b <= 2<sup>W-1</sup> - 1 by increments of 1.

• ac\_fixed<int width, int integer, bool signed>: will generate a signal with the number of bits defined with "width" and the number of integer bits the same as defined in the variable "integer". If signed or unsigned is the same as with the ac\_int. For example:

ac\_int<8, 6, false> c => unsigned variable with 6 integer bits and 2 decimal bits. (W=8, I=6).  $0 \le c \le (1 - 2^{-W})2^{I}$  by increments of  $2^{I-W}$ . ac\_int<32, 24, true> d => signed variable with 24 integer bits and 8 decimal bits. (W=32, I=24)  $-0.5 * 2^{I} \le d \le (0.5 - 2^{-W})2^{I}$  by increments of  $2^{I-W}$ .

Some functions also allows the user to read or write only selected bits of a signal or variable:

• <u>Slice read</u>: slc<width>(int lsb), this function enables the possibility to read selected bits of a signal. The bits that are read are the bits from the less significant bit (lsb) to the bit lsb + width. For example:

```

ac_int<3, false> a =5; (101)

ac_int<2, false> b = a.slc<2>(0); (01)

ac_int<2, false> c = a.slc<2>(1); (10)

```

• <u>Slice write</u>: set\_slc(int lsb, const ac\_int<width,sign>, this function enables the possibility to change the values of selected bits in a signal. The bits that are changed are from the less significant bits to lsb+width with the bits given as a second parameter to the function. For example:

```

ac_int<4, false> a =0; (0000)

ac_int<2, false> b = 3; (11)

a.set_slc(1,b); (0110)

```

Table 2.1 is shows the corresponding representation between the data types of standard C/C++, Catapult, VHDL and Verilog.

| C++ Code                 | Catapult               | VHDL                                   | Verilog    |

|--------------------------|------------------------|----------------------------------------|------------|

|                          | $ac_int<1, false>$     |                                        | reg        |

| bool My_Var              | My_Var                 | STD_LOGIC My_Var                       | My_Var     |

| -char My_Var             |                        |                                        |            |

| -signed char My_Var      | $ac_int < 8, true >$   | STD_LOGIC_VECTOR                       | reg [7:0]  |

| -signed char int My_Var  | My_Var                 | $(7 \text{ downto } 0) \text{ My}_Var$ | My_Var     |

| -unsigned char My_Var    |                        |                                        |            |

| -unsigned char           | $ac_int < 8, false >$  | STD_LOGIC_VECTOR                       | reg [7:0]  |

| int My_Var               | $My_Var$               | $(7 \text{ downto } 0) \text{ My}_Var$ | My_Var     |

| -short My_Var            |                        |                                        |            |

| -signed short My_Var     |                        |                                        |            |

| -signed short int        | $ac_int<16,true>$      | STD_LOGIC_VECTOR                       | reg [15:0] |

| My_Var                   | My_Var                 | (15 downto 0) My_Var                   | My_Var     |

| -unsigned short My_Var   |                        |                                        |            |

| -unsigned short          | $ac_int<16, false>$    | STD_LOGIC_VECTOR                       | reg [15:0] |

| int My_Var               |                        | (15 downto 0) My_Var                   | My_Var     |

| -int My_Var              |                        |                                        |            |

| -signed My_Var           | $ac_int{<}32,true{>}$  | STD_LOGIC_VECTOR                       | reg [31:0] |

| -signed int My_Var       |                        | (31 downto 0) My_Var                   | My_Var     |

| -unsigned My Var         | ac int $<32$ ,false>   | STD_LOGIC_VECTOR                       | reg 31:0   |

| -unsigned int My_Var     | My Var                 | (31 downto 0) My Var                   | My Var     |

| -long My_Var             |                        |                                        |            |

| -signed long My Var      | ac int $<32$ ,true $>$ | STD_LOGIC_VECTOR                       | reg [31:0] |

| -signed long int My_Var  | My Var                 | (31 downto 0) My Var                   | My Var     |

| -unsigned long My_Var    |                        |                                        |            |

| -unsigned long           | $ac_int<32, false>$    | STD_LOGIC_VECTOR                       | reg [31:0] |

| int My_Var               | My_Var                 | (31 downto 0) My_Var                   | My_Var     |

| -long long My_Var        |                        |                                        |            |

| -signed long long My Var |                        |                                        |            |

| -signed long             | ac int $<64$ ,true>    | STD_LOGIC_VECTOR                       | reg [63:0] |

| long int My Var          | My Var                 | (63 downto 0) My Var                   | My_Var     |

| -unsigned long long      | <u> </u>               |                                        |            |

| My_Var                   |                        |                                        |            |

| -unsigned long long int  | $ac_int{<}64, false{}$ | STD_LOGIC_VECTOR                       | reg [63:0] |

| My_Var                   |                        | (63 downto 0) My_Var                   | My_Var     |

| Table 2.1: Basic C/C++ data types and corresponding representation in high-level synthesis [3]. |

|-------------------------------------------------------------------------------------------------|

|                                                                                                 |

#### 2.1.3 Memory implementation

Catapult is also capable to generate memories inside the design or generate memory interfaces to make the blocks able to connect with an external memory that is not

included in the design. It is fundamental to declare or to call the memories in the correct way to obtain the desired architecture in the final design.

Catapult divides the memories in two types depending what is the memory purpose and how the memory is declared in the code:

• Read and write memories declared inside the design: these memories are the ones that are implemented inside the design and the design reads from them and writes to them.

These type of memories appear in the Architecture step that will be explained in the section 2.2.1, and the user can decide if the memories should be externalized or not. Externalize means that the memory is not implemented inside the design and generates interfaces. These memories are declared inside one of the blocks in the design, for example, in the top level block.

• Read or write memories declared outside the design: this kind of memory is never included in the design and is always given to the blocks as pointers. The area is not included in the design, but in the RTL tab (schematic view of the generated RTL) the user is able to see a block, which is the memory, to simplify the understanding of the generated architecture, but it is an "empty" block that does not consume resources.

This type of memory is not declared in the blocks or the top level, they are only declared in the testbench to test the behavior of the design and the most important thing, they are passed to the function in C as pointers. The user can check that they are not included, in the RTL's area score tab, checking the memory area usage to be zero for this kind of memories.

During the Architecture step the user can select which kind of memory to implement, for example single port memory, dual port memory or separate ports for write and read as the Figure 2.2 shows. The user can choose to implement the memory as registers, but this option is just reasonable when it is a small memory. To do this in an efficient way, there is a target to set that defines the maximum size of an array. If the size of an array is less or equal to that number, it will be treated by default as registers.

It is also possible to select the number of bits in the enable signal to allow the user to read or write individual parts of a memory word. For example if the width of a write memory is 32 bits (a word) and the variable num\_byte\_enable, that is shown in Figure 2.2 is set to 4, it means that we are able to write individual bytes (8 bits or more in each write access). In addition, the user can set the input and output delays of the memory.

#### 2.2 Catapult flow

This section will explain the possibilities Catapult gives to the user during its flow. It will describe the different tasks Catapult has to go through to generate

| SRAM_SP_HDE_16384X32M32WM8.SRAM_SP_HDE_16384X32M32WM8 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                              |                                    |

|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------------|

| ions                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                              |                                    |

| bles: 4                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                              | •                                  |

| absolute                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                              |                                    |

|                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                              | 0                                  |

|                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                              | 1                                  |

| ernal Enable                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                              |                                    |

|                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                              |                                    |

|                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.0                          | ns                                 |

| n                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.0                          | ns                                 |

|                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.0 🜩                        | ns                                 |

|                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.0                          | ns                                 |

| 1                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                              |                                    |

|                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.0                          | ns                                 |