Master of Science Thesis

# A 1 MHz Bandwidth, 90 nm CMOS Fractional-N Synthesizer Using Hybrid ΔΣ-DAC-Based Phase Noise Cancellation Technique for LTE FDD/TDD

By

# Dawei Ye

Supervised by Dr. Ping Lu, Lund University

Examined by Prof. Pietro Andreani, Lund University

Department of Electrical and Information Technology

Faculty of Engineering, LTH, Lund University

SE-221 00 Lund, Sweden

## © Dawei Ye 2012

# All Rights Reserved

To my dear aunt and mother

# Abstract

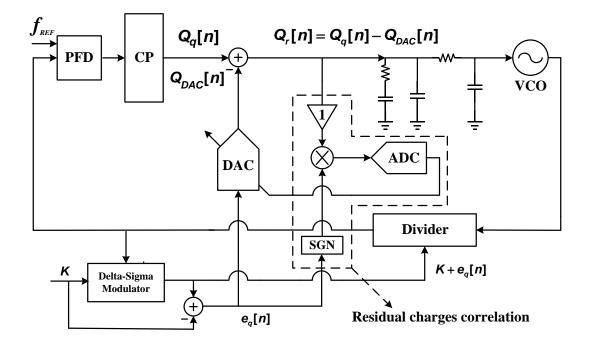

In this project, a 1MHz bandwidth,  $\Delta\Sigma$  fractional-N PLL using phase noise cancellation path is designed as the frequency synthesizer for LTE FDD/TDD, where the phase noise cancellation path is composed of a  $\Delta\Sigma$  DAC with equivalent 9 output bits. Nevertheless, the actual performance of this phase noise cancellation technique is limited by the mismatch, nonlinear distortion and additive noise in the charge pump and  $\Delta\Sigma$  DAC, respectively. Hence some advanced circuit topologies are developed to improve the system performance. At the first, the charges mismatch between the charge pump and current-steering DAC outputs can be decreased by introducing the digital shaped signals which are capable of increasing the overlapped region between their current pulses. Secondly, the timing offset pulses from the retiming circuit are fed to the charge pump in order to avoid the noise folding issue. Finally, a novel hybrid  $\Delta\Sigma$  DAC with fine output resolution is creatively designed in order to reduce its quantization noise which will inject into the PLL when enabling the phase noise cancellation path.

The performance and functionality of the proposed PLL are verified by both the behavioral and transistor-level simulated results. The synthesizer is integrated in a 90 nm CMOS process and the PLL core and I/Q generators consume 14mA and 6.96mA from a 1 V supply, respectively.

# Acknowledgements

Firstly, I would like to thank my daily supervisor Ping Lu for her endless patient helps in my thesis work. She also is the supervisor of my IC project course. Her insight experiences guide me to start my research life for the analog/mixed-signal IC design. Secondly, I want to deeply thank my thesis promoter Prof. Pietro Andreani for giving me freedom to organize and enjoy my research. He also gives me invaluable guidance. His respectable attitude toward the scientific work encourages me to challenge myself in the future work. I would like to thank Prof. Henrik Sjöland. His useful and innovative advices have inspired me in the IC project design. It is my honor to be a student under his supervision.

Finally, I will dedicate this master thesis to my beloved family. Without their unconditional support and encouragement, I could not smoothly continue my master study over the last three years.

Dawei Ye Lund, March 2012

# Contents

| A  | bstract                                      | 4          |

|----|----------------------------------------------|------------|

| A  | cknowledgements                              | 5          |

| C  | ontents                                      | 6          |

| L  | ist of figures                               | 9          |

| Li | ist of tables                                |            |

| 1  | Introduction                                 | 14         |

| 2  | Synthesizer basics for LTE                   | 16         |

|    | 2.1 Frequency synthesizer for LTE FDD/TDD    | 16         |

|    | 2.2 Frequency planning                       |            |

|    | 2.3 Phase noise requirement for LTE          | 19         |

|    | 2.3.1 In-band phase noise                    | 19         |

|    | 2.3.2 Far-out phase noise                    | 21         |

|    | 2.4 Chapter summary                          | 23         |

| 3  | High-level design of the synthesizer         | 24         |

|    | 3.1 Synthesizer based on PLL                 | 24         |

|    | 3.2 Types of wide bandwidth fractional-N PLL | 26         |

|    | 3.3 Issues of wide bandwidth PLL using pl    | hase noise |

|    | cancellation path                            | 28         |

|    | 3.3.1 Error charge mismatch                  | 31         |

|    | 3.3.2 Nonlinear effect in PFD/CP             | 34         |

|   |                                 | 3.3.3                                                           | Additive noise in DAC                                                              | 36                                     |

|---|---------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------|----------------------------------------|

|   | 3.4                             | Propo                                                           | osed wide bandwidth PLL                                                            | 40                                     |

|   |                                 | 3.4.1                                                           | Improvement of error charge mismatch betwee                                        | n the                                  |

|   |                                 |                                                                 | signal and phase noise cancellation path                                           | 41                                     |

|   |                                 | 3.4.2                                                           | PFD/CP linearization technique                                                     | 43                                     |

|   |                                 | 3.4.3                                                           | Proposed architecture for high resolution DAC                                      | 46                                     |

|   | 3.5                             | Simu                                                            | lated results in high-level design                                                 | 51                                     |

|   |                                 | 3.5.1                                                           | Loop filter design                                                                 | 51                                     |

|   |                                 | 3.5.2                                                           | Simulated results for the proposed DAC                                             | 53                                     |

|   |                                 | 3.5.3                                                           | Simulated results for the whole system                                             | 55                                     |

|   | 3.6                             | Chap                                                            | ter summary                                                                        | 59                                     |

|   |                                 |                                                                 |                                                                                    |                                        |

| 4 | Ci                              | rcuit                                                           | details and transistor-level simula                                                | ated                                   |

| 4 |                                 |                                                                 | details and transistor-level simula                                                |                                        |

| 4 | res                             | ults                                                            |                                                                                    | 60                                     |

| 4 | res                             | <b>ults</b><br>VCO                                              |                                                                                    | 60                                     |

| 4 | res                             | <b>ults</b><br>VCO<br>4.1.1                                     |                                                                                    | <b>60</b><br>60<br>61                  |

| 4 | res                             | <b>ults</b><br>VCO<br>4.1.1<br>4.1.2                            | Low power design                                                                   | <b>60</b><br>61<br>61                  |

| 4 | <b>res</b> 4.1                  | <b>ults</b><br>VCO<br>4.1.1<br>4.1.2<br>4.1.3                   | Low power design<br>Low phase noise design                                         | 60<br>61<br>61<br>63                   |

| 4 | <b>res</b> 4.1                  | ults<br>VCO<br>4.1.1<br>4.1.2<br>4.1.3<br>Charg                 | Low power design<br>Low phase noise design<br>Proposed VCO                         | 60<br>61<br>61<br>63<br>67             |

| 4 | <b>res</b><br>4.1<br>4.2<br>4.3 | ults<br>VCO<br>4.1.1<br>4.1.2<br>4.1.3<br>Charg<br>ΔΣ 1         | Low power design<br>Low phase noise design<br>Proposed VCO<br>ge pump              | 60<br>61<br>61<br>63<br>67<br>73       |

| 4 | <b>res</b><br>4.1<br>4.2<br>4.3 | ults<br>VCO<br>4.1.1<br>4.1.2<br>4.1.3<br>Charg<br>ΔΣ 1<br>ΔΣ 1 | Low power design<br>Low phase noise design<br>Proposed VCO<br>ge pump<br>modulator | 60<br>61<br>61<br>63<br>67<br>73<br>76 |

|   | 4.5  | Frequ | ency dividers                              | 84 |

|---|------|-------|--------------------------------------------|----|

|   |      | 4.5.1 | Divide-by-two                              | 84 |

|   |      | 4.5.2 | Divide-by-three                            | 86 |

|   |      | 4.5.3 | Synchronous divider with retiming circuit  | 88 |

|   | 4.6  | Chap  | ter summary                                | 90 |

| 5 | Co   | nclus | ion and future work                        | 92 |

|   | 5.1  | Conc  | lusion                                     | 92 |

|   | 5.2  | Futur | e work                                     | 93 |

|   |      | 5.2.1 | Spurious issue                             | 93 |

|   |      | 5.2.2 | Further suppression for quantization noise | 94 |

|   |      | 5.2.3 | Intrinsic noise                            | 95 |

| R | efer | ences | •••••••••••••••••••••••••••••••••••••••    | 97 |

# List of figures

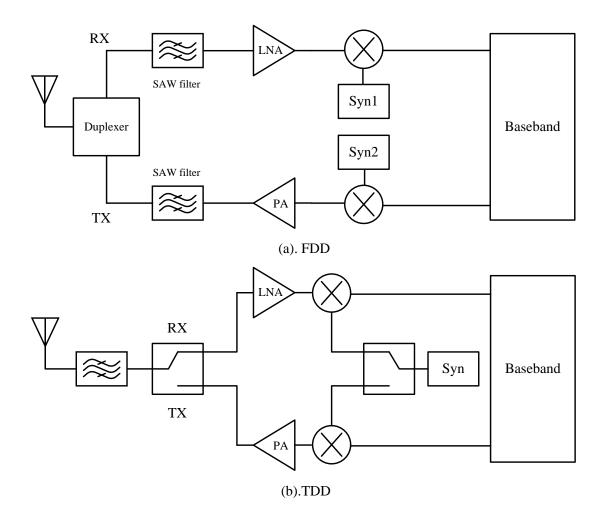

| 2.1  | Transceiver architectures for LTE TDD/FDD17                        |

|------|--------------------------------------------------------------------|

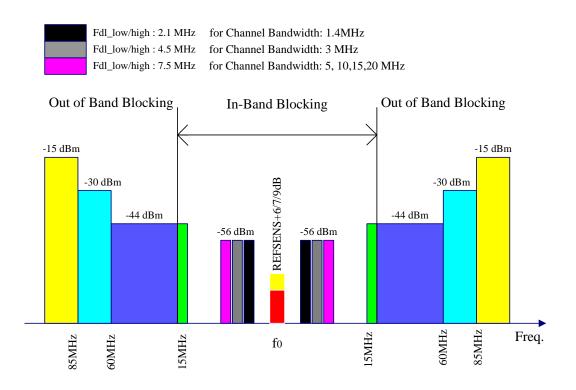

| 2.2  | In-band blocking profile for LTE20                                 |

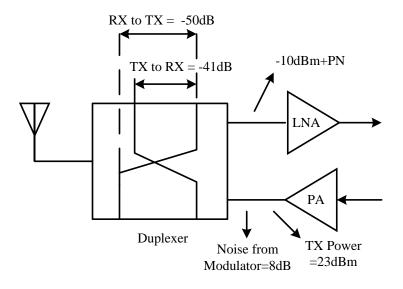

| 2.3  | Principle of TX-to-RX noise leakage in SAW-less FDD                |

|      | transceiver                                                        |

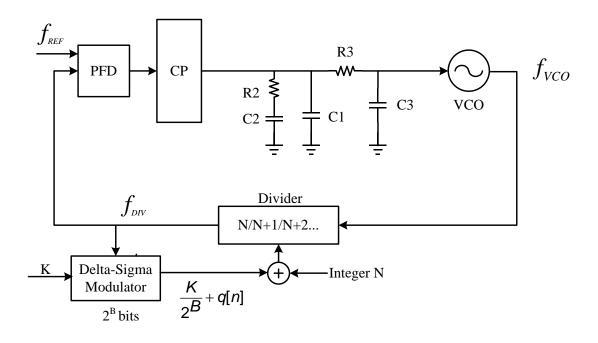

| 3.1  | Classical delta-sigma fractional-N PLL25                           |

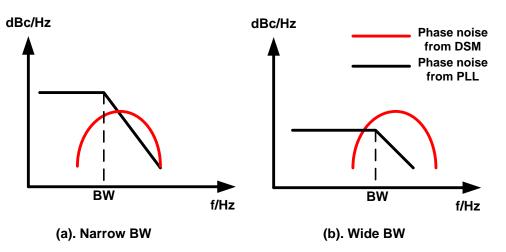

| 3.2  | Influence of BW on phase noise in fractional-N PLL26               |

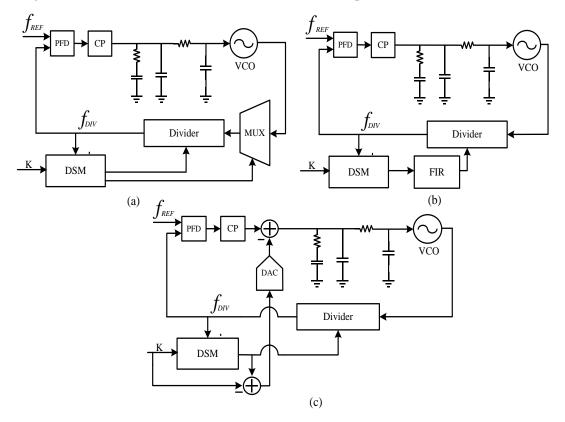

| 3.3  | Architectures for wide BW fractional-N PLL                         |

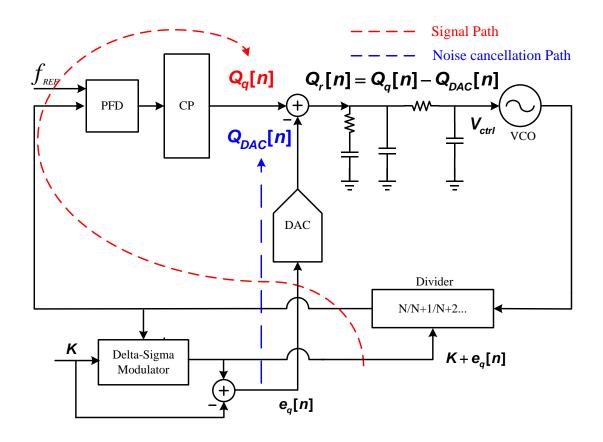

| 3.4  | Issues of wide BW fractional -N PLL using phase noise              |

|      | cancellation path                                                  |

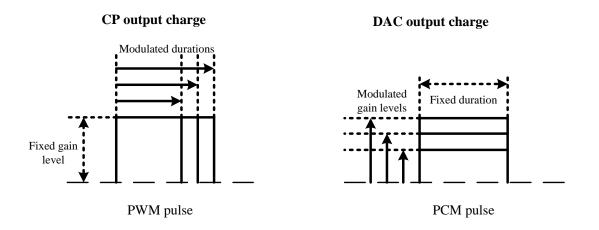

| 3.5  | Output charge shapes of CP and DAC                                 |

| 3.6  | Timing diagram of delta-sigma fractional-N PLL using phase noise   |

|      | cancellation path                                                  |

| 3.7  | PFD/CP nonlinearity                                                |

| 3.8  | Behavioral model to examine the effect of PFD/CP nonlinearity on   |

|      | $\Delta\Sigma$ fractional-N PLL                                    |

| 3.9  | Effect of requantization noise on the phase noise of PLL           |

|      | output                                                             |

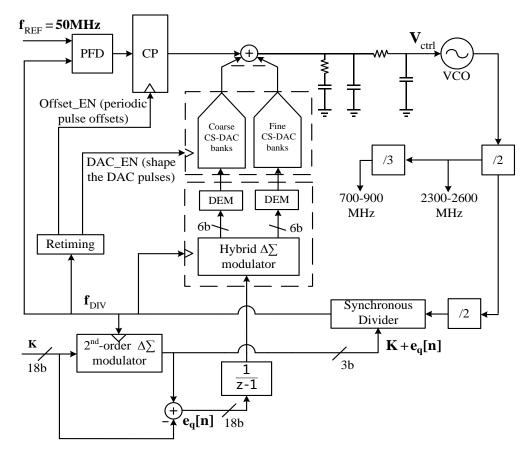

| 3.10 | Proposed wide BW fractional-N frequency synthesizer utilizing      |

|      | hybrid- $\Delta\Sigma$ -DAC for phase noise cancellation40         |

| 3.11 | Effect of DAC pulse duration and overlap area (red regions) on the |

|      | error charge cancellation                                               |

|------|-------------------------------------------------------------------------|

| 3.12 | Effect of offset current on the PFD/CP transfer function44              |

| 3.13 | Effect of fixed offset current on the reference spurious                |

|      | levels                                                                  |

| 3.14 | Proposed PFD/CP with fixed timing offset45                              |

| 3.15 | Segmented $\Delta\Sigma$ DAC with 6 bits modulator output46             |

| 3.16 | Cascaded $\Delta\Sigma$ DAC with more than 6 bits equivalent modulator  |

|      | output47                                                                |

| 3.17 | Proposed hybrid $\Delta\Sigma$ DAC with 9 bits equivalent output50      |

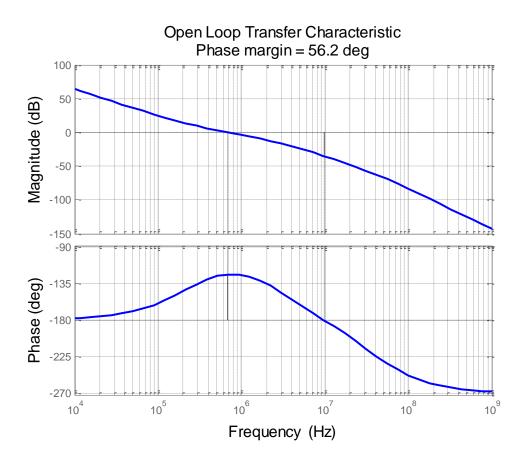

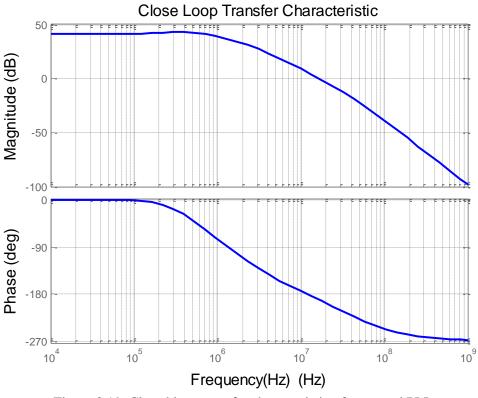

| 3.18 | Open loop transfer characteristic of proposed PLL52                     |

| 3.19 | Closed loop transfer characteristic of proposed PLL53                   |

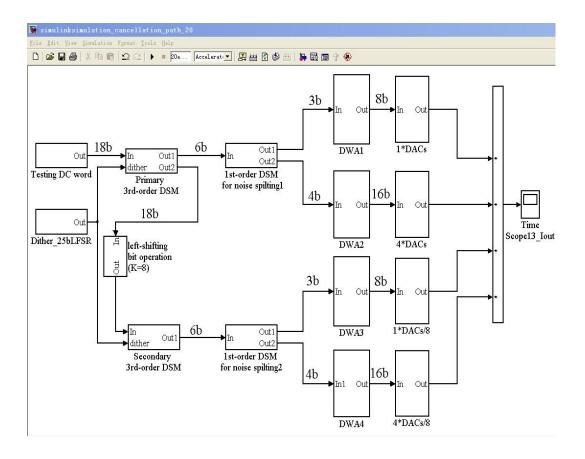

| 3.20 | Behavioral model of proposed $\Delta\Sigma$ DAC built in Simulink54     |

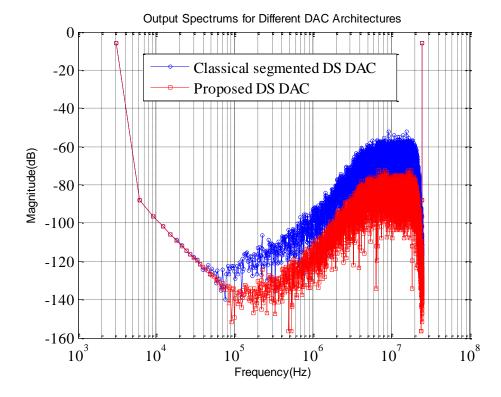

| 3.21 | Output spectrums of behavioral models for different $\Delta\Sigma$ DACs |

|      | (8192 points FFT)                                                       |

| 3.22 | Behavioral model of proposed system built in Simulink56                 |

| 3.23 | PLL transient response                                                  |

| 3.24 | Simulated results for the impact of noise cancellation path on          |

|      | proposed PLL                                                            |

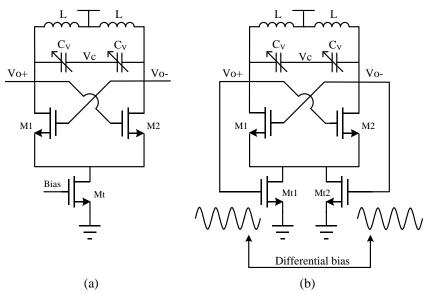

| 4.1  | LC VCO                                                                  |

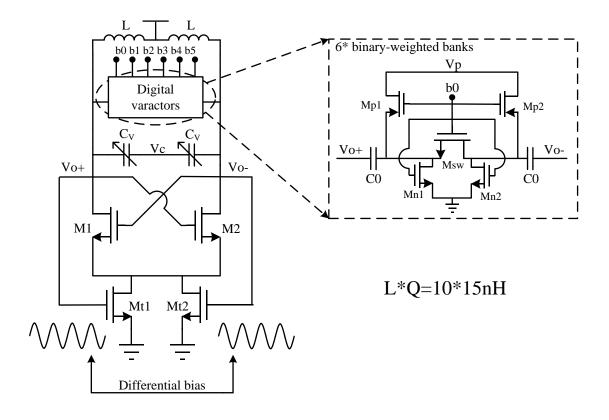

| 4.2  | Proposed LC VCO architecture63                                          |

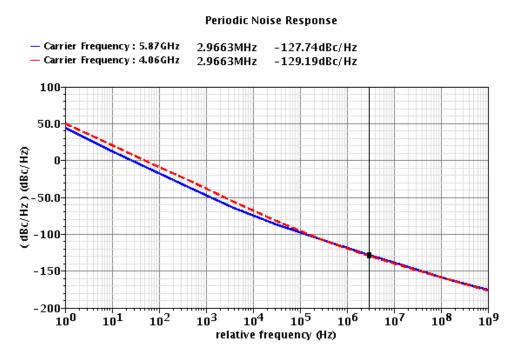

| 4.3  | Transistor-level simulated results for VCO phase noise in the           |

|      | tuning edges of the output frequency64                                  |

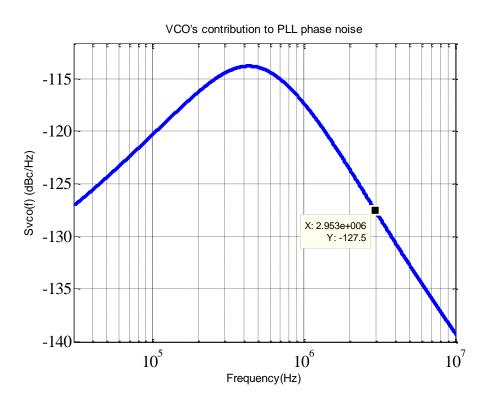

| 4.4  | PLL phase noise contributed by VCO                                 |

|------|--------------------------------------------------------------------|

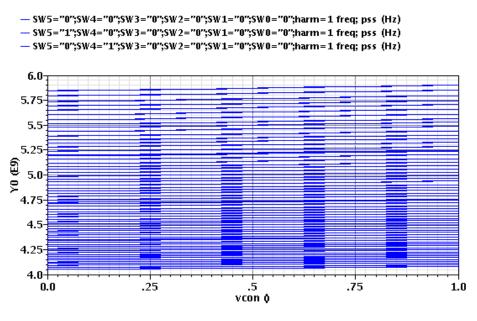

| 4.5  | VCO output frequency VS. Control voltage                           |

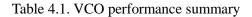

| 4.6  | Non-linear effect of standard CP67                                 |

| 4.7  | Schematic of a conventional current steering CP68                  |

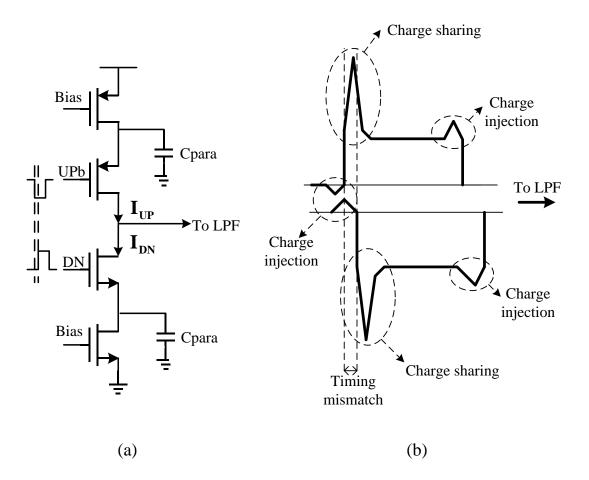

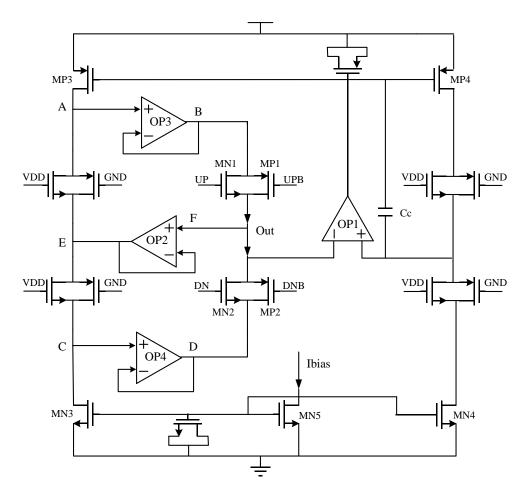

| 4.8  | Schematic of proposed CP70                                         |

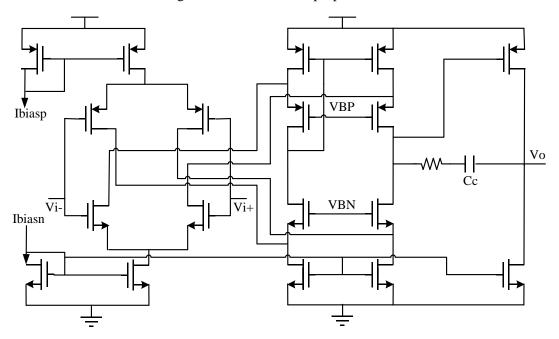

| 4.9  | Schematic of OPAMP with rail-to-rail input stage for the unit gain |

|      | voltage buffers- OP1 and OP2 in the proposed CP70                  |

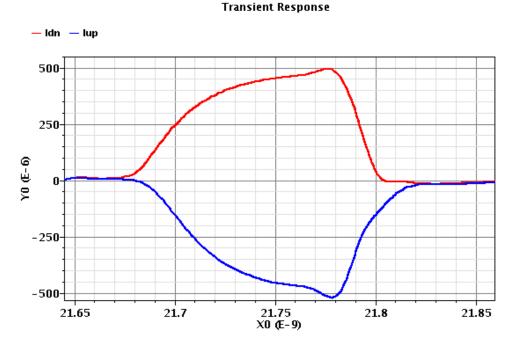

| 4.10 | Simulated result of CP current pulses71                            |

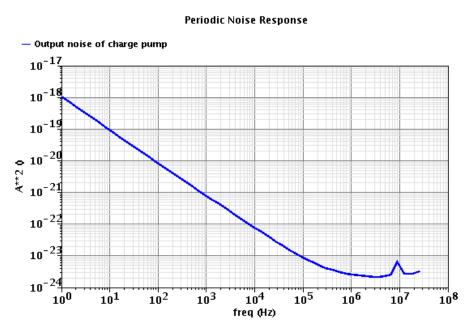

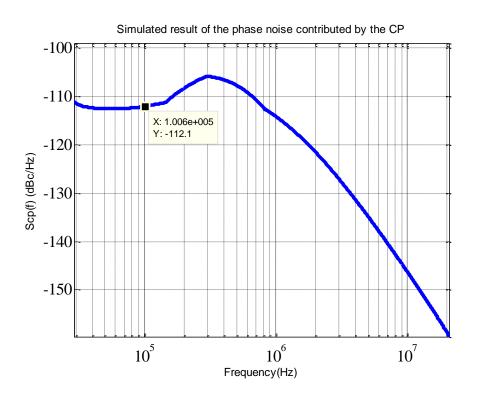

| 4.11 | Simulated result of CP output noise                                |

| 4.12 | PLL phase noise contributed by CP73                                |

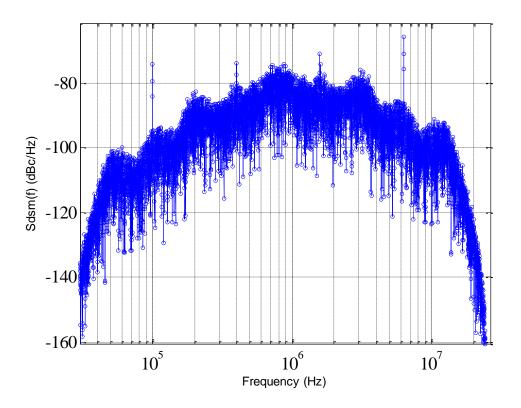

| 4.13 | Proposed $2^{nd}$ -order $\Delta\Sigma$ modulator for PLL          |

| 4.14 | Transistor-level simulated result for the DSM output spectrum of   |

|      | DC input -0.1 (8192 points FFT)74                                  |

| 4.15 | PLL phase noise contributed by DSM75                               |

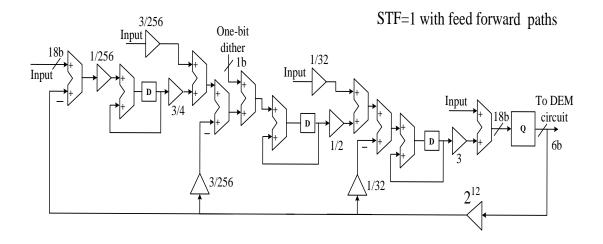

| 4.16 | Proposed 3 <sup>rd</sup> -order modulator with feed forward paths  |

|      | for $\Delta\Sigma$ DAC                                             |

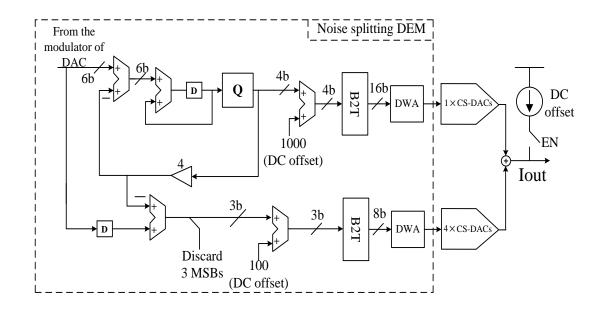

| 4.17 | Schematic of noise splitting DEM77                                 |

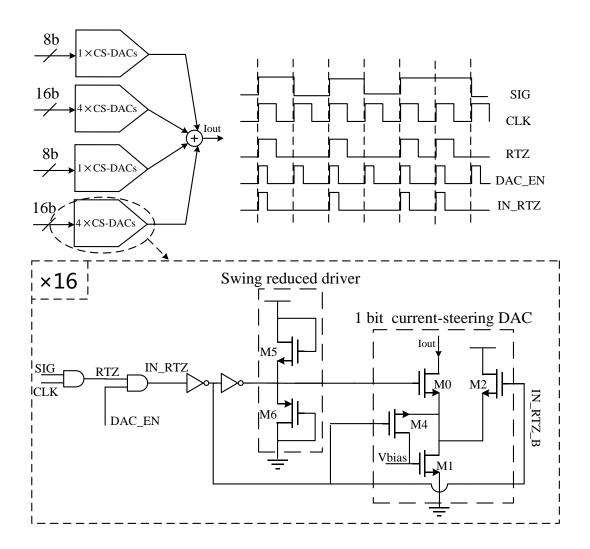

| 4.18 | Schematic of proposed CS-DAC78                                     |

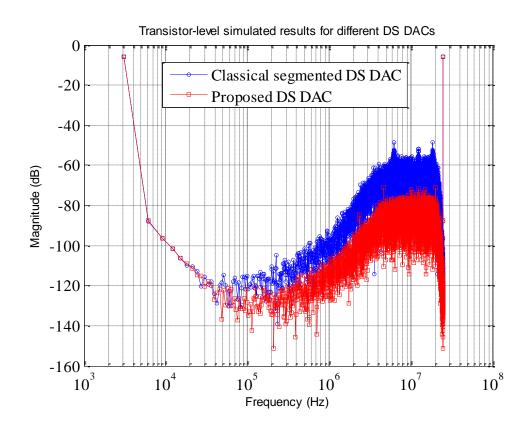

| 4.19 | Transistor-level simulated results of output spectrums for         |

|      | different $\Delta\Sigma$ DACs (8192 points FFT)                    |

| 4.20 | Transistor-simulated results of PLL phase noise contributed by     |

|      | different $\Delta\Sigma$ DACs80                                    |

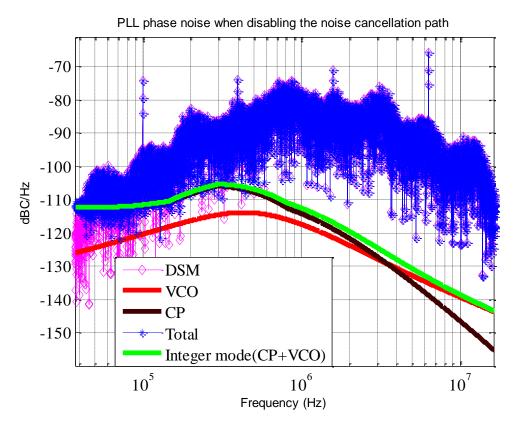

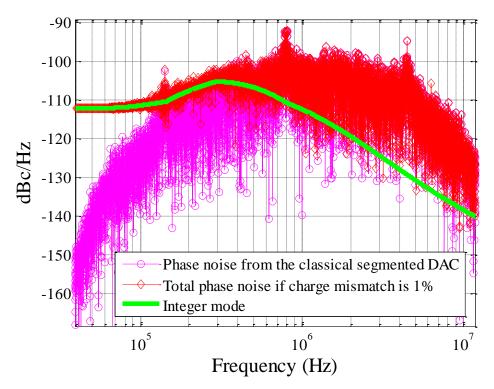

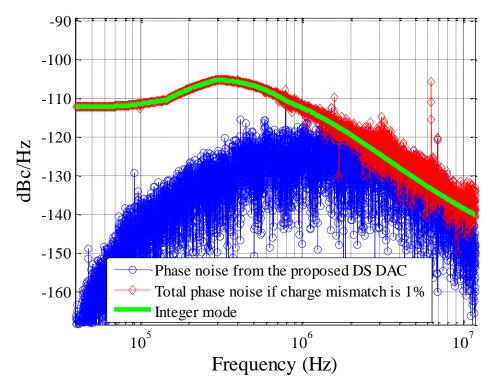

| 2.21 Estimation of PLL phase noise when disabling the noise         |

|---------------------------------------------------------------------|

| cancellation path                                                   |

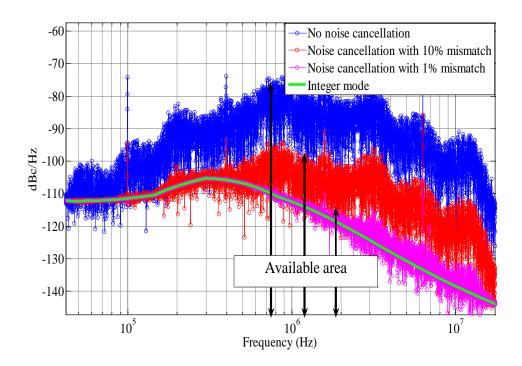

| .22 Available areas of DAC phase noise when the error charge        |

| mismatch between the signal and noise cancellation path is 10%      |

| and 1%, respectively82                                              |

| .23 Impact of the phase noise of classical segmented DAC on the PLL |

| phase noise when the error charge mismatch is assumed to be         |

| 1%83                                                                |

| .24 Impact of the phase noise of proposed DAC on the PLL phase      |

| noise when the error charge mismatch is assumed to be               |

| 1%83                                                                |

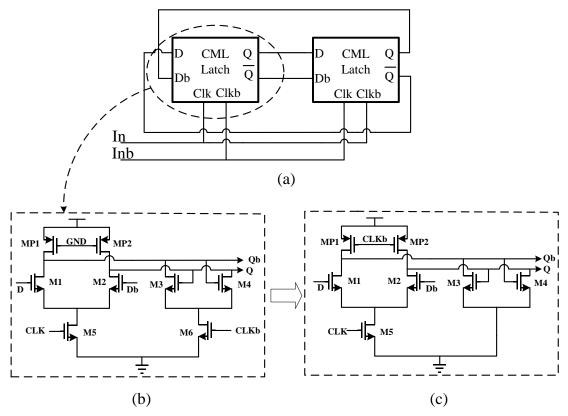

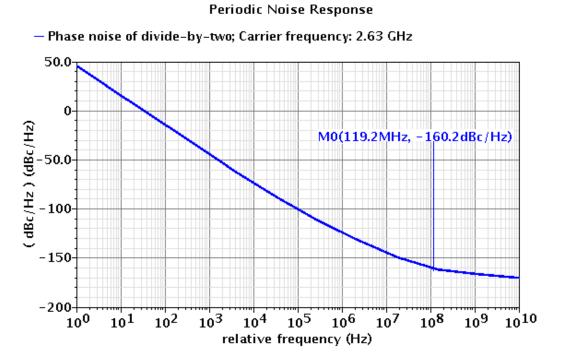

| 25 Divide-by-two frequency divider                                  |

| .26 Phase noise at the output of divide-by-two frequency            |

| divider                                                             |

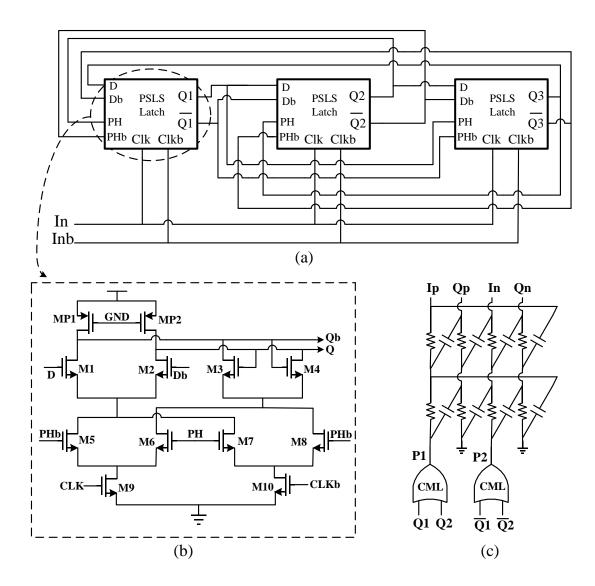

| .27 Divide-by-three frequency divider with 50% duty                 |

| cycle                                                               |

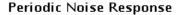

| .28 Phase noise at the output of divide-by-three frequency          |

| divider                                                             |

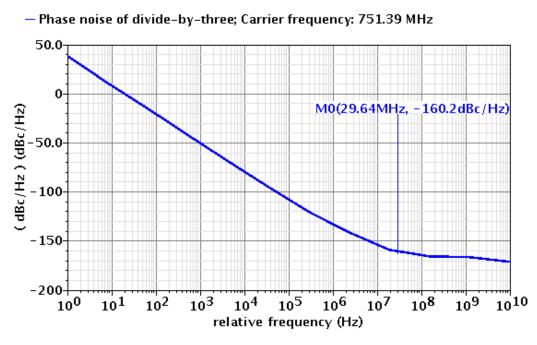

| .29 Proposed synchronous frequency dividers with retiming           |

| circuit                                                             |

| Adaptive phase noise cancellation technique                         |

# List of tables

| 2.1 | Frequency planning in this work18                         |

|-----|-----------------------------------------------------------|

| 4.1 | VCO performance summary67                                 |

| 4.2 | Current consumption of proposed system from a 1V supply91 |

# CHAPTER1

# **1** Introduction

The coming of 4<sup>th</sup> generation wireless communication standards brings up new challenges to the synthesizers design because of its flexible channel bandwidth and multi frequency bands. For instance, In the case of Long Term Evolution (LTE), the selectable channel bandwidth includes 1.4, 3, 5, 10, 15 and 20MHz, while the frequency bands reserved for LTE deployment are allocated from 700 to 2700MHz [1]. In addition, since LTE supports both Time Domain Duplex (TDD) and Frequency Domain Duplex (FDD) techniques, the targeted synthesizers should meet the specific requirements for different LTE divisions. Meanwhile, low power and low noise are the other two aspects which should be concerned in the related design. As a result, a compromise has to be made carefully when focusing on these technical issues in the practical design of the synthesizer for LTE.

The objective of this master work is to develop a high performance frequency synthesizer for LTE applications. Normally, most of the synthesizers are based on the Delta-Sigma (DS) fractional-N Phase-Lock-Loop (PLL) because of its fine frequency resolution, acceptable settling time and good noise performance. However, due to its inherent limitation, traditional DS fractional-N PLL is hard to follow the technical evolution for the newest generation wireless communication standards. Hence some advanced PLL structures with faster settling time and better noise performance were developed in recent years and a novel PLL based on these previous researches will be designed in our project.

The thesis is organized as follows. Chapter 2 introduces the specifications of the frequency synthesizer for LTE systems. Chapter 3 illustrates the main issues and relative solutions in high-level design. The corresponding behavioral

simulated results are also attached in the end. Chapter 4 shows the circuit details in each of the system blocks and their relative transistor-level simulated results. Finally, the conclusion will be made and the future works will be suggested in chapter 5.

# CHAPTER 2

# **2** Synthesizer basics for LTE

### 2.1 Frequency synthesizer for LTE FDD/TDD

There are two LTE divisions -TDD and FDD, each type has its specific RF front end for signal transmission. It therefore means the required synthesizer should be capable of working for both the transceiver architectures (TDD and FDD). Figure 2.1 shows the two transceiver architectures for different LTE divisions. The block diagram in figure 2.1 (a) describes the transceiver for FDD technique. In principle, the RX and TX paths work simultaneously, thus two synthesizers are needed to demodulate the receiving RF signals and modulate transmitting base-band ones at the same time. Furthermore, a duplexer is adopted to separate the RX and TX signals and hence reduce the interference between them. However, due to the limited signal separated ability in the practical duplexer, the noise will leakage from TX to RX at the duplex distance and deteriorates the noise figure in the whole RX. To ease the noise leakage problem, the Surface Acoustic Wave (SAW) filter with wide bandwidth and small gain loss can be inserted before the duplexer in order to suppress the noise at far out frequency offset (duplex distance). However, such an external and costly device is not suitable for the high integration design. Thereby the synthesizers should have better out-of-band phase noise performance in a SAW-less transceiver. Further, figure 2.1 (b) depicts the transceiver architecture for LTE TDD. Since the RX and TX will not wok simultaneously but in different time slots and the signal will be modulated or demodulated at a single frequency band, only one signal transmission path and frequency synthesizer is required for signal synthesis in TDD transceiver. For this to be true, the noise leakage issue in FDD architecture will not appear in the TDD RF front end. Additionally, the settling time of synthesizer should be fast enough so that it is within the guard period for the downlink (uplink) to uplink (downlink) switched activities. Finally, except for the noise and settling time requirements, the minimum frequency resolution of the designed synthesizer should be higher than the channel spacing in the LTE standards.

Figure 2.1 Transceiver architectures for LTE TDD/FDD. In conclusion, the synthesizer designed for LTE should

*A*. cover multi-bands across a wide frequency range for deployment in different countries and regions;

*B.* have good phase noise both at in-band and far-out frequency and meet the requirement of extremely low integrated phase noise;

*C*. enable fast settling time between transmitting and receiving time slots for TDD mode;

*D*. have fine frequency resolution which supports the minimum channel spacing in LTE.

| Modu. | TX/MHz    | RX /MHz   | Relations | Available Channel | Duplex         |

|-------|-----------|-----------|-----------|-------------------|----------------|

| Туре  |           |           | With VCO  | Bandwidth / MHz   | distances/ MHz |

|       | 2500~2570 | 2620~2690 | Fvco/2    | 5, 10, 15, 20     | 120            |

| FDD   | 698~716   | 728~746   | Fvco/6    | 1.4, 3, 5, 10     | 30             |

|       | 777~787   | 746~756   | Fvco/6    | 1.4, 3, 5, 10     | 31             |

|       | 704~716   | 734~746   | Fvco/6    | 1.4, 3, 5, 10     | 30             |

| TDD   | 2570~2620 |           | Fvco/2    | 5,10              |                |

|       | 2300      | ~2400     | Fvco/2    | 5, 10, 15, 20     |                |

### 2.2 Frequency planning

### Table 2.1 Frequency planning in this work.

Since multi frequency bands are reserved for LTE deployment, a good frequency planning is needed to ease the design difficulty. In this case, the synthesizer is applied for the direct conversion transceiver. One problem of such structure is the negative effect, namely Local Oscillator (LO) pulling, which will corrupt the VCO spectrum due to the undesired coupling of the high power level signal at the output of Power Amplifier. To alleviate this effect, the combination of VCO (which works at multiples of the desired frequency band) and frequency dividers can be adopted. This will allow the operating frequency of VCO ( $f_{VCO}$ ) to allocate far away from the desired frequency band (Fvco/2, etc.), thereby mitigate the electromagnetic coupling effect. In addition, this structure also can increase the output frequency range and hence reduce the design difficulty of VCO with wide tuning range. Another problem is the phase noise requirement for the synthesizer. High phase noise of the LO will enhance

the reciprocal mixing which decreases the SNR of the demodulated signal. We will come to some theoretical derivations for the phase noise at different carrier offsets in the next section.

Due to the multi reserved frequency bands for LTE, an increment of difficulty to cover the available frequency range for a worldwide wireless application is inevitable. This requires the targeted synthesizer to works as the one for the multi-standards transceiver. Moreover, some frequency bands, 700MHz and 2600MHz, for instance, are favored to the LTE deployment. This is ascribed to the fact that 2500~2700MHz is a large clear band for potential users whereas band at 700MHz has high penetrating and hence provides wider coverage for rural regions. In the mean time, the supplementary band at 2300 ~ 2400MHz is also included in our planning. Table 2.1 lists the relationship between different frequency bands and outputs of the synthesizer. What's more, the available channel bandwidths at different frequency allocations and the duplex distances for FDD modulation are also listed.

### 2.3 Phase noise requirement for LTE

### 2.3.1 In-band phase noise

Error Vector Magnitude (EVM) is one of the most important parameters to describe the modulated quality of the transmitted signal. If EVM is low enough, the receiver will have a good ability of properly recovering the transmitted signal and hence have a higher quality of signal propagation in larger area due to the lower Bit Error Rate (BER). EVM depends on many nonlinear effects. One of the main contributors for the EVM is the phase noise. Good phase noise performance of the synthesizer is important in a RF system. Currently it can be estimated that the EVM of the overall transmitter system should be less than 3% while the PLL' s contribution to EVM should be less than 2% for 4G communication standards. This requirement means that the integrated phase noise has to be less than 1°. Moreover, the in-band interfering signals, so called blockers, have a high power level (often higher than the desired modulated signal) which will deteriorate the phase noise over the channel bandwidth. Poor

phase noise performance of the LO will cause a serious reciprocal mixing at a direct conversion transceiver and eventually corrupt the receiving quality of the modulated signals.

Figure 2.2 In-band blocking profile for LTE

Figure 2.2 displays the in-band blocking profiles of the LTE standard. To avoid the over deterioration of the demodulated signal, the minimum requirement for the phase noise at different frequency offsets should be meet. The phase noise of LO L [dBc/Hz] is calculated by the following formula:

$$L(\Delta f) \le P_{noise} - P_{bloc\,ker}(\Delta f) - 10\log(BW)$$

(2.1)

and  $P_{noise}$  is given by:

$$P_{noise} = P_{REFSENS} + 6/7/9dBm - SNR$$

(2.2)

where  $P_{REFSENS}$  represents the reference sensitivity (REFSENS) of QPSK modulation, as shown in figure 1.2, SNR is the requiring signal-to-noise ratio

for given BER (here supposes 15 dB SNR corresponding with a  $10^{-7}$  BER in QPSK). What 's more, for the channel bandwidth 1.4, 3, 5 and 10MHz, the desired modulated signal is 6 dB higher than the reference sensitivity, while for 15 and 20MHz, it is 7dB and 9dB above the sensitivity, respectively.

As known in [1], and with (2.1) and (2.2) derived above, the minimum requirement for the in-band (<20MHz) phase noise at different frequency offsets can be therefore calculated. Here we only concern the most stringent specification. It can be proved that the worst case occurs at the band 38 (TDD, 2570 ~2620MHz) with 10MHz channel bandwidth, and the relative results is given as following:

$$L(7.5MHz) = -120dBc / Hz$$

$$L(15MHz) = -132dBc / Hz$$

(2.3)

### 2.3.2 Far-out phase noise

Figure 2.3 Principle of TX-to-RX noise leakage in SAW-less FDD transceiver. In the classical design, the far out phase noise of LO can be neglected since the using of SAW filter can greatly filter out the phase noise beyond the maximum channel bandwidth (20MHz for LTE, etc.) while keeping a small gain loss at the RF frequency. However, to meet the stringent requirement for high integration design, such an external and costly filter is welcome to be removed. This means that the far out phase noise of LO should be concerned carefully for a SAW-less transceiver.

As we described above, the saw filter is used to limit the impact of the transmitter noise on the receiver. If this filter is removed, the practical duplexer in FDD transceiver will result in the noise leakage from the TX to RX at the duplex distances (30MHz for 700MHz bands, etc.). Thereby the poor far-out phase noise of LO will degrade the noise figure of the whole RX. As shown in figure 2.3, at the first, we assume that the total TX power is 23dBm, the additional noise contribution from the Power Amplifier (PA) and modulator is 8dB, and the TX-to-RX attenuation is -41dB, respectively. Then we can know that the noise power density leaking to the input of Low Noise Amplifier (LNA) at the duplex distance (30MHz for 700MHz band, etc.) is

$$23dBm + 8dB - 41dB + PN = -10dBm + PN$$

(2.4)

The industry standard noise reference is defined at 17 deg C, using Boltzmann's constant and in a 1Hz bandwidth, the ideal noise floor is therefore -174dBm/Hz. If we also assume that the noise figure for the whole RX is 4dB. Combining with (2.4), it can be known that,

$$-10dBm + PN = -174dBm / Hz + 4dB$$

$$PN \approx -160dBc / Hz$$

(2.5)

where PN is the required phase noise of LO at the duplex distances. By considering some noise margin for different channel bandwidths and more stringent noise figure for RX, the practical LO phase noise at the duplex distance should be 3~4 dB lower than -160dBc/Hz. On the other hand, such a noise leakage issue will not be concerned when designing the frequency synthesizer for LTE TDD since the TX and RX don't work simultaneously and hence the duplexer is not needed for the TDD transceiver.

### 2.4 Chapter summary

This chapter determines the specifications for the synthesizer in LTE systems. Firstly, the synthesizer should cover a wide frequency range from 698 to 2690MHz. The frequency dividers will be adopted to ease design difficulty of wide tuning range VCO. Further, to determine the phase noise requirement for the synthesizer, the blocking profile based on [1] is used to specify the in-band phase noise while the noise leakage effect from TX to RX dominates the phase noise at far out frequency. Finally, the required synthesizer should be fit for the TDD modulation also, which means its settling time is within the guard period between transmitting and receiving time slots.

# CHAPTER 3

# **3 High-level design of the synthesizer**

### 3.1 Synthesizer based on PLL

The PLL is widely used as the frequency synthesizer because of its fast settling time and fine frequency resolution. In general, the PLL can be classified into two categories – integer and fractional-N PLL. Compared to the integer-N PLL, the  $\Delta\Sigma$  fractional-N PLL [2] is preferred to be used as the synthesizer due to its wider bandwidth (BW) and finer frequency resolution. As shown in figure 2.1, in the fractional-N PLL, the delta-sigma modulator (DSM) is adopted in order to control the divider to toggle its dividing ratio among some random integer numbers (N, N+1, N+2... etc.). The average value of this control sequence is equal to a targeted fractional number, which is given by:

$$f_{DIV} = \frac{f_{VCO}}{N + \frac{K}{2^B} + q[n]}$$

(3.1)

where *K* is the frequency control word, *B* is the bit width of DSM and *N* is the integer ratio for multi-modulus divider. Since the denominator of (3.1) includes fractional part  $-\frac{K}{2^B} + q[n]$ , and the control word K is selectable, a finer frequency resolution can be obtained. Moreover, unlike the integer-N PLL which has to keep a low reference frequency to guarantee a fine frequency resolution, with the advantage of fractional ratio, the reference frequency of fractional-N PLL can be chosen to any high values in principle, thus the PLL bandwidth can be wider until it reaches the limitation for the system stability

$(BW < f_{REF} / 10)$ . However, the main drawback for wide BW fractional-N PLL

is the quantization noise from the DSM. It is well known that the DSM is capable of pushing its in-band quantization noise to high frequency offsets, resulting in lower in-band and higher out-of-band quantization noise. The quantization noise is fed into the PLL and finally converted to the phase noise. To alleviate the impact of quantization noise on the PLL performance, the loop bandwidth has to be narrow enough to ensure that the instantaneous error charge at the Charge Pump (CP) output, which is converted by the quantization noise, can be greatly suppressed before it disturbing the VCO. As shown in figure 3.2. (a), the phase noise contributed by DSM has less impact on the narrow BW PLL and hence good phase noise performance can be obtained at the PLL output. While in figure 3.2 (b), the PLL BW is wider and the phase noise from DSM can not be suppressed effectively, deteriorating the phase noise at the PLL output.

Figure 3.1. Classical delta-sigma fractional-N PLL

Meanwhile, to meet the requirement for LTE, the settling time of the synthesizer should be faster compared to the traditional fractional-N PLL. This means the PLL BW can not be too narrow. While in the classical design, the DSM quantization noise will hinder the increment of the PLL BW. To obtain a wider PLL BW while keeping reasonable phase noise, some advanced

architectures, which are developed based on the classical delta-sigma PLL, will be introduced in the next section.

Figure 3.2 Influence of (a). narrow and (b). wide BW on phase noise in fractional-N PLL

Figure 3.3 Architectures for wide BW fractional-N PLL: (a). Multiphase VCO, (b). FIR (embedded) filtering and (c). DAC cancellation.

### 3.2 Types of wide bandwidth fractional-N PLL

Wide BW PLLs can benefit in some aspects. First of all, fast settling time

enabled by wide PLL BW is important for the efficient signal transmission in wireless communication. Secondly, wide BW can help to reduce the DC gain of loop filter if the Gain Bandwidth Product (GBP) keeps the same (see figure 3.2). This will result in a significant reduction of in-band phase noise and hence ease the design difficulty of high performance PFD/CP and VCO. However, as described before, the phase noise contributed by DSM is the main limitation for wide loop bandwidth in fractional-N PLL. To overcome this issue, several advanced architectures are introduced in the previous researches [3]-[9]. Such architectures can be roughly divided into three categories – multiphase VCO, FIR (embedded) filtering and DAC cancellation, which are shown in figure 3.3, respectively.

Firstly, it is known that the multiphase VCO (which is often implemented by ring oscillators) shown in figure 3.3 (a) can be used to reduce the in-band phase noise [3], [4]. By introducing the multiphase VCO, the "fractional divider" which is made of multi-modulus divider and DSM can provide finer quantization steps, resulting in a great reduction of quantization noise. However, the phase mismatch in the multiphase VCO will increase the level of spurious tones at the output spectrum. The adoption of phase randomization technique can ease the spurious issue to some extent, while the in-band quantization noise will therefore increase as a trade-off.

The block diagram shown in figure 3.3 (b) describes the FIR filtering method to suppress the quantization noise in a wide BW fractional-N PLL. The basic idea of this technique is to insert a digital FIR filter between the DSM and frequency divider so that the high frequency quantization noise of DSM output can be suppressed before it enters the PLL [5]. However, due to the DC gain (which is integer and larger than 1) of the digital FIR filter, the quantization noise will also be amplifying at low frequency range. To avoid the increment of in-band noise when using a digital FIR filter, the FIR-embedded noise filtering method is adopted in [6]. In this approach, the FIR algorithm is embedded into the fractional-N PLL sophisticatedly so that the quantization noise both in-band and out-of-band can be suppressed at the cost of power consumption and complexity. As a result, when the FIR algorithm is implemented in the analog domain, the DC gain equal to 1 in the FIR topology is possible to be realized.

As we know, the output sequence of DSM is actually predictable and high-pass shaped. The error sequence q(n) in (3.1) is therefore possible to be deleted before it disturbs the VCO. The third approach to widen the loop BW is refer to as the phase noise cancellation utilizing a feed forward path to delete the quantization error charges [7]-[9]. As shown in figure 3.3 (c), the quantization error is extracted by subtracting the DSM output from its input at the first, then we have it pass through the Digital-to-Analog-Converter (DAC) in order to convert it to the error charge in analog domain. Since the digital error sequence is predictable, its corresponding error charges after the DAC are correlated with the PFD/CP output. If the signal path (which is defined as the route from DSM to the loop filter) and the phase noise cancellation path are ideally matched, the instantaneous error charges due to the quantization noise can be eliminated completely. However, in the practical design, the main drawback for this approach is the mismatch between the signal and cancellation paths. In the mean time, the nonlinear effect in each of the two paths, such as the nonlinearity in PFD/CP and additive noise arising from the DAC itself, will also undermine the phase noise performance of the whole system.

In conclusion, each of these methods for wide BW fractional-N PLL has their own pros and cons. In our design, the topology using a DAC for noise cancellation will be adopted and developed. Some novel ideas and designed details will be introduced in the following sections.

# 3.3 Issues of wide bandwidth PLL using phase noise cancellation path

The details of wide BW fractional-N PLL using phase noise cancellation is described in figure 3.4. As we see, the DSM output including the quantization error  $e_q[n]$  and DC component K is going to change to the instantaneous error charge  $Q_q[n]$  when it arrives at the loop filter though the signal path (red dashed line). On the other hand, by introducing the noise cancellation path

(blue dashed line),  $e_q[n]$  is extracted individually and converted to the charges  $Q_{DAC}[n]$  by the high performance DAC. Then the charges  $Q_q[n]$  and  $Q_{DAC}[n]$  are about to make a subtraction before they pass trough the loop filter. If the matching between the two paths is perfect, nothing will be left to disturb the VCO, otherwise the residual charge  $Q_r[n]$  will degrade the phase noise performance to a certain extent.

Figure 3.4 Issues of wide BW fractional -N PLL using phase noise cancellation path. Now let us come to more details about the mechanism of phase noise cancellation. Based on the mathematical models developed in [10], we can know that the error charge  $Q_q[n]$  is given by:

$$Q_{q}[n] = I_{CP} T_{VCO} \sum_{k=n_{0}}^{n-1} e_{q}(k)$$

(3.2)

where  $T_{VCO}$  is the nominal period of VCO output and  $I_{CP}$  is the nominal output

level of CP. Furthermore, the charge  $Q_{DAC}[n]$  from the cancellation path is written as:

$$Q_{DAC}[n] = I_{DAC} T_{DAC} \sum_{k=n_0}^{n-1} e_q(k)$$

(3.3)

Likewise,  $I_{DAC}$  is the nominal gain level of the output pulse of the Current Steering (CS) DAC while  $T_{DAC}$  is the relative nominal duration. Obviously, to ensure that  $Q_r[n]$  is zero, we must have

$$Q_q[n] = Q_{DAC}[n]$$

$$I_{CP}T_{VCO} = I_{DAC}T_{DAC}$$

(3.4)

Equation (3.4) shows us a simple principle to cancel the quantization noise. However, in the practical design, the mismatch between the two paths is inevitable so that a portion of residual charges will always be added to the loop filter and cause phase noise. The  $Q_r[n]$  can be expressed as:

$$Q_r = Q_q - Q_{DAC} = \alpha I_{CP} T_{VCO} \sum_{k=n_0}^{n-1} e_q(k)$$

(3.5)

where  $\alpha$  is defined as the mismatch factor between the two paths. Practically, due to the nature of different modulation types in PFD/CP and CS-DAC, completed cancellation is impossible to be achieved. Further, other issues due to the nonlinear effects in the real circuits will also contribute to the phase noise. In general, such problems encountered in the phase noise cancellation technique can be classified into three aspects:

A. Error charge mismatch between the signal and noise cancellation path;

### B. Nonlinearity in PFD/CP;

C. Additive noise in DAC.

Each of these problems will be analyzed respectively in the following sections.

### 3.3.1 Error charge mismatch

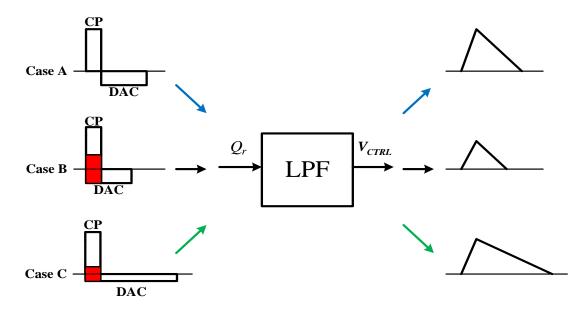

Figure 3.5 Output charge shapes of CP and DAC

In equation (3.4), we can find that the instantaneous error charge from DSM can be eliminated if the signal and cancellation path are perfectly matched. However, such condition is difficult to meet due to the fact that the two paths have different modulated characteristics for Digital-to-Analog (D/A) signal conversion.

Figure 3.5 describes the modulation types of CS-DAC and PFD/CP, respectively. As we see, the output charge of CP can be regarded as the Pulse-Width-Modulation (PWM) pulses which have fixed gain level and modulated durations. While for the CS-DACs, its output charge have fixed modulated gain levels which regarded duration and are the as Pulse-Code-Modulation (PCM) pulses. The output pulses with different modulation types determine that even if we suppose the charges of the two paths are equal in total (neglect the additive noise and nonlinear effect from the paths themselves), the residual charge  $Q_r[n]$  will still be left to a certain extent and hence deposit on the loop filter, causing the undesired instantaneous phase errors.

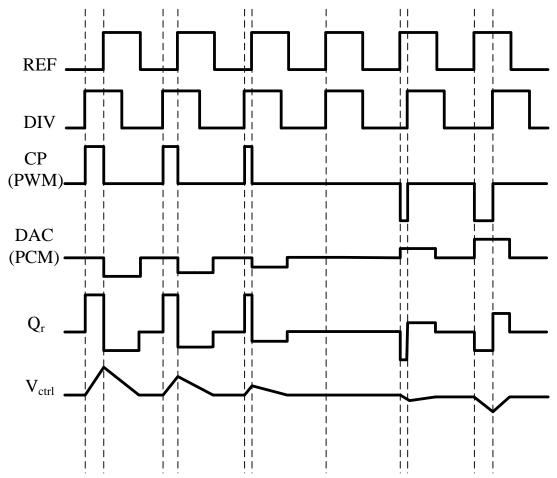

The timing diagram shown in figure 3.6 illustrates this imperfect cancellation mechanism. Obviously, due to the problems of phase and modulation type, the error charge of CP can not be eliminated immediately when it is subtracted by

the DAC output. Hence the instantaneous residual charge  $Q_r[n]$  is not equal to zero even though the total charges of each paths are supposed to be the same. Some spurs converted by  $Q_r[n]$  are therefore added to the control voltage  $V_{ctrl}$ , leading to an increment of the instantaneous phase errors at the PLL output and causing phase noise. In the previous researches [8], [9], the main idea to improve the cancellation is to develop sophisticated circuits to shape the charge pulses for both CP and DAC at the expense of system complexity. Whereas in our design, in order to mitigate this mismatch while keeping reasonable complexity, a simpler idea presented in [11] will be adopted and introduced in section 3.4.1.

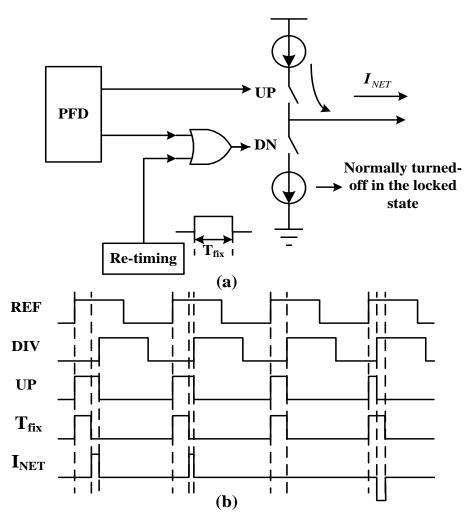

Figure 3.6. Timing diagram of delta sigma fractional-N PLL using phase noise cancellation path

Then, by understanding the noise cancellation mechanism, we can analyze the phase noise contributed by  $Q_r[n]$  mathematically. First of all, it is well known that the phase noise contributed by the quantization noise in the conventional

$\Delta\Sigma$  fractional-N PLL [10] is given by:

$$S_{DS}(j2\pi f) = \frac{\pi^2}{3f_{REF}} \left| 2\sin(\frac{\pi f}{f_{REF}}) \right|^{2(k-1)} \times \left| H(j2\pi f) \right|^2$$

(3.6)

Where k represents the order of DSM, f is the frequency offset relative to the PLL carrier frequency and  $H(j2\pi f)$  is PLL closed-loop transfer function. In our design, a third order passive loop filter shown in figure 3.1 is adopted, thus H(s) can be written as:

$$H(s) = \frac{NA(s)}{1 + A(s)} \tag{3.7}$$

where A(s) is the PLL open-loop transfer function, which can be expressed as:

$$A(s) = \frac{K_V K_{CP}}{Ns} \bullet \frac{(1 + sT2)T1}{(sC1(1 + sT1)(1 + sT3)T2)}$$

$$T1 = \frac{R2C1C2}{C1 + C2}$$

$$T2 = C2R2 \qquad K_{CP} = \frac{I_{CP}}{2\pi}$$

$$T3 = C3R3 \qquad K_V = VCO \ gain$$

(3.8)

Moreover, based on (3.5) and (3.6), if the DAC and PFD/CP are supposed to be ideal, the phase noise contributed by the DSM after the noise cancellation is shown in (3.9):

$$S_{Q_r}(j2\pi f) = \alpha^2 \frac{\pi^2}{3f_{REF}} \left| 2\sin(\frac{\pi f}{f_{REF}}) \right|^{2(k-1)} \times \left| H(j2\pi f) \right|^2$$

(3.9)

where  $\alpha$  is the mismatch factor introduced by (3.5). Equation (3.9) illustrates how the residual charges after the noise cancellation affect the phase noise performance at the PLL output. For instance, if  $\alpha = 0$ , the signal and cancellation path is matched perfectly. If  $\alpha = 1$ , equation (3.9) reduces to (3.7) which is used for the conventional  $\Delta\Sigma$  fractional-N PLL and thus the noise cancellation path has no impact on the PLL performance.

### 3.3.2 Nonlinear effect in PFD/CP

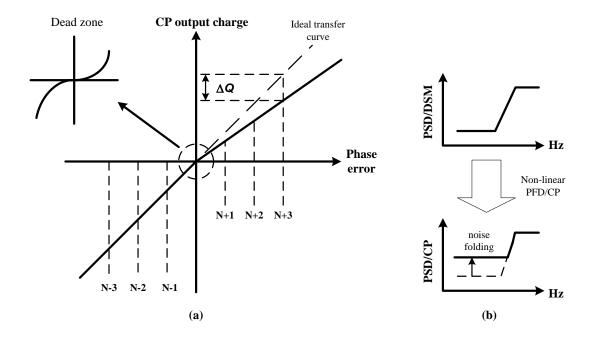

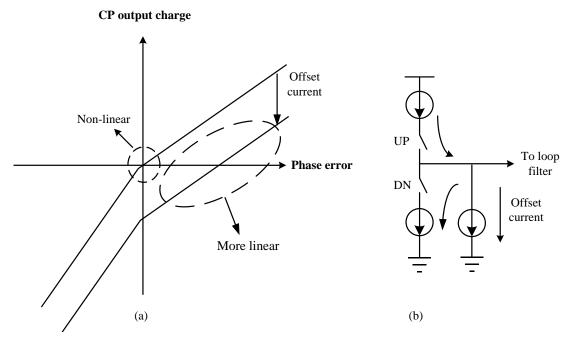

Figure 3.7 PFD/CP nonlinearity: (a). Sources of PFD/CP nonlinearity; (b). high frequency noise folding effect on PSD.

The PFD/CP-related nonlinearity and its influence on phase noise are depicted in figure 3.7. Figure 3.7 (a) shows the phase-error-to-CP-charge transfer function. Apparently, there are two reasons leading to the transfer nonlinearity. One is the dead zone resulted from the minimum settling time for the practical transistors. In order to reduce the dead zone range, some delays are usually added to guarantee that the designed devices have enough time to settle at the expense of an increment of the CP on-time. What's more, it is also known that the CP noise will inject into the loop filter when it is in the on state. Longer on-time means more CP noise will contribute to the PLL output. Therefore a compromise between the CP on-time and dead zone range should be made carefully. The other one is the current mismatch in the CP up and down currents. As we know, for the frequency divider in an integer-N PLL, the dividing ratio will be fixed to a specific value when it is in the locked state and hence the system mainly suffer the dead zone issue while the current mismatch only affects the level of reference spur at the PLL output. However, the mechanism in locked state is quite different when it comes to the  $\Delta\Sigma$ fractional-N PLL whose multi-modulus divider dynamically toggles its dividing ratio to gain the required fractional value. Thereby the nonlinear transfer curve due to the CP up/down current mismatch will result in an error charge  $\Delta Q$  (as shown in figure 3.7 (a)), causing the negative effect of folding high frequency noise back to lower frequency [5], which is depicted in figure 3.7 (b).

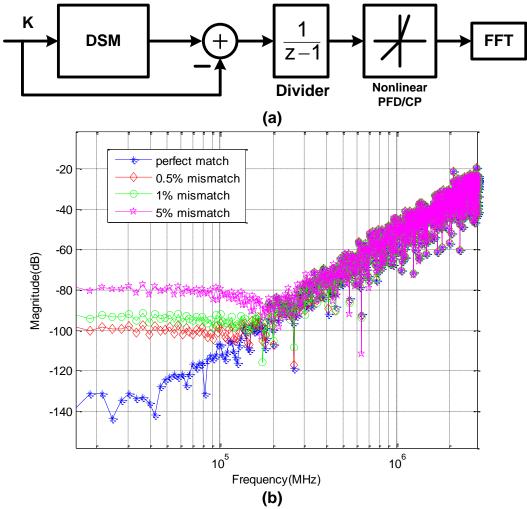

Figure 3.8 Behavioral model to examine the effect of PFD/CP nonlinearity on  $\Delta\Sigma$  fractional-N PLL: (a). Schematic; (b). Simulated results.

To further understand the noise folding effect which is attributed to the PFD/CP nonlinearity, a mathematical model presented in [12], [13] is built in Simulink and used to study this intrinsic characteristic. Firstly, functional

diagram shown in figure 3.8 (a) is constructed. The DSM output is subtracted by its input in order to remove the DC component K, and then we have the quantization error  $e_q[n]$  passing through the multi modulus divider which can be modeled as an integrator in the Z-domain [10]. Meanwhile, by referring to the figure 3.7, we find that the up/down current mismatch can be regarded as the gain (slope) variation in the nonlinear transfer function. By using this behavioral model, the relative results with 0, 0.5%, 1% and 5% current mismatches are shown in figure 3.8 (b), respectively. It is evident that when the current mismatch is increased, more high frequency noise will fold back into the lower frequency range, resulting in a great increment of the in-band noise. Therefore the PFD/CP nonlinearity is needed to be alleviated by some developed methods which will be introduced in section 3.4.2.

### 3.3.3 Additive noise in DAC

As shown in figure 3.4, the DAC in the noise cancellation path is used to convert the quantization error  $e_q[n]$  to  $Q_{DAC}[n]$  in order to cancel the instantaneous error charge  $Q_{CP}[n]$  at the charge pump output. If the DAC is ideal,  $e_q[n]$  can be converted perfectly and the only thing we should concern is the error charge mismatch due to the different modulation types which has been illustrated earlier. Otherwise some additive noise will inject into the loop filter accompanied with the imperfect D/A conversion. Actually such additive noise, which is mainly attributed to the DAC gain error, distortion and insufficient dynamic range, is inevitable in the practical system. So how to improve the DAC performance is the main target in this work.

As we know, to overcome the mismatches between the binary-weighted current banks of DAC, the Dynamic-Elements-Matching (DEM) algorithm combined with the thermometer-weighted current banks is preferred to be adopted. This means that for an N-bit input word, the required number of thermometer-weighted current banks will be up to 2<sup>N</sup>. On the other hand, it is also known that to gain finer frequency resolution at the PLL output, the bit

width of the DSM should be wide enough (18 bits in our case, etc.) and hence the error sequence  $e_q[n]$  has to require more current banks (2<sup>18</sup> unit current banks, etc.) and complicated DEM circuit to process. However, due to the transistor size scaling, complexity and power limitations, the design of the DEM circuit and thermometer-weighted current units is actually impractical when the DAC input has more than 6 bits [14]. To break up the dilemma between the wide input bit width and system complexity, a digital DSM, which is defined as the requantized modulator in this work, can be used to sequence truncate/requantize the and then push error  $e_a[n]$ the truncation/quantization noise to higher frequency. However, such typical high-pass shaped quantization noise will also inject into the loop filter and hence undermine the phase noise performance. As a result, how to improve the resolution of the  $\Delta\Sigma$  DAC and reduce its quantization noise becomes our main issue when designing the noise cancellation path. In the following, we will further study the phase noise contributed by the requantized modulator.

Firstly, the requantized error is defined as  $e_{rq}[n]$  in this work. If  $e_{rq}[n]$  is supposed to be uniformly distributed from  $-0.5\Delta_{RQ}$  to  $0.5\Delta_{RQ}$ , and has a variance of  $\Delta_{RQ}^2/12$  where  $\Delta_{RQ}$  is the minimum quantization step of the requantized modulator, the phase noise contributed by the requantization noise can be given by:

$$S_{RQ}(j2\pi f) \approx \frac{\Delta_{RQ}^2 \pi^2}{3f_{REF}} \left| 2\sin(\frac{\pi f}{f_{REF}}) \right|^{2(L-1)} \times \left| H(j2\pi f) \right|^2$$

(3.10)

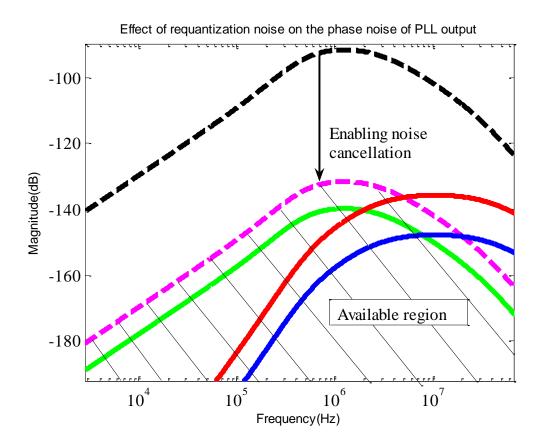

where *L* is the order of the  $\Delta\Sigma$  modulator. Equation (3.10) shows us that the  $\Delta_{RQ}$  and *L* determine the phase noise contributed by the requantized modulator. Hence it is essential that the *L*-order  $\Delta\Sigma$  modulator should have enough output levels to reduce the minimum quantization step since  $\Delta_{RQ} = 1/$ output levels. Reference [15] has proved that the requantization noise has less impact on the PLL phase noise performance if the order L is equal to K or K+1 (where K is the order of DSM in the PLL) and output bits of requantized modulator are more than 8. The reasons for choosing such order and output levels of requantized modulator can be explained by figure 3.9.

Figure 3.9 Effect of requantization noise on the phase noise of PLL output: (a). The phase noise contributed by the PLL DSM (second-order, 3 output bits) before the noise cancellation

(black dashed line); (b). The phase noise contributed by the PLL DSM after noise cancellation with 1% error charge mismatch (magenta dashed line); (c). The phase noise contributed by the second-order, 8 output bits requantized modulator (green solid line); (d). The phase noise contributed by the third-order, 6 output bits requantized modulator (red solid line); (e). The phase noise contributed by the third-order, 8 output bits requantized modulator (green solid line); (blue solid line); (c). The phase noise contributed by the third-order, 8 output bits requantized modulator (red solid line); (e). The phase noise contributed by the third-order, 8 output bits requantized modulator (green solid line); (blue solid line);

As seen in figure 3.9, the black dashed line expresses the phase noise of PLL DSM when disabling the noise cancellation path. The magenta dashed line expresses the phase noise of PLL DSM after noise cancellation with 1% error charge mismatch. It is worth nothing that the 1% charge mismatch can be regarded as a very pretty good result in the practical design of noise

cancellation path. The three solid lines express the phase noise contributed by the requantized modulators with different orders and output levels. Obviously, to ensure that the noise of the requantized modulator has less impact on (both in-band and out-of-band) PLL output, its phase noise contribution should be under the available region (shaded area in figure 3.9). For this to be true, the green and blue lines (8 output bits) therefore meet the phase noise requirement, while the red line will contribute more phase noise to the out-of-band frequency offset at the PLL output since only 6 output bits (256 output levels) are applied for the requantized modulator.

On the other hand, as described earlier, a high resolution (more than 6 output bits)  $\Delta\Sigma$  DAC is difficult to be implemented by using normal modulator architecture. The segmented [16], [17] and cascaded [18] modulators can solve this problem while keeping reasonable system complexity and power consumption. In our design, a novel hybrid (segmented + cascaded) requantized modulator will be developed for the  $\Delta\Sigma$  DAC to obtain high resolution (more than 8 bits) output while decrease the area and complexity simultaneously. More details about this issue will be discussed in section 3.4.3.

Finally, since the adoption of requantized modulator reduces the design difficulty of DEM circuit, the phase noise contributed by the mismatches between the unit current banks can therefore be improved by the implementation of DEM algorithm which is capable of high-pass shaping the mismatch error  $e_{DAC}[n]$  [19]. Hence the phase noise contributed by  $e_{DAC}[n]$  can be expressed as:

$$S_{DAC}(j2\pi f) \approx \frac{1}{f_{REF}} S_{e_{DAC}}(e^{\frac{j2\pi f}{f_{REF}}}) \times \left|H(j2\pi f)\right|^2$$

(3.11)

where  $S_{e_{DAC}}$  is the PSD of  $e_{DAC}[n]$ . The high-pass shaped characteristic of  $S_{e_{DAC}}$  can ensure that less noise closed to the carrier frequency will inject into the PLL bandwidth, which is similar to the mechanism of  $\Delta\Sigma$  modulator.

### 3.4 Proposed wide bandwidth PLL

To solve the problem mentioned in the previous sections, an advanced architecture shown in figure 3.10 is proposed. The combinations of VCO and Divide-by-Two/Three circuits are used to guarantee that the output range can cover the desired frequency bands listed in table 2.1. The adoption of second order  $\Delta\Sigma$  modulator with 18 bits DC input can ensure the PLL output has the required minimum channel spacing. Furthermore, the utilization of retiming circuit and synchronous divider can reduce the nonlinear effect in the PFD/CP on one side, and improve the error charge mismatch between the signal and noise cancellation paths on the other side. Finally, a novel hybrid  $\Delta\Sigma$  DAC, which will be proposed in section 3.4.3, is developed to increase the DAC output resolution and decrease the system complexity and area cost simultaneously. Each aspects of this architecture will be analyzed in the following sections.

Figure 3.10 Proposed wide BW fractional-N frequency synthesizer utilizing hybrid  $-\Delta\Sigma$ -DAC for phase noise cancellation.

## 3.4.1 Improvement of error charge mismatch between the signal and phase noise cancellation path

As the analysis in section 3.3.1, the error charge mismatch between the two paths is unavoidable since different signal modulation types (PCM and PWM) are used in different paths. This will result in undesired voltage spurs (see figure 3.6) after the loop filter even though the total error charge in each path are exactly the same.

The basic idea to solve this mismatch problem is to increase the overlap area between the CP and DAC output as much as possible. Therefore less residual charge will be converted to the voltage spur after enabling noise cancellation techniques. We know that the DAC pulse is typically aligned with the rising/falling edges of divider output. Hence, as shown in figure 3.6, the overlap area between CP and DAC output probably could be zero, resulting in a reduction of error charge canceling performance. To avoid such undesired condition, the retiming circuitry, which can be implemented easily when adopting the synchronous divider, is necessary to be used to ensure that the overlap area between the CP and DAC output is large and always exists.

On the other hand, it is known that the CP output are PWM pulses which have fixed gain level and variable durations. On the contrary, the DAC PCM output have fixed duration and modulated gain levels. To meet equation (3.4), the total charge of CP and DAC should be exactly the same. While this will not happen if  $T_{DAC}$  does not change with  $T_{VCO}$ . To solve this problem, the fixed duration  $T_{DAC}$  can be set to an integer number of VCO periods (i.e.  $T_{DAC} = MT_{VCO}$ , where *M* is an integer). Therefore when  $T_{VCO}$  is changed, the corresponding pulse duration of DAC output can be also changed. If the relationship between the gain levels of CP and DAC is  $I_{DAC} = I_{CP}/M$ , the total charge of DAC and CP can be equal theoretically. Then the following question is how to determine the integer number *M*? Figure 3.11 explains the effect of the DAC pulse duration  $MT_{VCO}$  and overlap area between CP and DAC output on the error charge cancellation.

Figure 3.11 Effect of DAC pulse durations and overlap area (red regions) on the error charge cancellation.

Before the analysis, we suppose that the total charge from DAC and CP output is exactly equal and the low-pass filter is built by a simple capacitor. Then it is evident that when the overlap area is zero in case A, more residual charge will be left to the loop filter, leading to a high voltage ripple which will cause reference spur and phase noise at the PLL output. On the contrary, in case B and C, the overlap area between the CP and DAC output decrease the residual charge after the noise cancellation and hence smaller voltage spur can be obtained. Moreover, compared to case C, the pulse duration in case B is narrower and the error charge cancellation is more effective because of the smaller voltage transients. In conclusion, the narrower the DAC pulse, the smaller the undesired voltage spur.

The above analysis seems to be true if we don't concern the timing errors in the real circuitries. Actually the timing error, which is defined as  $\Delta T_{DAC}$  in this work, will result in a normalized gain error  $\Delta T_{DAC}/T_{DAC}$  at the DAC output. What's more,  $\Delta T_{DAC}$  usually does not change accompanied with the variation of  $T_{DAC}$ . If  $T_{DAC}$  is too small, the gain errors induced by  $\Delta T_{DAC}$  will

become larger and affect the noise cancellation performance. Thus a compromise should be made carefully to determine the integer number M. Researches in [9], [10] had proved that the empirical optimized value of M is 4 which will also be adopted in our design.

Then when concerning the DAC pulse duration effects on the phase noise of PLL output, the equation (3.9) should be modified as

$$S_{Q_r}(j2\pi f) = \left\{ \alpha^2 + \left(\frac{\Delta T_{DAC}}{T_{DAC}}\right)^2 + (\pi f T_{DAC})^2 \right\} \times \frac{\pi^2}{3f_{REF}} \left| 2\sin(\frac{\pi f}{f_{REF}}) \right|^{2(k-1)} \times \left| H(j2\pi f) \right|^2$$

(3.12)

where  $\pi fT_{DAC}$  reflects the contribution of DAC pulse duration to the PLL phase noise. The detailed derivation of the part  $\pi fT_{DAC}$  can be found in [15].

Finally, we can derive the final equation for PLL phase noise contributed by the imperfect phase noise cancellation path.

$$S_{Cancel}(j2\pi f) = S_{RQ}(j2\pi f) + S_{DAC}(j2\pi f) + S_{Q_r}(j2\pi f)$$

(3.13)

where  $S_{RQ}$ ,  $S_{DAC}$  and  $S_{Qr}$  are given by equation (3.10), (3.11) and (3.12), respectively.

### 3.4.2 PFD/CP linearization technique

As analyzed earlier, the PFD/CP nonlinearity will deteriorate the phase noise performance at the PLL output because of the inherent mechanism of  $\Delta\Sigma$

fractional-N PLL in the locked state. In figure 3.7, we can find that one simple and directed method to overcome this problem is to narrow the range of DSM output pattern, therefore have the dynamic dividing ratio toggling in a more linear region. However, smaller output pattern range will affect the stable input range of high order DSM, probably inducing the frequency dead band [20]. Typically, to avoid the frequency dead band at the PLL output, the DSM should have more than 3 output bits with the output pattern ranging from N-4 to N-3. Nevertheless, the noise folding effect attributed to PFD/CP nonlinearity will be amplified if the output pattern range becomes wider.

Figure 3.12. Effect of offset current on the PFD/CP transfer function: (a). Linearized PFD/CP transfer characteristic by using offset current; (b). CP schematic with offset current source.

To break up the dilemma between the PFD/CP nonlinear effect and DSM output pattern range, the additional offset current source presented in [13] can be added to decrease the sensitivity of PFD/CP to nonlinear distortions while keeping reasonable DSM output bits. As shown in figure 3.12, the transfer curve around the origin is often nonlinear. By adding offset current, the operation region of the transfer curve can be shifted up or down to its more linear part, alleviating the high frequency noise folding issue.

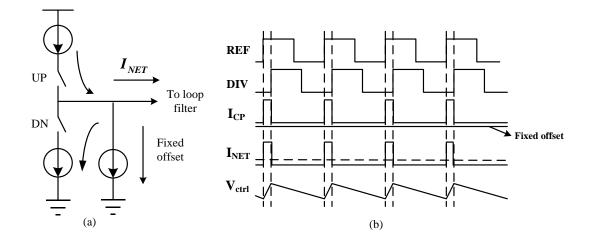

Conventionally, the added offset has a fixed value which can be easily implemented by a DC current source. However, such a fixed current will increase the gain level of undesired reference spur. As seen in figure 3.13, the net current  $I_{NET}$  after the subtraction between  $I_{CP}$  and fixed offset generates a

periodical ripple on  $V_{CTRL}$  which will modulate the VCO, resulting in an increment of reference spurious level.

Figure 3.13. Effect of fixed offset current on the reference spurious levels: (a). Schematic; (b). Timing diagram;

Figure 3.14. Proposed PFD/CP with fixed timing offset: (a). Schematic; (b). Timing diagram.

Instead of the linearization technique by using fixed current offset, the insertion of fixed timing offset pulse  $T_{fix}$  can greatly improve the reference spur performance. As shown in figure 3.14, the net current  $I_{NET}$  at the CP output, which will be further cancelled by the noise cancellation path, acts as the one without adding any linear offset. Furthermore, the pulse width of  $T_{fix}$  is set to guarantee that the final PFD output is capable of enabling a proper current pulse which has a large area overlapped with the CS-DAC output, resulting in an effective cancellation for the error charges. It is worth nothing that in this work the periodical timing pulses are provided by the retiming circuit proposed in figure 3.10. If the power and area budget is allowed, such timing offset approach can be replaced by the switch-controlled current source inserted before the loop filter.

### 3.4.3 Proposed architecture for high resolution DAC

In this section, a high resolution  $\Delta\Sigma$  DAC will be proposed to construct the phase noise cancellation path. As described in section 3.3.3, the main issue is how to optimize the circuitry to ensure that the DAC output has more than 6 bits while keeping acceptable area cost and system complexity.

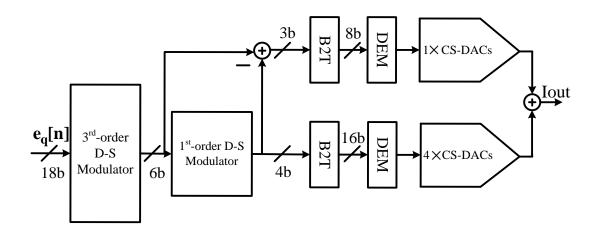

Figure 3.15. Segmented  $\Delta\Sigma$  DAC with 6 bits modulator output

The segmented modulator [16] shown in figure 3.15 is popular to be adopted when designing multi-bits  $\Delta\Sigma$  DAC. As we see, the third-order modulator has 6 bits output which will be divided into two parts for the subsequent processing. The adoption of a first-order modulator can guarantee that the mismatch between the two separated bit patterns is inherently shaped by the first-order high-pass transfer characteristic, avoiding an undesired increment of the in-band noise. Additionally, since the 6 bits output of the first modulator is divided into two smaller parts, the implementation of their own DEM circuitries will become easier, compared to the normal  $\Delta\Sigma$  DACs.

Figure 3.16. Cascaded  $\Delta\Sigma$  DAC with more than 6 bits equivalent modulator output. However, the classical  $\Delta\Sigma$  DAC by using segmented noise-shaped DEM algorithm will still suffer the complexity problem when more than 6 output bits are required. The improved segmented noise-shaped DEM technique proposed in [17] can be alternatively chosen to widen the output bit width whereas a novel DEM algorithm and CS-DAC banks are needed to be developed.

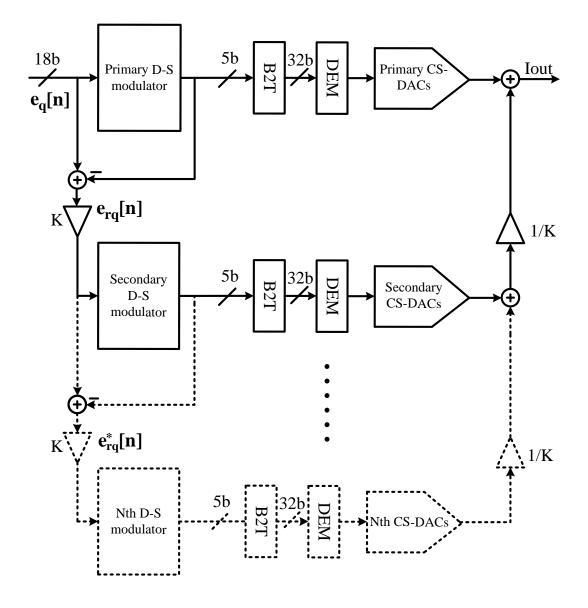

Another choice to further increase the output resolution of  $\Delta\Sigma$  DAC is the cascaded modulator architecture [18].

The cascaded modulator architecture is shown in figure 3.16. First of all, if we only concern on the primary stage, it is relative output in *Z*-domain can be expressed as:

$$Y_1(z) = STF_1(z)X(z) + NTF_1(z)E_{rq}(z)$$

(3.14)

where  $STF_1(z)$  and  $NTF_1(z)$  are the signal and noise transfer function for the primary modulator, respectively.  $E_{rq}(z)$  is the requantization noise from the primary  $\Delta\Sigma$  modulator, which is expressed as  $e_{rq}[n]$  in the time domain. Then extract  $e_{rq}[n]$  by subtracting the output of primary modulator from its input, scale up  $e_{rq}[n]$  by a factor of "K" and have it passing through the secondary modulator for the post processing. If  $STF_1(z)$  is easy to be built (i.e.  $STF_1(z) = 1$ , in our case), the input signal X(z) can be removed completely before  $E_{rq}(z)$  enters into the secondary path. Therefore, the secondary modulator output is:

$$Y_{2}(z) = K \cdot STF_{2}(z)NTF_{1}(z)E_{rq}(z) + NTF_{2}(z)E_{rq}^{*}(z)$$

(3.15)

where  $E_{rq}^*(z)$  represents the requantization noise in the secondary modulator which is expressed as  $e_{rq}^*[n]$  in the time domain.  $STF_2(z)$  and  $NTF_2(z)$  are the signal and noise transfer function for the secondary modulator, respectively. Note that the  $STF_2(z)$  is designed to be 1 to simplify the matching work. Subsequently, the next step is to scale down  $Y_2(z)$  by a factor of "1/K" and sum it with  $Y_1(z)$  in the analog domain. Thus the final output is given by:

$$Y_{Total}(z) = STF_{2}(z)Y_{1}(z) + \frac{1}{K}Y_{2}(z)$$

=  $STF_{1}(z)X(z) + \frac{1}{K}NTF_{2}(z)E_{rq}^{*}(z)$  (3.16)

Apparently,  $E_{rq}(z)$  in the primary modulator is removed from the final output and what's left in  $Y_{Total}(z)$  are the input signal and shaped noise  $NTF_2(z)E_{rq}^*(z)$  multiplied by a scaled down factor "1/K". Therefore the quantization noise will reduce proportionally, which is equivalent to an increment of the DAC output resolution.

On the other hand, if there are some mismatches between the primary and secondary path, the transfer function in (3.16) will be changed as:

$$Y_{Total}(z) = STF_{1}(z)X(z) + (1 - \frac{K_{D}}{K_{A}})NTF_{1}(z)E_{rq}(z) + \frac{1}{K_{A}}NTF_{2}(z)E_{rq}^{*}(z)$$

(3.17)

where  $K_D$  and  $K_A$  represent the scaled factors in the digital and analog domain, respectively. If  $K_D$  is equal to  $K_A$ , equation (3.17) reduces to (3.16) and the two stages are perfectly matched. Otherwise the mismatch, which can be regarded as the difference between the scalded factors in different domains, will be reduced inherently by the part " $1-K_D/K_A$ " and hence have less impact on the modulator output.

Additionally, in principle there is no limitation for the number of cascaded stages. Hence more stages can be cascaded to obtain finer output resolution. If the scaled up/down factors between each stages are supposed to be equal,

equation (3.16) can be modified as:

$$Y_{Total}(z) = STF_1(z)X(z) + \frac{1}{K^N}NTF_N(z)E_{rq}^{**}(z)$$

(3.18)

where *N* is the number of the cascaded stages, and  $NTF_N E_{rq}^{**}(z)$  represents the shaped requantization noise in the *N*<sup>th</sup> cascaded stage. Obviously, the scaled factor *K* before each stage will in turn increase the effective output resolution. Theoretically, *K* and *N* can be set to any high value until the designed system reaches to the minimum size limitation for the analog devices.

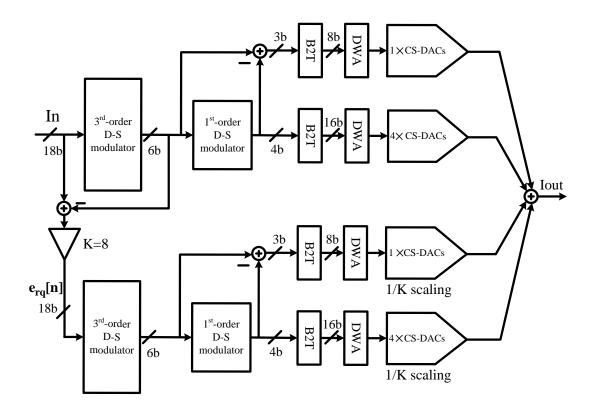

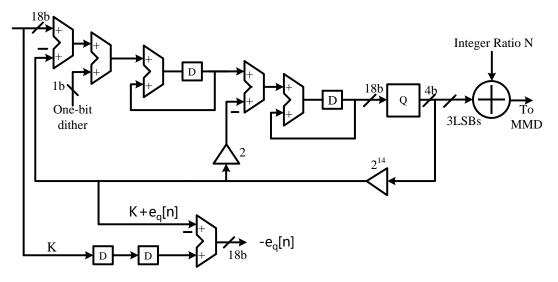

Figure 3.17. Proposed hybrid  $\Delta\Sigma$  DAC with 9 bits equivalent output

As the above analysis, the segmented and cascaded modulators are capable of providing higher output resolution respect to the normal architectures. On the other hand, to further simplify the complexity while keeping higher resolution, a hybrid  $\Delta\Sigma$  DAC shown in figure 3.17 is proposed in our design. As we see, the segmented modulator is adopted in each stage individually to ensure 6 output bits. On the other hand, the scaled up factor "*K*" is set to 8 in this case

which can be realized by a simple left-shifting bit operation whereas the factor "1/K" is implemented by scaling down the size of CS-DACs proportionally in the secondary stage. By referring to equation (3.16), we can know that the final equivalent output bits/levels is up to 9/512, which meets the requirement for the phase noise cancellation path. Further, the Data-Weighted-Averaging (DWA) is selected as the DEM algorithm in our design due to its simplification and power efficiency, whereas other newest DEM algorithms with more effective suppression for CS-DACs' distortion (such as [22]) can also be used alternatively to improve the PSD of  $S_{DAC}$  contributing to the PLL phase noise.

### 3.5 Simulated results in high-level design

### 3.5.1 Loop filter design

A third-order passive loop filter will be adopted in our design to implement a fourth-order closed loop transfer function for the whole system. By using the equation (3.8), we can guarantee that the setting parameters meet the stable and BW conditions. The targeted values of these parameters are given as follows:

| C2 = 33.7  pF        | $R2 = 19.8k\Omega$     |

|----------------------|------------------------|

| C1 = 3.08  pF        |                        |

| C3 = 0.8  pF         | $R3 = 5.3k\Omega$      |

| $I_{CP} = 450 \mu A$ | $K_{VCO} = 57 MHz / V$ |

| BW = 1MHz            | $f_{REF} = 50MHz$      |

All of the above parameters have to be determined carefully after a compromised consideration for settling time, stability and noise. For instance, the CP output current should be high enough in the wide BW PLL in order to avoid an apparent growth of in-band noise. While the VCO gain should be small enough to ensure that the control voltage fluctuation has less impact on

VCO since this undesired voltage ripple will eventually contribute to the phase noise and spurious tones at the PLL output. On the other hand, the 1 MHz PLL BW can enable fast settling time while the relative reference frequency  $f_{REF}$  has to be high enough to make the system be far away from the instable condition ( $BW < f_{REF} / 10$ ).

Figure 3.18. Open loop transfer characteristic of proposed PLL.

By using these predicted values mentioned above, now we can estimate the ideal transfer characteristics. Figure 3.18 depicts the open loop transfer characteristic of proposed system. Obviously, the phase margin is 56.2 degree and hence meets the requirement of system stability. Figure 3.19 shows the gain and phase of relative closed loop transfer function, it is evident that the system 3dB BW is around 1MHz which is capable of enabling fast settling time for our design target.

Figure 3.19. Closed loop transfer characteristic of proposed PLL

### 3.5.2 Simulated results for the proposed DAC

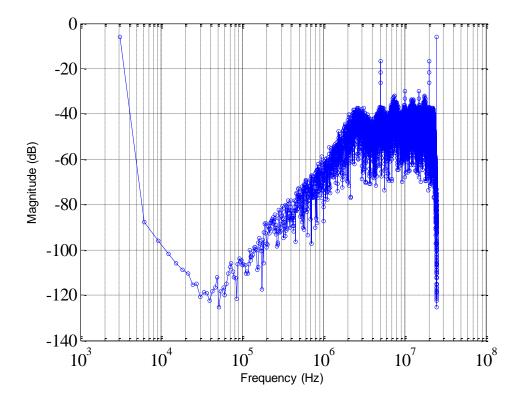

It is also necessary to estimate the performance of phase noise cancellation path before we come to the detailed circuit design. First of all, the behavioral model of proposed DAC is built in simulink. All the components are ideal and obtained from the default Matlab libraries. Secondly, two 3<sup>rd</sup>-order-singleloop  $\Delta\Sigma$  modulators with the same architecture are designed in each cascaded stage respectively. A Linear-Feedback-Shift-Register (LFSR) with 25 bits is used to generate one-bit dithering for both the two modulators, which can mitigate the spurious tones by randomizing the Least Significant Bit (LSB) of proposed modulators [22]. Moreover, Instead of the quantization error  $e_q[n]$ from PLL DSM, a DC word with 18 bits is setup to test the  $\Delta\Sigma$  DAC performance. Since the schematic in simulink is ideal and what we mainly concern here is the quantization noise, the analog mismatch and distortion between the practical CS-DACs can be neglected to simplify the simulation work. The relative simulated results are shown in figure 3.21.

Figure 3.20. Behavioral model of proposed  $\Delta\Sigma$  DAC built in Simulink

Figure 3.21. Output spectrums of behavioral models for different  $\Delta\Sigma$  DACs (8192 points FFT).

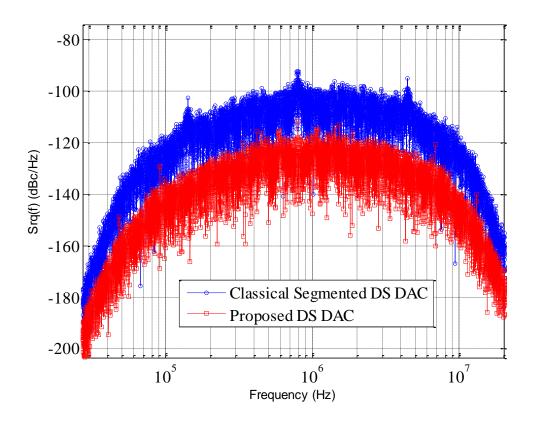

In the beginning of the simulation, the secondary stage of the proposed architecture is disabled, the system will reduce to classical a segmented  $\Delta\Sigma$  DAC and its corresponding output spectrum can be therefore obtained (blue line with circles). Then recover the proposed architecture and redo the simulation. Compared to the previous spectrum of segmented  $\Delta\Sigma$  DAC [16], the relative result (red line with squares) shows that the quantization noise in the proposed architecture is greatly reduced by 18 dB since the equivalent output bits are increased from 6 to 9. With the analysis in section 3.3.3, we understand that less out-of-band quantization noise in the proposed  $\Delta\Sigma$  DAC can ensure that its contribution to the phase noise is within the available region shown in figure 3.9, meeting the requirement for the additive noise in noise cancellation path.

### **3.5.3 Simulated results for the whole system**

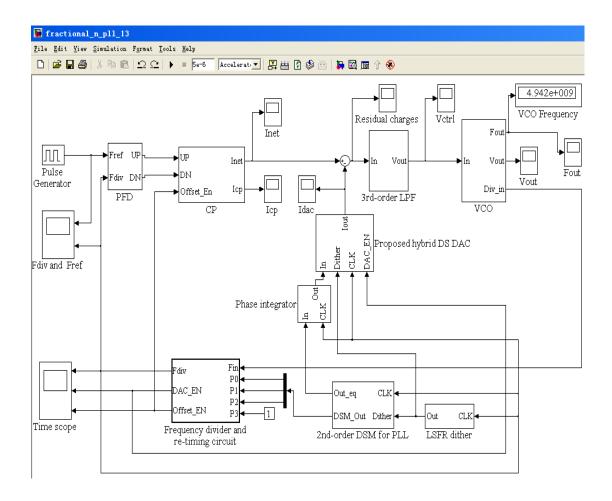

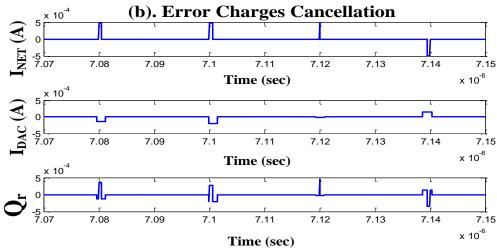

The behavioral model shown in figure 3.22 is built to examine the system functionality and impact of the quantization noise on the wide BW PLL. The basic parameters of the PLL have estimated in section 3.5.1 and will be used to specify the corresponding functional blocks. The ideal  $\Delta\Sigma$  DAC verified in section 3.5.2 is adopted to construct the noise cancellation path. On the other hand, by referring to figure 3.10, the phase integrator between the PLL DSM and  $\Delta\Sigma$  DAC is used to convert the quantization error to the phase error, matching the function of divider in signal path. What's more, just as the modulators in  $\Delta\Sigma$  DAC, a one-bit dithering should be inserted into the LSB of the PLL DSM to avoid the spurious problem. In order to simplify the complexity, only one LSFR is adopted in the system, whose output bit stream is shared by all the  $\Delta\Sigma$  modulators. Finally, the timing offset pulses from the retiming circuit is fed to the CP in order to force it operate in a more linear region. In the mean time, the retiming blocks also can increase the overlapped region between the CP and CS-DAC outputs, leading to a performance improvement of the noise cancellation technique.

Figure 3.22. Behavioral model of proposed system built in Simulink

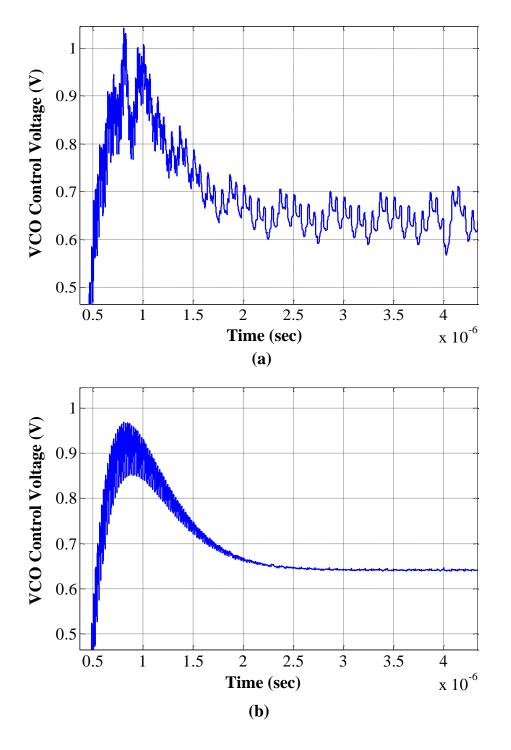

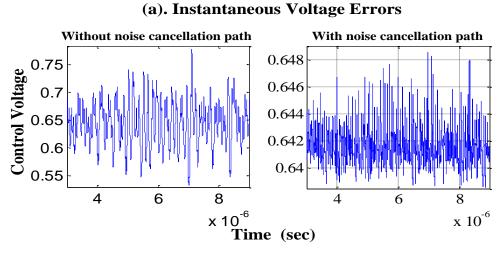

By using this behavioral model, we therefore can do the simulation to check its functionality and the impact of the proposed noise cancellation technique. At the first, the noise cancellation path is disconnected while keeping the BW unchanged. After the simulation, the relative results for the voltage transients is shown in figure 3.23 (a). It can be seen that the average level of control voltage  $V_{ctrl}$  is finally fixed to 0.64V at 2.5 $\mu$ S ( $\approx$  the PLL settling time) approximately. Hence, we can say that the functionality of the proposed PLL is correct. However, even though the average level of  $V_{ctrl}$  is locked, the instantaneous voltage error can be seen apparently on the control voltage which will deteriorate the phase noise at the PLL output. This is due to the fact that the quantization noise from the DSM will be converted to the related error through the signal path. The traditional method to solve this problem is to narrow the BW and hence suppress the instantaneous voltage error more effectively. However, this solution is not feasible in the proposed PLL since the wide BW is needed to be maintained. Then let's enable the noise cancellation path and redo the simulation. The related simulated result can be seen in figure 3.23 (b).