# Exploration of formal verification in GPU hardware IP

NISHANT GUPTA MASTER'S THESIS DEPARTMENT OF ELECTRICAL AND INFORMATION TECHNOLOGY FACULTY OF ENGINEERING | LTH | LUND UNIVERSITY

# Exploration of formal verification in GPU hardware IP

Nishant Gupta ni4086gu-s@student.lu.se

Department of Electrical and Information Technology Lund University

> Supervisors: Erik Larsson, LTH Sadat Rahman, ARM

Examiner: Christian Nyberg

October 10, 2019

© 2019 Printed in Sweden Tryckeriet i E-huset, Lund

### List Of Acronyms

**AXI** Advanced Extensible Interface. **BDD** Binary Decision Diagram. CH Cache Hit. CM Cache Miss. **CTL** Computation Tree Logic. **DUT** Design Under Test. FSDC Fragment Shader Descriptor Cache. **FSM** Finite State Machine. GPU Graphics Processing Unit. IC Integrated Circuit. IO Input Output. **IP** Intellectual Property. LRU Least Recent Used. LTL Linear Temporal Logic. **RTL** Register Transfer Level. **SAT** Satisfiability. **SCM** Shader Context Manager. SVA System Verilog Assertions. TCL Tool Control Language. **UVM** Universal Verification Methodology. **VIP** Verification Intellectual Property.

## Glossary

- ${\bf cache\ hit\ }$  When new pointer address value to FSDC is already present inside the cache.

- **cache miss** When new pointer address value to FSDC is not present inside the cache.

- **least recent used** It is a cache replacement policy algorithm which discards the least recent used item first.

- state space A set of states a system can occupy.

### Abstract

Today, digital circuits are part of every ones daily life in form of mobile phones, computers, television, smart cards etc. The advent of new technologies such as internet of things, 5G etc. are continuously making the digital circuits more and more complex in design. With this increase in complexity comes the possibility of more bugs in the system. Finding and fixing these bugs is of paramount importance as it can lead to huge financial losses or can even be fatal especially in safety critical applications. Over the last few decades, traditional simulation based verification has been used as the default methodology to verify digital hardware designs. Although it has certain drawbacks such as:

- It is not exhaustive in nature meaning that it is very tough to cover all the possible input test vector as part of input stimulus being applied to the test bench.

- And due to its non-exhaustive nature, there will always be a possibility of missing bugs in the design especially the corner cases that can lower the design quality.

Recently formal verification has been evolved as an attractive and more comprehensive alternative to simulation based verification. In this master thesis work, model checking (alternatively property based verification) has been applied as a preferred formal verification technique on a module inside the Arm Mali GPU hardware IP in order to try and hit the corner case design bugs, if any. The module or DUT chosen for investigation in this thesis work is Fragment Shader Descriptor Cache (FSDC). This is a new module and mainly consists of control path logic which suits formal verification. The DUT has already been extensively verified by simulation based verification. The result shown later for this thesis work highlights that:

- Formal verification can be applied to a complete module as an alternative verification methodology.

- After the application of formal verification on DUT, 3 design bugs were discovered which were missed by the simulation verification.

Finally, based on above results and various challenges faced during this thesis work such as state space exploration problem or applying formal verification on complex parts of the design, it can be concluded that formal verification complements and at least provides a partial solution to the limitations of simulation based verification.

## Acknowledgements

I would like to take this opportunity to thank LTH, Lund University and Arm for giving me this opportunity to pursue this master thesis. Moreover, I would like to thank my supervisor at Arm, Sadat Rahman for his continuous support and guidance. I would also like to thank Yunus Ökmen and Henrique Martins for their great insight and patience to answer all my questions.

Last but not the least, I would like to thank my supervisor at the university, Erik Larsson and my examiner, Christian Nyberg for their great support and continuous feedback throughout this thesis work.

Nishant Gupta, Lund 2019.

### Popular Science Summary

The advent of transistors in 1947 revolutionized the field of electronics and paved the way for development of first IC in 1949 by the German engineer Werner Jacobi. In 1965, Gordon Moore predicted that number of transistor per IC will double every year while their cost will get halved, which famously later come to known as Moore's law. For later part of most of 20th century, there has been a tremendous growth in advancement of IC's in terms of speed, size and capacity. Almost following the Moore's law, the IC's of today are million times more faster and bigger in size then the ones in 1970's. Although IC's continue to grow in design and complexity, the engineers at the same time start to get haunted by the question of reliability of these designs.

Today advancement in machine learning, big data analytic, Internet of Things (IoT), autonomous vehicles are further fueling the innovation in hardware, thus, further worsening the challenges of test and verification of these designs. Verification almost account for nearly 70% of the overall design cost. Dynamic simulation has been the most popular choice of verification methodology for testing and verification of hardware designs. It has evolved over years by consolidating various diverse sets of methodologies into one now known as UVM. Although overall framework looks promising but it still has some way to go.

While almost in parallel a new verification methodology was evolving in background called formal verification. During this thesis work, application of formal verification on DUT will be explored mostly from the point of view that it can be applied as an alternative verification methodology on a complete module inside a system and also that it can help to try and hit the corner case bugs which might be missed by the simulation verification.

# Table of Contents

| 1  | Introduction               |                                         |    |  |  |  |  |

|----|----------------------------|-----------------------------------------|----|--|--|--|--|

|    | 1.1                        | Simulation vs formal verification       | 2  |  |  |  |  |

|    | 1.2                        | Structure of the thesis                 | 4  |  |  |  |  |

| 2  | Theory                     |                                         |    |  |  |  |  |

|    | 2.1                        | Formal verification                     | 5  |  |  |  |  |

|    | 2.2                        | Fragment Shader Descriptor Cache (FSDC) | 10 |  |  |  |  |

| 3  | Met                        | hod                                     | 13 |  |  |  |  |

|    | 3.1                        | Formal verification test environment    | 13 |  |  |  |  |

|    | 3.2                        | Design specifications                   | 15 |  |  |  |  |

|    | 3.3                        |                                         | 15 |  |  |  |  |

|    | 3.4                        | Formal verification implementation      | 17 |  |  |  |  |

|    | 3.5                        |                                         | 19 |  |  |  |  |

|    | 3.6                        | Assertions                              | 22 |  |  |  |  |

| 4  | Resu                       | ılts                                    | 33 |  |  |  |  |

|    | 4.1                        | Formal verification application on DUT  | 33 |  |  |  |  |

|    | 4.2                        |                                         | 36 |  |  |  |  |

| 5  | Conclusion and Future work |                                         |    |  |  |  |  |

|    | 5.1                        | Conclusions                             | 37 |  |  |  |  |

|    | 5.2                        | Future work                             | 38 |  |  |  |  |

| Re | feren                      | ces                                     | 41 |  |  |  |  |

# List of Figures

| 1.2Simulation verification[5]1.3Formal verification[5] | 2<br>3<br>6 |

|--------------------------------------------------------|-------------|

| 1.3 Formal verification[5]                             | -           |

|                                                        | 6           |

| 2.1 Model checking                                     | U           |

| 2.2 Layers of SVA assertion language [10]              | 6           |

| 2.3 Interface of Cadence Jaspergold formal tool        | 9           |

| 2.4 Proof grid manager                                 | 9           |

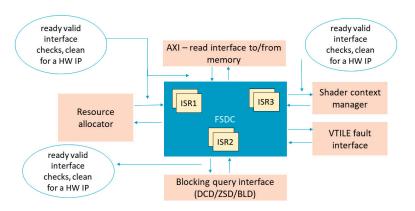

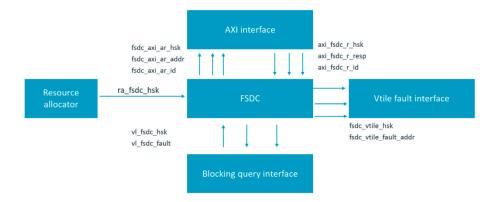

| 2.5 FSDC                                               | 10          |

| 2.6 Time vs FSDC operation stages                      | 11          |

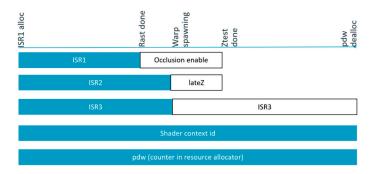

| 2.7 Lifetime of various registers and their index      | 11          |

| 3.1 Analyze and elaborate command in the TCL script    | 13          |

| 3.2 Bind file                                          | 14          |

| 3.3 Define global clock and reset                      | 14          |

| 3.4 Define proof engines for the tool                  | 14          |

| 3.5 Command for proving all the properties             | 14          |

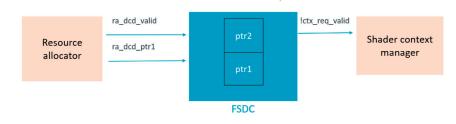

| 3.6 Ready valid interface for FSDC                     | 16          |

| 3.7 Example - Rasterizer to FSDC valid and ready       | 17          |

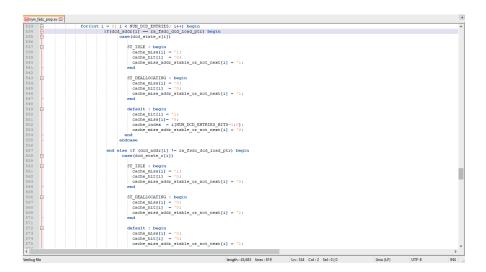

| 3.8 Auxiliary code snippet                             | 21          |

| 3.9 Cache miss scenario                                | 22          |

| 3.10 Cache hit scenario                                | 23          |

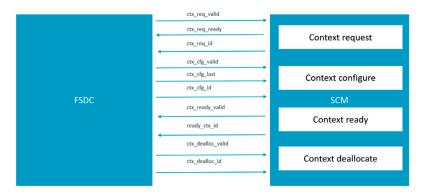

| 3.11 FSDC-SCM interface verification                   | 24          |

| 3.12 AXI fault verification                            | 31          |

| 3.13 Symbolic variable lifetime                        | 32          |

# List of Tables

| 3.1  | CH and CM scenario                                                          | 21 |

|------|-----------------------------------------------------------------------------|----|

| 3.2  | Total no. of assertions for verifying the cache behavior with their status  | 24 |

| 3.3  | Total no. of assertions for verifying the SCM context load with their       |    |

|      | status                                                                      | 26 |

| 3.4  | Undetermined properties for SCM context load with their depth               | 26 |

| 3.5  | Total no. of covers for undetermined property with their status             | 27 |

| 3.6  | Total no. of assertions for verifying the blocking query with their status  | 27 |

| 3.7  | Undetermined properties for blocking query with their depth                 | 27 |

| 3.8  | Total no. of covers for undetermined property with their status             | 28 |

| 3.9  | Total no. of assertions for verifying the design counters with their status | 29 |

| 3.10 | Total no. of assertions for verifying the FSM with their status             | 30 |

| 3.11 | Total no. of assertions for verifying the reset checks with their status    | 30 |

| 4.1  | Formal Vs. Simulation bring up time comparison result                       | 33 |

| 4.2  | Total no. of SVA written in this thesis work                                | 34 |

| 4.3  | IO Planned vs Covered                                                       | 34 |

### \_ Chapter 📕

### Introduction

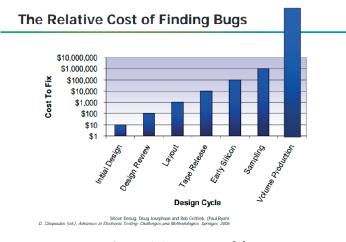

Today electronic systems are getting more complex in nature. The increasing design complexity increases the possibility of bugs in the design. As shown in figure 1.1, cost of fixing bugs increases a lot later in the development cycle, it is better to find bugs in the design as early as possible. Considering the increasing cost of fixing bugs with shorter development cycle and time to market pressure, a lot of effort and resources are put into the hardware verification these days. Almost 70% of the design time and engineering resources are put into design verification and that's why it is becoming such a bottle-neck for time to market in integrated circuit design [1].

Figure 1.1: Bug cost [2]

Hardware verification is the process of proving the correctness of the system based on its specification and implementation. Basically most of the hardware verification done today can be classified into two broad categories - simulation and formal verification.

#### 1.1 Simulation vs formal verification

Simulation verification is a technique where a test bench or test wrapper is created around the design. Then both direct written test or randomly generated test are used to stimulate the design. After running the test, the failures are debugged and fixed and then re-run again until the design is clean [3]. The advantages of simulation based verification is [4]:

- It is a proven methodology as it has been successfully used by verification engineers for so many years.

- It is scalable with bigger and complex designs.

- It helps to find most of the bugs, simple ones immediately and complex ones after some time.

Some disadvantages of simulation based verification are [4]:

- Creation of test bench is a lengthy process, generally takes months for the complex part or area of the design.

- It is very tough to create an exhaustive test bench covering all the possible input test cases.

- Some bugs are found very late in the development cycle and some are not found at all.

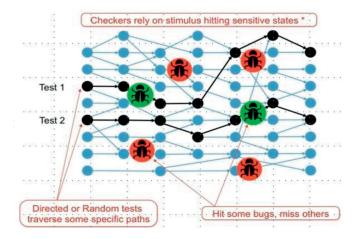

As shown in the figure 1.2, there are two tests (Test1 and Test2) which are applied on the design. After running them, they hit some states in the state space and depending on the presence of bugs on those path, they will either be able to find them or not. But at the same time a lot of states are still not covered with the generated input tests and because of that there is a possibility of missing some bugs in the design as shown in red.

Figure 1.2: Simulation verification[5]

In Formal verification, the intended behavior of DUT is described with formal test properties written as SVA and the formal tool checks that model of DUT obeys this behavior in every possible way. This can be considered as doing all possible simulations and filter out traces which do not satisfy the proof. A misbehavior results in counter-example. Formal verification provides the following advantages over simulation verification:

- It is faster to implement.

- No input simulation test or test vectors are required.

- It is exhaustive meaning that a proven property covers the whole design space, thus, eliminating the chance to miss bugs.

But formal also has some limitations too as mentioned below :

- It is not scalable as simulation verification and more suited to smaller size designs.

- Formal verification is also not suitable to apply on all the designs such as arithmetic heavy designs or designs with high sequential depth.

- It requires a lot of effort to get the constraints right to eliminate spurious scenarios and focus on real ones.

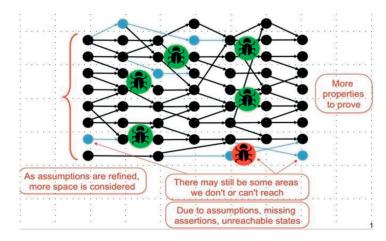

As shown in figure 1.3, the properties are written on the output pins and the assumptions or design constraints are put onto the input pins of the design. The tool will drive the input pins values and in process cover more state space thus hitting more design bugs in comparison to simulation verification. Still there can be some missing corner cases due to over constraining of the design or missing properties or unreachable states.

Figure 1.3: Formal verification[5]

In comparison, formal verification provides an advantage over simulation verification by covering more state space and try to reach and hit the corner case bugs that might or might not get missed by the simulation verification. Also, it is faster to implement compared to simulation environment set-up time and can be very useful to find the bugs early in a development cycle.

In this thesis work, the purpose would be to take the advantage of formal verification and apply it on the DUT. The DUT for this project is FSDC which is a module inside the Arm Mali GPU hardware IP. The DUT has already been extensively verified using simulation verification at Arm. The DUT consists mainly of control logic which suits formal verification. So the goals for this thesis work are :

- Application of formal verification on DUT.

- Try to find design bugs which might have been missed by the simulation verification already done on the DUT.

#### 1.2 Structure of the thesis

The rest of the thesis is structured as following. In chapter 2, in detailed theory is explained on *Formal verification and Fragment Shader Descriptor Cache (FSDC)*. In chapter 3, the approach or method to apply the formal verification on DUT is being mentioned. In chapter 4, the results for this thesis works are discussed. And finally in chapter 5, the conclusion with possible future work is mentioned.

# . <sub>Chapter</sub> 2 Theory

In this chapter, the basic theory related to theoretical concept of formal verification and FSDC is explained in detail.

#### 2.1 Formal verification

By definition, formal verification is the use of tools that mathematically analyze the space of possible behaviors of a design, rather than computing results for particular values [6]. By saying that it means that formal verification will consider the entire space of possible input stimulus and will use clever mathematical techniques to cover all the possible behaviors. There are mainly two major formal verification techniques - first is *automated model checking* which uses mathematical models to verify that a specification meets it's implementation by proving a property over a vast state space. It is mostly automated without much human intervention and return one of the 3 results [7]:

- Property is proved or passed.

- Property is not proved and will give back a counter example for it.

- Property is undetermined which means that the state space is too big for the tool to give back a result with in reasonable amount of time.

The second one is *theorem provers*, which requires human expertise in addition to the automated techniques to prove the design correctness. These are more powerful than the automated model checking but require lot of expertise to apply it [7]. For this thesis work, automated model checking is used as formal verification technique and described below in more detail.

#### 2.1.1 Automated model checking

Model checking problem is a problem for verifying that a formula f holds in a model M:

$M \mid = f$

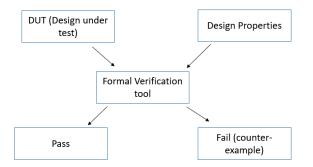

where M is the design implementation while f are the properties based on the design specifications expressed in temporal logic like Computation Tree Logic (CTL) or Linear Temporal Logic (LTL) [8]. As shown below in figure 2.1, the design implementation (RTL model) and its specifications are described in terms of intended design properties that is then being fed to the model checking tool which either prove its correctness or give a counter example if the property is not satisfied.

Figure 2.1: Model checking

#### 2.1.2 Design assertions

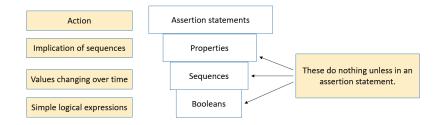

Formal verification conforms that the design meets its specifications. In order to achieve this the first step needed is to find a way to express what it means for a design to be correct. This can be achieved by writing assertions using the System Verilog Assertions (SVA) language. The SVA can be thought of as several layers of increasing complexity as shown in figure below 2.2 [9].

Figure 2.2: Layers of SVA assertion language [10]

#### Booleans

It can be a simple logical standard boolean expressions. It might be a single logic variable or a boolean formula such as  $a \ \mathcal{E} b$ . The boolean expressions can be used in a sequence or property as shown in figure 2.2 and shall be evaluated over the sampled values of all the variables [11]. Whereas, the sampled values are the values of the variable at the end of each previous simulation time step.

#### Sequences

These are the statements with boolean expressions in it that are happening over time. The simplest of sequences are linear in order meaning that they are just a list of finite boolean expressions that occur over linear order to increasing time. The increasing passage of time is defined with a clocking event. Sequences are composed by concatenation which specifies the time delay, using ## operator, from the end of first sequence to beginning of second sequence as shown below [9] [11].

a ##N b It means that signal b shall be true on the Nth clock tick after signal a was true.

#### Properties

A property combines sequences with additional operators in order to capture the design behavior that is expected to be verified based on design specification. A property can be used as an assumption, assertion or coverage specification but does not produce result by itself. Shown below is an example of a named property reqgnt:

```

property reqgnt;

req |-> s_eventually gnt;

endproperty

```

It states that if there is a request req which is an antecedent then eventually a grant must come for it gnt which is the consequent. The antecedent and consequent in the property are connected via the implication operators |-> or |=>. The first one (|->) is overlapping meaning that, if there is a match for antecedent then the end point for match is start point for the evaluation of consequent expression. While the second one (|=>) is non-overlapping meaning that, the start point for the evaluation of consequent [9] [11].

#### Assertion statements

An assertion statement is used to validate the behavior of a system. As stated above, properties do not produce any result by itself. They need to be put into an assertion statement which uses one of the following keywords *assert, assume or cover*:

• Assert: to specify the property as an obligation for the design that is to be checked to verify that the property holds [11].

assert property (req |-> gnt);

• Assume: to specify the property as input constraints on the environment. Formal tool use these input constraints in order to generate the input stimuli [11].

```

assume property (!req |-> !gnt);

```

• Cover: these are used to monitor the property evaluation for coverage [11]. They make sure that the intended behavior is happening at least once by finding a single trace for it.

cover property (req |-> gnt);

The assertions in general can be of two types - immediate and concurrent:

• Immediate assertion statements are simple assertions which follow simulation event semantics and are executed in procedural blocks. There is no clocking or reset and does not support many advanced property operators. Due to this they cannot check conditions which have passage of time. The immediate assertions are defined using only *assert* keyword without using *property* keyword with it [9] [11]:

immediate1: assert (!req && !gnt);

• Concurrent assertion statements follow the clock semantics and can describe the behavior that include passage of time. They also support advanced property statements about logical implementation that include time intervals. Concurrent assertion statements use both *assert and property* keyword in the statement as shown below [9] [11]:

conc1: assert property (a ##2 req |=> gnt);

It is worth noting that immediate assertion statements are mostly used for simulation. In this thesis work, only concurrent assertion statements were written to verify the design behavior.

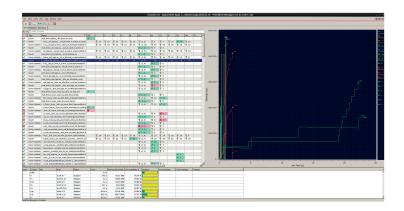

#### 2.1.3 Model checking tool

As stated earlier, automated model checking is the preferred choice of formal verification technique used for this thesis work. At present Cadence Jaspergold is one of the leading tool in this area. It is designed by Jasper design automation which is a software company and provides formal functional verification software. Jasper design automation was founded in 1999 and was later acquired by Cadence in 2014. Cadence Jaspergold encapsulates the knowledge of formal expert in a tool. It combines advanced techniques such as tunneling and abstractions with powerful proof engines based on clever mathematical models which can help to prove a property smartly and efficiently. It has easy to use interface as shown in figure 2.3. Through its interface the formal verification process can be easily iterative (performing a verification, property changes and iterating on the verification). It also provides the support for liveness properties which are missing by some other tools [7] [12].

The Cadence Jaspergold applications consist of multiple Satisfiability (SAT) and Binary Decision Diagram (BDD) based proof engines with variation of these algorithms. Proof engines are basically mathematical models that are run on a

| t Edit View Design Reports Application Tools Mindow Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                 |                                                                                       |         |           |                                               |               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------------------------------------------------------------------------------|---------|-----------|-----------------------------------------------|---------------|

| Fernal Property Ver. Coverain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 |                                                                                       |         |           |                                               |               |

| Contribution Contribution Contribution Contribution     Contribution Contribution Contribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                 |                                                                                       |         |           |                                               |               |

| A B S + S to M R R + B + B + B + B + B + B + B + B + B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 |                                                                                       |         |           |                                               |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | - h-            |                                                                                       |         |           |                                               |               |

| (p) Heardy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Property Table  |                                                                                       |         |           |                                               |               |

| ■ Independent (and a set of the set of t               | 16 🐨 17-88_JL   | 0 a B                                                                                 |         |           |                                               |               |

| I upd taps investigation (advantage) (MM, 250, DTIRES-25)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | AT Tge          | 7 Name                                                                                | T Inges |           | Time Task                                     | Taxora Soar   |

| UN3r6 (HIL)FILUE/FILLB0/FILB0/20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | A354E.          | mail_books_pop_prop_perdikc[05,as1_doot_perdix_inc_asseed06                           | HE CO   | infinite: | 17.9 <ente< td=""><td></td></ente<>           |               |

| E X 0 w, not have over their out have out the provided and the provided              | Cover (related) | mail_fudca_top_prop_entbld[0],as_j_dot_enfort_inc_assed01 precondition1               | H       | 3         | 2.7 cente                                     | xied> 1 Analy |

| <ul> <li>Contraction of the second</li> <li>Contraction of the second</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Asset.          | mail_fedcu_top_propgentikQI05as_i_dod_pefoxt_dec_asset21                              | R( (2)  | infait+   | 17.9 -cente                                   | olec > 0 Anal |

| - 🗋 0 uson, duseta inal, kol, son, dusetabliku, oco, ExtRES-234M, cTX, DITRES-23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Cover (telated) | mail_fudca_top_prop_dentiliC[[0];asi_dot_prioni_dec_assert11precondition1             | 8       | 24        | 17.2 cembe                                    | Xed> 1 Analy  |

| - V B scoruptcout instructionst                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Asset.          | mail_fodcw_top_prosglenblid[I05as_i_dod_refoxt_coreaq_assert01                        | Hp (2)  | infinite  | 17.9 -cembe                                   | Sted - 0 Anal |

| - [] 0 u_bart mail_kar_barbarbart_CTX_BITRES=20<br>8 • 0 0 u_mail_mail_bar_barbarbarbarbarbarbarbarbarbarbarbarbarb                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Cover pasated   | mail_fidex_3qu_magentilic((0)asi_dot_mfox_canne_assert03per-condition3                | FIL.    | 4         | 62 cente                                      | sted- 1 Ara   |

| - V 0 v. to pro-thic population provided to a second secon           | Asset.          | mail_fodcx_top_pros_gionbik2[05as_i_dot_refort_assert62                               | Hp (2)  | infinito  | 17.9 -cembe                                   | ided- 0 Ana   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Cover (Hided)   | mail_fedcx_top_prop_dentiliC[05_asi_dod_sefort_assertI2precondition1                  | 10      | 1         | 0.0 -ente                                     | Xed- 1 Ara    |

| - X 0 mail_bdc_asid_() (ob., abig_asid_starred) (00TH-4.600 /00TH-48181, WDTH-10.11, BEFORE_CONTROL_ON_INCE_STOP_COMPLOY=TORREDONU_INTE-<br>H X 0 v as from the prosent inputs-outle to the entropy of an entropy of the           | Asset.          | mail foldow too prosidentik/200.as _ i som verbat, inc. assert/00                     | Ny (2)  | intrito   | 17.9 -embe                                    | Sted- 0 And   |

| <ul> <li>Colorado de la constructiva de<br/>la constructiva de la cons</li></ul> | Cover (misted)  | mail_foldca_top_prop_dentikC[0].asi_son_what_ac_assert02:precondition1                | H       | 2         | 2.7 -embe                                     | ted- 1 And    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Asset.          | mail fodce top prosglenbik/(ICLas   som refatt, deoc assertio)                        | NI (2)  | infinite  | 17.9 cente                                    | ided> 0 Ana   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Cover (misted)  | mail fodce top prosperitik/20535_1.5cm /what decc assert02precondition1               | 12      | 24        | \$21 <embe< td=""><td>Med- 1.And</td></embe<> | Med- 1.And    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Asset.          | mail fudce top propajentik/202.as i som retort consq assertid                         | NE GD   | infitie   | 17.9 cente                                    | otet> 0 An    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Cover (twisted) | mail (sdc.e. top propgientik2[0].a.e. ) is on prited, conseq assert literrorandition1 | H       | 4         | 6.9 -ombo                                     | ded> 1 An     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Asset.          | mail_fstcs_top_exp_extRic(0(as_)_scm_witht_essen02                                    | NU CO   | intrite   | 17.9 cembe                                    | otet> 0 An    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Cover (saladed) | mail_fulce_top_prop_instit/citiesi_con_print_accost02procendition1                    | 10      | 1         | 0.0 combo                                     | ded> 1 And    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Asset.          | mail foldes too presidentik/[1] as i dod refet inc assert();                          | NI CI   | initize.  | 17.9 cente                                    | sted> 0 Ars   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Cover Swisted   | mail fadou too proprietitic@illas i dot refut inc assert/dimecondition1               | 1       | 6         | 7.4 cente                                     | sted - 1 Arm  |

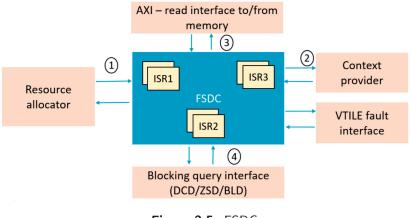

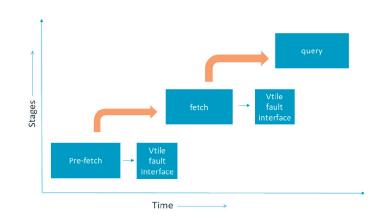

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1 Auget         | mail_folce_top_presidentific[1].asi_dol_wfoit_doc_aveotiti                            | He CO   | kitte.    | 17.9 cente                                    | sted + 0 Ara  |