# Performance Evaluation of MathWorks HDL Coder as a Vendor Independent DFE Generation

ELISABETH PONGRATZ ROSHAN CHERIAN MASTER'S THESIS DEPARTMENT OF ELECTRICAL AND INFORMATION TECHNOLOGY FACULTY OF ENGINEERING | LTH | LUND UNIVERSITY

LUND UNIVERSITY Lund University EITM01/EITM02 Master thesis report August 27, 2019

# Performance Evaluation of MathWorks HDL Coder as a Vendor Independent DFE Generation

Master thesis

By

Elisabeth Pongratz and Roshan Cherian Department of Electrical and Information Technology Faculty of Engineering, LTH, Lund University SE-221 00 Lund, Sweden 2019

Elisabeth Pongratz elt14epo@student.lu.se Roshan Cherian ro6211ch-s@student.lu.se

## 1 Abstract

This thesis aims to evaluate MathWorks HDL (Hardware Descriptive Language) Coder and compare the results with designs produced by its vendor dependent counterparts. The focus is mainly on evaluate the design effort needed to close timing and to get optimal resource mapping for a selected design. Different tests were carried out with the designs made in HDL Coder ranging from a small design to a complex digital front end design. Several logic tests were also carried out to understand the efficiency of the hardware produced from HDL Coder. To get our hands on with the tool, a power meter was undertaken as the design under test. Further, a down sampling filter chain was designed in HDL Coder and lastly, a branched filter was designed. Results have been presented for the unoptimized design and the various optimizations tried. An analysis of the different methodologies used is discussed and how the tool can make the design flow more effective. With the time invested in learning and using the tool, an experience of HDL Coder as a HLS (High Level Synthesis)) tool can be analyzed and compared to other HLS tools.

In conclusion, it was found out that in the bigger designs HDL Coder did not have a problem meeting the timing requirements for the selected designs and the results are comparable. However, it does not map optimally to the resources on the FPGA (Field Programmable Gate Array) fabric and it was difficult to change the mapping of resources according to constraints. On analysis, the HDL Coder blocks consume a lot of DSP (Digital Signal Processing) slices compared to the vendor dependent counterparts. Though, the tool is faster and easier to learn, work with and many optimization methods can be done automatically by the tool. Additionally, there is no need to run synthesis on a separate vendor cause this can be done by HDL Coder which improves the workflow. Using HDL Coder in a design methodology would increase productivity because of it being vendor independent. Whereas, the performance results can vary depending on design structure.

i

Keywords: MATLAB, Simulink, HDL Coder, XSG, DSPB.

## 2 Acknowledgements

We would like to thank LTH, Lund University and Ericsson AB for giving us this opportunity to pursue this Master thesis. In addition, we would like to express gratitude to a few people in particular. Special thanks to: our supervisor at the university, Professor Liang Liu for ensuring we ask the right research question and motivate our thesis around it. Also, great thanks to our supervisors Adeel Tajammul and Naeem Abbas at Ericsson for helping us out with their great knowledge, feedback and the review meetings. Similarly thanks to our manager, Sacki Agelis for giving us the support and the resources needed to fulfill this thesis. Thanks to Lakshmi Prasad for helping us out during the initial days to get started with the designs and continued help during the thesis.

We are also grateful for our parents who have been the pillars because of which we are here today. Additionally, in case we have missed out, we would also like to thank everyone who have contributed to this thesis in anyway possible.

| M        | ASTER | THESIS CONTEN                                   | NTS      |

|----------|-------|-------------------------------------------------|----------|

| С        | onte  | ents                                            |          |

| 1        | Abs   | tract                                           | i        |

| <b>2</b> | Ack   | nowledgements                                   | ii       |

| Li       | st of | Tables                                          | vi       |

| Li       | st of | Figures                                         | vii      |

| 3        | Pop   | ular Science Summary                            | 1        |

| 4        | Intr  | oduction                                        | <b>2</b> |

|          | 4.1   | Motivation                                      | 2        |

|          | 4.2   | State of the Art                                | 3        |

|          | 4.3   | Thesis Structure                                | 4        |

| <b>5</b> | Bac   | kground                                         | <b>5</b> |

|          | 5.1   | Digital Front-End                               | 5        |

|          | 5.2   | Current Methodology - Vendor Specific Workflow  | 5        |

|          | 5.3   | Proposed Methodology - Vendor Agnostic Workflow | 6        |

|          |       | 5.3.1 High Level Synthesis                      | 6        |

|          |       | 5.3.2 High Level Tools - HDL Code Generation    | 7        |

|          | 5.4   | FPGA Fabric                                     | 8        |

|          |       | 5.4.1 Xilinx                                    | 8        |

|          |       | 5.4.2 Intel                                     | 9        |

|          | 5.5   | Chapter Summary                                 | 9        |

| 6        | Mat   | thWorks HDL Coder                               | 10       |

|          | 6.1   | HDL Supported Blocks                            | 10       |

|          | 6.2   | Design Considerations                           | 11       |

|          | 6.3   | HDL Workflow Advisor                            | 12       |

|          |       |                                                 |          |

|   | 6.4 | Optimization Options                                                         | 12 |

|---|-----|------------------------------------------------------------------------------|----|

|   | 6.5 | Logic Tests                                                                  | 15 |

|   |     | 6.5.1 Hardware generation transformation tests $\ldots \ldots \ldots \ldots$ | 15 |

|   |     | 6.5.2 Analysis of the above tests                                            | 18 |

|   | 6.6 | Reports                                                                      | 18 |

|   | 6.7 | Resource Mapping                                                             | 18 |

|   | 6.8 | Chapter Summary                                                              | 19 |

| 7 | Exp | perimental Design, Power Meter                                               | 20 |

|   | 7.1 | Design and Implementation                                                    | 20 |

|   | 7.2 | Synthesis                                                                    | 22 |

|   | 7.3 | Optimization                                                                 | 24 |

|   | 7.4 | Results Xilinx                                                               | 24 |

|   |     | 7.4.1 HDL Coder Block Design                                                 | 26 |

|   |     | 7.4.2 HDL Coder MATLAB Function Block Design                                 | 26 |

|   |     | 7.4.3 HDL Coder MATLAB Function and Block Design                             | 26 |

|   | 7.5 | Results Intel                                                                | 27 |

|   |     | 7.5.1 HDL Coder Block Design                                                 | 28 |

|   |     | 7.5.2 HDL Coder MATLAB Function Block Design                                 | 28 |

|   |     | 7.5.3 HDL Coder MATLAB Function and Block Design                             | 28 |

|   | 7.6 | Chapter Summary                                                              | 28 |

| 8 | Des | ign of Down Sampling Filter Chain                                            | 29 |

|   | 8.1 | Design and Implementation                                                    | 29 |

|   | 8.2 | Synthesis                                                                    | 30 |

|   | 8.3 | Optimization                                                                 | 30 |

|   | 8.4 | Optimization Results Xilinx                                                  | 32 |

|   | 8.5 | Optimization Results Intel                                                   | 33 |

|   | 8.6 | Chapter Summary                                                              | 34 |

|   |     |                                                                              |    |

Elisabeth Pongratz, Roshan Cherian

August 27, 2019

| 9  | Bra  | nched Filter                                 | 36 |

|----|------|----------------------------------------------|----|

|    | 9.1  | Design and Implementation                    | 36 |

|    | 9.2  | Synthesis                                    | 37 |

|    | 9.3  | Optimization                                 | 37 |

|    | 9.4  | Optimization Results                         | 37 |

|    | 9.5  | Chapter Summary                              | 39 |

| 10 | Ove  | erall Analysis and Conclusion                | 40 |

|    | 10.1 | HDL Coder                                    | 40 |

|    | 10.2 | Comparison of the Different Vendors $\hdots$ | 42 |

|    | 10.3 | Methodology                                  | 44 |

|    | 10.4 | Tips and Tricks                              | 45 |

|    | 10.5 | Problems Faced with MATLAB and HDL Coder     | 46 |

|    | 10.6 | Conclusions                                  | 47 |

|    | 10.7 | Future Work                                  | 48 |

| 11 | Ref  | erences                                      | 50 |

| 12 | App  | pendix A                                     | 52 |

|    | 12.1 | Power Meter MATLAB Code                      | 52 |

| 13 | App  | oendix B                                     | 53 |

|    | 13.1 | Power Meter MATLAB Pipelined Code            | 53 |

| 14 | App  | pendix C                                     | 54 |

|    | 14.1 | Power Meter MATLAB Code                      | 54 |

## List of Tables

| 1 | Power meter in XSG                                                                        | 23 |

|---|-------------------------------------------------------------------------------------------|----|

| 2 | Power meter in DSP Builder.                                                               | 23 |

| 3 | Xilinx slack comparison with HDL Coder models and optimizations. $\ . \ .$                | 25 |

| 4 | Intel slack comparison with HDL Coder models and optimizations                            | 27 |

| 5 | Slack results from XSG design and initial HDL Coder design aimed for Xilinx device.       | 32 |

| 6 | Slack results from DSPB design and initial HDL Coder design aimed for<br>Intel device     | 34 |

| 7 | Slack results from XSG design compared with HDL Coder with different optimization options | 38 |

| 8 | Methodologies pros and cons.                                                              | 44 |

## List of Figures

| 1  | Optimized bit reversal [1] $\ldots$                                                       | 16 |

|----|-------------------------------------------------------------------------------------------|----|

| 2  | Code motion. [1]                                                                          | 17 |

| 3  | Power meter block design.                                                                 | 21 |

| 4  | Power meter MATLAB function.                                                              | 21 |

| 5  | Power meter MATLAB functions and block design                                             | 22 |

| 6  | Power meter design in XSG                                                                 | 22 |

| 7  | Power meter design in DSPB                                                                | 23 |

| 8  | Xilinx comparison with HDL Coder models and optimizations. $\hdots$                       | 25 |

| 9  | Intel comparison with HDL Coder models and optimizations. $\hdots$                        | 27 |

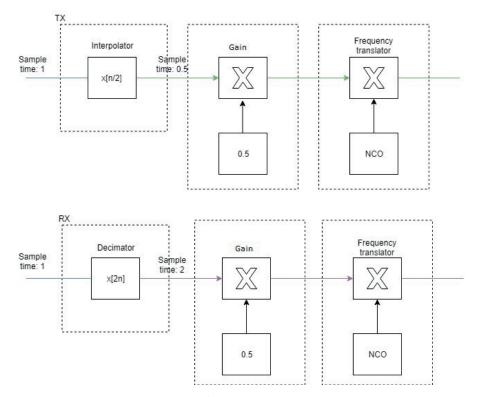

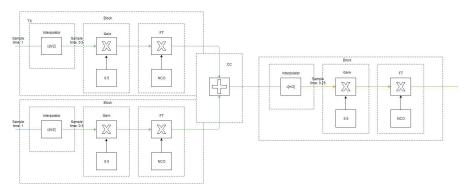

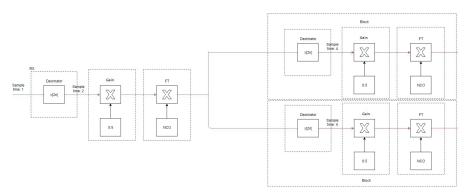

| 10 | One TX and one RX design                                                                  | 30 |

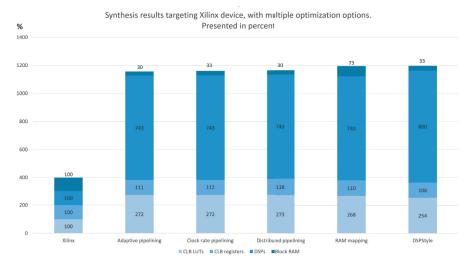

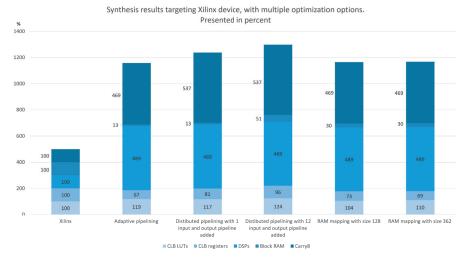

| 11 | Xilinx comparison with HDL Coder models with different optimization options.              | 32 |

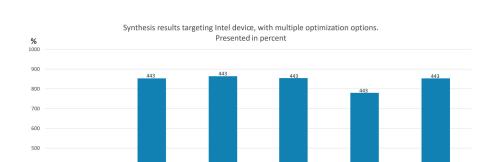

| 12 | Intel comparison with HDL Coder models with different optimization options                | 34 |

| 13 | TX branch                                                                                 | 36 |

| 14 | RX branch.                                                                                | 37 |

| 15 | Xilinx comparison with HDL Coder branched design with different opti-<br>mization options | 38 |

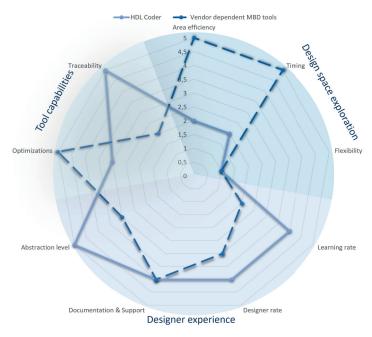

| 16 | Our experience with HDL Coder compared to vendor dependent high level tools               | 42 |

## Acronyms

- ${\bf ALM}\,$  Adaptive Logic Modules.

- **ALUT** Arithmetic LUT.

- ${\bf ASIC}\,$  Application-Specific Integrated Circuit.

- ${\bf CC}\,$  Carrier Combiner.

- ${\bf CLB}\,$  Configurable Logic Block.

- ${\bf CSD}\,$  Canonical Signed Digit.

- **DFE** Digital Front End.

- ${\bf DSP}\,$  Digital Signal Processor.

- FCSD Factored Canonical Signed Digit.

- ${\bf FFT}\,$  Fast Fourier Transform.

- ${\bf FIR}\,$  Finite Impulse Response.

- ${\bf FPGA}\,$  Field-Programmable Gate Array.

- ${\bf FT}\,$  Frequency Translator.

- HDL Hardware Descriptive Language.

- HLT High Level Tool.

- **IIR** Infinite Impulse Response.

- ${\bf IP}\,$  Intellectual Property.

- LUT Look Up Table.

- ${\bf MBD}\,$  Model-Based Design.

- $\mathbf{mux}$  Multiplexer.

- NCO Numerically Controlled Oscillator.

- ${\bf RAM}\,$  Random Access Memory.

- ${\bf R}{\bf X}$  Receiver.

- $\mathbf{T}\mathbf{X}$  Transmitter.

- $\mathbf{VGA}\xspace$ Voltage Gain Amplifier.

## **3** Popular Science Summary

The number of transistors on a silicon chip has doubled every two years as per Moore's law and the design requirements have been exponentially increasing. Wireless systems are also getting more and more complex. With the development of 5G, this has been no exception. This complexity increases the design workload which makes the design flow multiple times longer and puts a lot of pressure on the designer. These complex systems generally contain a mix of DSP algorithms such as FFT's, IIR filters, FIR poly-phase filters. With the advancements in the FPGA technology, designs can be built on them with great flexibility. Since the time to market is critical, the development time window is reducing drastically. This is where High-Level Synthesis (HLS) and Model-Based Design (MBD) tools fit in. MBD is a methodology which lets the designer creates models of the design implementation and promotes the use of the high level synthesis within it to create RTL relatively easily.

HLS tools have been designed to automate and accelerate design by moving manual work on to a higher level. FPGA vendors have come out with high level tools(HLTs) optimized specifically for their hardware and are integrated within the MBD tool Simulink. These tools are vendor specific and the learning curve can be quite steep and a deeper understanding of hardware is needed to use them. One of the problems with this vendor specific approach arises if the same design needs to be ported on to different FPGA vendor platform. This causes the same design to be replicated and re-implemented in the other vendor specific HLT. This procedure is time consuming and requires knowledge of the new tool. One other tool which looks promising and produces vendor independent synthesizable HDL code is HDL Coder provided by MathWorks. In this thesis, Simulink is the MBD tool used along with the HLTs like HDL Coder, Xilinx SysGen and Intel DSP builder.

In this thesis, a few experimental designs of a complex filter chains is done with HDL Coder. HDL Coder like the other architecture based design tools is a HLT that can be used to generate HDL code from Simulink and MATLAB algorithms. The resulting HDL code can be further synthesized into any FPGA. The design and results from HDL coder is compared to the results from same design implemented in vendor dependent tools: Xilinx SysGen (XSG) and Intel DSP Builder(DSPB). All the HLTs are evaluated with a major focus on HDL Coder on the metrics of ease of implementation, RTL produced, design space exploration, resulting speed and area consumption as well as the learning curve.

1

Elisabeth Pongratz, Roshan Cherian

August 27, 2019

## 4 Introduction

Currently, hardware design companies are running several products with several different vendors for which the digital designs are generated separately using vendor specific RTL generation tools. These tools are excellent in generating digital designs quickly compared to the handwritten HDL code.

HDL Coder from MathWorks is a HLT that is used to generate vendor independent HDL code from MATLAB and Simulink. This tool is evaluated in this thesis work and compared with the vendor dependent counterparts. The vendor dependent HLT tools almost always needs additional interconnections, also called as the glue logic which are not available within these blocks and require significant amount of time to design and verify. This results in structurally lowering the level of abstraction of the design. This costs a lot of working hours which could be reduced by reusing these blocks from a local block library which can be effectively done in MATLAB. These blocks have also been identified and HDL supported designs have been designed for use in the future.

HDL Coder can generate HDL for different FPGAs from the standard Simulink library blocks. Thus, in case there are similar requirements for a different FPGA, the designer can switch vendors for the same implementation of the design easily and would not have to redo the design and the verification for it. Since, many industries are increasing its FPGA product development due to its economic standpoint, investigating options to improving efficiency and productivity of development process is worth exploring.

The prior state of the art does not make comparisons between different HLT tools and have previously compared HDL Coder to HLS tools and hand written RTL code. Related thesis works have also set a foundation on how to use the HDL Coder and listed some of the best practices. These have come in handy and made the learning curve for the thesis smooth. Most of the previous work also does not quantify the performance aspects of the tools from the different vendors. This thesis aims to do that and suggest a methodology for a vendor independent use case.

## 4.1 Motivation

The motivation of this Master's thesis is based on the need to explore a performance effective tool to generate vendor independent HDL that could save development time and is comparable to its vendor dependent tools. HDL Coder fit into these tool requirements and is to be evaluated in this thesis where both the efficacy and efficiency of HDL Coder has been explored. A list of best practices and possible solutions to problems is also covered.

There exists vendor specific architecture-level design tools for implementing high performance DSP algorithms for a FPGA. The ones widely used in the industry nowadays are DSPB and XSG. Both of the these tools are vendor specific i.e. work on the FGPA's manufactured by them and operate more on the block level with highly optimized blocks for commonly used sub blocks. These tools are integrated in the Simulink MBD environment and are used seamlessly within this environment to produce designs. However, the optimization methods on the system level are quite limited for these two tools. One other tool used with the Simulink MBD environment available in the industry is HDL Coder which is vendor independent has not been explored much at Ericsson for FPGA prototyping and design. HDL Coder also provides system level optimizations to explore the design space. In this thesis, one of the previously implemented designs on the Xilinx/Intel FPGAs is implemented using HDL Coder and various performance metrics involved with the design are evaluated and possible alternatives have been suggested. It also throws light into design productivity and IP reuse as the design made in HLT tools can be easily ported to new designs.

#### 4.2 State of the Art

There has been prior work on similar topics. The learning from sources [2] and [14] have been used to pave the way for this thesis. The source [2] though a little outdated (2010), shows the flow and contains tips and tricks that can be used by the designer. It also discuses some of the optimization techniques tried by the user to meet the timing constraints. It describes the design and the implementation of software defined radio (SDR) with the HDL Coder based design implemented on Altera Cyclonce II platform. The conclusion for this thesis is that it is easy to understand the programmable logic tools but the result may vary a bit. Source [14] is relatively new (2018) and has taken a similar approach but is comparing the HDL Coder results to hand written HDL code. Valerie Youngmi Sarge claims in this thesis that HDL Coder design offered reasonable performance with greater ability to parameterize a design and easily visualize and re-use portions of an existing design. Traditional forms of hardware description still give a more highly optimized and greater degree of control over pipelining and reset and enable behaviour.

Reference [4] is another example which has compared the Vivado HLS tool with the HDL coder as an HLS tool. The thesis work is done by Gerald Baguma in 2014. It concludes that as a HLS tool Vivado HLS generated more efficient designs, because of it provide more granularity to control of scheduling and allocation, than HDL Coder. This thesis also list the various HLS tools that were available then. Additionally, it is concluded that the HLS tools provided today does not meet the requirements from FPGA/ASIC designers. The thesis is from 2014 and there has been a few updates to HDL Coder since then. There had been some options available then in HDL Coder which have been disabled or discontinued from this version which have been made note of. Also used is the source from 2014 [3] by Mathew S. Allen. This thesis is evaluating the performance of designs using HLT using HDL Coder and hand-written RTL code and the pros and cons of each. His conclusions were that HDL Coder has a high productivity once the tool is understood, though, he proves that it produces inefficient design.

Also a bit out dated (year 2015) is the thesis work for reference [12], made by Joonas Järviluoma. This thesis work is mostly evaluating HDL Coder as a HLS tool. Additionally, he is looking into the generation flow with HDL Coder for writing HDL, as for coding styles and synthesizable RTL code produced.

In the source [15] the people involved have made a comparison between HDL Coder and hand written RTL with the case of methodology and time spent. Their result is positive for HDL Coder, in the manner of time spent, though, negative for the other parameters as area, power consumption and operating speed.

To summarize, the current state of the art gives a brief introduction to HDL Coder and compares the results with HLS tools and handwritten HDL. The tool have also improved ever since and is fairly accepted in the industry with positive case studies and scenarios. There have not been any comparisons so far of the different HLT tools using the MBD workflow and this thesis aims to do that.

## 4.3 Thesis Structure

The new design workflow methodology and tools makes it a requirement to do an elaborate pre-study. The pre-study is made based on the HDL Coder toolbox, tutorials and previous thesis work and related work section 4.2 on the subject.

Chapter 5 gives the background needed to understand this thesis. It explains the current and the proposed workflow. It also gives a brief information of the tools used in this thesis and their optimization techniques. Section 6 provides the information needed to understand the HDL Coder tool that was used.

A design already implemented on the Xilinx and Intel FPGA was given. All of the produced designs in this thesis is done with MATLAB version 2018a and is used within a Linux virtual server based system. This design consists mainly of FIR filters, down samplers, decimators, interpolators and a NCO. Also, MathWorks offers support to assist in the design of optimized filter chains for different vendors. A common subsystem, the power meter, was observed that is present in almost all the designs. This power meter, which can be used across future designs was a good beginning to go through the flow and gain more hands on knowledge of the tool. An understanding of what each subsystem can do and how the logic can be recreated was needed. The power meter flow was documented in chapter 7. Once the experience with the new workflow and tools has been gained then the design of the filter can be created and tested on. This is covered in section 8. Further, a bigger branched design was made to investigate optimizations with a bigger design, see section 9. Further logistic test were done, which is explained in section 6.5.

Once all designs have been created and the optimization of each has been done, evaluation of the HDL Coder tool has been done. Further comparison of the tool with other work flow options, problems faced and work around are also suggested in this topic. This is documented in chapter 10. Also during the project, the time taken was recorded and evaluated to get a rough estimate of the time needed for research and learning so as to find out how much time is needed to get the HDL Coder up and running in terms of working man-hours, this can also be observed in section 10. Additionally, the hours used for optimization also needs to be documented. A summary of the results and this thesis are made in section 10.6. Finally, possible future work within this topic are discussed in the chapter 10.7.

## 5 Background

In this section the background information needed for the thesis is presented. First an explanation of the current methodology used for FPGA based design. Second, the proposed methodology with HDL Coder instead is described. Last, an explanation of the different FPGA fabrics concerning each FPGA.

## 5.1 Digital Front-End

For wireless base stations the Digital Front-End (DFE) is the most vital component. The DFE along with an analog to digital converter handles the path from radio and intermediate frequency process to the digital baseband process. The signal processing is done on a software programmable DSP before the baseband processing can be preformed. Digital signal processing is used because it can in real time reconfigure the radio frequency channels in the base station. Therefore, multiple signal conditions, compensations and limitations to channel non-linear responses can get implemented. [8] The functionality of a DFE can be derived from the characteristics of the input and output signals of the DFE. The output is a digital signal with a specific sample rate controlled by the DFE. Lastly, this signal can then be baseband processed. [9]

## 5.2 Current Methodology - Vendor Specific Workflow

The current methodology of FPGA based design go through the specific steps, as follows. First requirements for a particular design are set in a specification. Then the functionality is split into various functional blocks. These functional blocks require their own block specification from this a reference model for this design is made in Simulink. If the target FPGA is a Xilinx based device, the design is done in SysGen with Simulink and compared with a reference model in Simulink. The delays in the reference model are then adjusted to account for latency to make it cycle and bit accurate with respect to the reference model. Suppose if the same design is to be implemented on the Intel FPGA device then the same design has to be redesigned using DSP Builder because the earlier design is not valid in this case. Additionally, the delays are adjusted to make this design cycle and bit accurate as in the previous case. When the design is working or during the design time some optimizations has to be done. [15]

This methodology is time consuming and inefficient, involves repetition of the design process and needs a person to be skilled in all the three software working with the project. Therefore, there might be a need for more than one person working with the project with each having expertise in Simulink, XSG and Intel DSPB in order to make the designs work.

## 5.3 Proposed Methodology - Vendor Agnostic Workflow

The specifications for the design and blocks is set and the functionality in each block is decided. From these specification the designer can create a reference model in Simulink. The reference model from the current methodology can be directly taken and a new model can be made using only blocks supported by HDL Coder and/or HDL Coder MATLAB function blocks. The design then gets optimized to fit the requirements. Lastly, this model can generate HDL for both Xilinx and Intel FPGAs. In this methodology there is no need to redesign the same IP which saves a considerable amount of time. Moreover, the tools is known for its fast prototyping targeting toward FPGAs.

### 5.3.1 High Level Synthesis

HLS tools has provided the possibility of software programmers to target hardware, FPGA and ASICs more rapidly. Functionality or behavioural logic is written in software which then by the tool can be turned into RTL code, VHDL or Verilog. The tools provide scheduling, allocation of the logic onto the hardware and in most cases the tools automatically generate cycle-by-cycle details for the implementation. This essentially means that the designer do not have to be an expert in those fields and can focus on getting the functionality implemented. This gives us a tool with a higher level of abstraction than designer's hand written RTL.

Below are some of the many HLS vendors available today. They support different programming languages and provide different HDL outputs (RTL, verilog, VHDL or systemC) and constraints as fixed or floating point.[13]

- Bambu from PoliMi

- Stratus from Cadence

- C-to-Silicon from Cadence Design Systems

- Catapult C from Mentor Graphics

- Intel High Level Synthesis Compiler from Intel FPGA

- Synphony C from Synopsys

- Vivado HLS from Xilinx

- HDL Coder from MathWorks

As a HLS tool, HDL Coder workflow can produce results comparable with hand coding, given that the tool and it's optimization settings are correctly used. There is a possibility to write the functionality in a MATLAB function block and add it in the design and HDL Coder will provide the RTL for that logic. This method is much faster than the HLS tools available in the market. A HLS tool automatically takes care of the scheduling, resource allocation and more, which normally would take a lot of time for the person working with it. Though, this include that the person would have to trust the tool which

comes with continuous use and expect it to automatically provide somewhat good results. Otherwise, HDL Coder provide good traceability between the RTL code produced and the MATLAB function block. It is also possible to use HDL Coder to produce HDL Code from Mealy and Moore State Machines designed in Simulink with Stateflow.[13]

#### 5.3.2 High Level Tools - HDL Code Generation

The core principle of MBD workflow is the capability of using a model in the design process to simulate and verify the functionality before the creating the real system which has been explored with the HLT listed below. In this thesis, Simulink from MathWorks is used as the MBD tool. LabVIEW from National Instruments is one another alternative but does not have any support from vendor specific HLT. Vendor dependent HLT are highly optimized for their own hardware especially for filter chains because the blocks are hardwired. HDL Coder on the other hand, considers the whole design and analyzes the functionality and then proceeds with the implementation.

• Xilinx System Generator

Xilinx System Generator XSG is high-level software tool that enables the use of MATLAB/Simulink environment to create and verify hardware designs for Xilinx FPGAs quickly and easily. It provides a library of Simulink blocks bit and cycle accurate modelling for arithmetic and logic functions, memories, and DSP functions. It also includes a code generator that automatically generates HDL code from the created model. Generated HDL code can be synthesized and implemented in the Xilinx FPGAs. The XSG blocks are like standard Simulink blocks except that they can operate only in discrete-time.[17]

• Intel DSP Builder

DSP Builder (DSPB) for Intel FPGAs is a digital signal processing (DSP) design tool that allows push-button HDL generation of DSP algorithms directly from the MathWorks Simulink environment on Intel FPGAs. The tool generates high quality, synthesizable VHDL/Verilog code from MATLAB functions and Simulink models. The generated RTL code can be used for Intel FPGA programming. DSP Builder for Intel FPGAs is widely used in radar designs, wireless and wireline communication designs, medical imaging, and motor control applications.

DSP Builder for Intel FPGAs adds additional library blocks alongside existing Simulink libraries with DSP Builder for Intel FPGAs (Advanced Blockset) and DSP Builder for Intel FPGAs (Standard Blockset).[11]

• MathWorks HDL Coder

HDL Coder generates portable, synthesizable Verilog and VHDL code from MAT-LAB functions, Simulink models, and Stateflow charts. The generated HDL code can be used for FPGA programming or ASIC prototyping and design. It also supports Hardware/Software co-design targeting SoC targets like Xilinx Zynq and Intel SoC. In this case both HDL and C code for embedded CPUs are generated.

HDL Coder provides a workflow advisor that automates the programming of Xilinx, Microsemi, and Intel FPGAs. You can control HDL architecture and implementation, highlight critical paths, and generate hardware resource utilization estimates. HDL Coder provides traceability between your Simulink model and the generated Verilog and VHDL code, enabling code verification for high-integrity applications adhering to DO-254 and other standards.

HDL Coder produces vendor independent RTL. Hence the generated RTL can be ported to FPGAs of any platform and even an ASIC based on the design requirements. This allows the same design to be reused for future projects and also enables ease to change platforms when necessary. The level of detailing in the vendor dependent tools is a lot and requires deep knowledge of the hardware to implement them. Whereas, in HDL Coder, there are limited options available for block configuration. This drastically reduces the design time. Moreover HDL Coder is highly recommended for fast FPGA prototyping.[7]

## 5.4 FPGA Fabric

The overview of the resources utilized by the different vendor is given below and the terms are explained briefly. Since this thesis work focuses on porting the design on a FPGA these terms are important to understand the resource utilization metrics mentioned in the further chapters.

The synthesis tool by the vendor uses the RTL produced from the HLTs and maps it onto the FPGA fabric. Since the FPGA fabric is different for different hardware vendors, the RTL written for a particular FPGA design will not map well with any other FPGA fabric leading to inefficient resource usage. For example, to convert from a Xilinx to Intel design flow all the Xilinx primitives and Xilinx specific IP's needs to be replaced by the Intel ones. Also, because the standard multipliers sizes within DSP are different across devices. HDL Coder creates the RTL based on the synthesis tool selected and thus maps the same design on different FPGA's. The design generated in this thesis are designed to be implemented on the Xilinx Ultrascale+ xczu15eg-ffvb1156-2-i device and the Intel Arria 10 AX115R3F40I2LG.

## 5.4.1 Xilinx

#### Configurable logic blocks (CLB)

Every CLB in the Zynq Ultra-scale+ architecture contains one slice with 8 six-input LUTs and 16 storage elements. The LUTs are organized as a column with an 8-bit carry chain per CLB, called CARRY8. Wide-function multiplexers combine LUTs to create any function of seven to nine inputs, or some functions of up to 55 inputs. SLICEL is the name used to describe CLB slices that support these functions, where the L is for logic. These are mapped as CLB LUTs by the synthesis tool. The LUTs in a SLICEM, where the M is for memory, can be configured as a look-up table, 64-bit distributed RAM, or a 32-bit shift register. These are mapped as CLB Registers by the synthesis tool.

#### Block RAM

The block RAM in Zynq UltraScale+ architecture-based devices stores up to 36 Kbits of data and can be configured as either two independent 18 Kb RAMs, or one 36 Kb RAM.

## Arithemetic DSPs

The Zynq UltraScale+ devices have many dedicated low-power DSP slices, combining high speed with small size while retaining system design flexibility. The DSP slice in the UltraScale+ architecture is defined using the DSP48E2 primitive and the slice is referred to as either DSP or DSP48E2 by the synthesis tool. Each DSP48E2 slice has a two-input multiplier followed by multiplexers and a four-input adder/subtracter/accumulator. The DSP48E2 multiplier has asymmetric inputs and accepts an 18-bit two's complement operand and a 27-bit two's complement operand. The multiplier stage produces a 45-bit two's complement result in the form of two partial products. These partial products are sign-extended to 48 bits in the X multiplexer and Y multiplexer and fed into four-input adder for final summation. This results in a 45-bit multiplier is used, the adder effectively becomes a three-input adder. [18]

## 5.4.2 Intel

### **Combinational ALUT:**

Combinational ALUT is used to indicate half-Adaptive logic moduleALMs used in the design. The ALM consists of 8 input fracturable look-up table with four dedicated registers.

#### Dedicated logic registers:

Dedicated Logic Registers refer to the four registers in the ALM, these are dedicated to being registers.

Together, the combinational ALUT's and dedicated logic registers form an ALM in the Intel Arria 10. The Arria 10 uses an enhanced 8-input ALM with 4 registers and they are grouped as combinational ALUT.

## Block memory bits:

The Intel Arria 10 devices contain two types of memory blocks: MLAB and M20K (blocks of dedicated memory resources). The block memory indicates the number of bits used by the design in both the above stated memories.

## DSP blocks:

The Intel Arria 10 variable precision DSP blocks support fixed-point arithmetic and floating-point arithmetic. It could map two  $18 \ge 19$  multipliers or one  $27 \ge 27$  multiplier per DSP block. [10]

#### 5.5 Chapter Summary

This chapter provides the background on the design methodologies currently used in Ericsson for a model based design workflow with vendor dependent tools. This can be reduced by using HDL Coder workflow which is presented as the proposed workflow. This eliminates the re-design time to target a different vendor. This chapter also presents the different FPGA fabric and terminologies covered in the thesis.

## 6 MathWorks HDL Coder

HDL Coder from MathWorks embedded in the MATLAB/Simulink environment allows a designer to generate synthesizable HDL code for FPGA and ASIC implementations in the following steps:

- Build a model of the design using a combination of MATLAB code, Simulink and State flow charts.

- Simulate and check behaviour.

- Make the model HDL compliant.

- Convert to fixed point if needed.

- Generate HDL Code and synthesize.

- Optimize and iterate the design to meet area-speed objectives.

- Generate the design using the integrated HDL Workflow Advisor for MATLAB and Simulink targeting different vendors.

- Verify the generated code using HDL verifier.<sup>1</sup>

The HDL Coder is basically a compiler which translates the Simulink model to a data and control flow intermediate representation and performs many structural optimizations to produce the RTL. Whereas for the HDL Coder workflow, the code is converted to a control flow representation and then this goes through the data flow graph conversion before the structural optimization kicks in. Once the model is designed as per specifications, design space exploration can be done on them. The design points can be check pointed using the commands *hdlsaveparams* and *hdlrestoreparams*. The workflow advisor also helps to anotate the model with the synthesis results and helps you in further analysis.[5]

## 6.1 HDL Supported Blocks

HDL Coder can generate code from algorithms built using the HDL Coder library of blocks. These blocks are compatible with HDL Code generation and pre-configured with HDL-friendly settings. The HDL Coder library blocks come with Simulink, so you can share your models and collaborate with colleagues who may not have access to HDL Coder. Sub-libraries such as *HDL RAMs* and *HDL Subsystems* provide blocks specific to HDL applications, e.g. RAMs, and subsystems with synchronous enable/reset control inputs. Additional blocks for signal processing, communications and computer vision are also available. Apart from these toolboxes, HDL Coder also supports Stateflow. This allows state charts, state transition table and truth table to be implemented on HDL Coder.

<sup>&</sup>lt;sup>1</sup>The HDL Verifier is not within the scope of this thesis work.

In HDL Coder, it is also possible to place a MATLAB Function block in which an algorithm can be written and RTL code can be produced provided the supported MATLAB HDL functions and constructs are used. When there is a need to create control logic that is not available in standard Simulink blocks but do not want to put the logic together with smaller adders or products. For instance an if-else mux or a simple finite state machine, you can use a MATLAB Function block embedded in the Simulink model. This is an easy way to create custom logic using MATLAB but integrated with the algorithm.

## 6.2 Design Considerations

#### Reset

There is no need to consider the resets and enables in the design as HDL Coder takes care of it internally. While a synthesis tool can faithfully implement either synchronous or asynchronous reset logic, matching the reset type to the underlying FPGA architecture will result in better resource utilization and performance. It is very important that the proper reset is selected as a improper reset selection can lead to poor and inefficient hardware mapping. Following are the reset that should be used based on the design target.

Xilinx -> Synchronous Intel -> Asynchronous

#### Multi-rate modelling

Multi-rate modeling is possible but only with the Simulink HDL flow. The sample rates are shown with different coloured signals. The timing logic for different rates are automatically taken care of by HDL Coder. Additionally, no explicit clock system is needed. HDL Coder creates a timing controller based on the selected clock input selection. If a single clock system is selected for a single rate design, one sample time maps to one clock cycle in HDL, whereas, for a multi-rate model fastest sample time maps to one clock cycle in HDL. Blocks operating at a slower sample time have the same clock in HDL but gated with different clock enable based on the rate it is operating.

#### Block design

Functions are implemented as smaller blocks and placed inside subsystem which enable ease in design. Each subsystem has some parameters and optimization options. Some parameters are set as *Inherit* by default, this means that it is inherited by the hierarchy above. This is an important part in optimizing the design.

#### RTL code

The RTL code can be produced in VHDL and in Verilog. One unique thing about HDL coder is that it produces code-to-model and model-to-code traceabilty. This enables designers to move through their models seamlessly from requirements to HDL code, while maintaining the capability to add legacy code to the design. Additionally, HDL Coder creates different files in the RTL code for different subsystem which makes it easily accessible and readable. Thus, it can be good to make individual subsystems for big functionality.

#### Data types

If the model designed is using floating point data types, the MATLAB Fixed-Point

Designer from MathWorks can be used for changing the design to a fixed point one which is needed to generate the HDL code using HDL Coder toolbox. Single precision floating point is supported by HDL Coder though the use of Native Floating Point. When simulating the model more precision is obtained when floating points are used but since efficient and highly optimized HDL designs are needed it is more often converted to fixed point design to be implemented on the hardware. In HDL Coder a mix of floating point and fixed point is possible. [7]

## 6.3 HDL Workflow Advisor

The tool also seamlessly integrates the selected FGPA synthesis tools and create projects and can run the whole synthesis/implementation from within MATLAB. The HDL Workflow Advisor checks if the model is compatible for HDL code generation from HDL Coder and generate vendor independent HDL. Along with the HDL code, it can also generate HDL testbench and a co-simulation model. It is possible to run synthesis and implementation for a vendor specific FPGA the design could target. Two of the possible vendors that is being evaluated by this thesis and the tool can target are Xilinx Vivado and Intel Quartus. HDL Workflow Advisor generates the RTL for a system or subsystem then creates a project for the selected vendor. It is also possible to get the results of the synthesis and implementation runs in the Workflow advisor without launching the synthesis tool manually. Which makes it easier to use and compare. The project can be opened from within the Workflow Advisor and all the intricate details can be obtained. The settings for the parameters and the setup can be extracted or another setup can be imported in the Workflow adviser.

#### 6.4 Optimization Options

HDL Coder offers several point and click optimisations that can be applied across the whole design, and it is very important that one has the understanding of what each change does before using it. HDL compatible blocks, subsystem or systems have additionally HDL block properties. These are instrumental in optimizing the design and exploring the design space.

A entire model properties can be adjusted using the HDL coder properties. Following are the list of HDL Coder optimizations on system level that are good to know to understand the tool better. The general optimization options are:

• Balance Delays

When certain optimisations such as pipelining or resource sharing are enabled, or specify certain block implementations and code is generated, HDL Coder introduces pipeline delays along certain signal paths in your model. The code generator detects these pipeline delays introduced along one path and then inserts matching delays on other paths.

• Map pipeline delays to RAM Map pipeline registers in the generated HDL code to RAM. Certain speed or area optimisations such as pipelining and resource sharing, or specify certain block implementations that can insert pipeline registers in the generated HDL code. Save area on the target device by mapping these pipeline registers to RAM.

• Transform non zero initial value delay

This option optimizes delay blocks with non-zero initial condition. By using this transformation, HDL Coder can perform optimisations such as sharing, distributed pipelining, and clock-rate pipelining more effectively, and prevent an assertion from being triggered in the validation model.

• Multiplier partitioning threshold

This parameter specifies the maximum input bit width for a multiplier. If at least one of the inputs to the multiplier has a bit width greater than the threshold value, the code generator splits the multiplier into smaller multipliers. To improve hardware mapping results, set the multiplier partitioning threshold to the input bit width of the DSP or multiplier hardware on your target device.

The pipeline optimization options are:

• Hierarchical distributed pipelining

Hierarchical distributed pipelining extends the scope of distributed pipelining by distributing delays across subsystem hierarchies. This optimization moves the delays within a subsystem while preserving the hierarchy. It is used to reduce the timing, slack and latency of the design. This parameter within optimization decrease the slack by inserting pipeline registers in the critical paths within the subsystem.

• Hierarchical Distributed pipelining priority

Numerical integrity:

This option uses a conservative retiming algorithm that does not move registers across a component if the functional equivalence to the original design is unknown. Performance:

This option uses a more aggressive re-timing algorithm that moves registers across a component even if the modified design's functional equivalence to the original design is unknown.

• Clock-rate pipelining

If your design contains multicycle paths, use clock-rate pipelining to insert pipeline registers at a clock rate that is faster than the data rate. This optimization improves the clock frequency and reduces the area usage without introducing additional latency. Clock-rate pipelining does not affect existing design delays in your model.

• Adaptive pipelining

This inserts pipeline registers to the blocks in your design, reduce the area usage, and maximize the achievable clock frequency on the target FPGA device. Adaptive pipelining makes the tool inserts pipelines between arithmetic operations, when rounding or saturation is used and after a down sample and transition block. Additionally, pipelines get added within LUTs, multipliers and rate change blocks. [7] The last optimizing option is the the resource sharing options. The requirement for sharing factor between blocks is that [4]:

- Data types of their inputs and outputs are identical.

- Block parameter settings are identical.

- HDL block properties are identical.

The resource sharing options are:

• Share Adders

Enable this parameter to share adders with the resource sharing optimization. Resource sharing identifies addition and summation blocks in your design and replaces them with a single block in the hardware. This optimization saves area on the target FPGA device.

Similar options are there for the multipliers, multiply blocks, atomic subsystems, gain blocks, MATLAB function blocks and floating point IP's. There are different requirements for different types of blocks which is described by Mathworks. The resource sharing options impacts the frequency of operation and thereby timing of the system, which has to be kept in consideration. The target frequency would be the frequency it is synthesized multiplied by the sharing factor.

The use of sharing factor is to reduce the amount of hardware components. For example when multiple multipliers are used then each multiplier can be mapped to DSPs on the device, depending on options for the design. This is relevant for devices with limited amount of DSPs on the board. With a sharing factor, a rise of registers used can be predicted, but most often FPGA devices have much more registers available than amount of DSPs. [6].

The adaptive pipelining and balance delays are enabled by default. The default design thus has optimizations enabled due to adaptive pipelining and delay balancing and the latency due the same have been considered. HDL Coder offers a variety of block level optimizations and varies between different blocks. The list is quite extensive and all cannot be covered here. The ones used in this thesis are as follows:

#### • Hierarchy flattening:

Hierarchy flattening enables you to remove subsystem hierarchy from the HDL code generated from your design. The HDL Coder considers blocks within a flattened subsystem to be at the same level of hierarchy, and no longer grouped into separate subsystems. This consideration allows the coder to reorganize blocks for optimization across the original hierarchical boundaries, while preserving functionality.

• DSPStyle:

DSPStyle enables you to generate code that includes synthesis attributes for multiplier mapping in your design. You can choose whether to map a particular block's multipliers to DSPs or logic in hardware. • UseRAM:

The UseRAM implementation parameter enables using RAM-based mapping for a block instead of mapping to a shift register.

The above stated system level and block level optimization options, where ever applicable have been used in this thesis. The optimizations for XSG takes place more on a block level and the designer needs to have a high level of understanding for tuning these parameters. With block level optimizations the configurations of for example a bigger FIR filter or a small adder, these configurations vary the synthesis results for the specific block. There are also a lot of options for the designer to choose from. Moreover, system level optimizations are not present and the designer has to take care of them manually. System level optimization effects many blocks within a system, for example pipelining, this will result in synthesis changes on a system level. Different configurations has different advantages. DSPB also have similar optimizations as XSG with the exception that a system or a subsystem can be scheduled for a certain number of clock cycles.

## 6.5 Logic Tests

The HDL Coder has two different workflows: Simulink HDL workflow and MATLAB HDL workflow. The Simulink HDL workflow can be equated to the HLS tools XSG and DSPB. The subsystems are implemented more or less like IP's and RTL are created for each of them separately unless specified otherwise. The blocks within the subsystem generate lines of code which is one of the reasons the code is traceable to the block level. The RTL code generated is dynamically generated in HDL Coder and is much cleaner and understandable compared to the other HLT. The various compiler optimization techniques have been presented below and the results for both workflows have been included. In these various techniques used to check efficient hardware generation [1].

## 6.5.1 Hardware generation transformation tests

#### Bit width analysis test:

HDL Coder does bit width analysis automatically if the designer wants. It is also possible to use the Fixed-Point Designer to determine the bit widths of all the signals in the design. This can be used to avoid complexities like overflows, bit growth effects, etc where a lot of design time is spent to ensure that these do not cause problems in the design. The designer can also choose to change the assigned bit width by forcing a specified bit width in the signal attributes of the block. On updating the model, the bit types are recalculated and updated.

#### Bit reversal test:

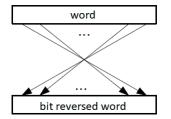

As for testing bit-level optimization a four bit reversal implementation was made using the HDL supported blocks. The inputs are sliced to extract each bit and concatenated to give a reversed four bit result. The code generated uses the same approach as the described in the model. The input is first sliced and then the outputs of the slices are then concatenated in RTL using the & operator. There is also a MATLAB function block example provided by MATLAB which reverses a 32 bit input. The code declares constants and performs a series of bit operations for getting the reversed result which generates unnecessary complicated hardware. The optimal implementation would have been to use wires between the inputs and the outputs as in 1.

Figure 1: Optimized bit reversal [1]

## Multiply/divide by 0,+1,-1 and Operator Strength Reduction (OSR) techniques:

There are two options to go by with this design. Either to use a product block or to use the gain block. The Simulink HDL Coder workflow as mentioned earlier generates lines of code and hence the product block is always interpreted as is and irrespective of any number you multiply with, the workflow will generate constants and multiply it with the inputs. There is an exception here that the product block is supported with this optimization in the the native floating point mode if the single data type is used but not for other types of inputs. The other option is to use the gain block which does provide the same functionality and generates more optimized HDL code. There is also an option of changing the block properties 'ConstMultiplierOptimization' to CSD or FCSD which replaces multiplier operations with additions of partial products produced by CSD or factored CSD implementation. The MATLAB function block has similar optimization options in its block properties and generates similar code based on the inputs assigned to it. The optimal way in implementing these techniques if it is multiplied by zero would be not to generate any hardware, a wire in case its multiplied by one and taking the two's complement of the number in the case it is multiplied by minus one.

### Add with 0 test:

Both workflows produce a constant and add them to the input using a adder. This is a poor implementation but in order to provide traceability this has to be done. It is also important to note that this operation should not be performed by the designer as it does not really make an sense to do it. The optimal implementation in this case would be a wire.

#### Constant folding test:

If there is an expression declared with constants, this technique computes the expression and directly uses the computed values wherever it is declared. Both workflows make use of constant unfolding and use the result of the constant equation in the generated RTL code. This technique works as expected and provides constants in the generated HDL code.

## Common Sub-expression elimination test:

In this technique, the common sub-expressions are found out and assigned to a temporary

instance instead of computing the common sub-expression for each iteration. For eg,  $a = b \times c + d$  followed by  $a = b \times c + f$  does the computation  $b \times c$  twice. This can be reduced by declaring a temporary variable t as  $t = b \times c$  followed by  $a = t \times d$  and c = t + f. The MATLAB HDL workflows do not support common sub-expression elimination. As for the Simulink HDL workflow, this can be done directly at the model level by connecting the result from  $b \times c$  to the other inputs.

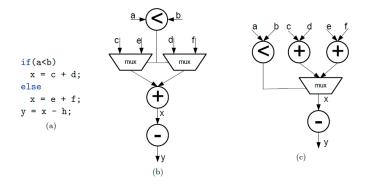

#### Code motion test:

Code motion is a technique which changes the order of execution of instruction in a program. It performs speculation and tries to shorten the critical path by adding registers. Since Simulink HDL workflow is a MBD approach, the hardware generated resembles the

Figure 2: Code motion. [1]

model and for this optimization to take place the optimized design should be designed. As for the MATLAB HDL workflow, the compiler does not handle this optimization and produces hardware as (b) in the above figure, 2. The optimized hardware would be as shown in figure (c) which has a low critical path compared to (b).

### Constant Propagation test:

This can be understood from the equations x = 4 and y = x + 7. This should be simplified by the compiler by assigning y = 11. In this way, the constant propagates as and when it occurs next. The Simulink HDL flow similar to the previous cases, the optimized model needs to be designed. Optionally, the workspace variables can be used for defining constants and used in the blocks. The MATLAB HDL flow handles this case and makes use of the propagated constant in the HDL generated.

### Loop unrolling test:

Two different loop optimization supported in HDL Coder are: Loop streaming and loop unrolling. The Simulink HDL workflow, by default unrolls the hardware. For example, if given a vector input, HDL Coder unrolls the vector and repeats the hardware for each index in the vector. This can be changed if the streaming option is enabled and a streaming factor is mentioned.

The MATLAB HDL workflow the unroll option does not create a control algorithm as expected but instead produces the same hardware as in the case of the rolled loop. The only difference is in terms of the HDL code produced, the unroll option when turned on, has individual assign statements for each output whereas, in the other case, for generate is used to produce the HDL code.

## 6.5.2 Analysis of the above tests

Both the workflows have limited support for efficient hardware generation and can not be really classified as an HLS tool which offers highly efficient RTL. Traceability in HDL Coder comes at a cost and in most cases end up producing inefficient HDL code and relies on the designer to create an optimized design.

There is lack of integration of some of the feature tests conducted above in HDL Coder, as the RTL generated from these tools is often below par in performance in comparison with a hand written, fine tunable RTL code. The results from HDL Coder depends on the design and the experience of the designer with the tool. The design should be broken down into small blocks and these blocks should be optimized for the target hardware and then integrated together to get the optimal results. The difference in performance can be reduced by expressing the design in a more detailed manner but this lowers the level of abstraction considerably. The results from this section should be considered while designing the designs presented until the tools get updated and incorporates these features in them.

## 6.6 Reports

To check the resulting model and to investigate the result of the optimization methods it is a good idea to go through the generated reports and check the generated model. The reports that get generated by HDL Coder are traceability, high level resource utilization, high level timing report, optimization report and web view model. The optimization options in the generated report shows the optimizations that were successful and the generated model shows all the added pipelines and the matched delays. The generated model can be found in the project folder created.

## 6.7 Resource Mapping

This is one of the most important aspects to be considered while designing the system especially for this thesis as this is a major point of concern. The mapped hardware should be efficient and the resource used during the design should map effectively to the FPGA fabric. The block level optimizations UseRAM and DSPStyle have been used wherever applicable to get the most from the DSP resources of the FPGA.

1. RAM mapping

One of the most common sources of area inefficiency when first targeting hardware is large register banks. Often these can be more efficiently implemented on the FPGA device by targeting its block RAM resources.

#### 2. DSP mapping

In addition to multipliers, DSP blocks in modern FPGA devices provide many other dedicated resources, such as adders and pipeline registers, for high-performance signal processing computations. The following guidelines will help you leverage those resources for designs containing common DSP operations. [7]

• Reset:

Use the global reset type, or set the HDL property *ResetType* to none for multiplier or adder pipeline registers. Using an incorrect reset type prevents DSP block resources from being fully utilized.

## • Multiplier word size:

18 x 18-bit multiplication is a good starting point, as it usually maps well into FPGA DSP blocks. However, the architecture of the target device needs to be checked to maximize the built-in multiplier resources. When a multiplication exceeds the built-in word size, the synthesis tool either implements the extra bits in FPGA fabric, or splits the operation into multiple DSP blocks, resulting in lower speed and higher area.

## • Fixed point settings:

Use full-precision fixed-point for any multiply/add operations, add output pipeline registers, and then perform the necessary rounding/saturation after the final output register with a *Data Type Conversion block*. Alternatively, use rounding/saturation on a product/add block, and let HDL Coder automatically insert pipeline registers between the multiplier and output logic via *Adaptive Pipelining*.

## • Pipeline registers:

Using all available pipeline registers in the DSP blocks will give you highest clock frequency at the expense of increased latency. On the other hand, exceeding available pipeline registers may prevent synthesis tools from mapping all math operations within the DSP, resulting in sub-optimal area and timing performance. Choose pipelining level that matches the DSP architecture of your target device and your hardware requirements; adjust them as needed based on synthesis results.

## 6.8 Chapter Summary

In this chapter, literature on the HDL Coder is collected and presented in a way a person with a basic knowledge of hardware can use Simulink with HDL Coder in a smooth and hassle free way.

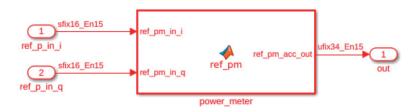

## 7 Experimental Design, Power Meter

The purpose of this experimental design was to introduce ourselves with HDL Coder. Firstly, Simulink to HDL code workflow was used to learn how to combine HDL Coder blocks to get the required functionality. Once a bit accurate and cycle accurate functionality was achieved, synthesis of the design was done and the results were compared in terms of size, timing and RTL readability. Later the optimization options that can be implemented on the design were evaluated.

To do the comparison, both the HDL Coder designs were synthesized for the selected devices using Xilinx Vivado and Intel Quartus. Once the functionality is verified both flows, the designs should be optimized for timing and area. The new values obtained can be compared with the same designs in XSG and DSPB. Using HDL Coder, one single model can be used to target both vendors, then synthesis can be done independently in Vivado or Quartus. The experimental design test are all run with a frequency of 122.88 MHz which is the frequency of operation. For achieving the best resource mapping with the tool the parameter for reset type was put to *Synchronous* for the HDL Coder designs that target Xilinx vendor and *Asynchronous* for the Intel vendor designs.

## 7.1 Design and Implementation

Power meter is used for measuring the power of the I-Q data in a design. When the transmitter or receiver is being used, the power meter makes it easier to investigate the power used in the circuit. It presents the real power magnitude from signals. The magnitude can be calculated with the equation below.

$$M = (a^2 + b^2)$$

This power meter has two input signals apart from the clock, enable and reset. The signals are the I and Q data from the TX or RX and are the signals to be squared, added and accumulated, The reset, clock and enable signals are self explanatory. The output of the design is the result signal. In the magnitude equation, the a and b are the input signals. The square is made with two multipliers, one for each signal. The input to both the multipliers is the same signal which results in the square. The output from the multipliers gets added. The result gets accumulated with the previous result. The whole system is an enabled system. The output gets cleared when the reset goes high.

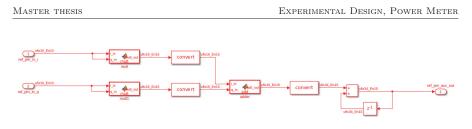

This functionality was used as an inspiration for the first HDL Coder design to understand the workflow and was compared to its XSG and DSPB workflow tools. Simulations were done to confirm that the design gives the correct outputs. One of the major differences between a design done in XSG/DSPB and a design in HDL Coder is that the enable and reset is done automatically, as mentioned in part 6. Therefore the enable and reset signals used in this power meter is not included in the block design but will end up in the RTL code generated. Therefore, the amount of pins into the Simulink block only has to be the two inputs that is to be multiplied, as seen in figure 3.

Figure 3: Power meter block design.

A HDL Coder design was made using the MATLAB HDL workflow to evaluate how does it compare to the Simulink HDL workflow. A MATLAB code as a function was written and the results were compared. The design of a power meter with only a MATLAB Function block within the Simulink environment can be seen in figure 4, and the MATLAB code can be viewed in appendix 12.1. The function arguments and the return type signifies the inputs and the outputs to the design respectively. Since the design is to be done in fixed point, the *fi* method is used to define the data types used in the design. The registers in the design can modelled using the *persistent* keyword. There are other methods to model registers as well and they are *coder.hdl.pipeline()* and *dsp.Delay(expr,no\_of\_registers)*. The code is written so that the data flow can be visualized and only the final output is given to a register.

Figure 4: Power meter MATLAB function.

To investigate the design options further, a model of the power meter was made with both HDL Coder blocks and MATLAB function blocks within the Simulink environment. MATLAB code for the multipliers and adders were written and were replaced with these MATLAB function blocks in the design, see figure 5. This was done to investigate how both designs work together. The code for the multipliers and adders are presented in appendix 14. The rest of the blocks and settings for this design is the same as the first design, the block design.

Figure 5: Power meter MATLAB functions and block design.

## 7.2 Synthesis

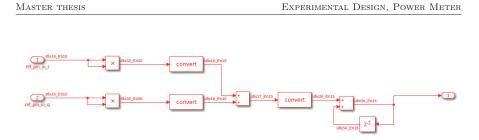

To synthesize the HDL Coder designs, the HDL Workflow Advisor was used. Also, to check if the design is compatible for HDL Coder the commands *checkhdl('path')* and *makehdl('path')* can be used on MATLAB command window. The Workflow Advisor, as mentioned in section 6.3, can produce RTL, synthesis and implementation reports according to the synthesis tools specified in Workflow Advisor. With this tool, it becomes possible to receive various reports from both HDL Coder tool and the ones produced from the selected vendor. Therefore, to compare the results from the power meter in Xilinx the same synthesis tool Vivado was applied with the same device.

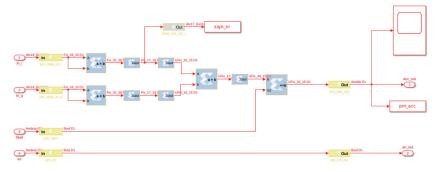

Figure 6: Power meter design in XSG.

Moreover, the synthesis is run with the corresponding Xilinx and Intel power meter designs. For the Xilinx design made using XSG the HDL netlist is extracted which also creates a project in Vivado. The complete design can be viewed in figure 6. The reports are generated to view the timing and the resource utilization for the selected FPGA. The results from the power meter in Xilinx measured with a frequency of 122.88 MHz is shown in table 1.

The RTL produced from XSG is exported as a HDL netlist and the HDL code is barely readable or understandable. The different blocks used in the design generates complicated IP's and the HDL for the power meter shows just the port mapping to these IP's. Moreover, the code can not be observed to be a general power meter code.

The Intel design of the power meter can be viewed in figure 7. In comparison to the HDL

Elisabeth Pongratz, Roshan Cherian

Master thesis

| Resource Summary $(\#)$ | XSG design |

|-------------------------|------------|

| CLB LUTs                | 41         |

| CLB Registers           | 54         |

| DSPs                    | 2          |

| Carry8                  | 8          |

| Block RAM Tile          | 0          |

| Timing Summary (ns)     |            |

| Requirement             | 8.138      |

| Data Path Delay         | 4.053      |

| Slack                   | 4.085      |

Table 1: Power meter in XSG

Coder model there is not that much extra blocks needed. The prior effect is the two extra inputs and input and output blocks for the system. In DSPB, it is possible to put an extra function block to get a scheduled architecture, that is for balancing and insert delays where it is most optimized. For the Intel design made using DSPB the project, no reports need to be generated, since DSP Builder within Simulink can keep track of utilization and timing as and when the block are added to the design. The results for the power meter in Intel run with the same frequency as the Xilinx design can be viewed in table 2.

Figure 7: Power meter design in DSPB.

| Resource Summary(#)  | DSPB design |

|----------------------|-------------|

| Combinational ALUTs  | 66          |

| Dedicated logic regs | 167         |

| Block memory bits    | 0           |

| DSP blocks           | 2           |

| Timing Summary (ns)  |             |

| Period               | 8.138       |

| Worst case slack:    |             |

| Setup slack          | 5.702       |

| Hold slack           | 0.038       |

|                      |             |

Table 2: Power meter in DSP Builder.

The RTL code produced from the design made in DSPB is more readable than the one produced in XSG. It is more than connected blocks and includes traceable functions and comments to know what operation in the design corresponds to the RTL code. However, it is not as readable as the HDL Coder produced RTL. The timing for the Intel device is presented in setup and hold slack, which is defined by:

## Setup Slack= Data Required Time - Data Arrival Time

Hold Slack= Data Arrival Time - Data Required Time

Zero setup slack indicated that the design is exactly working at the specified frequency and no margin available. Negative setup slack implies that the design can not manage the constrained frequency and timing, also called setup violation. A similar hold violation exists for negative hold slack.

## 7.3 Optimization

For small designs, there are not much optimization options available. However, all the optimization options offered by HDL Coder were explored. First, each of the three HDL Coder design was made, verified and optimized individually, to make sure the best case for all the parameters for the individual design. The optimization options that is appropriate for a design this size is to use pipelines, sharing factor and the flattened hierarchy option provided by HDL Coder. How this is done can be read about in section 6.4.

The use of sharing factor is suppose to reduce the amount of multipliers used and therefore the amount of DSP blocks used. With use of sharing factor a rise of registers used can be predicted, but most often devices have much more registers available than amount of DSPs. An experiment with a sharing factor of two was done for the block design and the MATLAB function and block design, to investigate if the area would get reduced. Though, it has to be kept in mind that the double frequency is needed for these designs.

The optimization option for distributed pipelining was tried on all three of the designs. Though, it was noticed that the timing was not that effected compared to the extra registers added for the designs. The option for using a flattened hierarchy was tried as well, to distribute the registers across the subsystem to optimize the timing.

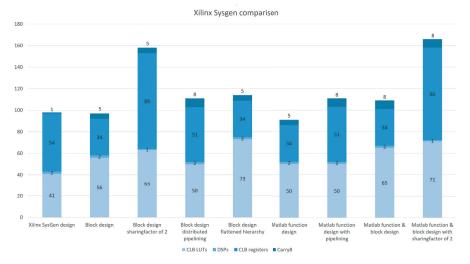

## 7.4 Results Xilinx

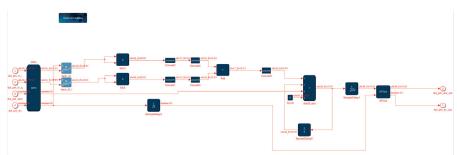

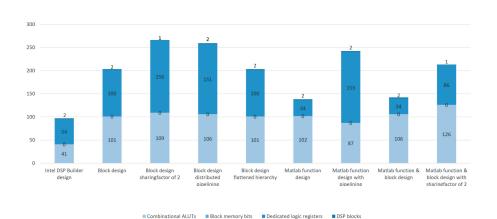

A power meter design was a reasonable design to start because of the logic and size. The block design was easy to make and understand. Most of the results from it are relevant for this thesis work. The resulting block designs looks very similar, the one implemented in HDL Coder, XSG and DSPB. The logic can be understood from all three designs. Though, the design part with the reset and timing is understandable in RTL produced by HDL Coder but less so in XSG and DSPB. The design with a MATLAB code function block is not as clear as the one where only blocks are used. It took more time to produce the MATLAB code compared to designing with HDL Coder blocks. The chart in figure 8 show the synthesis results before optimization for the HDL Coder designs and after optimization, and the results are discussed in the sections below. All the designs met

the timing constraints. The table 3 show the slack for each test. Considering timing the block design with distributed pipelining, the MATLAB function design with pipelining and MATLAB function and block design works best. The worst is the unoptimized MATLAB function design. As for a design with area constraints the designs to choose from could be block design and MATLAB function design because using only 5 DSPs and low amount of resources otherwise.

Figure 8: Xilinx comparison with HDL Coder models and optimizations.

The block design corresponds to the design consisting of Simulink HDL synthesizable blocks whereas in the MATLAB function based design it consists of a MATLAB function block within the Simulink model where the code written generates the synthesizable HDL. A mixture of the block design with MATLAB function blocks have also been tried out and is named MATLAB function and block design. In the below table, the results for the different optimization tried with the block design and MATLAB function block have been summarized.

|                                                           | Slack (ns) |

|-----------------------------------------------------------|------------|

| XSG                                                       | 4.085      |

| Block design                                              | 5.193      |