## Implementation of a Deep Learning Inference Accelerator on the FPGA

SHENBAGARAMAN RAMAKRISHNAN MASTER'S THESIS DEPARTMENT OF ELECTRICAL AND INFORMATION TECHNOLOGY FACULTY OF ENGINEERING | LTH | LUND UNIVERSITY

## Implementation of a Deep Learning Inference Accelerator on the FPGA

Shenbagaraman Ramakrishnan sh2053ra-s@student.lu.se

Department of Electrical and Information Technology Lund University

Supervisor: Liang Liu and Sven Karlsson

Examiner: Erik Larsson

March 23, 2020

© 2020 Printed in Sweden Tryckeriet i E-huset, Lund

## Abstract

Today, Artificial Intelligence is one of the most important technologies, ubiquitous in our daily lives. Deep Neural Networks (DNN's) have come up as state of art for various machine intelligence applications such as object detection, image classification, face recognition and performs myriad of activities with exceptional prediction accuracy. AI in this contemporary world is moving towards embedded platforms for inference on the edge. This is essential to avoid latency, enhance data security and realize real-time performance. However, these DNN algorithms are computational and memory intensive. Consequently, exploiting immense energy, compute resources and memory-bandwidth making it difficult to be deployed in embedded devices. To solve this problem and realize an on-device AI acceleration, dedicated energy-efficient hardware accelerators are paramount.

This thesis involves the implementation of such a dedicated deep learning accelerator on the FPGA. The NVIDIA's Deep Learning Accelerator (NVDLA), is encompassed in this research to explore SoC designs for integrated inference acceleration. NVDLA, an open-source architecture, standardizes deep learning inference acceleration on hardware. It optimizes inference acceleration all across the full stack from application through hardware to achieve energy efficiency synergy with the demanding throughput requirements. Therefore, the following thesis probes into the NVDLA framework to perceive the consistent workflow across the whole hardware-software programming hierarchies. Besides, the hardware design parameters, optimization features and system configurations of the NVDLA systems are analyzed for efficient implementations. Also, a comparative study of the diverse NVDLA SoC implementations (nv\_small and nv\_medium) with respect to performance metrics such as power, area, and throughput are discussed.

Our approach engages prototyping of Nvidia's Deep Learning Accelerator on a Zynq Ultrascale+ ZCU104 FPGA to examine its system functionality. The Hardware design of the system is carried out using Xilinx's Vivado Design Suite 2018.3 in Verilog. While the on-device software runs Linux kernel 4.14 on Zynq MPSoC. Thus, the software ecosystem is built with PetaLinux tools from Xilinx. The entire system architecture is validated using the pre-built regression tests that verify individual CNN layers. Besides these NVDLA hardware design also runs pre-compiled AlexNet as a benchmark for performance evaluation and comparison.

## Popular Science Summary

Today, Artificial Intelligence is at the edge. This edge or endpoint device is becoming more sophisticated with the evolution of Internet of Things (IoT) and 5G. For instance, these devices are employed in different applications such as autonomous cars, drones, and other IoT gadgets. At present, a self-driving car is a data center on wheels, a drone is a data center on wings as well as robots are data centers with arms and legs. All these mechanisms collect vast real-world information that demands to be processed in real-time. Here in these applications, there is no time to send data to the cloud for processing and wait for action. As the decision making needs to be instantaneous. There is a shift in transforming the processing to the edge devices.

The edge acceleration brings computation and data storage closer to the device. With the evolution of specialized hardware's providing increased computational capabilities, the AI models are processed on the edge. As a result, the overall system latency gets reduced, the bandwidth costs for data transfers are lowered and the data processing is done locally enhances privacy concerns. For example, autonomous cars require a spontaneous reaction (in seconds) to avoid potential hazards on the road. Consider the situation where a self-driving car is collecting real word information like images, videos, in this case, assume it's sensing for a stop sign. If the system sends the specific image information to the cloud for processing and waits for a decision to stop. By that response time, the autonomous vehicle could have already blown through the stop sign running over several people. Therefore, it is paramount to process the data in real-time which could be accomplished using dedicated hardware for processing locally.

This thesis primarily explores those hardware architectures for efficient processing of AI algorithms and their corresponding software execution environment setup. The particular thesis was carried out as a joint collaboration between Ericsson and Lund University. Here Nvidia's Deep Learning Accelerator architecture is engaged as a target to comprehend the complete system incorporating a hardware-software co-design. The particular architecture is an essential characteristic of NVIDIA's Xavier Drive chip which is utilized in their autonomous drive platforms. This thesis is addressed to a variety of audiences who are passionate about Deep Learning, Computer Architecture, and System-on-Chip Design. The thesis illustrates a comprehensive implementation of an AI accelerator to envision AI processing on the edge.

## Acknowledgement

Foremost, I would like to take this opportunity to thank my family for supporting me to pursue my dreams. Their unconditional love and encouragement paved the way for my graduate studies in Sweden. Next, I would thank all my professors, supervisors, classmates and colleagues at Lund University as well as at Ericsson, Lund for assisting me with everything during the course of two years.

Besides, I would like to express my sincere gratitude to the following people who have helped me undertake the particular research. My university supervisor Mr. Liang Liu for his enthusiasm on this project, for his support, encouragement, and patience; Mr. Sven Karlsson, my supervisor at Ericsson for his valuable inputs throughout the master thesis; To all the lab supervisors and Ph.D. students at Lund University for their assistance during the challenging times of the thesis. And the Ericsson Research team, Lund for providing adept suggestions.

> Shenbagaraman Ramakrishnan Stockholm, March 2020

# Acronyms

| AI    | Artificial Intelligence.                 |

|-------|------------------------------------------|

| DL    | Deep Learning.                           |

| ML    | Machine Learning.                        |

| DNNs  | Deep Neural Networks.                    |

| CNNs  | Convolutional Neural Networks.           |

| MLP   | Multi Layer Perceptron.                  |

| ReLU  | Rectified Linear Unit.                   |

| PReLU | Parametric Rectified Linear Unit.        |

| FC    | Fully Connected.                         |

| LRN   | Local Response Normalization.            |

| BN    | Batch Normalization.                     |

| NVDLA | NVIDIA Deep Learning Accelerator.        |

| FPGA  | Field Programmable Gate Arrays.          |

| PS    | Processing System.                       |

| PL    | Programmable Logic.                      |

| ASIC  | Application Specific Integrated Circuit. |

| SoC   | System On Chip.                          |

| CPU                           | Central Processing Unit.                    |

|-------------------------------|---------------------------------------------|

| GPU                           | Graphical Processing Unit.                  |

| MAC                           | Multiply and Accumulate.                    |

| RTL                           | Register Transfer Level.                    |

| VMOD                          | Verilog Model.                              |

| AMBA                          | Advanced Micro-controller Bus Architecture. |

| AXI                           | Advanced eXtensible Interface.              |

| APB                           | Advanced Peripheral Bus.                    |

| HP                            | High Performance.                           |

| SDK                           | Software Development Kit.                   |

| FFT                           | Fast Fourier Transforms.                    |

| $\mathbf{DRAM}/\mathbf{SRAM}$ | Dynamic/Static Random Access Memory.        |

| ІоТ                           | Internet of Things.                         |

| BSP                           | Board Support Package.                      |

| ioctl                         | Input Output Control.                       |

| API                           | Advanced Peripheral Interface.              |

| ONNC                          | Open Neural Network Compiler.               |

| SD                            | Secure Digital.                             |

| DFT                           | Design For Test.                            |

| IRQ                           | Interrupt Request.                          |

viii

# Table of Contents

| 1  | Introduction                                     | 1  |

|----|--------------------------------------------------|----|

|    | 1.1 Context                                      | 1  |

|    | 1.2 Project Goals and Challenges                 | 4  |

|    | 1.3 NVDLA Design Flow                            | 5  |

|    | 1.4 Implementation Methodology                   | 6  |

| 2  | Theoretical Background                           | 7  |

|    | 2.1 Convolutional Neural Networks                | 7  |

|    | 2.2 Design Methodologies for Efficient Inference | 15 |

|    | 2.3 NVDLA Architecture Design and Specification  | 18 |

| 3  | NVDLA SoC Design Implementation                  | 25 |

|    | 3.1 Environment Setup                            | 25 |

|    | 3.2 NVDLA SoC design in Vivado                   | 27 |

| 4  | Configuring the Software Environment             | 35 |

|    | 4.1 Compilation Build                            | 35 |

|    | 4.2 Run-time Execution                           | 36 |

|    | 4.3 PetaLinux Flow                               | 37 |

| 5  | Results Analysis                                 | 41 |

|    | 5.1 Hardware Performance Parameters              | 41 |

|    | 5.2 Accelerator Performance comparisons          | 46 |

|    | 5.3 System Verification                          | 48 |

| 6  | Conclusion and Future Works                      | 51 |

| Re | ferences                                         | 53 |

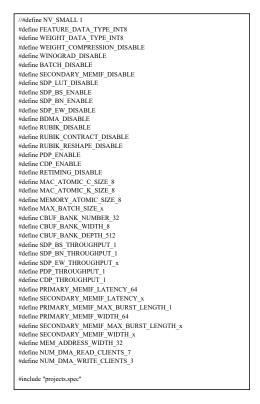

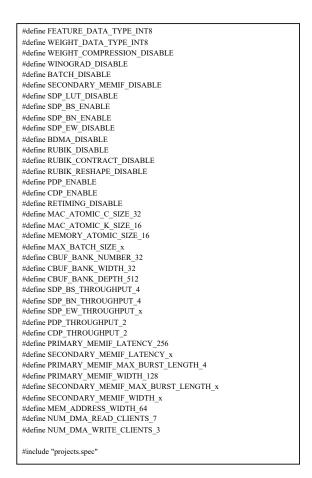

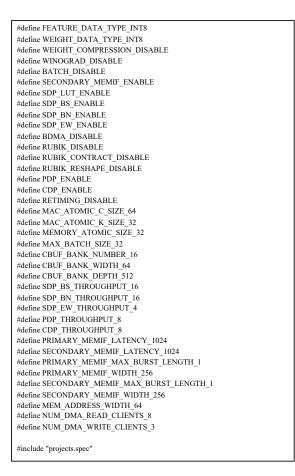

| ^  | NVDLA Succification Files                        | 67 |

| Α  | NVDLA Specification Files                        | 57 |

| В  | PetaLinux Design Flow                            | 61 |

| с  | Miscellaneous                                    | 63 |

| C.1 | The Multi Layer Perceptron model | 63 |

|-----|----------------------------------|----|

| C.2 | AlexNet Architecture             | 64 |

# List of Figures

| 1.1<br>1.2 | AI Hardware Target Domains3NVDLA Design Flow5                |

|------------|--------------------------------------------------------------|

| 2.1        | Convolutional Neural Network                                 |

| 2.2        | 2D Direct Convolution                                        |

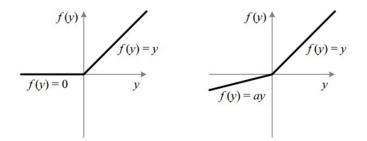

| 2.3        | Relu and PRelu Activation    9                               |

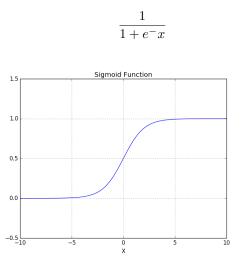

| 2.4        | Sigmoid Activation                                           |

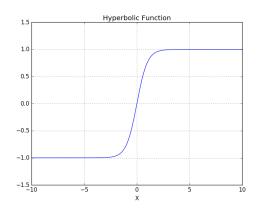

| 2.5        | Hyperbolic-Tangent Activation                                |

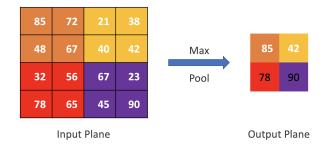

| 2.6        | Max Pooling                                                  |

| 2.7        | Fully Connected Layer    12                                  |

| 2.8        | Local Response Normalization                                 |

| 2.9        | Pruning Neural Networks                                      |

| 2.10       | Quantization Technique 16                                    |

| 2.11       | Winograd Algorithm                                           |

| 2.12       | Batched Convolution                                          |

| 2.13       | NVDLA Hardware Primitives                                    |

| 2.14       | External Interfaces                                          |

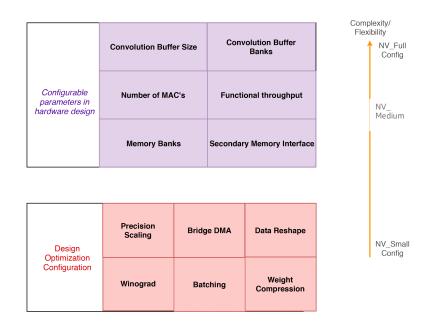

| 2.15       | Parameters Configuration                                     |

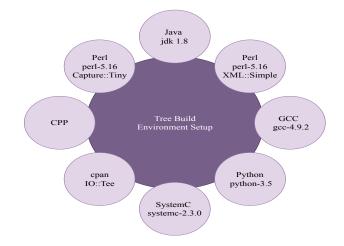

| 3.1        | Tree Build Setup                                             |

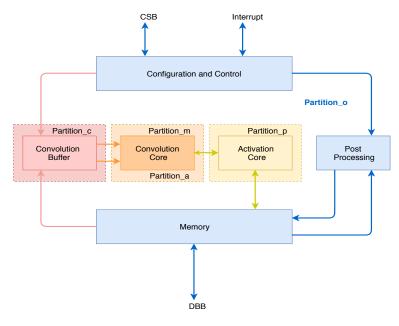

| 3.2        | VMOD Partition                                               |

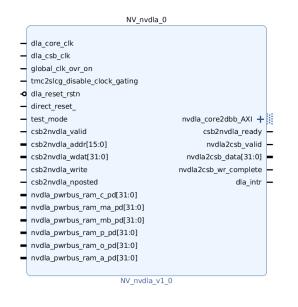

| 3.3        | NVDLA Core Packaged IP                                       |

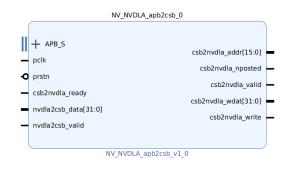

| 3.4        | APB to CSB Bridge Packaged IP                                |

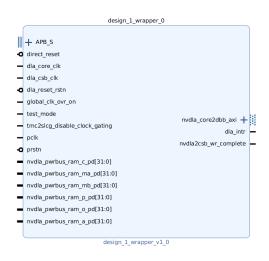

| 3.5        | Packaged NVDLA Wrapper IP                                    |

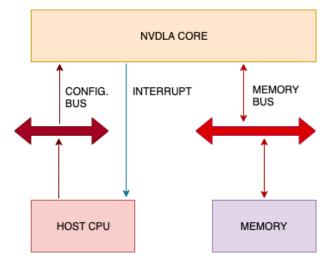

| 3.6        | NVDLA Hardware Architecture                                  |

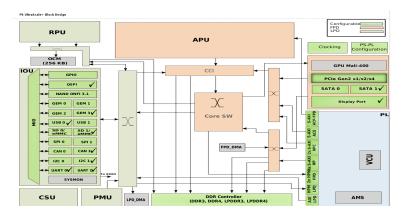

| 3.7        | Block Diagram of Zynq Ultrascale+ MPSoC                      |

| 3.8        | Address Segmentation of peripherals attached to processor 32 |

| 3.9        | NVDLA System Architecture                                    |

| 4.1        | NVDLA Software Stack                                         |

| 4.2        | Linux Execution Environment Framework                        |

| 4.3        | PetaLinux Flow                                               |

| 4.4        | Device Tree                                                  |

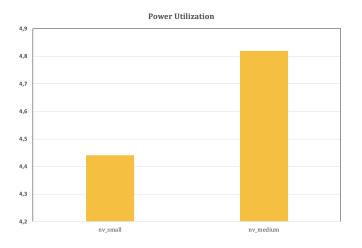

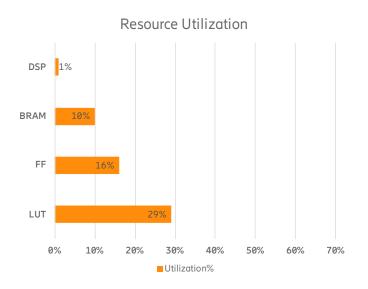

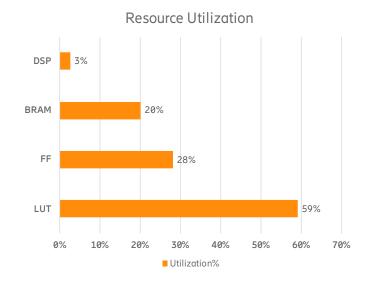

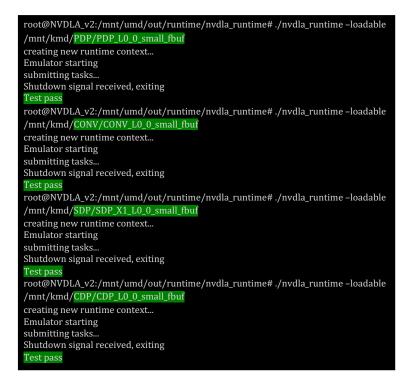

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6 | NVDLA Power Consumption graphNV Small Utilization graphNV medium utilization graphPerformance Comparison of DNN HardwaresSanity Tests Execution on FPGAAlexNet Execution on FPGA | 43<br>45<br>46<br>47<br>48<br>49 |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| A.1<br>A.2<br>A.3                      | NVDLA Small Specification file.NVDLA medium Specification file.NVDLA large Specification file.                                                                                   | 57<br>58<br>59                   |

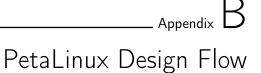

| B.1                                    | General design flow in PetaLinux.source (From PetaLinux reference guide).                                                                                                        | 61                               |

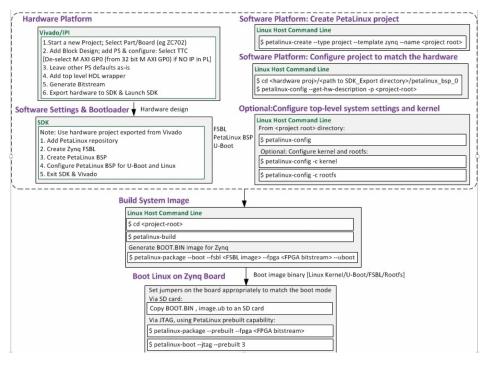

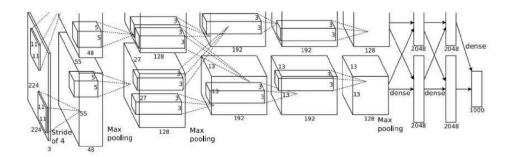

| C.1<br>C.2<br>C.3                      | A Multi Layer Perceptron model with two hidden layers                                                                                                                            | 63<br>64<br>64                   |

# List of Tables

| 3.1 | Verilog Macros                                        | 28 |

|-----|-------------------------------------------------------|----|

| 5.1 | Post Implementation timing summary.                   | 42 |

| 5.2 | Post Implementation power consumption                 | 43 |

| 5.3 | Post Synthesis Utilization results for NV Small       | 44 |

| 5.4 | Post Implementation utilization results for NV Small  | 44 |

| 5.5 | Post Synthesis utilization results for NV Medium      | 45 |

| 5.6 | Post Implementation utilization results for NV Medium | 46 |

## \_\_\_\_<sub>Chapter</sub> \_ Introduction

In this introductory section, the context of hardware acceleration of deep learning will be conferred together with the previous state of the arts in this field. This is followed by the general deep learning acceleration design flow along with the research questions and challenges of this project. Furthermore, a methodology to accomplish the objectives are outlined.

Artificial Intelligence is the science of contriving machines to make intelligent decisions, processing several computational learning algorithms. They are broadly classified into Machine Learning and Deep Learning. Machine Learning is the ability to learn from data. While Deep learning is a specialized technique that implements machine learning tasks through artificial neural networks, inspired by the human brain. The advent of Deep Learning started from the influential paper of Geoffrey Hinton in 2012 [1], where these deep neural networks performed image classification exceptionally than the traditional computer vision, machine learning, and feature engineering algorithms. At the moment, Artificial Intelligence is empowering endless capabilities for the present as well as the future. Specifically, with the deep neural network architectures establishing the foundation for its modern applications in image, face and speech recognition's. Apparently, AI is advancing as the driving force in our socio-economic progress at the prominence of technological revolution and industrial transformation. This thesis primarily scrutinizes deep learning in the context of AI and its respective inference acceleration.

## 1.1 Context

At present, Deep learning is transforming our everyday experience by initiating smart capabilities to industrial and consumer products. Deep Neural Networks revolutionize in the field of computer vision [1] [2] [3], natural language processing [4] [5], autonomous vehicles [6], etc. These DNN's achieve near state of the art accuracy on many AI applications as mentioned above. This exceptional performance is due to its inherent ability of feature extraction on their own from raw data. However, this super-human accuracy comes at the expense of demanding computational complexities. Besides, these deep algorithms consume greater energy consumption taking into account their large memory footprints. As a result, the design of an efficient deep learning accelerator evolved as a demanding subject of interest for research.

A general AI flow involves two phases training and inference. During training, the deep learning algorithms acquire intelligence from the existing data and use cases. The primary objective here is to minimize the error function of parameters (weights) for a given neural network. This phase exploits enormous resources and time. Also, the process demands high throughput, therefore they are processed on cloud clusters or GPUs. Whilst during Inference, the developed intelligence from training is applied to test on new sets of scenarios, to validate the general system performance. This inference acceleration is carried out on dedicated compute devices as they are latency and resource critical. Thus, the computational approaches differ significantly for both the training and inference process.

There are lots of research in academia and industry focused on designing hardware systems for training and inference operations. It is challenging to design a hardware system specific to certain AI applications. Since the field of AI is constantly advancing with the development of novel algorithms, architectures, and applications. Besides, the costs involved in designing custom AI hardware is also immense. Therefore the AI hardware systems typically are domain-specific rather than application-specific. Hence can possess more degree of freedom in their target architectures to comply with different application requirements.

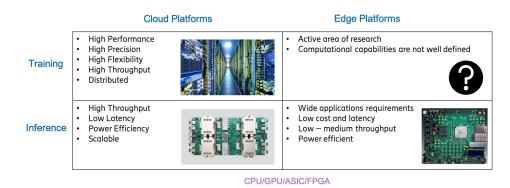

The AI hardware domain is classified based on their application such as training or inference. As well as, categorized based on deployments either on the cloud or edge as shown in the figure 1.1. The inference is essentially targeted for the edge/embedded platforms. While the training on the edge is still an active area of research where the computational requirements are not yet characterized distinctively. The training is usually accomplished on the cloud. Sometimes highperformance edge devices can also be exploited in training as cloud devices. This thesis primarily delves into hardware accelerators focusing inference on the edge devices.

Figure 1.1: AI Hardware Target Domains

#### 1.1.1 Deep Neural Networks Processing in Hardware.

A deep learning accelerator generally refers to a physical chip that speeds up computations. These accelerators primarily target convolution and fully connected layers for acceleration as they are computationally intensive. The particular layers primarily involve multiplications and accumulation (MAC) operations which can easily be executed in parallel. Thus, the initial hardware inference accelerators exploited the inherent spatial parallelism in DNNs and performed parallel processing over an array of processing elements (PEs) [7] [8] [9]. These accelerators employed data-flow architectures that efficiently mapped convolution operations in hardware as well as specialized on highly parallel computational paradigm. As a result the custom accelerators accomplished more efficiency than the traditional CPUs and GPUs.

But the most important bottleneck in the specific implementations included memory access and data transfers [10, 13]. The previous accelerator designs inferred that the data transfers utilized immense energy costs than the actual computations. Accordingly, the next evolution of inference accelerators focused on energy efficient designs which maximized data reuse and reduced memory overheads. The MIT Everiss [11] exploited a row stationary (RS) data-flow [12] architecture that efficiently reused input feature maps and filter weights. Accelerators such as Dian-Nao [14] and its variant designs [15, 16] reduced memory references by introducing on-chip buffers to store all the weights and avoid DRAM access. Besides, novel architectures started to employ deep compression techniques such as low precision and quantization to curtail memory traffic at the cost of reduced accuracy [17, 18]. These compression techniques exploit the neural networks inherent error resilience ability. In the current accelerator trends, the optimizations were accomplished not only on the hardware level but also on the algorithm level of deep neural networks [19]. As a result, the particular approaches achieved enhanced performance and energy efficiency.

NVIDIA's Deep Learning Accelerator (NVDLA) is a standardized inference accelerator implemented based on the current accelerator design trends especially sparse compression techniques [20]. The particular accelerator addresses the computing demands of inference along with a flexible and energy efficient hardware implementation. The specific acceleration solution equips a simplified, reconfigurable design which supports different performance requirements. Besides, the NVDLA is an open source and free architecture that promotes a standard method of designing inference accelerators on the edge.

## 1.2 Project Goals and Challenges

The primary objective of this thesis is to implement the NVDLA architecture as an SoC design and prototype on an FPGA platform to run on-device inference. This is accomplished to comprehend the consistent workflow of NVIDIA's deep learning accelerator standards. The NVDLA architecture supports a complete deep learning inference framework succeeding in a hardware-software co-design. Thus, providing an opportunity to examine the complete system integration from neural networks compilation to its deployment in edge devices. This thesis illustrates the entire NVDLA project development constituting environment setup, RTL design, SoC implementation, and software execution environment.

In this research, the hardware acceleration is focused essentially on FPGA/ASIC platforms for edge IoT applications. Recent trends in this domain incorporate special-purpose hardware for inference acceleration on the edge. The particular inference accelerator demands high versatility, prediction accuracy and compels near real-time solution. This poses a great challenge when the implementations accomplished on precise SoC architectures are resource-constrained in terms of power, memory and computational capabilities.

To engage the computational challenges of the neural networks with the resource constraints in implementations different design methodologies are leveraged. It comprises an array of micro-engines with highly coupled local memories that minimizes data movements, improves data re-usage and enables parallel processing. The techniques such as Weight compression and network pruning are employed to enhance computation performance as well as reduce hardware cost utilizing small network sizes and data-types [19]. Sometimes simplified architectures for fast convolutions such as Winograd transformation [21], FFT's [22] are modeled for optimizing operational efficiency. These architecture designs for efficient hardware implementation for the edge inference are examined comprehensively on the NVDLA framework. The NVDLA architecture can be configured differently based on the performance levels. Two such architectures (nv small and nv medium) are analyzed in-depth concerning power, area, and throughput requirements. Besides these NVDLA hardware architectures also runs a neural network for inference like AlexNet on the FPGA [23]. This operates as a benchmark to evaluate performance and prediction accuracy metrics across different implementations.

This NVDLA core is very attractive among enthusiasts as it is an open-source design. It can be utilized by the AI developers as an initial target model for inference acceleration. However, the subsequent system has its challenges while implementation. This open-source approach is noble and the complete hierarchical system design can be immense. The technological breadth, design tools and set up environments of the NVDLA flow are boundless. The system comprises of engaging in all the levels of programming hierarchies to realize its design implementation. As a result, poses a greater challenge in developing in a shorter time frame. Besides NVDLA executes only specific pre-compiled deep neural network models. As the inherent compiler environment was not available for the user's examination during this implementation.

### 1.3 NVDLA Design Flow

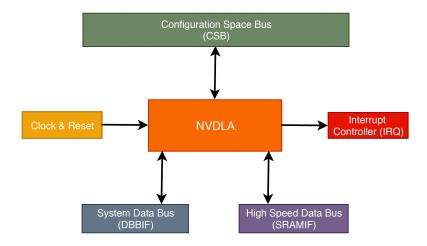

The inference process is where the AI's substantial power after training meets the real-world application. To envision an AI-driven smart ecosystem, inference acceleration is primarily decisive. The NVIDIA's Deep Learning Accelerator (NVDLA), provides a robust, versatile, configurable architecture to standardize deep learning inference operation. This accelerator is an essential characteristic of NVIDIA's Xavier Drive System-on-a-chip which is employed in autonomous vehicles.

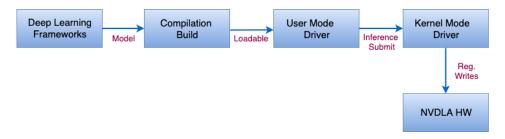

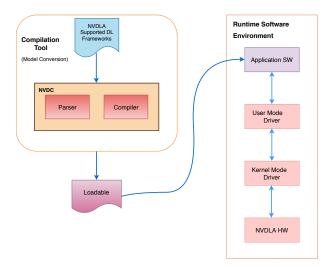

The following NVDLA design flow comprises a hardware accelerator as well as a software ecosystem that co-ordinates to accelerate the inference process effectively. The general flow is represented as shown in the figure 1.2.

Figure 1.2: NVDLA Design Flow

The neural networks are generally trained in TensorFlow or Caffe software. The hardware acceleration for the training of neural networks on-device is still an active area of research. Next, the trained model is fed to a compilation build, that converts deep neural networks into a sequence of hardware layers based on its underlying accelerator configuration. The compiler generates hardware layers appropriate to NVDLA configuration given as an input. Later, these compiled models are stored as NVDLA loadable image. The specific loadable images are pre-compiled and only supports specific deep learning models. Thereafter, this loadable is passed to a run-time environment that co-ordinates between software and hardware executions. It constitutes of device drivers to synchronize the hierarchical design, schedule functional blocks and handles interrupt from the NVDLA hardware. The hardware accelerator involves different functional blocks that perform convolution, activations, pooling, normalization, data transformations, and memory transfer operations. Each of these functional blocks can be configured exclusively. Different configurations concerning these scalable parameters culminate distinctive implementations such as nv\_small, nv\_large models. The explicit configurations are utilized based on performance specifications.

NVDLA caters to simplified system integration. A host processor is the main control unit that manages the process flow on the hardware core. The hardware core employs standard AXI buses to interface with memory for data transfers. Whereas the control channel utilizes a register file and interrupts interface to the host processor. The primary memory, in general, a DRAM is mapped to both processors and external peripherals. In the case of high memory bandwidth applications, a dedicated high-speed SRAM interface is exploited. The host processor associates with the external drivers and peripherals through memory-mapped addresses.

### 1.4 Implementation Methodology

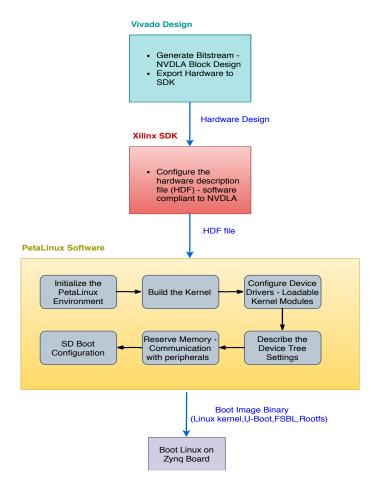

The design procedure for the NVDLA implementation involves a hardware-software co-design. As a result, various application tools are realized to accomplish a complete development environment. The embedded hardware design flow is carried out in Xilinx's Vivado Design Suite tools 2018.3. While the software development and embedded drivers setup are accomplished in the PetaLinux platform from Xilinx. The Zynq Ultrascale+ ZCU102 is employed as the FPGA target to map the NVDLA core. While the Zynq MPSoC functions as the primary processing system in the SoC architecture. The project implementation is subdivided as follows:

- 1. An Environment setup to establish a tree build that generates RTL in Verilog from a SystemC hardware specification file.

- 2. An Embedded SoC architecture that accomplishes relevant communication between the host processor and NVDLA core.

- 3. A run-time execution environment to load and process compiled neural networks in the NVDLA system implemented in the Petalinux application.

- 4. An Inference setup on Zynq Ultrascale+ FPGA for executing Neural Networks especially AlexNet as bench-mark and run regression tests for evaluating the implemented system.

# \_\_\_\_<sub>Chapter</sub>2 Theoretical Background

In this chapter, the background of Convolutional Neural Networks is presented. Besides, the design methodologies leveraged for efficient hardware implementation of CNN's are discussed. Later, the hardware specifications of NVDLA architecture are illustrated.

## 2.1 Convolutional Neural Networks

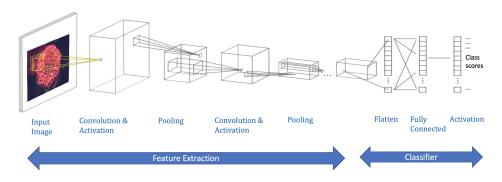

A Convolutional Neural Network is a deep learning algorithm consists of neurons with learnable weights and biases. Each neuron performs a dot product of its input and weights followed by a non-linear activation. The CNN architecture is prominent because of its proficiency to learn feature extractions on their own from raw image pixels, and inherent fault tolerance to inputs. These CNNs perform exceptionally well on image classification, natural language processing, recommender systems and more. Also, the CNN possess a remarkable capability to express output as a single differentiable score emerged just from the raw input image. A CNN incorporates a series of layer operations to accomplish the above characteristics as shown in the figure 2.1 subsequently.

Figure 2.1: Convolutional Neural Network

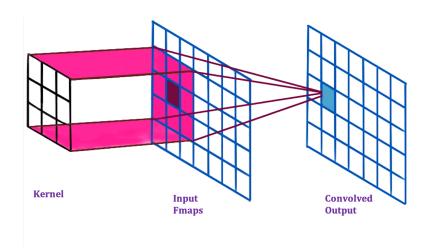

#### 2.1.1 Convolution Layer

The Convolution layer extracts information from the input image. It is an elementwise multiplication operation between the kernel weights and input feature maps. This operation slides the kernel across the input at every location, shifting one neuron each time (for stride of 1). The partial sums of these convolutions are aggregated into respective output feature maps. For simplicity, the input image is given by I (i,j) considering every pixel to be scalar. The filter is represented as a kernel K (n,m) and the convolved output is given by h(i,j). A figure 2.2 successively represents a convolution operation.

$$\begin{split} h(i,j) &= (I \ast K)(i,j) \\ &= \sum_m \sum_n I(i-m,i-n) K(m,n) \end{split}$$

Figure 2.2: 2D Direct Convolution

This sliding window kernel operation also facilitates sparse connectivity and parameter sharing. When considering a convolution layer the receptive field for a given hidden node is small. As the node only maps to the kernel parameters, unlike a Multi-Layer Perceptron (Appendix C.1) that links a hidden node to all of the inputs. Therefore leading to fewer network inter-connections empowering sparse connectivity. In the kernel process, all the parameters stay constant during the sliding operations. As a result, the kernel weights can be shared while performing the weighted sums for respective hidden nodes. Besides the convolution layer, there are more computational blocks when constructing a complete CNN. Those blocks are discussed subsequently.

#### 2.1.2 Activation Layer

The activation layers are the most integral part that adds non-linearity to the system. They enable the network to learn highly complex relationships between the feature maps. An activation function determines the output of the model, their prediction accuracy and computational efficiency during training. These functionalities are realized through dedicated hardware logic and Look-Up-Table in the hardware implementation. Different activation functions are chosen based on the specific problem statement. They are as follows:

• **ReLu.** The most popular activation function for CNN's are the Rectified Linear Unit [24]. Since they result in sparse activation reducing the network parameters. They are defined as.

$$f(y) = max(0, y)$$

This activation gives an output y if y is positive and 0 otherwise. It is advantageous since there is no problem with vanishing gradients and they are computationally less expensive. The only problem with this type of activation is the decaying nodes. Sometimes the ReLu nodes are pushed into regions of inactivity (i.e zero) for all inputs. This results in dead neurons which can no longer be used.

• **PReLu.** To solve the above problem, a Parametric ReLu is used [25]. Instead of squashing the outputs to 0 when the inputs are less than or equal to zero. PReLu keeps a small linear trainable parameter (a) that learns with other neural network parameters to avoid dead neurons. An image of ReLu and PReLu is presented in the figure 2.3.

$$f(y) = \left\{ \begin{array}{cc} y & \text{if } y > 0 \\ ay & \text{otherwise} \end{array} \right\}$$

Figure 2.3: Relu and PRelu Activation

• **Sigmoid.** A Sigmoid function activates the input between 0 and 1. This operation is bounded and the results are always positive. Sigmoid is mainly used as output activation for binary classification problems. They have a

complication of diminishing gradients. Also, the curve is not zero centered as shown in the figure 2.4.

Figure 2.4: Sigmoid Activation

• Hyperbolic Tangent. This is a bounded activation function that ranges between -1 and 1. The gradients for this operation are stronger than sigmoid as the derivatives are steeper. Deciding between sigmoid and tanh will depend on the requirement of gradient strength. This activation also faces the problem of diminishing gradients. An image 2.5 of the following activation is presented.

$$f(x) = tanh(x)$$

$$tanh(x) = \frac{e^x - e^{-x}}{e^x + e^{-x}}$$

Figure 2.5: Hyperbolic-Tangent Activation

#### 2.1.3 Pooling Layer

A pooling layer summarizes the neighborhood of a respective hidden node. This is achieved by sliding the window over the inputs and extract a single value based on the type of pooling operation. As a result, this layer down samples the filtered image reducing the training and inference time. Besides, this operation makes the features invariant to small changes in the raw input evading the problem of over-fitting. The commonly employed pooling functions are enumerated.

- Max Pool : This operation is the most commonly used type of pooling. It returns the maximum value within the receptive field. An example is shown in the successive image 2.6.

- **Min Pool** : In this operation the minimum value within the pooling window is selected.

- Average Pool : This function returns the average value within the receptive field.

Figure 2.6: Max Pooling

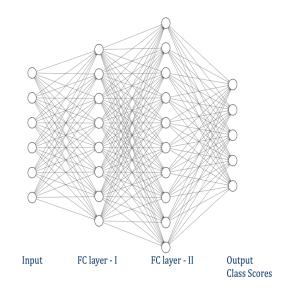

#### 2.1.4 Fully Connected Layer

A Fully Connected (FC) layer resembles a multi-layer perceptron model where each neuron has full connections to the previous layers as shown in the figure 2.7. The input for this layer is a 1D vector of numbers flattened from the previous convolution layers comprising of 3D volumes. While the output of an FC layer is a list of probabilities of different class scores. The particular FC layer functions as a classifier. This operation analyzes the previous layer's high-level features representations (after convolution and activation) and applies weights to predict which features correlate to the specific class. The class score constituting the highest probability is the classifier's decision. For instance, if a model is predicting that the image is a bird, then it holds large value in the activation maps representing high-level features such as wings or beaks. Thus the classifier correlates the extracted high-level feature maps to definite class scores.

Figure 2.7: Fully Connected Layer

#### 2.1.5 Normalization Layer

A normalization layer is necessary in Convolutional Neural Network architectures, considering the unbounded nature of certain activation functions such as ReLu. This process limits the outputs of the activation's and is applied usually before the activation layers. There are two types of normalization layers commonly employed.

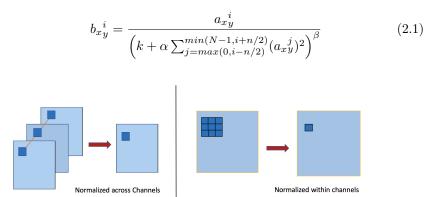

• Local Response Normalization. The Alex-Net architectures using ReLu activation introduced this concept [23]. It resembles the neuro-biology concept of 'lateral inhibition' to boost the neurons and subdue its neighbors [26]. This inhibition forms a local maxima of values for excitation in subsequent layers. Here the neurons excitation are enhanced and the surrounding local neighborhood is dampened. It is achieved by square normalizing the image pixels of feature maps over a local neighborhood that extends across or within the respective channels as shown in the figure 2.8.

The AlexNet utilized a local response normalization across channels (in the dimension of depth) and is given by the subsequent formula. In the formula, i indicates the output of filter i. a(x,y), b(x,y) represents the pixel values before and after normalization. Here  $(k, \alpha, \beta)$  are hyper-parameters. n is the size of normalization neighbourhood and N is the total number of kernels. In the corresponding figure n=1 and N=3.

Figure 2.8: Local Response Normalization

• Batch Normalization. This technique normalizes the output of previous activation layer to reduce the internal co variance shift [27, 28]. This arises due to changing distributions in hidden neurons/activations. As a result, the batch normalization allows each layer to learn independently of preceding layers. This is accomplished by subtracting the batch mean and dividing by the batch standard deviation. The particular technique improves the stability of a neural network and reduces over-fitting as it contains regularization effects top. The mathematical representation is described. Here the batch normalization transform (BN) is applied to activation x over a mini batch B of size m.

Input = Values of x over a mini - batch (B).B = x1...m;

Learning Parameters =  $\gamma, \beta$

$\mu_B = \frac{1}{m} \sum_{1=1}^m x_i$

mean

$$\sigma_B^2 = \frac{1}{m} \sum_{1=1}^m (x_i - \mu_B)^2 \qquad variance$$

$$\vec{x_i} = \frac{x_i - \mu_B}{\sqrt{\sigma_B^2 + \epsilon}} \qquad normalize$$

$$\vec{y_i} = \gamma \vec{x_i} + \beta \equiv BN_{\gamma,\beta}(x_i)$$

shifting

### 2.2 Design Methodologies for Efficient Inference

In this section, the design methodologies leveraged for efficient hardware implementation are discussed in detail. The current trends of hardware accelerators in deep learning employs "Deep compression" techniques for efficient inference. In this method, the deep neural networks are compressed before their inference acceleration in hardware targets. Consequently, it reduces the number of parameters as well as it's computational efforts. Deep compression mainly includes network pruning and quantization techniques. Besides, the computational complexity can also be reduced by exploiting Winograd and batching transformations. These optimization methods applied to realize efficient inference are interpreted below.

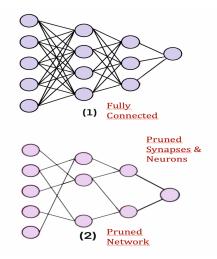

#### 1. Pruning.

The pruning mechanism was inspired to eliminate the redundant parameters of the neural networks that do not contribute significantly to the outputs. Especially, the zero weights and activations. This procedure can be exercised to all the layers as a whole or specific layer of CNN. This facilitates sparse executions, which enhances computational performance as well as reduce memory overheads.

Pruning can be implemented using ranking methods. The rankings are generally based on L1/L2 norm of weights, mean activation's, etc., considering individual layers. The alternative technique employed is iterative pruning, which applies to the complete network. In this process, CNN is fine-tuned until the pruning objective is attained. For example, the objective for pruning could be in terms of definite model size or execution performance.

Figure 2.9: Pruning Neural Networks

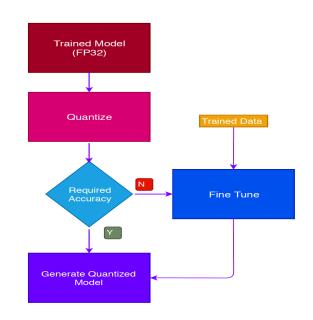

#### 2. Quantization.

The quantization method adopts reduced precision as well as smaller data representations of weights and activations. This is achieved to primarily reduce the hardware cost, memory accesses and increase parallel executions. The quantization to the desired number of bits solely depends on the requirements of the application and accuracy. Therefore, it is difficult to speculate an optimal precision that suffices all-purpose.

Generally multiple precision such as INT4, INT8, FP16, FP32 are utilized for different applications. Recently INT8 datatype is widely used for inference while FP16, FP32 data-types are exploited for training. The quantization techniques are applied to the granularity of channel level for weights and layer level for activations. Normally the activation quantization has a significant impact on the accuracy than that of the weight's quantization. To improve the accuracy, the quantified parameters are fine-tuned by retraining recurrently with the original data-set. Sometimes to avoid retraining, smaller floating-point precision is exploited.

Figure 2.10: Quantization Technique

#### 3. Winograd Transformation.

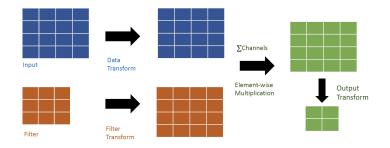

Winograd transformation is an optimized convolution algorithm that reduces the number of multiplier units and increases functional throughput [21]. These methods work well on 3x3 convolutions. Here the inputs and kernel parameters are transformed. These transformed values are subjected to an element-wise multiplication then the results are converted back to obtain the convolved output.

Consider an input image of 4x4xC, kernel window of 3x3xC. To compute the output feature map (2x2x3) the required functional units (MACs) includes: Direct Convolution demands (4x3x3xC) 36xC functional units. While, the Winograd expects 16xC functional units. Therefore, it improves performance by a factor of 2.25x.

Figure 2.11: Winograd Algorithm

### 4. Batching.

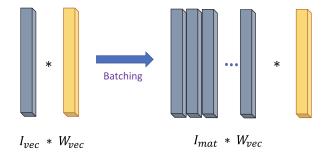

The Batching mechanism is applied to the fully connected layers. These layers functions as a classifier that encompasses full interconnections with their previous layer. Subsequently, do not perform any sliding window operations, confining weight sharing and sparsity. As a result, this functional block demands high memory bandwidth as well as compute resources. To solve this problem batching is employed for reusing kernel weights. Here multiple feature maps of the input image are processed in parallel to perform dot products with the kernel weights. This facilitates the re-usability of weights across multiple images.

Figure 2.12: Batched Convolution

## 2.3 NVDLA Architecture Design and Specification

This section describes the design of NVDLA core, it's respective interconnects, hardware specifications and parameter configurations.

### 2.3.1 Hardware Primitives

The NVDLA core comprises of hardware primitives to realize inference acceleration on deep neural networks. Each of the modules performs a specific operation as discussed previously in the background section. Also, they can be configured independently. It is a versatile, highly scalable architecture that standardizes hardware acceleration of AI inference. For instance, if a system requires multiple layers of convolution operations then the particular building block can be scaled up. Suppose the design does not require any pooling function then the planar data processing engine can be removed exclusively. Therefore, the complete system can be sized appropriately based on application requisites. The hardware primitive blocks are:

- Convolution Core advanced high performance convolution engine.

- Single Data Processor single point lookup engine for activation operations.

- Planar Data Processor planar averaging engine for pooling function.

- Channel Data Processor multi-channel averaging engine for optimized normalizing functions.

- Dedicated Memory Engine dedicated high performance memory interfaces.

- Data Reshape Engine data format transformations for tensor reshaping.

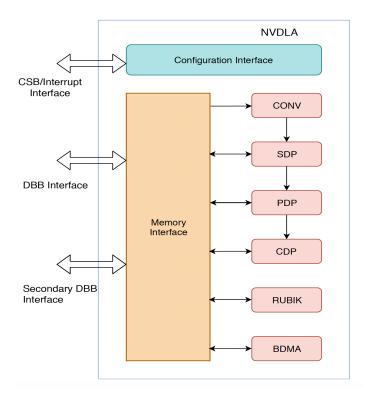

The hardware architecture comprises of four computational blocks (CONV, SDP, PDP, CDP) and two data transformation engines (RUBIK, BDMA) as shown in the figure 2.13. The compiler maps the layers of the deep neural networks to these computational blocks based on the dependency graphs. The inference flow starts when an activate command is sent from the host processor along with the configurations of one hardware layer. If there are no data dependencies among multiple hardware layer configurations, then they are assigned and executed simultaneously. When the corresponding layer finishes its process, it issues an interrupt to the co-processor reporting completion. Consequently, the processor engages in processing the next layers. Thus the system follows command-execute-interrupt flow for completion of the whole convolution network.

Figure 2.13: NVDLA Hardware Primitives

### 2.3.2 Interconnects

The NVDLA core connects to the rest of the system through the following interface options as illustrated in fig 2.14.

- Configuration Space Bus Interface (CSB). The host processor uses this 32-bit synchronous bus to access the NVDLA configuration register sets. NVDLA acts as a slave on the CSB interface. It implements a simple address/data interface to establish communication.

- External Interrupt (IRQ). This system follows a command-executeinterrupt flow where every layer operation is asserted through interrupts to the host processor. It is a 1-bit level driven interrupt that affirms completion and error conditions.

- Data Backbone (DBBIF). NVDLA has its own DMA subsystem that connects to each block. This interface is an AMBA AXI-4 compliant that associates the DRAM memory to the DMA engine. It is a high speed, synchronous and extremely configurable data bus.

• SRAM Connection (SRAMIF). For high performance-oriented systems which emphasize high throughput and low latency. An SRAM memory is used as cache. This interface provides a connection to the cache memory.

Figure 2.14: External Interfaces

#### 2.3.3 Hardware Specifications

NVDLA hardware provides a scalable architecture that can be configured for different application requisites. These hardware specifications depend on the requirements of the CNN employed for inference acceleration also the recommended performance measures. Consequently, performance measures have a significant impact on the following parameters.

#### 1. Convolution Buffer

The Convolution buffer holds both weights and feature data for individual layers. These buffers reduce the number of memory access and enhance energy efficiency. The size of these buffers is configured within the range of 4KB to 32KB. The model size of the CNN is paramount for the buffer sizing.

NVDLA uses a ping-pong buffer mechanism to improve system efficiency. The reprogramming latency can be reduced by utilizing two register groups. This methodology concurrently programs the second group of buffer when the first group is processing the convolution computations. The hardware switch between the register groups through an interrupt based control flow.

#### 2. Number of MAC units

The number of MAC units determines the overall system throughput. The MAC operations in a convolution operation can easily be calculated. They depend on the size of input feature maps, kernel size and number of kernels.

$$MAC \ Units = 2 * nK * (Kx * Ky * Kz + 1)(Ix * Iz)$$

(2.2)

The hardware architectures leverage parallelism in convolution computations exploiting the input and output feature channels. They are represented as Atomic-C and Atomic-K values. The MAC computations on the input feature channels are assigned between 16 to 128. While the computations on the output feature channels are assigned values between 4 to 16. These sizing values impact the number of MAC arrays. For example, if the NVDLA configurations of Atomic C is 32 and Atomic-K is 16 then,

number of MAC = Atomic - C \* Atomic - K = 32 \* 16 = 512 instances (2.3)

#### 3. Memory Bandwidth

For high-performance systems that are time-critical, high memory bandwidth can be capitalized using an on-chip SRAM. It functions as a secondlevel cache memory block. An on-chip SRAM is less expensive in implementation than a large convolution buffer considering its wide ports and demanding timing requirements. But provides less in exchange if the layers are limited by convolution buffer size. So from an implementation perspective, the convolution buffer size is enhanced to reduce memory bandwidth demands and the auxiliary SRAM advances the total available memory bandwidth of the system. Considering the above hardware specifications the NVDLA architecture can be implemented for distinct operations. Also, the architecture can be configured based on the required performance requirement. While the primary configuration includes nv\_ small and nv\_large models. The figure 2.15 shown below interprets the different configurable parameters.

Figure 2.15: Parameters Configuration

#### • NVDLA Small Model

The NVDLA small model is well compliant with AI, IoT systems where performance levels are less of a preference and primarily targets cost and resource efficiency. These implementations provide a basic architecture that supports smaller tasks. Typically, the NVDLA small configurations incorporate reduced precision arithmetic, fewer design optimization features, and limited throughput enhancements. The specified design parameters are enlisted below

| Feature                 | Configured Option                                         |

|-------------------------|-----------------------------------------------------------|

| Data Type Precision     | INT8.                                                     |

| Winograd Support        | Not supported.                                            |

| Compression Support     | Not supported.                                            |

| Second Memory Bus       | Not supported.                                            |

| Image Input format      | Supports 8-bit RGB/YUV.                                   |

| SDP function            | Single Scaling                                            |

| Bridge DMA              | Not supported.                                            |

| Rubik                   | Not supported.                                            |

| Atomic-C                | 8                                                         |

| Atomic-K                | 8                                                         |

| Layer throughput        | One output feature data gets generated every clock cycle. |

| Convolution Buffer size | 32KB                                                      |

#### • NVDLA Large/Full Model

The NVDLA large is utilized for high performance and dynamic applications. These models are highly flexible and multiple tasks can be completed concurrently. As a result, the design includes a high bandwidth SRAM interface connected to the design implementation that shares workloads with the NVDLA core. This SRAM is used as cache memory. These systems incorporate an increased number of processing elements, maximum operational throughput and enable all design optimizations. The hardware design sizing of NVDLA Large is described below.

| Feature                 | Configured Option                                          |

|-------------------------|------------------------------------------------------------|

| Data Type Precision     | FP16/INT16.                                                |

| Winograd Support        | Yes, supported.                                            |

| Compression Support     | Yes, supported.                                            |

| Second Memory Bus       | Yes, supported.                                            |

| Image Input format      | Supports 8/16-bit RGB/YUV.                                 |

| SDP function            | Single Scaling/LUT                                         |

| Bridge DMA              | Yes, supported.                                            |

| Rubik                   | Not supported.                                             |

| Atomic-C                | 64                                                         |

| Atomic-K                | 16                                                         |

| Layer throughput        | Four output feature data gets generated every clock cycle. |

| Convolution Buffer size | 32KB                                                       |

Chapter 3

## NVDLA SoC Design Implementation

This chapter provides an in-depth understanding of integrating NVDLA into an SoC for FPGA implementation. It provides information on setting up the environment for model creation, project development in Vivado as well as system architecture design of the SoC.

#### 3.1 Environment Setup

To develop the RTL model of NVDLA core, a tree build setup is constructed. The following environment generates multiple configurable hardware designs from a single source. These hardware configurations are defined on a specification file. Based on these specifications, a Verilog RTL code is generated appropriately. Different NVDLA configuration can be characterized in the following specification file to develop diverse hardware cores in regards to application requirements. The spec file definitions are provided in the appendix A.

The environment setup requires different tools to build the configured RTL. The essential software's are chartered below in the 3.1.

Figure 3.1: Tree Build Setup

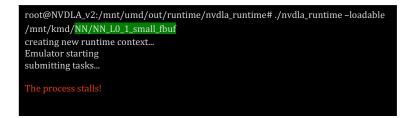

The path to above tools and configurations set-up are constituted in a tree.make file. Once when all these composed modules are compiled through build, an **outdir** directory is established incorporating the Verilog model of the NVDLA hardware. Thus, a successful RTL tree build for a relevant specification file is shown in the subsequent image.

#### 3.1.1 Overview of Generated VMOD

The Verilog model generated from the tree build engages NV\_Small specification for the following case. Here the organizational structure of the generated NVDLA core is discussed. The top module includes the following partitions as also depicted in the figure 3.2.

- 1. Partition\_o : This section controls the communication between processing elements with external controllers and memory units.

- CSB This module reads and writes configuration registers of each layer in NVDLA core. This transfers data from the external management processor through the APB interface.

- CFGROM This maintains configurable parameters of the core for its respective specification definition.

- MCIF This interface communicates with all subunits that access the external DDR. This data bus uses an AXI protocol.

- PDP and CDP These units perform pooling and local response normalization respectively.

- GLB They control the output interrupt signals of all the sub cores of NVDLA.

- 2. Partition\_c: This section manages various convolution kernel operations such as CDMA, CBUF, and CSC.

- CDMA Convolution DMA fetches data from SRAM/DRAM and stores it in a convolution buffer. It comprises two read ports namely weight read and data read ports that connect to the AXI interface to obtain weight/feature data.

- CBUF Convolution buffer is the next stage of the pipeline. It is a 512KB of SRAM cache that stores input data and weights.

- CSC Convolution Sequence Controller loads the stored data from the buffer to its respective MAC units appropriately. Thus, controlling the computation sequence in the convolution pipeline.

- 3. Partition\_m: This partition performs multiplication and addition computations. This Convolution MAC module comprises of 16 MAC cells. Each of these cells includes 64 16-bit multipliers and 72 adders.

- 4. Partition\_a: This module accumulates the partial sums from the MAC arrays and estimates the results before sending it to the next stage of activations.

5. Partition\_p: This section performs various linear and non-linear operations as discussed.

Figure 3.2: VMOD Partition

#### 3.2 NVDLA SoC design in Vivado

The integration of NVDLA core into SoC design is carried out using Vivado Design Suite - 2018.3 provided by Xilinx. This software accelerates the design and verification of NVDLA architecture. Several tools from Xilinx such as Vivado IP integrator, RTL Synthesis, Vivado Simulator, Implementation, Xilinx SDK and Petalinux applications are exercised during the project development .

The design methodology for the implementation of NVDLA SoC is divided into two parts.

- Design of NVDLA Hardware Core and Wrapper

- SoC System Architecture

#### 3.2.1 NVDLA Hardware Core

The NVDLA hardware core is built from the generated Verilog RTL model. Certain modifications are performed in the developed RTL model to integrate the accelerator core into FPGA. As the NVDLA implementation on its own is well defined for custom ASIC design. For instance, the implementation comprises clock gating and power gating features to limit dynamic power dissipation at the cost of more hardware logic. Contrarily, these features when used in FPGA prototyping results in timing violations. Therefore, definite macros are added in Verilog header files and set as global include to disable the auxiliary hardware architectures. Besides, the inferred RAM resources included in the source files also disable these features for the prior purpose.

> VLIB\_BYPASS\_POWER\_CG NV\_FPGA\_FIFOGEN FPGA FIFOGEN\_MASTER\_CLK\_GATING\_DISABLED RAM\_DISABLE\_POWER\_GATING\_FPGA

#### Table 3.1: Verilog Macros

Here synthesis is accomplished to verify the substantiation of source code for preceding user alterations. The tool generates top-level instances with all of its references along with appropriate reports that are utilized to validate the developed RTL design. In general, synthesis performs a high-level abstraction to logic gate levels where it maps the generic gate-level netlists. It also incorporates advanced design optimization's for timing and area. The behavioral model sources along with netlists from synthesis are packaged into an IP using Vivado IP integrator. The packaged NVDLA Core IP is shown below in the fig 3.3 includes the following external pins and interfaces:

- Clock Interface: NVDLA core consists of *dla\_core\_clk* and *dla\_csb\_clk*. The dla\_core\_clk acts as the functional clock for the complete system while dla\_csb\_clk for the configurable interface. These clock interfaces are connected as a system clock.

- Reset Interface: The *dla\_reset\_rstn* operates as a primary functional reset for the NVDLA core. While the *direct\_reset\_* serves for DFT reset. They are connected to the processor system reset.

- Clock Gating Interface: Here global\_clk\_ovr\_on is tied low to disable noninferred clock gating. tmc2slcg\_disable\_clock\_gating is also kept low to disable the same during DFT.

- System Data Interface: The external data are accessed through master AXI interfaces *nvdla\_core2dbb\_axi*. The DBBIF and SRAMIF buses fetch data from off-chip DRAM and on-chip SRAM respectively.

- Configuration Interface: This slave interface addresses the configurations of hardware layers through an APB bus, APB S.

- Interrupt Port: A single bit level driven interrupt port is used *dla\_intr* to control the processing of different layers.

Figure 3.3: NVDLA Core Packaged IP

- Power Gating Interface: Power gating features are established when these power buses *nvdla pwrbus ram* are tied to 0.

- DFT Interface : The *test mode* is preferred low to disable DFT mode.

#### 3.2.2 NVDLA Wrapper

The NVDLA Wrapper combines NVDLA Core functionality with the configuration and control operations to constitute an exclusive hierarchical system design. The configuration definitions from the host processor are delegated to NVDLA core for managing underlying hardware layers for the provided network description. This interconnection is achieved through configuration space bus, exposed as an APB interface that establishes communication with the central management processor. This APB to CSB bridge RTL model is associated with NVDLA core to develop an NVDLA subsystem. The APB2CSB IP is shown below in the fig 3.4.

In the developed wrapper module the clock and reset interfaces of the custom IPs are made as external pins. While the clock-gating and power-gating features are disabled, connecting to zero constants. Data and configuration interfaces are made as external ports. Also, the interrupt port is connected as an external link. Once these relevant interconnections are completed, the NVDLA Wrapper is packaged as a custom IP to be utilized in the hardware system architecture. The corresponding image of the wrapper module IP is displayed in image 3.5.

Figure 3.4: APB to CSB Bridge Packaged IP

Figure 3.5: Packaged NVDLA Wrapper IP

#### 3.2.3 Hardware System Architecture

The hardware system architecture establishes different system functionalities. Primarily, constitutes the communication between NVDLA hardware core and management processor of the FPGA. Besides, the system architecture specifies memory mapping of different associated soft IP's (peripherals) as well as resource utilization of hardware modules on the FPGA board.

The hardware architecture includes the following and depicted in the succeeding figure 3.6.

- A host processor: Zynq Ultrascale+ MPSoC.

- Associated DMA engine, an AMBA AXI4-compliant acting as memory bus.

- Instructions regulated through Configuration bus and interrupts.

- Peripherals such as AXI-APB bridges, AXI interconnects and constants.

- Clock and reset generators adhered to the whole system.

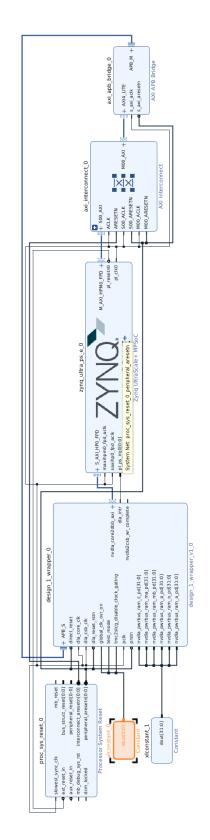

Figure 3.6: NVDLA Hardware Architecture

To accomplish the communication flow of the implemented system, the custom NVDLA wrapper IP communicates with a series of interconnections through PS-PL interfaces of the host processor. The host processor acts as a logical interface between PS and PL while integrating custom IPs in the fabric as a PS+PL configuration. The PS-PL interfaces are configured as follows, the data bus of NVDLA wrapper is connected to High Performance (HP) slave port 0 AXI in full power domain. This S-AXI HP port directly communicates with DDR Controller. While the configuration bus is associated with High-Performance Master (HPM) 0 in full power domain. This HPM-FPD port establishes transmission with the Processing System through the APU engine. The block diagram of Zynq Ultrascale+ MPSoC is shown in the subsequent figure 3.7.

The host processor communicates with its memory and other peripherals at different addresses in the address space. The intercommunication is accomplished through memory mapping at a specific address. The configuration space bus of NVDLA hardware reaches out to the processor through a reserved memory of 64KB. Also, the data bus is interlinked with DDR controllers at a specified address spacing. Thus the memory mapping to different peripherals and memories is done systematically by the tool, utilizing a mapping strategy that minimizes address

Figure 3.7: Block Diagram of Zynq Ultrascale+ MPSoC

decoding complexity. The address segmentation of different peripherals is given below in the figure 3.8.

| 👎 zynq_ultra_ps_e_0                                     |                                   |                   |          |       |                     |                 |

|---------------------------------------------------------|-----------------------------------|-------------------|----------|-------|---------------------|-----------------|

| 🗸 🔣 Data (40 address bits : 0x00A0000000 [ 256M ] .0x04 | 00000000[4G].0x100000000[224G].0x | 00B0000000 [ 256N | 1].0x050 | 00000 | 000 [ 4G ] .0x48000 | 00000 [ 224G ]) |

| m design_1_wrapper_0                                    | APB_S                             | reg               | 64K      |       | 0x00_A000_0000      | 0x00_A000_FFFF  |

| <pre># design_1_wrapper_0</pre>                         |                                   |                   |          |       |                     |                 |

| 🖉 🕅 nvdla_core2dbb_axi (32 address bits : 4G)           |                                   |                   |          |       |                     |                 |

| == zynq_ultra_ps_e_0                                    | S_AXI_HP1_FPD                     | HP1_DDR_LOW       | 2G       | ~     | 0x0000_0000         | 0x7FFF_FFFF     |

| 🚥 zynq_ultra_ps_e_0                                     | S_AXI_HP1_FPD                     | HP1_LPS_OCM       | 16M      | ~     | 0xFF00_0000         | 0xFFFF_FFFF     |

| 🚥 zynq_ultra_ps_e_0                                     | S AXI HP1 FPD                     | HP1 OSPI          | 512M     |       | 0xC000 0000         | 0xDFFF FFFF     |

### Figure 3.8: Address Segmentation of peripherals attached to processor

These memory-mapped master and slave devices are connected through a series of Xilinx's Core IP's to establish appropriate communication. The system comprises two main transmission flows. One for the data and other for the NVDLA configuration space bus (instruction bus). The complete system architecture is discussed and also a corresponding figure 3.9 is presented.

1. Data Transmission flow: The data backbone interface of NVDLA wrapper is connected as Direct Memory Access (DMA) which accelerates data transfer from external DDR4 memory of Zynq FPGA. The data transmission takes place directly to the NVDLA wrapper without passing through the host processor. These interface connections can be instantiated given all the AXI ports are properly matched between the peripherals. This high-performance slave interface is part of programming logic in Zynq MPSoC and designated a data width of 64 bits.

- Configuration flow: The configurations space bus is APB compliant. It is a simplified design for low bandwidth control access like the register interfaces. Unfortunately, these APB interfaces are not supported in Zynq Ultrascale+ FPGA. Therefore transformed into AXI-4 compatible.

- In this case, an AXI-APB peripheral is utilized to translate APB transfers into AXI-4 transfers. This soft IP core functions as a slave on the AXI-4 interface and master on the APB3/APB4 bus. They interlink APB slaves to AXI masters, supporting 32-bit data widths.

- The connection to the memory-mapped master of Zynq MPSoC is established through an AXI interconnect IP. It enables a connection between an AXI master and slave device. The following system employs a data width of 32-bits. This subsequent interface is exploited for AXI memory-mapped transactions.

- 3. Zynq UltraScale+ MPSoC is the main processing system of the hardware architecture. IP cores are attached as a PS+PL configuration. The following PS-PL configurations can be customized based on different requirements. Here the default settings are employed. And the output clock configuration is set to 100MHz.

- 4. The one-bit level driven interrupt interface of NVDLA IP is connected to PL to PS interrupts handled by the host processor.

- 5. The clock and reset interfaces of the system architecture are connected appropriately and sourced from PL clock and reset pins of the processor core.

Once the system integration is done, the developed block design is validated for errors and warnings. Subsequently, the output products of the design are generated as out-of-context as well as a top-level HDL wrapper is constructed for synthesizing the advanced design. Followed by an implementation process carried out to place and route the design components pertinently. This process generates a design specific to the FPGA prototype. Next, the low-level configuration for the specific FPGA is generated as bitstream. Finally, the hardware is exported to SDK including bitstream, this provides the HDF file which configures hardware platform specification. The following emulates hardware-specific flow but the software to run on it is established using Petalinux tools described in the next section.

Figure 3.9: NVDLA System Architecture

# Configuring the Software Environment

. Chapter 4

This chapter encompasses the software flow for the NVDLA system which comprises compilation and run-time environments as shown in the subsequent image 4.1. The compiler incorporates different machine learning model transformations and run-time environment executes these compiled architectures. Here an existing model of Alex-Net (a deep convolutional neural network) architecture is used as a standard compilation model. While the run-time environment engages the software to run this standard on the NVDLA hardware. The PetaLinux tool is used to realize these functions and deploy embedded Linux solutions on FPGA prototyping systems. A detailed description regarding the organization of the execution environment is explained in the consequent chapter.

Figure 4.1: NVDLA Software Stack

#### 4.1 Compilation Build

The compilation build converts a deep neural network into a series of hardware layers compatible with the specified NVDLA hardware configuration. The com-

piled model is optimized for the underlying hardware enhances the performance reducing the model size and its execution time. This build consists of two main phases.

- **Parser**: The parser creates a representation of the neural network as a set of different layers translated from the pre-trained Caffe model given as input. It passes this representation to the compiler and acknowledges if these networks are consistent with the given NVDLA flow.

- **Compiler**: The compiler translates the representations from parser into a series of hardware layers following the insights of NVDLA specification defined during implementation. It maps the network operations to the respective functional blocks of NVDLA. The compiler designates these functionalities primarily based on the NVDLA configurations. These operations are done offline and the compiled neural networks are stored in a standard format known as NVDLA Loadable.

Sadly, the NVDLA compiler was not open-sourced and transparent during this project phase. As a result, the compiler wasn't supporting various network models and their hyper-parameter configurations. Therefore the available network standard of Alex-Net, an used case with the NVDLA hardware, was utilized as a benchmark to evaluate the complete system architecture.

#### 4.2 Run-time Execution

This run-time execution layer includes device drivers to the application software namely User Mode Driver and Kernel Mode Driver. These drivers provide abstraction serving as a translator between the NVDLA hardware and PetaLinux application software. These drivers are incorporated in PetaLinux environments as part of the kernel through loadable modules. Also, they are defined as Application Programming Interfaces wrapped around system portability layers, to facilitate flexible coherence with different hardware platforms. A general framework of the Linux execution environment is described in the figure 4.2.

- User Mode Driver: The User Mode Driver is the primary interface to the application software. It loads the NVDLA loadable standard and submits the inference task to Kernel Mode Driver. This driver loads the network tensors into memory engaging as an ioctl() function. Besides, this also employs synchronizations with different hierarchies before carrying out with inference task.

- Kernel Mode Driver: The Kernel Mode Driver acts as the core module of the software flow. It handles interrupts, associates optimized scheduling of layers and updates dependencies after operations. Further, these drivers program the functional blocks of the underlying NVDLA hardware.

The run time environment of NVDLA architecture is established employing PetaLinux tools. The execution of those device drivers are elucidated in the ensuing sections.

Figure 4.2: Linux Execution Environment Framework

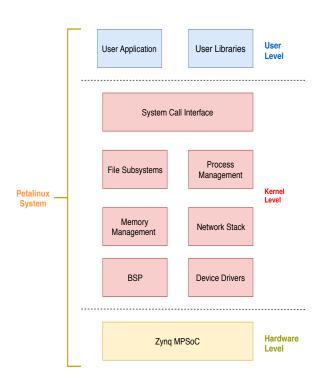

#### 4.3 PetaLinux Flow

The PetaLinux tools are exploited in this project to accelerate the development of NVDLA's run-time environment adopting an embedded Linux based solution. PetaLinux tools facilitate a hardware/software co-design offering integrated Linux configurations and software development tools. Simplifying deployments of hardware designs on FPGA platforms. The complete integration of software stack inclusive of kernels, device drivers, system boot and UMD realizations are described in this section.

The PetaLinux 2018.3 utilized for this purpose operates on a 4.14 Linux Kernel created as an application software available from Xilinx Git. As they do not deliver any commercial Linux distribution. This Linux execution environment is configured on Zynq Ultrascale+ MPSoC, the host processor of NVDLA hardware. The hardware design accomplished in Vivado earlier is exported as a hardware description file to initialize PetaLinux software. The software stack developments of this architecture follows the subsequent workflow as shown in fig 4.3.

Figure 4.3: PetaLinux Flow

#### 4.3.1 Initializing the PetaLinux environment

The primary step constitutes of initializing the PetaLinux environment. The hardware description file imported from the corresponding Vivado tools provides information to PetaLinux, generating appropriate software settings and Boot-loaders. Essentially boot header files, device tree source files, and Kernel drivers. Here the PetaLinux environment is initialized to configure kernel and u-boot to point to the SD boot. The SD card acts as the only memory storage device in this case, therefore the Root Filesystem is set to the same type.

#### 4.3.2 Building the Kernel

PetaLinux provides the flexibility to build custom Linux distribution establishing diverse system tool-kits and libraries in the root directory. An optimal package group with essential tools are adopted in the Linux kernel to build API sub-routines interface to hardware. With these elementary system organizations complete, the petalinux-build is executed to build the kernel system image.

#### 4.3.3 Device Drivers as Loadable Kernel Modules

Most of the fundamental device drivers are enabled while building the above kernel image. But explicit NVDLA device drivers are defined as loadable kernel modules. As a result, an external module is created over the pre-built kernel.

Linux Operating Systems typically maintains high compliance providing capabilities to extend kernel features during run-time. The functionalities of these Linux kernels are customized on the fly through programmable modules. These modules are compiled with the Linux kernel and built into Kernel object files (.ko) which are loaded using insmod during boot. These modules comprise programmable sections that establish communication between the kernel and NVDLA hardware.

#### 4.3.4 Device trees and Reserved Memory

Device trees are wielded as the default methodology to describe low-level hardware information from the boot-loader to the kernel. They are constituted in the source include files (.dtsi). It includes a simple tree structure of nodes and properties that determines the peripheral devices available for the kernel in the current environment. The OS uniquely identifies the underlying NVDLA hardware through the compatible property specifying the exact device information.

A reserved memory is delegated for custom device driver usage from system RAM and these address spaces cannot be exploited by the kernel. Here 1GB memory is reserved for memory-mapped devices specifically for DDR memory interface through Processor Subsystems (PS DDR). This PS DDR is assigned a base address and memory size. The address-cells and size-cells are selected 2 for designating 64-bit addressing schemes in the device tree. The reg field defines the address range used by the device. The PetaLinux project is recompiled to effect the encompassed module and device tree settings. A snippet of the device tree is encompassed below in fig 4.4.

```

/include/ "system-conf.dtsi"

/{

reserved-memory {

#address-cells = <2>;

#size-cells = <2>;

ranges;

nvdla_reserved: buffer@0 {

no-map;

reg = <0x0 0x4000000 0x0 0x4000000>;

};

};

};

&design_1_wrapper_0 {

compatible = "nvidia,nvdla_2";

memory-region = <&nvdla_reserved>;

};

```

Figure 4.4: Device Tree

#### 4.3.5 SD Boot Configuration