# Evaluation of Discrete-Time Wideband Receivers for NB-IoT

MAGNUS WASTING MASTER'S THESIS DEPARTMENT OF ELECTRICAL AND INFORMATION TECHNOLOGY FACULTY OF ENGINEERING | LTH | LUND UNIVERSITY

### Evaluation of Discrete-Time Wideband Receivers for NB-IoT

Magnus Wasting

Department of Electrical and Information Technology Lund University

Supervisor: Henrik Sjöland

Examiner: Pietro Andreani

October 31, 2021

© 2021 Printed in Sweden Tryckeriet i E-huset, Lund

### Abstract

A receiver that covers several RF bands requires multiple front-end filters which increases the cost in terms of components and/or board/silicon area. Front-end filters assist a receiver to withstand interference at multiples of its down-conversion frequency. Analog discrete-time filters have gained a lot of traction lately, mainly due to their promising architecture, achieving baseband filtering, image and harmonic rejection within the same circuit, allowing a fully integration on-chip. These filters will also scale well with further process shrinking as only switches, capacitors and transconductors are required. The evaluation is performed with a standard 40 nm CMOS technology. This thesis aims to focus on those details that previous papers did not describe in detail, such as different topologies of switches and transconductors, mismatches, non-ideal clock sources, capacitive ratios, intermediate frequency, sample rate, common-mode, noise, on-resistance of switches, power consumption, folding, and simulation aspects with Spectre. To understand these filters a dedicated theory chapter is included, starting from a simple first-order low-pass filter up to the complex M/2M band-pass filter which uses M signals and 2M clock phases. All of the above is applied onto a Narrowband Internet of Things (NB-IoT) receiver, as specified in 3GPP release 15. However, a final receiver is not built, only a theoretical one on paper. Discrete-time filters are not suitable for NB-IoT, primarily due to the low requirement on bandwidth (180 KHz), pointing towards a low baseband frequency, which is the opposite of what these filters are suitable for. A high sample rate is required to not degrade the systems performance from folding issues, causing high power consumption. The theoretical receiver is derived to handle all test cases and RF bands, as specified from 3GPP release 15. However, it was not possible to implement a receiver without any front-end filter due to the lack of attenuation of harmonic content over all RF bands. To reduce the power consumption a second-order anti-alias filter was required to reduce the sample rate. The Power consumption was  $6.65 \ mW$  with a supply voltage of 1.2 V, excluding LNA, mixer, clock dividers and ADC.

### Acknowledgements

In no particular order.

Anders Nejdel, as my mentor at Arm. Thanks for help and guidance, you always find a way to explained things in a calm and logical way.

Henrik Sjöland, as my mentor and teacher at Lund University. Thanks for your help and guidance during my thesis, giving me negative feedback, and for answering all my questions during previous courses.

Johan Wernehag, as my teacher at Lund University and colleague at Arm. Thanks for your help at university and Arm, but also for pushing me to finalize this thesis.

Andreas Axholt, as my mentor at Acconeer, colleague and friend. Thanks for all your time during this thesis and during work, I have learned a lot from you. Looking forwards to the years to come.

Anders Kristensson, colleague and friend from Arm and Acconeer. Thanks for all your tips and tricks, especially; a transient simulation never lies. But also for your sense of humor.

Mats Erixon and Joakim Ferm, my team/project leaders at Nordic Semiconductor, by forcing me to finalize this thesis on paid hours.

Pablo Costas, my colleague at Acconeer and friend. Thanks for the help with language and grammar, effectively reducing the grammar mistakes in this thesis by at least an order of magnitude.

### Popular Science Summary

In today's world almost everything is connected by a wireless connection. Given the past history even more will be connected, even for things that no one asked for, perhaps even a can opener. All devices should also be battery powered with several years between any charging. Which can be summarized with other words; how can we create a wireless device that's both cheap and barely consumes any energy? Both of these parts are solved by further integration onto silicon, which is the building foundation of an integrated circuit, namely 'chips' or transistors. You find these transistors in everything from your smart LED lamp to your mobile phone.

The cost aspects can be explained through 'economy of scale', which simplifies to "producing two of the same will always be cheaper than two different things". A real-world example of this would be the dual zone fridge freezer, one could argue that the freezer is integrated into the fridge and thereby making it cheaper to buy then buying the two by themselves.

I think we all have heard about submicroscopic transistors, which year after year shrink in size, mainly due to the science and engineering efforts into this field. As an example, the physical diameter of the COVID-19 virus is  $\sim 100 \ nm$  [1] which in comparison to today's transistors is colossal. This thesis is built upon a rather old manufacturing process of 40 nm, in which its mass production started back in 2008. Today you can buy phones in masses that are built upon 5 nm transistors.

In any case, this might sound rather good, which it is! At least for computers and phones as smaller devices means less energy for the same performance, which also goes the other way around. Given the same speed, one can reduce the energy consumption, effectively increase the battery time. But for analog circuits, such as amplifiers, there is not much to gain. There are even aspects where it's worse. Analog discrete-time circuits are supposedly a solution to this, as it scales with the same parameters as computers, but also opens the possibility of more integration onto silicon due to their nature in design, and thereby reducing its cost.

# List of Acronyms

| 5G          | The fifth generation technology standard for broadband cellular networks. |

|-------------|---------------------------------------------------------------------------|

| 3GPP        | 3rd Generation Partnership Project                                        |

| ADC         | Analog-to-Digital Converter                                               |

| BB          | Baseband                                                                  |

| BPF         | Band-pass Filter                                                          |

| BW          | Bandwidth                                                                 |

| СМ          | common-mode                                                               |

| CMOS        | Complementary Metal–Oxide–Semiconductor                                   |

| CMRR        | common-mode Rejection Ratio                                               |

| CS          | Common Source (transconductor)                                            |

| CSBPF       | Charge Sharing Band-pass Filter                                           |

| DCR         | Direct-Conversion Receiver                                                |

| DR          | Dynamic Range                                                             |

| DT          | Discrete-Time                                                             |

| E-UTRA      | Evolved Universal Terrestrial Radio Access                                |

| FB          | Feedback (transconductor)                                                 |

| FIR         | Finite Impulse Response                                                   |

| FS          | Full Scale                                                                |

| $g_m$ -cell | Transconductor                                                            |

| GSM         | Global System for Mobile Communications                                   |

| HB          | High Band                                                                 |

| IIP         | Input-referred Intercept Point                                            |

- LB Low Band

- FD Fully Differential (transconductor)

- HPF High Pass Filter

- IF Intermediate Frequency

- IMRR Image Rejection Ratio

- IIR Infinite Impulse Response

- IP2 Second-order Intercept Point

- IP3 Third-order Intercept Point

- LNA Low Noise Amplifier

- LO Local Oscillator

- LPF Low Pass Filter

- LSB Lower-Sideband

- LTE Long Term Evolution

- MB Mid-Band

- MC Monte Carlo

- MOM Metal-Oxide-Metal

- NB-IoT Narrowband Internet of Things

- **QPSK** Quadrature Phase Shift Keying

- OFDM Orthogonal Frequency-Division Multiplexing

- OFDMA Orthogonal Frequency-Division Multiplexing Access

- PAC Periodic AC Analysis

- PAR Peak-to-Average Ratio

- PD Pseudo-Differential (transconductor)

- PLL Phase-Locked Loop

- PSS Periodic Steady State

- PXF Periodic Transfer Function

- Q-factor Quality factor

- **QPSK** Quadrature Phase Shift Keying

- SAW Surface Acoustic Wave

- SNR Signal to Noise Ratio

- STS Single Transistor Switch

- TA Transconductance Amplifier

- TG Transmission Gate

- UE User Equipment

- ULB Ultra Low Band

- USB Upper-Sideband

# Table of Contents

| 1 | Intro | oduction                                              | . 1  |

|---|-------|-------------------------------------------------------|------|

|   | 1.1   | Background                                            | 1    |

|   | 1.2   | A Typical Wideband Receiver                           | 2    |

|   | 1.3   | Thesis Scope                                          | 3    |

|   | 1.4   | Thesis Structure                                      | 4    |

| 2 | The   | ory                                                   | 5    |

|   | 2.1   | Intermodulation Products                              | 5    |

|   | 2.2   | Sampling and Anti-Aliasing                            | 7    |

|   | 2.3   | Sinc Filter                                           | 8    |

|   | 2.4   | General Information of Discrete-Time Filters          | 10   |

|   | 2.5   | Discrete-time Low-pass Filter                         | 12   |

|   | 2.6   | Complex Band-pass Filter                              | 16   |

|   | 2.7   | Pipeline and/or Parallelization                       | 24   |

|   | 2.8   | Harmonic Rejection                                    | 25   |

| 3 | 3GP   | P NB-IoT Standard and Receiver Specification          | . 29 |

|   | 3.1   | Frequency Bands                                       | 30   |

|   | 3.2   | Signal Power and Noise Floor                          | 31   |

|   | 3.3   | Receiver Test Cases                                   | 31   |

|   | 3.4   | Summary                                               | 35   |

| 4 | Low   | Noise Amplifier and Mixer                             | 39   |

|   | 4.1   | Low Noise Amplifier                                   | 39   |

|   | 4.2   | Mixer                                                 | 39   |

|   | 4.3   | Simulations                                           | 41   |

| 5 | Disc  | rete-Time Filters                                     | 43   |

|   | 5.1   | How to Simulate with Spectre                          | 43   |

|   | 5.2   | Resource Overview                                     | 46   |

|   | 5.3   | Switch Topology                                       | 47   |

|   | 5.4   | Sideband Selection                                    | 49   |

|   | 5.5   | Relation Between IF, Capacitor Ratios and Sample Rate | 49   |

|   | 5.6   | Simulations                                           | 50   |

| 6  | Tran  | sconductance Amplifiers        | _ 6  |

|----|-------|--------------------------------|------|

|    | 6.1   | Topologies                     | 6    |

|    | 6.2   | Simulations                    | 6    |

| 7  | Harr  | nonic Rejection                | _ 7  |

|    | 7.1   | Topologies                     | 7    |

|    | 7.2   | Simulations                    | 7    |

| 8  | Disc  | ussion and a Receiver on Paper | _ 8  |

|    | 8.1   | Discrete-Time Filters          | 8    |

|    | 8.2   | A Receiver on Paper            | 8    |

| 9  | Con   | clusions                       | _ 9  |

|    |       | Discrete-time Low-pass Filter  |      |

|    |       | Discrete-time Band-pass Filter |      |

| Re | feren | ces                            | _ 9' |

# List of Figures

| 1.1  | Block diagram of a typical wideband receiver                                                                                                                     | 2  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1  | Intercept point diagram between signal and intermodulation products two and three. In this example IIP2 is 20 $dBm$ while IIP3 is 0 $dBm$ .                      | 6  |

| 2.2  | A continuous signal and its discrete representation by sampling with a time period of $T_s$ .                                                                    | 7  |

| 2.3  | Sampling and its aliasing effects within the complex plane. a) is with an input frequency of $f_s/8$ , b) with $\frac{7}{8}f_s$ and c) with $f_s$ . In all cases |    |

|      | the sample rate is $f_s$                                                                                                                                         | 8  |

| 2.4  | Convolution of a time window creates a sinc filter in frequency                                                                                                  | 9  |

| 2.5  | General implementation of the sinc filter.                                                                                                                       | 9  |

| 2.6  | Illustration of the combined frequency response of a generic discrete-                                                                                           |    |

|      | time system and its sinc filter.                                                                                                                                 | 10 |

| 2.7  | A generic discrete-time filter with its two clock phases                                                                                                         | 11 |

| 2.8  | Concept of a switched capacitor                                                                                                                                  | 11 |

| 2.9  | A simple $g_m$ -cell with its load                                                                                                                               | 12 |

| 2.10 | Ideal first-order low-pass filter with voltage sampling                                                                                                          | 12 |

| 2.11 | Ideal first-order low-pass filter with charge sampling.                                                                                                          | 13 |

| 2.12 | Ideal second-order low-pass filter with combined charge and voltage                                                                                              |    |

|      | sampling                                                                                                                                                         | 14 |

| 2.13 | Ideal M'th order low-pass filter.                                                                                                                                | 15 |

| 2.14 | Ideal 4/4 complex band-pass filter.                                                                                                                              | 16 |

| 2.15 | Ideal $M/M$ complex band-pass filter.                                                                                                                            | 18 |

| 2.16 | Ideal $M/2M$ complex band-pass filter.                                                                                                                           | 20 |

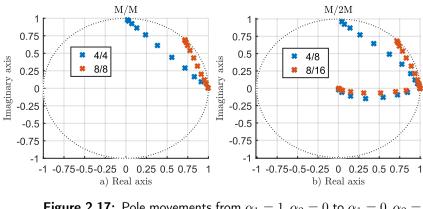

| 2.17 | Pole movements from $\alpha_1 = 1, \alpha_2 = 0$ to $\alpha_1 = 0, \alpha_2 = 1$ , a) shows                                                                      |    |

|      | the poles for a $M/M$ while b) shows the $M/2M$ . All poles starts at                                                                                            |    |

|      | $e^{j0\pi}$                                                                                                                                                      | 22 |

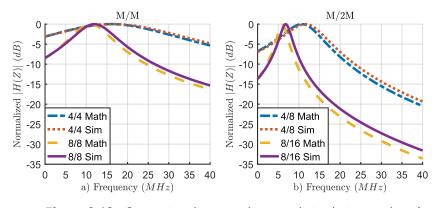

| 2.18 | Comparison between theory and simulation results, a) shows the $M/M$                                                                                             |    |

|      | while b) shows the $M/2M$ .                                                                                                                                      | 23 |

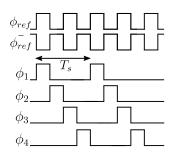

| 2.19 | Division of a differential reference clock into four phases, its period $T_s$                                                                                    |    |

|      | will therefore be doubled compared to its reference clock.                                                                                                       | 24 |

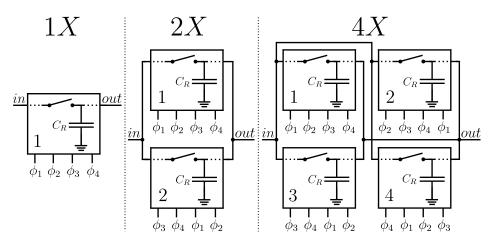

| 2.20 | Concept of pipelining a discrete system to effectively increase its sam-                                                                                         |    |

|      | ple rate, $1X$ , $2X$ and $4X$ will sample at a frequency of $f_s$ , $2f_s$ and                                                                                  |    |

|      | $4f_s$ respectively.                                                                                                                                             | 25 |

|      | • • •                                                                                                                                                            |    |

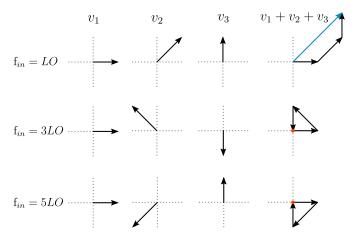

| 2.21 | Concept of harmonic rejection with 8 phases, $v_1$ shows the starting positions while $v_2$ and $v_3$ shows the forthcoming position. With $f_{in}$ equal to $LO$ the step size is one while with $3LO$ and $5LO$ the step size is three and five, respectively. $v_1 + v_2 + v_3$ shows the sum of these three vectors, $f_{in}$ equal to $LO$ increases the length while $3LO$ and $5LO$ are cancelled. | 26 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

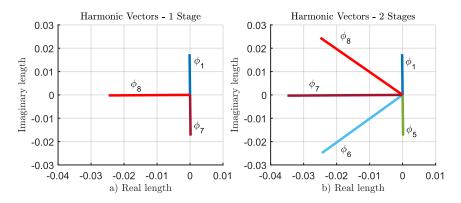

| 2.22 | Residual of the third harmonic with a theoretical 8 phase harmonic rejection circuit where one phase as an error of $1^{\circ}$ , a) shows the content after the first stage while b) shows the second stage                                                                                                                                                                                              | 27 |

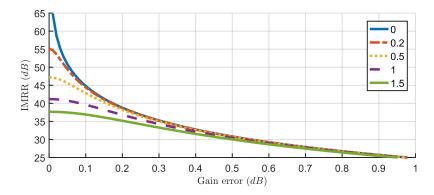

| 2.23 | Theoretical image rejection ratio with gain error between 0 to 1 $dB$ and a phase error from 0° to $1.5^{\circ}$                                                                                                                                                                                                                                                                                          | 28 |

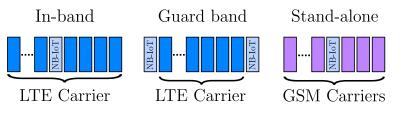

| 3.1  | Illustration where a NB-IoT channel can be placed, either as in-band, guard band or stand-alone.                                                                                                                                                                                                                                                                                                          | 30 |

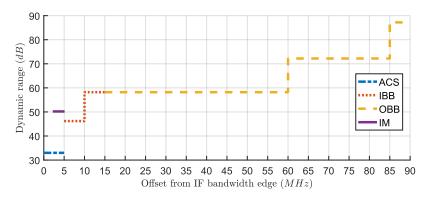

| 3.2  | Dynamic range mask for NB-IoT with the assumption of zero attenu-<br>ation within the receiver.                                                                                                                                                                                                                                                                                                           | 35 |

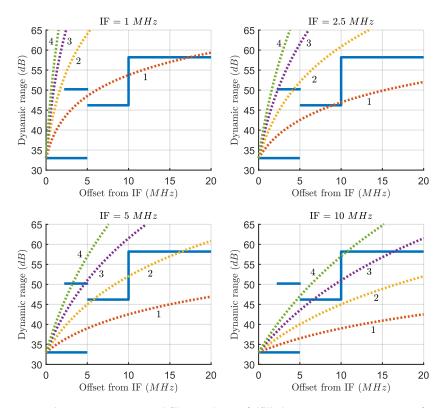

| 3.3  | Required filter order to fulfill the receiver tests at a IF of 1, 2.5, 5 and 10 $MHz$ , the blue solid line represents the mask while the four dotted lines shows different filter order, marked with 1 to 4                                                                                                                                                                                              | 37 |

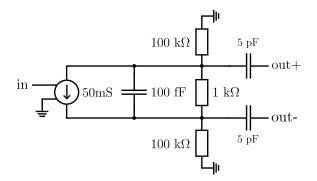

| 4.1  | Implementation of the ideal differential LNA.                                                                                                                                                                                                                                                                                                                                                             | 39 |

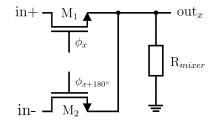

| 4.2  | Schematic of the Mixer.                                                                                                                                                                                                                                                                                                                                                                                   | 40 |

| 4.3  | Text                                                                                                                                                                                                                                                                                                                                                                                                      | 41 |

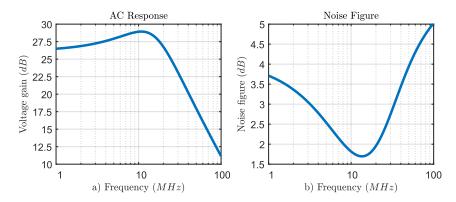

| 4.4  | Reference figures of the LNA and mixer, a) AC response and b) noise figure                                                                                                                                                                                                                                                                                                                                | 41 |

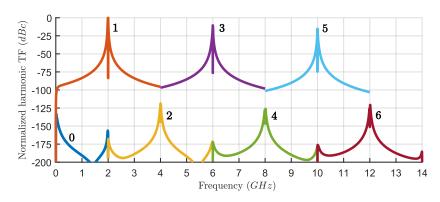

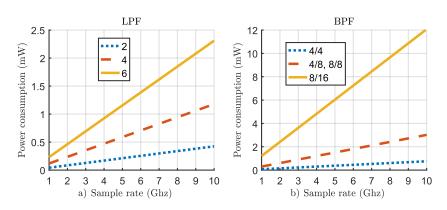

| 5.1  | Typical response of a PSS + PXF simulation with six harmonics at a beat frequency of 2 $GHz$ and a wide frequency range                                                                                                                                                                                                                                                                                   | 45 |

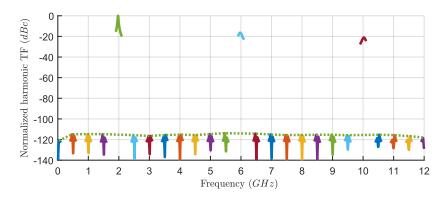

| 5.2  | Typical response of a PSS + PXF simulation with 24 harmonics at a beat frequency of 0.5 $GHz$ and a narrow frequency range, the harmonic noise floor is depicted as the dotted line                                                                                                                                                                                                                       | 45 |

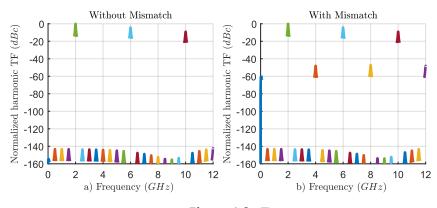

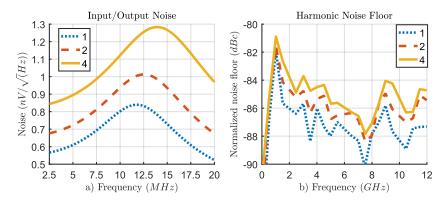

| 5.3  | A generic simulation of a filter harmonic noise floor with different tolerances, 1 are loose while 4 are tight, a) are without mismatches                                                                                                                                                                                                                                                                 | 40 |

|      | while b) are with mismatch.                                                                                                                                                                                                                                                                                                                                                                               | 46 |

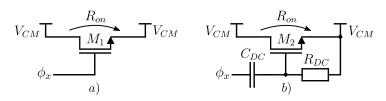

| 5.4  | Implementation of the single transistor switch, without DC-shift in a) and with in b).                                                                                                                                                                                                                                                                                                                    | 48 |

| 5.5  | Implementations of the transmission gate.                                                                                                                                                                                                                                                                                                                                                                 | 48 |

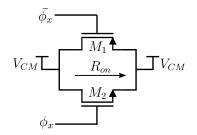

| 5.6  | Sideband selection from a PSS + PXF simulation. The dotted line represents the response when both mixer and DT-BPF clocks are running in the same order while the other line has its clocks order inverted, either the mixer or filter but not both.                                                                                                                                                      | 49 |

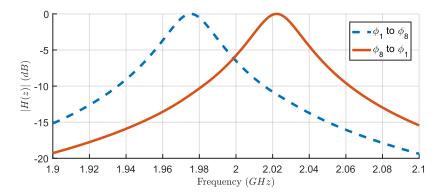

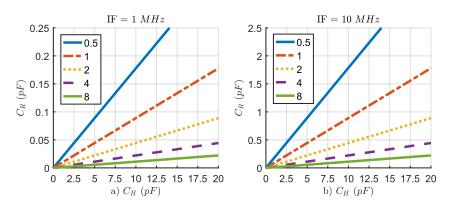

| 5.7  | Relationship of a $8/8$ DT-BPF between $C_H$ and $C_R$ with different sampling rates from 0.5 to 8 $GHz$ , a) is with a IF of 1 $MHz$ while b) is 10 $MHz$ . Note that the scale of the two y-axes are not the same.                                                                                                                                                                                      | 50 |

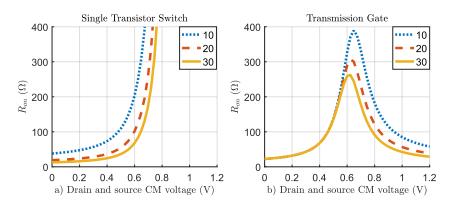

| 5.8  | Simulation of the on-resistance with different transistor widths from                                                                                                                                                                                                                                                                                                                                     | 50 |

| 5.5  | 10 to 30 $\mu m$ . a) shows the STS with an NMOS while b) shows the TG.                                                                                                                                                                                                                                                                                                                                   | 51 |

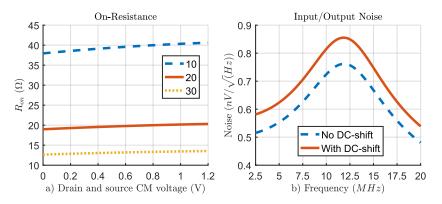

| 5.9  | a) On-resistance with different transistor widths from 10 to 30 $\mu m$ of the STS with DC-shift. b) Input/output noise of an $8/8$ DT-BPF, due |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | to the design of $M/M$ the input and output-referred noise are equal.                                                                           | 51 |

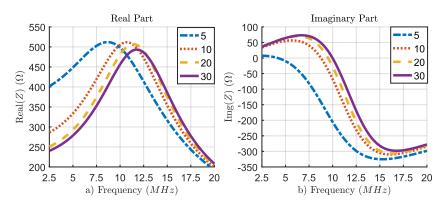

| 5.10 | Differential impedance simulation of an $8/8$ DT-BPF with different                                                                             |    |

|      | transistors widths of 5, 10, 20 and 30 $\mu m$ , a) shows the real while b)                                                                     |    |

|      | shows the imaginary part.                                                                                                                       | 52 |

| 5.11 | Simulation of an 8/8 DT-BPF with different transistor widths of 10,                                                                             |    |

|      | 20 and 30 $\mu m$ on a single transistor switch, a) shows the input/output                                                                      |    |

|      | noise, due to the design of $M/M$ the input and output-referred noise                                                                           |    |

|      | are equal. b) shows the normalized power consumption for one switch                                                                             |    |

|      | at $f_s = 1 \ GHz$ .                                                                                                                            | 53 |

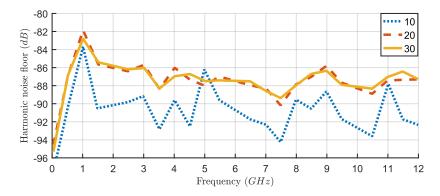

| 5.12 | Simulation of the harmonic noise floor with different transistors widths                                                                        |    |

|      | of 10, 20 and 30 $\mu m$ and the LNA, mixer and one $8/8$ DT-BPF stage.                                                                         | 54 |

| 5.13 | Simulation of the harmonics noise floor with different rise and fall                                                                            |    |

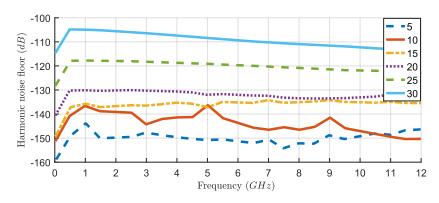

|      | times of its clocks, from 5 to 30 $ps.$                                                                                                         | 55 |

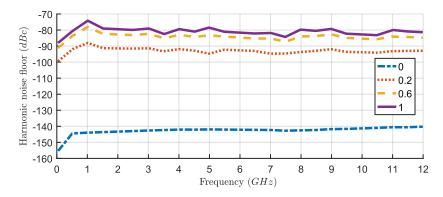

| 5.14 | Simulation of the harmonics noise floor with different phase error on                                                                           |    |

|      | $\phi_{0^\circ}$ , from $0^\circ$ to $1^\circ.$                                                                                                 | 55 |

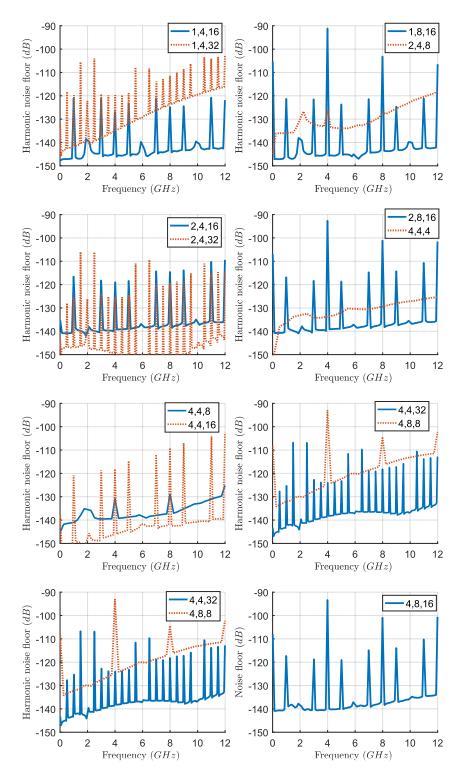

| 5.15 | Harmonic noise floor spectrum with 15 different samples rates of three                                                                          |    |

|      | subsequent $8/8$ DT-BPF with its transconductor                                                                                                 | 57 |

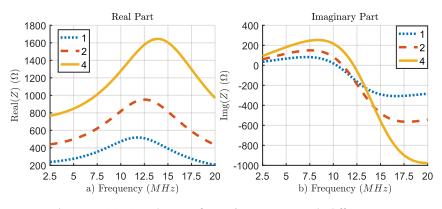

| 5.16 | Simulation of an $8/8$ DT-BPF with different capacitor values, $C_x/1$ ,                                                                        |    |

|      | $C_x/2$ and $C_x/4$ , a) shows the real part while b) the imaginary part                                                                        | 59 |

| 5.17 | Simulation with different capacitor values, $C_x/1$ , $C_x/2$ and $C_x/4$ . a)                                                                  |    |

|      | shows the input/output noise of an $8/8$ DT-BPF, due to the design                                                                              |    |

|      | of $M/M$ the input and output-referred noise are equal. b) shows the                                                                            |    |

|      | harmonics noise floor of the LNA, mixer and one $8/8$ DT-BPF stage.                                                                             | 60 |

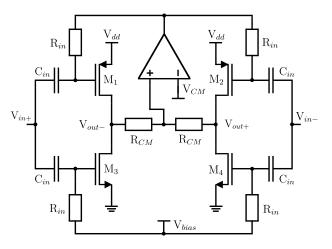

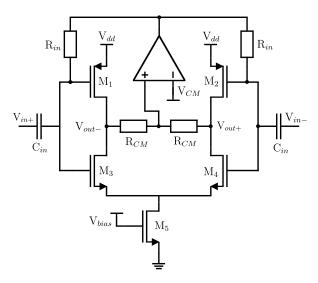

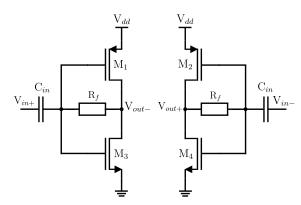

| 6.1  | Schematic of the pseudo differential inverter.                                                                                                  | 62 |

| 6.2  | Schematic of the fully differential inverter.                                                                                                   | 63 |

| 6.3  | Schematic of the feedback inverter.                                                                                                             | 64 |

| 6.4  | Schematic of the common source amplifier.                                                                                                       | 65 |

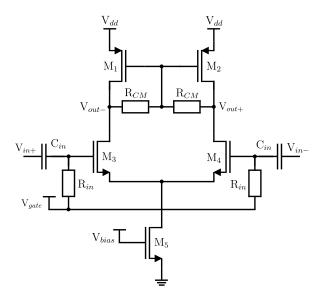

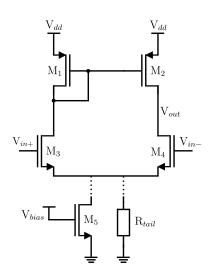

| 6.5  | Schematic of the common-mode amplifier.                                                                                                         | 67 |

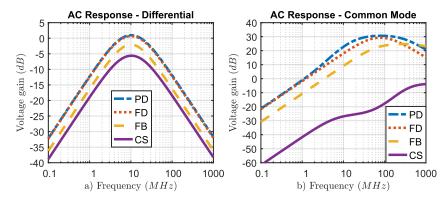

| 6.6  | AC response of the four transconductors, a) shows differential gain                                                                             | 01 |

| 0.0  | while b) show the common-mode gain.                                                                                                             | 68 |

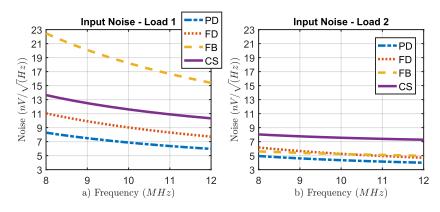

| 6.7  | Input-referred noise of the four transconductors, a) shows the standard                                                                         |    |

|      | differential load of 10 $pF$ while b) is with 0.2 $pF$ .                                                                                        | 69 |

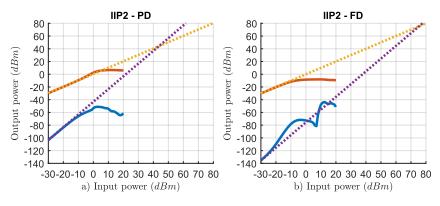

| 6.8  | Input-referred IP2 of PD in a) and FD in b).                                                                                                    | 70 |

| 6.9  | Input-referred IP2 of FB in a) and CS in b).                                                                                                    | 70 |

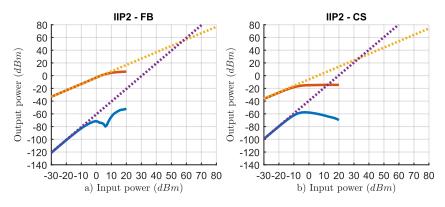

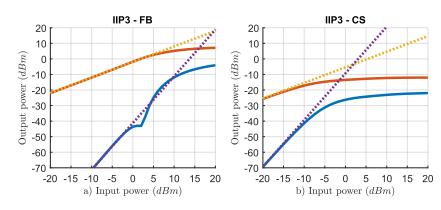

| 6.10 | Input-referred IP3 of PD in a) and FD in b).                                                                                                    | 71 |

| 6.11 | Input-referred IP3 of FB in a) and CS in b).                                                                                                    | 72 |

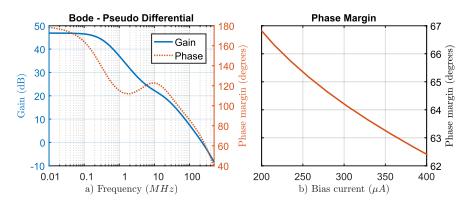

| 6.12 | Simulation of the CM amplifier controlling the PD inverter, a) shows                                                                            |    |

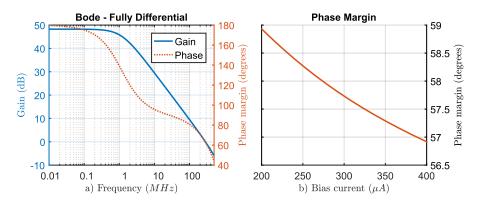

|      | a Bode plot while b) shows the phase margin over bias current                                                                                   | 73 |

| 6.13 | Simulation of the CM amplifier controlling the FD inverter, a) shows                                                                            |    |

|      | a Bode plot while b) shows the phase margin over bias current                                                                                   | 73 |

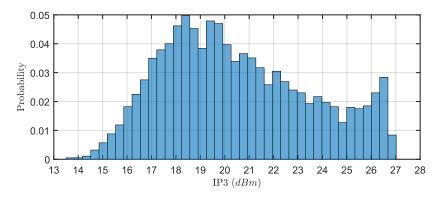

| 6.14 | Distribution of a Monte Carlo simulation with IP3 of the FB stage,                                                                              |    |

|      | 10000 runs were performed                                                                                                                       | 75 |

| 7 4  |                                                                                                                                                 | 70 |

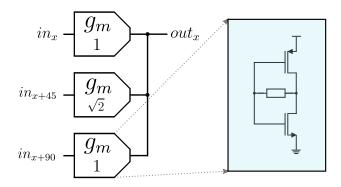

| 7.1  | Implementations of a $g_m$ -HR unit-cell                                                                                                        | 78 |

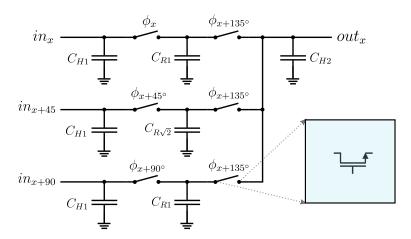

| 7.2<br>7.3 | Implementations of the DT-HR unit-cell                                                                                                                                                                                | 79 |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

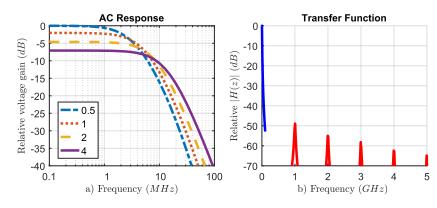

| 1.5        | from 0.5 to 4 GHz. b) Relative transfer function of the DT-HR with a sample rate of 1 GHz.                                                                                                                            | 80 |

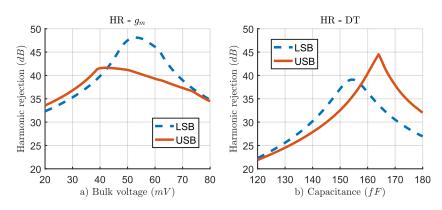

| 7.4        | Rejection of both upper and lower sideband of the third harmonic, with $g_m$ in a) and DT in b)                                                                                                                       | 81 |

| 7.5        | Harmonic rejection of only the upper sideband, a) shows the driving strength by increasing the inverters size while b) shows the size of all switches, both at different sampling rates from 0.5 to 4 $GHz$           | 81 |

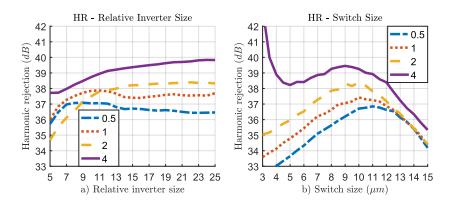

| 8.1        | Estimated power consumption to run a DT filter. a) shows the LPF variant with a order of 2, 4 and 6 while b) shows the BPF with the $4/4$ , $4/8$ , $8/8$ and $8/16$ configuration. Their respective $g_m$ -cells are | 07 |

|            | excluded                                                                                                                                                                                                              | 87 |

| 8.2        | Block diagram of a NB-IoT receiver                                                                                                                                                                                    | 91 |

## List of Tables

| 32       |

|----------|

| 33       |

| 34       |

| 34       |

| 36       |

| 38       |

| 47       |

| 58       |

|          |

| 62       |

| 63<br>65 |

| 05<br>66 |

| 00       |

| 67       |

|          |

|          |

|          |

| 74       |

|          |

| 75       |

|          |

| 7.1 | Harmonic rejection of the upper and lower sideband with a Monte     |    |

|-----|---------------------------------------------------------------------|----|

|     | Carlo simulation, 1724 runs with the $g_m$ version while the DT ran |    |

|     | with 1510 runs                                                      | 82 |

### . Chapter

### Introduction

### 1.1 Background

Modern telecommunications are continuously growing with even more connected devices and higher data traffic every year that passes. The fifth generation (5G) is the latest and was commercially launched at the end of 2018 in several cities [2]. The 5G New Radio standard was developed by the 3rd Generation Partnership Project (3GPP) and first specified in release 13. As with previous generations, the naming scheme is a collection of several different radio bands and protocols.

Narrowband Internet of Things (NB-IoT) can be seen as a subgroup of 5G and it has been designed for massive amount of connected devices that both have low power and throughput. These devices consist of sensors, meters, wearables, and other so called "smart" things. NB-IoT was also developed by 3GPP and first specified in release 13. Cellular IoT connections were one billion in 2018 and are expected to grow to 4.1 billions in 2024, at an annual growth rate of 27 percent, where NB-IoT is expected to have a big market share [2].

A big portion of the NB-IoT market is low cost devices, especially the "smart" IoT as these will be marked to consumers, and one of the strongest drivers in consumer electronics are the competition of price. These devices also require longer battery life, up to 10 years is a common sales pitch, although its battery life is strongly dependent on how often one sends and receives data.

For a CMOS receiver this means removal of even more off-chip components and integrating these on-chip. Which is a lot easier said than done. For example, if the front-end filters described in chapter 1.2 are meant to be integrated on-chip, more silicon area is required, which makes it more expensive although the end cost would be lower if it would be mass produced. Majority of the cost comes from off-chip components, board space, assembly and verification. Another point is the low Q-factor of on-chip inductors, at least in comparison to off-chip inductors and Surface Acoustic Wave (SAW) filters that are normally used [3]. A lower Q-factor will results in a flatter filter response, hence less attenuation of harmonic content and out of band blockers. This would in turn set higher linearity and filtering requirements on the whole receiver to not increase the Analog-to-Digital Converter (ADC) bit resolution, as the dynamic range (DR) of the ADC will increase with less filtering.

### 1.2 A Typical Wideband Receiver

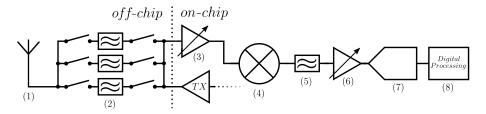

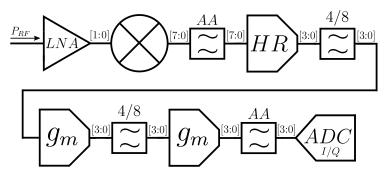

Figure 1.1: Block diagram of a typical wideband receiver.

The building blocks of a typical wideband receiver in CMOS technology can be seen in figure 1.1. The antenna is the first part (1) where radiant energy is absorbed and converted into an electrical signal. The antenna impedance is usually 50  $\Omega$ .

Next in-line are multiple of switches (2) with their corresponding front-end filter. The switches connect the antenna to either the receiver or transmitter, depending on if it is sending or receiving information. The switches can also route the signal through different front-end filters depending on what frequency band is used. These filters can also be in combination with a balun that convert the signal from single-ended to differential. The filter type in question is typically a band-pass filter and is there to reduce harmonic content and out of band interference.

Now comes the first amplifier (3), which is a special Low Noise Amplifier (LNA) with a moderate to high gain  $\sim 25 \ dB$ . The amplifier will reduce noise requirement of all forthcoming blocks accordingly to Friis formula for noise. The LNA can either be a true wideband with a flat frequency response over several GHz or have multiple resonant circuits, one for each RF band. The first implementation requires less area and attains close to zero attenuation of unwanted harmonic content, while the other is opposite in both cases.

The mixer (4) performs frequency mixing of the RF signal and the Local Oscillator (LO). Mathematically speaking, a frequency multiplication between the RF and LO are performed and it creates new frequencies, namely the difference between RF and LO and all combinations of their harmonic content. Fourier analysis is a great tool to express the complete transfer. The new frequency from the first harmonic of both RF and LO is called the Intermediate Frequency (IF) and contains the wanted information of the RF signal at a much lower frequency. By using a lower frequency, the forthcoming blocks can thereby be designed with a lower bandwidth, hence they are less sensitive to parasitic capacitance. These blocks are also grouped together figurative as the Baseband (BB) to emphasize

the difference between the high-performance RF side with frequencies up in the GHz range and the BB side with frequencies between DC and a couple of MHz.

The mixer is followed by a BB-filter (5), the filter type is a low-pass in directconversion receiver (also known as homodyne or zero-IF receiver) as the IF frequency is centred at DC. If the IF is not centred at DC, the filter is thereby a band-pass and is known as Superheterodyne receiver. In any case, the task of the BB filter is to attenuate frequencies that are close to the carrier, as adjacent channels or in-band interference. The signal strength at this stage is still to low and needs further amplification.

The weak signal is then amplified by the BB amplifier (6) to a level well above the quantization noise floor. This amplifier also needs to have variable gain to maximize the dynamic range of the analog-to-digital converter (ADC) (7), which is the last analog block before the signal is quantified and converter to a digital representation. The ADC should have its own anti-aliasing filter to prevent folding, but it could be integrated into the BB amplifier given that it is normally bandwidth limited. The last stage (8) is post-processing were decoding and further digital filtering are done.

### 1.3 Thesis Scope

This thesis started as a request from Arm, they were interested in an evaluation of discrete-time receivers and if they are suitable for NB-IoT, without any external front-end filter. This means that the receiver must be able to handle all interference that 3GPP specifies, without sacrificing other key parameters.

However, it must be stated that halfway through the thesis work Arm decided to close their analog department and essentially fired everyone, including me and my mentors. As a result, further thesis work was delayed until Acconeer encouraged me to finalize it. Although this never happened due to personal issues and thereby delayed my work again. Later, I relocated to Nordic Semiconductor where the thesis was finalized.

The filter in question from a discrete-time receiver is known as Charge Sharing Band-pass Filter (CS-BPF) and has gained a lot of traction lately [4–8], these filters are built upon the old N-path filter from 1960 [9] and do no longer suffer from a repetitive frequency response, which effectively means that it is possible to attenuate negative frequencies, or in other words, the image frequency.

The main selling points of CS-BPF are supposedly better performance scaling with a shrinking process node as they can handle the reduction of supply voltage. This comes down to the simplicity of the filters as the building blocks are simple  $g_m$ cells, capacitors, and switches (single transistors). These filters are also supposedly stable over Process, Voltage and Temperature (PVT) as the center frequency is only dependent on a capacitive ratio and its sample rate. The focus will be on; what is needed to fulfill the 3GPP requirements for a NB-IoT receiver with CS-BPF as baseband filters and  $g_m$ -cells for amplification. By removing the input front-end filter, the receiver is now susceptive to interference located at a multiple of its LO frequency and thereby harmonic rejection is required and will be looked upon. The power consumption of the whole BB chain is set to max 10 mW and the IF is set to 10 MHz. The low power consumption is needed as NB-IoT devices are intended to be powered from a battery while the rather high IF was requested from Arm with the argument that an IF of 10 MHz would remove all issues caused by intermodulation and 1/f noise. No limit on area was set, although capacitors in the nF range is out of the question. The power supply voltage is set to 1.2 V given that this thesis is built upon a typical 40 nm CMOS bulk technology.

Because of time constrains this thesis will only look on the BB side of the mixer. However, the RF side is still needed in several simulation and must therefore be built. The implementation of the LNA was an ideal amplifier while the mixer was with physical models in CMOS, more about this is explained in chapter 4.

### 1.4 Thesis Structure

A short list of all forthcoming chapters and a brief explanation about them.

- Chapter 2, Theory : A detailed explanation of the mathematics behind analog discrete-time filters and their subcategories.

- Chapter 3, 3GPP NB-IoT Standard and Receiver Specification : What is 3GPP? How are NB-IoT specified from a receiver perspective? A dynamic range mask with filter requirement is also derived from its specifications.

- Chapter 4, Low Noise Amplifier and Mixer : Disclosure of LNA and mixer that was used in several simulations.

- Chapter 5, Discrete-Time Filters : A detailed investigation of the sub-blocks within a discrete-time filter and impacts of different design parameters.

- Chapter 6, Transconductance Amplifiers : Four different, but quite similar topologies, were investigated. What are the trade-offs? Is there any clear winner?

- Chapter 7, Harmonic Rejection : Two different topologies of harmonic rejection are looked upon, one is based on continuous-time while the other is discrete-time.

- Chapter 8, Discussion and a Receiver on Paper : Summary of the whole thesis, comments on what we have learned and own opinions. A theoretical NB-IoT receiver is also derived on paper.

- Chapter 9, Conclusions : A short summary with conclusions, will NB-IoT and discrete-time filter work tougher?

### Theory

### 2.1 Intermodulation Products

In a perfect world an ideal amplifier produces an output signal that is proportional to what it is given to its input, no additional information is created or removed. However, in the real-world amplifiers are usually linear at *lower* input levels, to be gradually more and more non-linear at higher levels.

A common way of representing this is seen in eq. 2.1, where A represents the DC component,  $C_1$  the linear gain,  $C_2$  and  $C_3$  the coefficient for the second and third-order products, respectively. With an ideal amplifier only  $C_1$  is non-zero. An important concept from this relationship is that its order is proportional to its growth, second-order products grow by the square while the third with the cube. In terms of power levels, this translates to a slope of one, two and three for the first to third-order respectively.

$$V_{out} = A + C_1 V_{in} + C_2 V_{in}^2 + C_3 V_{in}^3 + \dots + C_n V_{in}^n$$

(2.1)

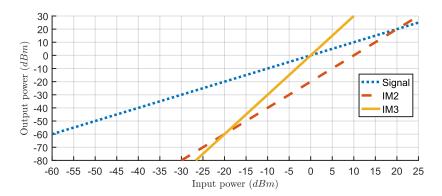

The concept in question is called Intermodulation (IM), which describes the amplitude modulation of at least two different frequencies. IM2 represents the secondorder while IM3 the third-order products. The new frequencies that are created comes from a scaled sum and difference, namely  $f_1 \pm (n-1)f_2$  and  $(n-1)f_1 \pm f_2$ , where n is the intermodulation order. This comes for the core concept from amplitude modulation. Although, not all new frequencies will cause trouble. The product of the sum will go up in frequency by approximately a factor of two, and thereby increasing the distance in the frequency domain from our wanted signal.

The difference though, it can fall directly at our wanted signal or close to it. Given its amplitude it could be high enough to obscure our wanted signal or saturate the forthcoming circuit. In particular the IM2 product of  $f_2 - f_1$  and the IM3 at  $2f_1 - f_2$  and  $2f_2 - f_1$  are the cause of most issues and will set requirements on linearity of all amplifiers. In other words, nothing is perfect, new frequencies will always be created. If an amplifier is good enough, in terms of linearity, the level of these new frequencies will still be below the noise floor and thereby not impact the systems performance.

The question then arises, what is good enough? This is in turn answered by [10] and seen in eq. 2.2 and 2.3, although the M term has been added and represents a margin between the signal and its IM product. IIP stands for Input-referred Intercept Point and is a theoretical point where signal and IM product is equal in strength, the number behind IIP represents the modulation order.

$$IIP2_{min} = 2P_i - P_s + M \tag{2.2}$$

$$IIP3_{min} = \frac{1}{2}(3P_i - P_s + M) \tag{2.3}$$

As an example with two tones, representing an interference and a signal at a power level of  $P_i = -20 \ dBm$  and  $P_s = -50 \ dBm$ , respectively. Given these two levels and a margin of  $M = 10 \ dB$ , with the equations above, the minimum IIP2 is thereby 20 dBm while IIP3 is 0 dBm, which is the same as the cross-points between signal, IM2 and IM3 in figure 2.1. Furthermore, the signal power, both its input and output, are equal to  $-50 \ dBm$ , as in our example the gain is zero. Its IM products are well below its own signal level and thereby will not cause issues. However, the interferer with its higher level at  $-20 \ dBm$  results in a non-negligible IM2 and IM3 level at  $-60 \ dBm$ . Which is  $10 \ dB$  lower compared to our signal at  $-50 \ dBm$ . The difference between our wanted signal and IM products from the interference is only  $10 \ dB$ , which is the same as our given margin of  $10 \ dB$ .

Figure 2.1: Intercept point diagram between signal and intermodulation products two and three. In this example IIP2 is  $20 \ dBm$  while IIP3 is  $0 \ dBm$ .

Note that any frequency information is never told. The signal and interferer could have the same frequency, in that case the interference level is already an issue and IM can be ignored. In another case where the interference is *further* from the signal and thereby not an issue per se. But as the amplifier is not perfect, the

IM products from the interferer might fall directly onto the wanted signal with a level difference of 10 dB and thereby cause issues. Calculating intermodulation products will never give the full story, but it is a great tool to have.

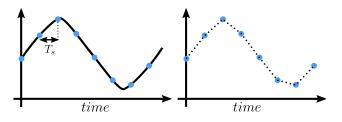

### 2.2 Sampling and Anti-Aliasing

In the world that we all live in, signals are real and continuous (excluding quantum mechanics). This means that you can always find another point between two given points, in fact there is an infinite set of new points between these two adjacent points. A discrete-time signal is the opposite to a continuous one, the signal is defined with a limited set of single points and is undefined between two adjacent points. A discrete-time signal is in a way a lossy compression of a real continuous signal as all information that could be gathered under the limited time frame is approximated into a single point. This process is called sampling and is illustrated in figure 2.2. How many samples one take under one second is called sample rate or sampling frequency,  $f_s$ , and its inverse,  $1/f_s = T_s$ , will be the time between two adjacent samples.

Figure 2.2: A continuous signal and its discrete representation by sampling with a time period of  $T_s$ .

A major issue with all discrete-time systems is the unwanted aliasing effect that occur for input frequencies higher than  $f_s/2$ , commonly known as the Nyquist frequency. Aliasing is also called folding as input frequencies that are a multiple of the sampling rate,  $kf_{in} = f_s, k = 1, 2...$ , are folded back to zero. The folding effect can also be seen as frequency multiplication, or mixing, between the input and sampling frequency as it will down-convert all harmonics of the input signal that are higher than  $f_s/2$ . Although no up-conversion occurs.

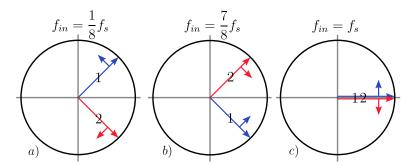

The aliasing effect can be illustrated in the complex plane. Frequency is represented by two rotating vectors, positive and negative frequency. Both vectors starts from (1, 0) and rotate with the same angular velocity, but in opposite directions. Sampling captures a snapshot of the vectors position. A position of (1, 0) represents zero Hz while (0, 1) and (-1, 0) represents  $f_s/4$  and  $f_s/2$ , respectively.

Figure 2.3 shows three different input frequencies, all are sampled with a constant sampling rate of  $f_s$ . In a) the input frequency is  $f_s/8$  which is lower than  $f_s/2$ , the sampled signal will therefore correspond to the real input signal, no aliasing

occurs. In b) the input frequency is increased to  $\frac{7}{8}f_s$ , aliasing will now occur as we have passed  $f_s/2$ , the sampled signal will be seen to have the same frequency as in a) but with a phase shift of 180°. Information is lost as there is no way to confirm that the actual frequency was  $\frac{7}{8}f_s$ . In c) the input frequency is yet again increased to  $f_s$ , which is as in b) higher than  $f_s/2$  and therefore aliasing will occur. The observed frequency from sampling is zero, all information are lost. Not only are information lost in b) and c) but the input frequency are also down-converted below  $f_s/2$  and can therefore interfere with signals of interest.

**Figure 2.3:** Sampling and its aliasing effects within the complex plane. a) is with an input frequency of  $f_s/8$ , b) with  $\frac{7}{8}f_s$  and c) with  $f_s$ . In all cases the sample rate is  $f_s$ .

To remove these unwanted effects, an anti-aliasing filter is required to attenuate unwanted signal above  $f_s/2$  before any sampling occurs. In theory, this filter is a so-called brickwall low-pass filter that removes all frequencies higher than  $f_s/2$ , but in practice it consist of a high-order active low-pass filter, there is also other solutions such as the sinc filter.

### 2.3 Sinc Filter

The sinc filter is an effective way of creating an anti-aliasing filter as it comes for free with charge sampling (section 2.5.2). The ideal impulse response from the sinc filter is a sinc function and its frequency response is a perfect rectangular function, it is a perfect low-pass filter, removing all content above its cut-off frequency.

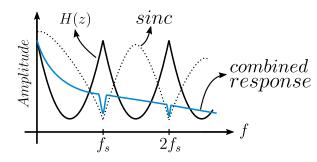

In the real-world however, there is no such thing as a perfect sinc filter. The actual frequency response follows the first-order low-pass filter but with multiple of infinite notches that are located at the inverse of its time window  $T_s$ ,  $k/T_s$ , k = 1, 2..., figure 2.4. If the window time is set to the same time as the sample interval the notches from the sinc filter will cancel the repetitions of a discrete-time frequency response, also, all folding that occurs with frequencies higher than  $f_s/2$  will be attenuate due to the low pass characteristics. The end result is the removal of all repetitive responses but not the removal of the folding effects, unwanted content is still folded back to zero but with a lower amplitude.

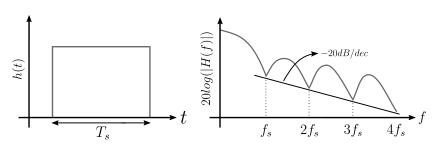

Figure 2.4: Convolution of a time window creates a sinc filter in frequency.

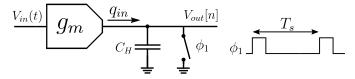

The sinc filter can be implemented in CMOS with a transconductor  $(g_m)$ , a capacitor, and a switch (transmission gate or a single transistor), as shown in figure 2.5. The switch will clear the previous sample every  $T_s$  and thereby convert the continuous-time into a time window.

Figure 2.5: General implementation of the sinc filter.

A more formal name of this implementation is called Windowed Integration Sampler (WIS) [11] and works by integrating the output current, or charge, from a transconductor onto a capacitor under its time window. This creates a discrete voltage sample that corresponds to the integrated current and is stored onto the capacitor with a sinc frequency response as seen in eq. 2.4 (assuming  $V_{in} = 1$ ). The level of attenuation depends on how deep the notches of the sinc filter are, which in turn is entirely decided by the output impedance of its transconductor [12]. The combined response of a generic discrete-time system and the sinc filter is illustrated in figure 2.6

$$V_{out}[n] = \frac{g_m}{C} \int_{nT_s}^{(n+1)T_s} V_{in} dt \to |H(f)| = \frac{V_{out}}{V_{in}} = \frac{g_m T_s}{C} sinc(f_{in}T_s)$$

(2.4)

**Figure 2.6:** Illustration of the combined frequency response of a generic discrete-time system and its sinc filter.

### 2.4 General Information of Discrete-Time Filters

### 2.4.1 Common Definitions

Analog discrete-time filters are built upon discrete charge packages that moves from one capacitor to another, and in all forthcoming filters there are two common capacitors and its three related ratios that are recurrent through the thesis.

$C_H$  is the first capacitor and represents the *history*. The stored charge is the integrated current of the present sample and all previous samples, an analogy is a Infinite Impulse Response (IIR).  $C_H$  is also the capacitor that creates the sinc filter. The second capacitor is  $C_R$  and represents a *rotational* charge between different  $C_H$  capacitors, its analogy is more of a Finite Impulse Response (FIR) as its charge is cleared every cycle. There are normally one or two  $C_H$  for each signal phase but only one  $C_R$ , for one filter circuit. All rotations are controlled by the movement from clock phases  $\phi_1$  to  $\phi_N$ .

Two ratios are named  $\alpha_1$  and  $\alpha_2$ , expressed in eq. 2.5 and 2.6 where  $\alpha_1$  represents the charge movement from  $C_H$  to  $C_R$  while  $\alpha_2$  represents the opposite, a charge movement from  $C_R$  to  $C_H$ . The last ratio is k and represents a capacitive loading factor *seen* by a transconductor, multiplying with its  $g_m$  will give the voltage gain of a filter.

0

$$\alpha_1 = \frac{C_H}{C_H + C_R} \tag{2.5}$$

$$\alpha_2 = \frac{C_R}{C_R + C_H} \tag{2.6}$$

$$k = \frac{1}{C_H + C_R} \tag{2.7}$$

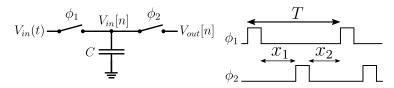

#### 2.4.2 Clock Phases

Any discrete-time filter is always controlled by at least two clock phases, as the example shown in figure 2.7. Given a continuous input signal, the first phase,  $\phi_1$ , will define the exact moment when the signal is converter to a discrete representation. This exact moment happens when the first switch disconnects  $V_{in}(t)$  and  $V_{in}[n]$ . Therefore,  $\phi_1$  must meet high requirements, typically very low jitter. If the system has no decimation of sample rate,  $\phi_1$  will be the only phase that sets the systems performance. In terms of jitter,  $\phi_2$  can be orders of magnitude worse and it won't degrade the performance.

Furthermore, if the time period T is constant between several samples, then any variations of  $x_1$  and  $x_2$  has zero impact. Even if this generic filter is analog by nature the concept is identical to digital filter, an analogy towards digital filter is, it doesn't matter if the computation time of a digital filter varies, as long as it is done before the next sample and that the sampling is coherent. An analog discrete-time filter acts the same way as the digital representation, but the analog world brings its own aspects such as non-zero ohm switches, leakage, and low output impedance.

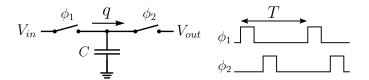

Figure 2.7: A generic discrete-time filter with its two clock phases.

#### 2.4.3 Equivalent Resistance of a Switched Capacitor

Two switches and a capacitor can act as an equivalent resistance, if the switches are controlled in a proper way. Given the schematic in figure 2.8, the charge transfer, q, from  $V_{in}$  to  $V_{out}$  during one period is equal to the voltage difference multiplied by the capacitance, C,  $q = C(V_{out} - V_{in})$ . Dividing the charge by the time period gives the current I, I = q/T. The resistance,  $R_{eq}$ , is then calculated with Ohms law. Replacing time with frequency gives the final form as seen in eq. 2.8.

Figure 2.8: Concept of a switched capacitor.

$$R_{eq} = \frac{V}{I} = \frac{V_{out} - V_{in}}{\frac{q}{T}} = \frac{V_{out} - V_{in}}{\frac{C(V_{out} - V_{in})}{T}} = \frac{T}{C} = \frac{1}{f_s C}$$

(2.8)

### 2.4.4 Gain of a Unit $g_m$ -cell

A  $g_m$ -cell is short for a Transconductance Amplifier (TA), it takes a voltage as its input and outputs a current. The  $g_m$  part comes from its definitions of  $g_m = I_{out}/V_{in}$ .  $V_{out}$  in figure 2.9 is derived directly from ohms law, the load,  $Z_L$ , is the parallel impedance of  $C_H$  and  $R_{eq}$  as described in eq. 2.9.

$$V_{in} - g_m \xrightarrow{I_{out}} V_{out}$$

$$C_H \xrightarrow{I_{out}} R_{eq}$$

**Figure 2.9:** A simple  $g_m$ -cell with its load.

$$V_{out} = I_{out}Z_L , \ I_{out} = g_m V_{in} \to \frac{V_{out}}{V_{in}} = g_m Z_L = g_m (R_{eq} || Z_{C_H})$$

(2.9)

Further expansion with eq. 2.8 and  $Z_{C_H} = 1/(2\pi f_{IF}C_H)$ , gives the final expression as seen in eq. 2.10. Note that C in eq. 2.8 is changed to  $C_R$  to match further equations.

$$\frac{V_{out}}{V_{in}} = \frac{g_m}{C_R f_s + 2\pi C_H f_{IF}} \tag{2.10}$$

### 2.5 Discrete-time Low-pass Filter

#### 2.5.1 Voltage Sampling

The first-order low-pass filter with voltage sampling is attained with two capacitors and two switches. It is controlled by two phases as depicted in figure 2.10.

Figure 2.10: Ideal first-order low-pass filter with voltage sampling.

The first switch acts as a typical sample and hold circuit, the voltage onto  $C_R$  follows  $V_{in}(t)$  continuously given that  $\phi_1$  is asserted. The exact moment  $\phi_1$  changes state, the voltage onto  $C_R$  are no longer continuous, therefore it is discrete and is now expressed as  $V_{in}[n]$ . Next,  $\phi_1$  and  $\phi_2$  transition from high to low and low to high, respectively. Charges from  $C_R$  moves onto  $C_H$ , this gives the term  $\alpha_2 V_{in}[n]$ . As charges of  $C_H$  is never cleared, its previous sample [n-1] also contributes to  $V_{out}[n]$ . However, the movement of charges are now inverted, charges moves from  $C_H$  to  $C_R$  and therefore gives the term  $\alpha_1 V_{out}[n-1]$ . The cycle repeats with a time period of T and as the system has neither gain or attenuation the voltage gain is always unity. The expression of  $V_{out}[n]$  is given by eq. 2.11 and its Z-transform by 2.12.

$$V_{out}[n] = \alpha_2 V_{in}[n] + \alpha_1 V_{out}[n-1]$$

(2.11)

$$H(z) = \frac{V_{out}(z)}{V_{in}(z)} = \frac{\alpha_2}{1 - \alpha_1 z^{-1}}$$

(2.12)

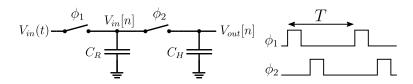

#### 2.5.2 Charge Sampling

The charge sampling variant of the discrete-time low-pass filter is quite similar to the voltage sampling circuit in section 2.5.1, the biggest difference is the sampling method. Instead of converting the voltage at an exact moment in time the sampling works by integrating charge from a  $g_m$ -cell under a time period T. Other than that, it works identical and uses the same building blocks, two capacitors, two switches and two phases. And as we are integrating the charge, we gain another function, the sinc filter, in which one could argue that the charge sampling is superior to the voltage sampling as it comes with a free anti-aliasing filter. The circuit are shown in figure 2.11.

Figure 2.11: Ideal first-order low-pass filter with charge sampling.

When  $\phi_1$  is asserted, charge of the present sample is stored onto the parallel capacitance of  $C_H$  and  $C_R$ , which gives the  $kq_{in}[n]$  term. The second part when  $\phi_1$  closes and  $\phi_2$  opens works identical to the voltage sampling, thereby gives the term  $\alpha_1 V_{out}[n-1]$ . The cycle repeats with a time period of T and the expression of  $V_{out}[n]$  is given by eq. 2.13. With help from eq. 2.14 the Z-transform of eq. 2.13 is given by eq. 2.15. The voltage gain of the system is obtained from eq. 2.15 with z = 1 and gives  $\frac{kg_mT}{1-\alpha_1}$ .

$$V_{out}[n] = kq_{in}[n] + \alpha_1 V_{out}[n-1]$$

(2.13)

$$q_{in}[n] = g_m \int_{nT}^{(n+1)T} V_{in}(t) dt \to V_{in}(t) = 1 \to g_m T$$

(2.14)

$$H(z) = \frac{V_{out}(z)}{q_{in}(z)} = \frac{k}{1 - \alpha_1 z^{-1}} \to \frac{V_{out}(z)}{V_{in}(z)} = \frac{kg_m T}{1 - \alpha_1 z^{-1}}$$

(2.15)

#### 2.5.3 Combined Charge and Voltage Sampling

By combining the charge and voltage circuit from section 2.5.2 and 2.5.1 another order on the low-pass filter is gained without doubling the necessary components, only one more of each are needed. The circuit is shown in figure 2.12.

Figure 2.12: Ideal second-order low-pass filter with combined charge and voltage sampling

When dealing with multiple stages the complexity increases substantially, one way of simplifying is to express each node as it is the present sample,  $V_x[n]$ , and continuing with the Z-transform of each expression individually to be later added together, this works as one of the properties of the Z-transform is linearity. The charge sampling gives  $V_1[n]$  while the voltage sampling gives  $V_{out}[n]$ , as expressed in eq. 2.16, 2.17 and their respective Z-transform by eq. 2.18, 2.19.

$$V_1[n] = kq_1[n] + \alpha_1 V_1[n-1]$$

(2.16)

$$V_{out}[n] = \alpha_2 V_1[n] + \alpha_1 V_{out}[n-1]$$

(2.17)

$$V_1(z) = \frac{kq_{in}(z)}{1 - \alpha_1 z^{-1}} \tag{2.18}$$

$$V_{out}(z) = \frac{\alpha_2 V_1(z)}{1 - \alpha_1 z^{-1}}$$

(2.19)

By combining 2.18 and 2.19, and solving for  $V_{out}/q_{in}$  we obtain the transfer function as given in eq. 2.20, which can be expressed in terms of  $V_{out}/V_{in}$  with 2.14, and with z = 1 the voltage gain is given by eq.  $\frac{k\alpha_2 g_m T}{(1-\alpha_1)^2}$  Theory

$$H(z) = \frac{V_{out}(z)}{q_{in}(z)} = \frac{k\alpha_2}{(1 - \alpha_1 z^{-1})^2} \to \frac{V_{out}(z)}{V_{in}(z)} = \frac{k\alpha_2 g_m T}{(1 - \alpha_1 z^{-1})^2}$$

(2.20)

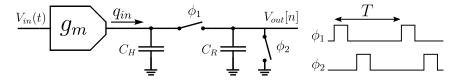

#### 2.5.4 M'th Order

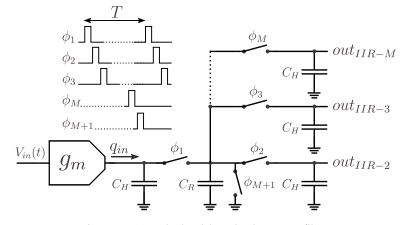

The M'th order low-pass filter consist of one charge sampling stage and M-1 voltage sampling stages, the required resources are one  $g_m$ -cell, one  $C_R$ ,  $M C_H$  and M+1 switches with its corresponding phase, as shown in figure 2.13. It is possible to switch order of the filter as each order has its own output, the only thing one need is to connect all outputs to an analog multiplexer and control which output one wants.

Figure 2.13: Ideal M'th order low-pass filter.

The transfer function is expressed in eq. 2.21 and was derived the same way as in section 2.5.3, the only difference is that each additional stage adds another  $\frac{\alpha_2}{1-\alpha_1 z^{-1}}$ , note that the equation is only valid for M > 1, and with z = 1 gives the voltage gain as seen in eq. 2.22.

$$H(z) = \frac{V_{out}(z)}{q_{in}(z)} = \frac{k\alpha_2^{M-1}}{(1-\alpha_1 z^{-1})^M} \to \frac{V_{out}(z)}{V_{in}(z)} = \frac{kg_m T\alpha_2^{M-1}}{(1-\alpha_1 z^{-1})^M}$$

(2.21)

$$A_V = \frac{kg_m T \alpha_2^{M-1}}{(1-\alpha_1)^M}$$

(2.22)

# 2.6 Complex Band-pass Filter

The complex Band-Pass Filter (BPF), or charge sharing band-pass Filter as many prior papers use, are mainly divided into two groups, the M/M and M/2M. The M/- represents the number of inputs and outputs while -/M and -/2M represents how many clock phases are required. Input and clocks must be distinct with its phase, typically by  $360^{\circ}/M$  or  $360^{\circ}/2M$  depending on which filter order is used. This section starts with the 4/4, continues with M/M and ends with the M/2M. A detailed explanation is given with the 4/4 while the other sections are simplified as they all work in the same way.

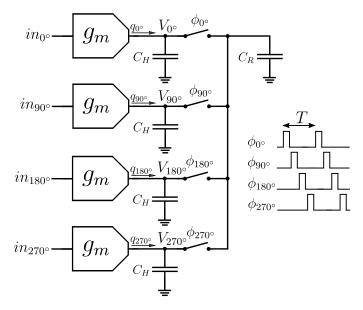

### 2.6.1 Conventional Quadrature 4/4

The conventional quadrature 4/4 band-pass filter, has as its name suggest, 4 inputs/outputs (4/-) and 4 clock phases (-/4). The filter requires an input that are separated into 4 different phases, normally by 90 degrees from each other as  $0^{\circ}$ ,  $90^{\circ}$ ,  $180^{\circ}$ , and  $270^{\circ}$  but the absolute values are irrelevant. The same phase difference is required onto the clocks and that they have the same frequency. Furthermore, four  $g_m$ -cells, four  $C_H$ , four switches, and one  $C_R$  are required. The filter is controlled by these 4 clocks,  $\phi_1, \phi_2, \phi_3, \phi_4$  and creates the distinct charge packages of  $q_1$ ,  $q_2$ ,  $q_3$ , and  $q_4$  that are in turn created by its  $g_m$ -cell. Schematics over the ideal filter can be seen in figure 2.14.

Figure 2.14: Ideal 4/4 complex band-pass filter.

The voltage of  $V_x[n]$  is sampled once  $\phi_x$  transitions from high to low.  $V_x[n]$  is described by its previous value, n-1, and the new incoming charge,  $q_x$ , during

the time T. The previous value is the sum of two previous samples, its own that is scaled by  $\alpha_1$  and from the prior phase that is scaled by  $\alpha_2$ . Both of these samples follow the principle of voltage sampling while the present sample relates to charge sampling and is therefore scaled by k. Each signal path generates its own transfer function as seen in eq. 2.23, 2.24, 2.25, and 2.26.

$$V_{0^{\circ}}[n] = kq_{0^{\circ}}[n] + \alpha_1 V_{0^{\circ}}[n-1] + \alpha_2 V_{270^{\circ}}[n-1]$$

(2.23)

$$V_{90^{\circ}}[n] = kq_{90^{\circ}}[n] + \alpha_1 V_{90^{\circ}}[n-1] + \alpha_2 V_{0^{\circ}}[n-1]$$

(2.24)

$$V_{180^{\circ}}[n] = kq_{180^{\circ}}[n] + \alpha_1 V_{180^{\circ}}[n-1] + \alpha_2 V_{90^{\circ}}[n-1]$$

(2.25)

$$V_{270^{\circ}}[n] = kq_{270^{\circ}}[n] + \alpha_1 V_{270^{\circ}}[n-1] + \alpha_2 V_{180^{\circ}}[n-1]$$

(2.26)

A simplification can be made by using differential signals as half (M/2) the equations are then needed. Let  $V_{d_1}$  be defined as  $V_{0^\circ} - V_{180^\circ}$  and  $V_{d_2}$  as  $V_{90^\circ} - V_{270^\circ}$ , this gives us eq. 2.27 and 2.28.

$$V_{d_1}[n] = kq_{d_1}[n] + \alpha_1 V_{d_1}[n-1] - \alpha_2 V_{d_2}[n-1]$$

(2.27)

$$V_{d_2}[n] = kq_{d_2}[n] + \alpha_1 V_{d_2}[n-1] + \alpha_2 V_{d_2}[n-1]$$

(2.28)

Notice how  $\alpha_2 V_{d_2}$  in eq. 2.27 has changed sign, one product of  $V_{0^\circ} - V_{180^\circ}$  creates an angle subtraction of  $270^\circ - 90^\circ$ , which is the negative definition of  $90^\circ - 270^\circ$ and therefore  $-V_{d_2}$ .

Further simplification can be made by using a complex definition of our signals. Let  $q_c$  be defined as  $q_{d_1} + jq_{d_2}$  and  $V_c$  as  $V_{d_1} + jV_{d_2}$ . Why multiple with j one might ask, if one see  $V_{d_1}$  as a unit vector with Cartesian coordinate it is [0, 1] and  $V_{d_2}$  as [1, 0], the first is pointing to the right while the second one is point up, which are the same as [1, 0j] and [0, 1j] respectively.

With four phases it does not really matter but with higher complexity and more phases it will be a lot easier to express the system with Polar coordinates, or in other words, with complex numbers. With our new definitions we can finally express the relation between the input and output with only one equation as seen in eq. 2.29, and its Z-transform by eq. 2.30. One could express the voltage gain with z = 1 into eq. 2.30 but it is a rather lengthy process, a much simpler solution is to use eq. 2.10.

$$V_c[n] = kq_c[n] + \alpha_1 V_c[n-1] + \alpha_2 V_c[n-1]e^{j\pi/2}$$

(2.29)

$$H_{4/4}(z) = \frac{V_c(z)}{q_c(z)} = \frac{k}{1 - z^{-1}(\alpha_1 + \alpha_2 e^{j\pi/2})} \to$$

$$\to \frac{V_{out}(z)}{V_{in}(z)} = \frac{kg_m T}{1 - z^{-1}(\alpha_1 + \alpha_2 e^{j\pi/2})}$$

(2.30)

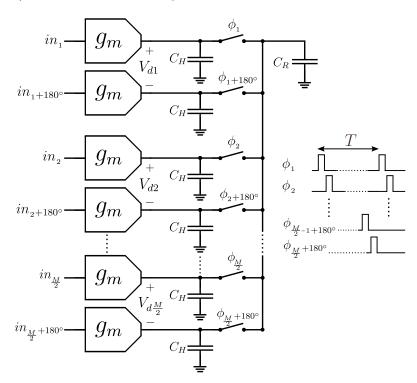

# 2.6.2 General M/M

An M/M BPF has M independent single-ended inputs and outputs, phases,  $g_m$ cells, and history capacitors but only one rotational capacitor. The core concept is identical to section 2.6.1 and therefore no detailed explained is given here, the only difference is the share amount of resource and equations. Schematics over the ideal M/M filter can be seen in figure 2.15.

**Figure 2.15:** Ideal M/M complex band-pass filter.

M/2 differential signals are defined, each separated by  $360^\circ/M.$  Their expression is seen in eq. 2.31.

$$V_{d_{x}} = \begin{cases} V_{d_{1}}[n] = kq_{d_{1}}[n] + \alpha_{1}V_{d_{1}}[n-1] - \alpha_{2}V_{d_{M/2}}[n-1] \\ V_{d_{2}}[n] = kq_{d_{2}}[n] + \alpha_{1}V_{d_{2}}[n-1] + \alpha_{2}V_{d_{1}}[n-1] \\ V_{d_{3}}[n] = kq_{d_{3}}[n] + \alpha_{1}V_{d_{3}}[n-1] + \alpha_{2}V_{d_{2}}[n-1] \\ \vdots & \vdots & \vdots \\ V_{d_{\underline{M}}}[n] = kq_{d_{\underline{M}}}[n] + \alpha_{1}V_{d_{\underline{M}}}[n-1] + \alpha_{2}V_{d_{(\underline{M}-1)}}[n-1] \end{cases}$$

(2.31)

To further simplify and solve for the system transfer function we need to define a complex input and output, these are in turn the voltage sum of all differential voltages,  $V_{d_x}[n]$ , from eq. 2.31 and multiplied by its corresponding phase shift,  $e^{j2\pi(x-1)/M}$ , the same concept is also true for all charge packets. This results in eq. 2.32 and 2.33 which together gives 2.34 and its Z-transform by 2.35.

$$V_c[n] = \sum_{x=1}^{M/2} V_{d_x}[n] e^{j2\pi(x-1)/M}$$

(2.32)

$$q_c[n] = \sum_{x=1}^{M/2} q_{d_x}[n] e^{j2\pi(x-1)/M}$$

(2.33)

$$V_c[n] = q_c[n] + \alpha_1 V_c[n-1] + \alpha_2 V_c[n-1] e^{j2\pi/M}$$

(2.34)

$$H_{M/M}(z) = \frac{V_c(z)}{q_c(z)} = \frac{k}{1 - z^{-1}(\alpha_1 + \alpha_2 e^{j2\pi/M})} \to$$

(2.35)

$$\to \frac{V_{out}(z)}{V_{in}(z)} = \frac{kg_m T}{1 - z^{-1}(\alpha_1 + \alpha_2 e^{j2\pi/M})}$$

As seen in the equation above, higher orders of M do not create more poles and keeps the voltage gain fixed. Only the poles placement is changed, a more details exploration of this are given in section 2.6.4. The Voltage gain is best calculated with 2.10 due to the complexity. For simplicity's sake the transfer function of a 4/4 and 8/8 system are given in eq. 2.36 and 2.37 as they are the most common M/M band-pass filters.

$$H_{4/4}(z) = \frac{k}{1 - z^{-1}(\alpha_1 + \alpha_2 e^{j\pi/2})}$$

(2.36)

$$H_{8/8}(z) = \frac{k}{1 - z^{-1}(\alpha_1 + \alpha_2 e^{j\pi/4})}$$

(2.37)

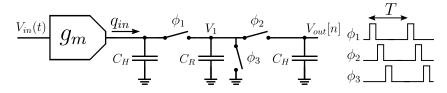

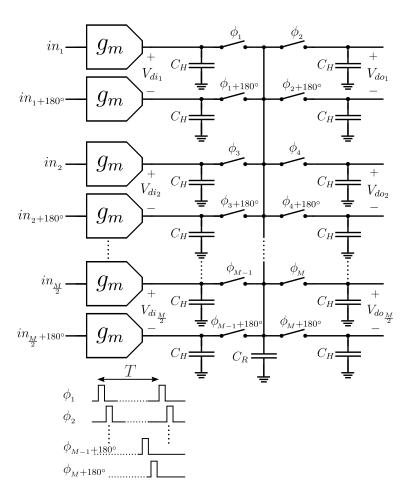

#### 2.6.3 General M/2M

The M/2M band-pass filter is built upon the M/M and uses the same resources with an additional doubling of switches, phases and  $C_H$  capacitors as depicted in figure 2.16. From these extra components an additional low-pass filter is gained, which further helps with filtering as the effective filters Q-factor is increased. The concept of the M/2M filter is more or less a combination of the first order low-pass filter and the 4/4 band-pass filter from section 2.5.1 and 2.6.1 respectively.

Figure 2.16: Ideal M/2M complex band-pass filter.

Let the differential voltage created by two  $g_m$ -cells over its corresponding  $C_H$  capacitor be called  $V_{di_x}$  and its output by  $V_{do_x}$ , x = 1, 2, 3...M/2. The input to output relation follows the same principle as given from eq. 2.23-2.26 and 2.11. By following the same concept, we can express the  $V_{di_x}$  and  $V_{do_x}$  as seen in eq. 2.38 and 2.39.

$$V_{di_{x}} = \begin{cases} V_{di_{1}}[n] = kq_{di_{1}}[n] + \alpha_{1}V_{di_{1}}[n-1] - \alpha_{2}V_{do_{\frac{M}{2}}}[n-1] \\ V_{di_{2}}[n] = kq_{di_{2}}[n] + \alpha_{1}V_{di_{2}}[n-1] + \alpha_{2}V_{do_{1}}[n-1] \\ V_{di_{3}}[n] = kq_{di_{3}}[n] + \alpha_{1}V_{di_{3}}[n-1] + \alpha_{2}V_{do_{2}}[n-1] \\ \vdots & \vdots & \vdots \\ V_{di_{\frac{M}{2}}}[n] = kq_{di_{\frac{M}{2}}}[n] + \alpha_{1}V_{di_{\frac{M}{2}}}[n-1] + \alpha_{2}V_{do_{(\frac{M}{2}-1)}}[n-1] \end{cases}$$

(2.38)

$$V_{do_x} = \begin{cases} V_{do_1}[n] = \alpha_1 V_{do_1}[n-1] + \alpha_2 V_{di_1}[n] \\ V_{do_2}[n] = \alpha_1 V_{do_2}[n-1] + \alpha_2 V_{di_2}[n] \\ V_{do_3}[n] = \alpha_1 V_{do_3}[n-1] + \alpha_2 V_{di_3}[n] \\ \vdots & \vdots & \vdots \\ V_{do_{\frac{M}{2}}}[n] = \alpha_1 V_{do_{\frac{M}{2}}}[n-1] + \alpha_2 V_{di_{\frac{M}{2}}}[n] \end{cases}$$

(2.39)

As with previous M/M filter a transfer to the complex plane is necessary to solve for the system transfer function, each serie of equation above generates a new complex definitions, all follow the same pattern by being the sum of all differential equation which are in turn multiplied with its corresponding phase, in this case it is  $V_{di_x}$ ,  $V_{do_x}$ ,  $q_{d_x}$  and the phase by  $e^{j2\pi(x-1)/M}$  as seen in eq. 2.40, 2.41, 2.42 which all together creates 2.43 and 2.44

$$V_{ci}[n] = \sum_{x=1}^{M/2} V_{di_x}[n] e^{j2\pi(x-1)/M}$$

(2.40)

$$V_{co}[n] = \sum_{x=1}^{M/2} V_{do_x}[n] e^{j2\pi(x-1)/M}$$

(2.41)

$$q_c[n] = \sum_{x=1}^{M/2} q_{d_x}[n] e^{j2\pi(x-1)/M}$$

(2.42)

$$V_{ci}[n] = kq_{ci}[n] + \alpha_1 V_{ci}[n-1] + \alpha_2 V_{co}[n-1]e^{j2\pi/M}$$

(2.43)

$$V_{co}[n] = \alpha_1 V_{co}[n-1] + \alpha_2 V_{ci}[n]$$

(2.44)

The last step is to take the Z-transform of the two equations above, independent of each other and then combining them eases the maths, but it is possible to combine first and then solve for  $V_{co}(z)/q_c(z)$ .