# Capacitance Optimization and Ballistic Modeling of Nanowire Transistors

AZAL ALOTHMANI MASTER'S THESIS DEPARTMENT OF ELECTRICAL AND INFORMATION TECHNOLOGY FACULTY OF ENGINEERING | LTH | LUND UNIVERSITY

# Capacitance Optimization and Ballistic Modeling of Nanowire Transistors

Azal Alothmani azalalot@gmail.com

Department of Electrical and Information Technology Faculty of Engineering, LTH, Lund University SE-221 00 Lund, Sweden

> Supervisors: Erik Lind & Adam Jönsson Examiner: Mats Gustafsson

> > June 15, 2018

© 2018 Printed in Sweden Tryckeriet i E-huset, Lund

### Abstract

Downscaling of Si-based metal-oxide-semiconductor field-effect transistors (MOSFETs) has contributed to increased microchip device density and to improve the functionality of the electronic circuits. The dimensions of state of art MOSFET is down to a few nanometers. It has been demonstrated that smaller MOSFETs are faster and more energy-efficient. However, with continued device scaling the performance of ICs starts to deteriorate making it important to implement new technology solutions. Nanowire transistors have in recent years been introduce to face some of semiconductor challenges, such as short-channel effects and performance degradation. The geometry of the nanowires allows the gate contact to be wrapped all-around the nanowire which offers an excellent electrostatic integrity.

However, the performance of nanowire MOSFETs is restricted due to parasitic capacitances and resistances between the metal contacts and semiconductor nanowires. The presence of parasitic capacitances and resistances in devices introduces time delay, which is the time required for charging and discharging the capacitances. Insulating interlayers with high relative permittivity contribute to higher capacitances, and thereby increased time delay. There are amount of materials with low relative permittivity that are suitable to replace the conventionally used spacer material, SiO<sub>2</sub>. The high  $\kappa$ -value of SiO<sub>2</sub> is believed to contribute to higher parasitic capacitances, and performance degradation.

Integration of Hydrogen silses quioxane (HSQ) as an interlayer dielectric in multilevel interconnects has received much attention in semiconductor fabrication. To investigate the possibility of using HSQ as insulating material in nanowire transistors, the properties and the relative permittivity of this material should be explored. Measurement of HSQ  $\kappa$ -value has not been done before and this value has only been speculated. Therefore, a parallel-plate capacitor structure with a varying HSQ-thickness, obtained by using Electron Beam Lithography (EBL), has been manufactured to study the properties of HSQ. Furthermore, the thickness of HSQ has been estimated and CV - characteristics has been considered to measure the  $\kappa$ -value of this material. Experimental measurements on the manufactured structure showed that HSQ is durable as a spacer material, and it has the capability to be used as interlayer dielectric in nanowire transistors. Additionally, the calculated relative permittivity,  $\kappa$ , of HSQ was approximately  $3.00 \pm 0.40$ .

Furthermore, this thesis is about investigating the performance of ballistic 1-D MOSFETs at high frequencies, explaining the operational principles of these devices, calculating RF figures of merit, and extracting high frequency transistor metrics,  $f_T$  and  $f_{max}$ . The simulation in this thesis is based on parameter optimization to find the optimal parameters that give minimized parasitic capacitances and thereby improved transistor performance. To achieve these purposes, 3D-structures have been modeled using COMSOL Multiphysics. The numerical calculations on the modeled 3D nanowire transistor structures demonstrate a transition frequency  $f_T \approx 480$ GHz and maximum frequency  $f_{max} \approx 1.60$  THz.

## Populärvetenskaplig Sammanfattning

Teknologiutvecklingen inom halvledarindustrin och integrerade krestsar har inom de senaste åren skett i en mycket hög takt, vilket också har medfört en förbättring av transistornas prestanda. Transistorn är grundläggande biståndsdel i elektroniska kretsar med huvudsaklig uppgift att styra strömmar och fungerar på så sätt som ett elektriskt relä. Transistorn består av tre elektroder, som kallas source, drain och gate. Genom att applicera en elektrisk spänning över gate-elektroden, kan resistansen hos kanalen mellan source och drain kontrolleras. På det sättet styrs strömmen genom den elektriska kretsen. Användningsområden för transistorer sträcker sig från förstärkning av elektriska signaler till att bygga logiska kretsar som används för att utföra många, komplexa lösningar.

Nedskalning av transistorer till storleksordning av tiotals nanometer har under de senaste 40 åren bidragit till ökad prestanda av integrerade kretsar. Idag är det möjligt att integrera fler transistorer, upp till miljarder, på ett och samma chip.

Transistorn baserad på halvledarmaterialet kisel, har varit den dominerande inom industrin. Kisel är ett halvledarmaterial som under flera decennier har varit en enastående kandidat till både digitala och analoga applikationer. Kisel är dock ganska ofördelaktig som en elektisk ledare. De fysikaliska begränsningarna hos det materialet har blivit ett hinder inför en fortsatt nedskalning av transistorer och en fortsatt förbättring av transistornas prestanda. Av denna anledning, utforskas det alltjämt konkurrerande tekniker för att överträffa de existerande kiselbaserade kretslösningarna och för att utveckla nya tekniska lösningar.

Forskning och utveckling av transistor baserad på alternativa material och utformningar kan gynna utmaningar vid ytterligare miniatyrisering av transistorer. Ett av alternativen är användande av III-V sammansatta halvledare, främst indiumarsenid InAs eller indiumgalliumarsenid InGaAs. Dessa material har förbättrade egenskaper och kan leda till utveckling av snabba transistor. Detta beror på att elektronerna i dessa material har en hög hastighet i jämförelse med kisel, vilket på sikt bidrar till en transistor med betydligt lägre energiförbrukning. Användning av III-V halvledare har öppnat nya dörrar för att utveckla nya typer av transistorer som är baserade på nanotrådar. Strömflödet genom kanalen kan bättre kontrolleras eftersom dess cylindriska geometri tillåter gate-kontakten, som lätt kan lindras runt tråden, att ha mer precis kontroll över kanalen. Prestandan av den typen av transistor förväntas ligga i terahertz-området, tack vare kombinationen av dessa innovationer. Trots förbättrad tansistorprestanda, står de nya teknikerna inför nya utmaningar. Därför bör nya lösningar utredas för att kunna uppnå ett optimerat resultat.

I det här projektet har fysikaliska och ballistiska simuleringar av nanotrådstransistor utförs med syftet att uppskatta prestandan och studera kapacitansernas inverkan. Detta har genomförts genom att variera dimensionerna av den modellerade 3D transistorstrukturen. Dessutom omfattar projektet tillverkning av en platt kondensator som sedan utvärderas. Detta görs i syfte att undersöka möjligheten att ersätta det traditionella isolerande materialet mellan metal elektroderna med andra material som har lägre dielektrik konstant, som till exempel HSQ. På det viset kan man minska påverkan av parasitiska kapacitanser som annars påverkar transistorprestandan negativt.

### Acknowledgements

"Everybody is a genius. But if you judge a fish by its ability to climb a tree, it will live its whole life believing that it is stupid."

$Albert\ Einstein$

This thesis would not have been possible without the contributions of many people.

Firstly, with all my heart I will thank my family, and specially my mother, for the unconditionally love and endless support. Thank you from the deepest of my heart for being an endless source of inspiration, not giving up on me and always pushing me to achieve my goals and dreams.

I would like to express my gratitude to my supervisors Erik and Adam for their great support and guidance. I would also like to take the opportunity to thank Markus Hellenbrand, together with all members of the nanoelectronics group and lab staff at Lund Nano Lab, who without the work would not be possible.

My sincere gratitude is also dedicated professor Lars-Erik Wernersson for being a great inspiration through my time as a student at Lunds University. vi

# Abbreviations and Symbols

## Abbreviations

| $Al_2O_3$<br>Ar | Aluminum oxide<br>Argon                                      |

|-----------------|--------------------------------------------------------------|

| CMOS<br>DOS     | Complementary metal-oxide-semiconductor<br>Density of states |

| FET             | Field-effect transistor                                      |

| GAA             | Gate-all-around                                              |

| $HfO_2$         | Hafnium dioxide                                              |

| HCl             | Hydrochloric acid                                            |

| HSQ             | Hydrogen Silsesquioxane                                      |

| ILD             | Interlayer dielectric                                        |

| InAs            | Indium arsenide                                              |

| InGaAs          | Indium gallium arsenide                                      |

| ITRS            | International technology roadmap for semiconductors          |

| MOSFET          | Metal-oxide-semiconductor field effect transistor            |

| $\mathbf{N}_2$  | Nitrogen                                                     |

| NW              | Nanowire                                                     |

| $\mathbf{QCL}$  | Quantum capacitance limit                                    |

| $\mathbf{RC}$   | Interconnect delay                                           |

| RF              | Radio frequency                                              |

| Si              | Silicon                                                      |

| ${f SiO}_2$     | Silicon dioxide                                              |

| Ti<br>TMAH | Titanium<br>Tetramethylammonium hydroxide |

|------------|-------------------------------------------|

| UV         | Ultraviolet lithography                   |

| W          | Tungsten                                  |

## Physical constants

| $\varepsilon_0$ | vacuum permittivity  | $8.854^{*}10^{-12} \mathrm{F/m}$ |

|-----------------|----------------------|----------------------------------|

| $k_B$           | Boltzmann's constant | $8.617^{*-5} \ {\rm eV/K}$       |

| q               | elementary charge    | $1.602^{*}10^{-19}$ C            |

## Symbols

| A         | area                          | $\mathrm{m}^2$            |

|-----------|-------------------------------|---------------------------|

| $C_{ox}$  | intrinsic oxide capacitance   | $F/m^2$                   |

| $C_{gd}$  | gate-drain capacitance        | $\mathrm{F}/\mathrm{m}^2$ |

| $C_{gs}$  | gate-source capacitance       | $\mathrm{F}/\mathrm{m}^2$ |

| $C_L$     | load capacitance              | $\mathrm{F}/\mathrm{m}^2$ |

| $C_{gs}$  | quantum capacitance           | $\mathrm{F}/\mathrm{m}^2$ |

| $D_{it}$  | density of interface traps    | $\mathrm{m}^{-3}$         |

| $E_c$     | conduction band energy        | eV                        |

| $E_F$     | Fermi level                   | eV                        |

| $f_t$     | cut-off frequency             | Hz                        |

| $f_{max}$ | maximum oscillation frequency | Hz                        |

| $g_d$     | output conductance            | $\mathbf{S}$              |

| $g_m$     | transconductance              | $\mathbf{S}$              |

| $I_{ds}$  | drain-source current          | А                         |

| $I_{on}$  | on-state current              | А                         |

| $L_g$     | gate length                   | m                         |

| $m^*$     | effective electron mass       | kg                        |

| $N_d$     | donor doping concentration    | $\mathrm{m}^{-3}$         |

| $n_{1D}$  | 1-D carrier density           | ${\rm m}^{-3}$            |

| Q         | quantum charge                | С                         |

| $V_{ds}$  | drain-source voltage          | V                         |

| $V_{gs}$  | gate-source voltage           | V                         |

|           |                               |                           |

| $V_t$           | threshold voltage     | V                                               |

|-----------------|-----------------------|-------------------------------------------------|

| $R_{nm}$        | nanowire resistance   | $\Omega\mathrm{m}$                              |

| $R_d$           | drain resistance      | $\Omega\mathrm{m}$                              |

| $R_g$           | gate resistance       | $\Omega\mathrm{m}$                              |

| $R_c$           | access resistance     | $\Omega\mathrm{m}$                              |

| $R_s$           | source resistance     | $\Omega\mathrm{m}$                              |

| $\varepsilon_r$ | relative permittivity | -                                               |

| $\kappa$        | relative permittivity | -                                               |

| $\mu_e$         | electron mobility     | $\mathrm{cm}^{2}\mathrm{V}^{-1}\mathrm{s}^{-1}$ |

|                 |                       |                                                 |

<u>×</u>\_\_\_\_\_

# Contents

| 1        | Intr | oduction                            | 1         |

|----------|------|-------------------------------------|-----------|

| <b>2</b> | Tra  | nsistor Theory                      | 5         |

|          | 2.1  | Planar MOSFET                       | 5         |

|          | 2.2  | Vertical MOSFET                     | 7         |

|          |      | 2.2.1 Transistor Structure          | 8         |

|          | 2.3  | Dielectric Materials                | 9         |

|          |      | 2.3.1 Hydrogen SilsesQuioxane       | 10        |

|          | 2.4  | RC Interconnects Delay Time         | 11        |

| 3        | Ball | listic 1D Transistors               | 15        |

|          | 3.1  | Theory of Ballistic 1-D MOSFETs     | 15        |

|          |      | Ballistic 1D Current                | 17        |

|          | 3.2  | Quantum Capacitance                 | 18        |

|          | 3.3  | Ballistic Transconductance          | 19        |

| 4        | RF-  | Transistors                         | <b>21</b> |

|          | 4.1  | Simulation details                  | 21        |

|          |      | 4.1.1 Device Structure              | 21        |

|          |      | 4.1.2 Numerical Modeling            | 22        |

|          | 4.2  | Numerical Calculation of RF Metrics | 25        |

|          |      | 4.2.1 Small-Signal Model            | 25        |

|          |      | 4.2.2 Device Capacitances           | 26        |

|          |      | 4.2.3 Device Resistances            | 27        |

|          |      | 4.2.4 Nanowire FET Scaling          | 28        |

|          | 4.3  | Review of RF Metrics                | 29        |

|          |      | 4.3.1 Two-port Parameters           | 29        |

|          |      | 4.3.2 RF Metrics                    | 31        |

| <b>5</b> | Ma   | nufacturing Process                 | 33        |

|          | 5.1  | Background                          | 33        |

|          | 5.2  | Experiment Details                  | 34        |

|   | $5.3 \\ 5.4 \\ 5.5$  | HSQ-thickness $Cf$ - Characteristics $Durability$ of $HSQ$ | <br>36<br>37<br>38 |

|---|----------------------|------------------------------------------------------------|--------------------|

| 6 | $\operatorname{Res}$ | sults and Analysis                                         | 41                 |

|   | 6.1                  | Simulation Result                                          | <br>41             |

|   |                      | 6.1.1 Numerical Modeling                                   | <br>41             |

|   |                      | 6.1.2 Intrinsic and Extrinsic Capacitances                 | 43                 |

|   |                      | 6.1.3 Extrinsic Resistances                                | <br>44             |

|   |                      | 6.1.4 Simulation Characteristics                           | <br>45             |

|   | 6.2                  | Experiment Result                                          | <br>46             |

|   |                      | 6.2.1 Measurement of HSQ-thickness                         | <br>47             |

|   |                      | 6.2.2 $Cf$ - Measurement                                   | <br>49             |

|   |                      | 6.2.3 Measurement of $\kappa$ -value                       | <br>49             |

|   |                      | 6.2.4 Measurement of HSQ Durability                        | <br>52             |

| 7 | Cor                  | nclusion and Outlook                                       | 55                 |

# List of Figures

| 2.1 | A schematic overview of a planar <i>n</i> -type MOSFET, with highly doped source and drain regions.                                                                                                                                                                                                                                                                                             | 5  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | MOSFET band simulation. (a) Off-state, the thermionic<br>emission of electrons is blocked by the potential barrier, no<br>conducting channel is created as $V_{gs} < V_t$ . (b) On-state,<br>MOSFET operates above threshold voltage which results in<br>electrons flow across the channel                                                                                                      | 6  |

| 2.3 | A cross-sectional layout of a nanowire transistor, with the gate electrode warped around the wire. A high- $\kappa$ oxide material covers the entire nanowires, shown here in orange. Source and drain contacts are arranged at the bottom and the top of the nanowire, respectively. $L_g$ corresponds to the gate length. The structure is embedded in an insulating material, shown in blue. | 8  |

| 2.4 | The two common structures of HSQ. (a) The monomer or cage structure for an eight-corner oligomer (b) Cross-linked or network form, with some intermediate species involved. The picture is taken from [59]                                                                                                                                                                                      | 10 |

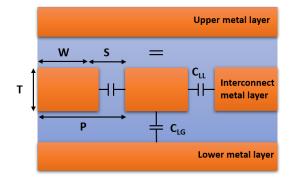

| 2.5 | A schematic view of an interconnect element, capacitance,<br>embedded in a dielectric material (in blue). This schematic<br>overview includes three lines of length $T$ that run in paral-<br>lel with each other. The capacitance $C_{LL}$ couples two lines<br>to each other.Capacitance $C_{LG}$ represents the line-to-ground<br>capacitance                                                | 12 |

| 3.1 | Conduction band diagram of a MOSFET. The transistor is<br>modeled as a structure consisting of three capacitors with a<br>channel charge of Q                                                                                                                                                                                                                                                   | 16 |

| 4.1 | A schematic side view illustration of the modeled nanowire<br>FET structure including the extrinsic capacitances $(C_{gp}$ and<br>$C_{gw})$ , intrinsic gate capacitance, $C_{gg,i}$ , contact resistance, $R_c$ ,<br>and the nanowire resistance, $R_{nw}$ . The entire structure is<br>embedded in low- $\kappa$ material, where $L_{HSQ}$ is the distance be-<br>tween two metal contacts. (b) A Top view of a 2D device<br>structure, illustrating the electrode configuration, as well as<br>the triangular arrangement of the nanowire array | 22 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.2 | The transistor unit cell used during the simulation, with the details of wire geometry are included. $r_{nw}$ is wire radius, $t_{ox}$ is the nanowire thickness, and $w_s$ is the distance between two wires. Periodic boundary condition at the unit cell boundaries in <i>y</i> -direction is considered.                                                                                                                                                                                                                                       | 23 |

| 4.3 | A schematic side view of two additional models of the nanowire FET. (a) The drain contact thickness is varied in order to investigate how the overlap capacitance changes as the distance $L_{HSQ}$ is varying between 30 to 130 nm. (b) The high- $\kappa$ oxide film is only covering the gated segment of the nanowire.                                                                                                                                                                                                                         | 24 |

| 4.4 | A small signal hybrid- $\pi$ circuit model with the passive elements of a three-terminal FET. Intrinsic and extrinsic capacitances and resistances are included.                                                                                                                                                                                                                                                                                                                                                                                   | 25 |

| 4.5 | A schematic view of a 3D nanowire FET structure with re-<br>sistances included. The length and width of the gate contact<br>is equal. A similar structure has been modeled in COMSOL<br>to determine the cheet gate maintained                                                                                                                                                                                                                                                                                                                     | 27 |

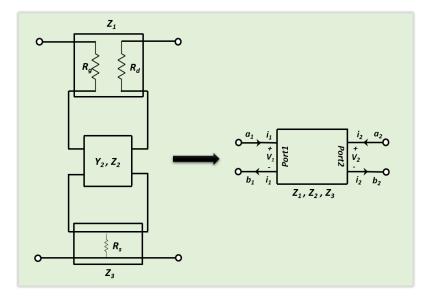

| 4.6 | to determine the sheet gate resistance. $\dots \dots \dots \dots$<br>Schematic overview of the two-port $Y$ - and $Z$ - parameters,<br>which corresponds to the small-signal model illustrated in<br>Fig.4.4. A series connection of three two-port networks is<br>shown. The figure also includes an additional two-port net-<br>work, to the right, to represent the sum of the Z-parameters.<br>The incoming and reflected power waves are given by a and<br>b, and the associated currents and voltages are depicted                           | 30 |

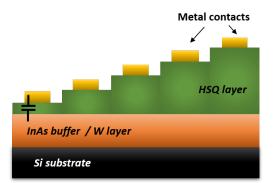

| 5.1 | A schematic layout of the desired structure with varying thickness of HSQ. The thickness is controlled by the electron exposure dose in EBL. The metal contacts consist of a layer of Ti and Au, deposited by metal evaporation.                                                                                                                                                                                                                                                                                                                   | 34 |

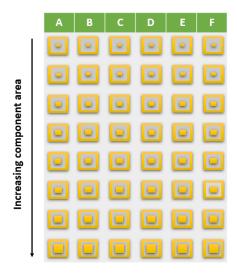

| 5.2 | A schematic overview of the lithography hard mask used dur-<br>ing this thesis. The mask is necessary to defined the pattern<br>of the metal contacts. The area of the components is varied                                                                                                                                                                                                                                                                                                                                                        |    |

|     | along the $y$ -axis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 35 |

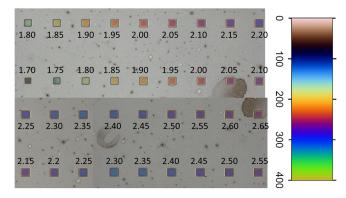

| 5.3 | Reference sample with components exposed with different<br>energy doses. The exposure dose varies from 1.80 to 2.55,<br>with an exposure step of 0.05. The colorbar indicates the<br>thickness of the deposited layer.                                                                                                                                                                                                                                  | 37 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

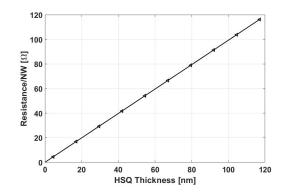

| 5.4 | The figure shows a capacitance parallel coupled to a resistance $R_L$ associated with current leakage. The sum of these elements is in series with device resistance, $R$ .                                                                                                                                                                                                                                                                             | 38 |

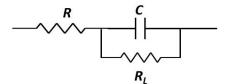

| 6.1 | (a) The numerically calculated parasitic capacitances as a function of the dielectric constant of the embedded material. Wire spacing is 15 nm. The blue curve shows the correlation when high- $\kappa$ is surrounding the entire nanowire, while the red curve shows the correlation where only the gate electrode surrounded segments of the nanowire are coated. (b) The correlation between the capacitances as a function of spacer distances $I$ | 42 |

| 6.2 | distance $L_{HSQ}$                                                                                                                                                                                                                                                                                                                                                                                                                                      | 42 |

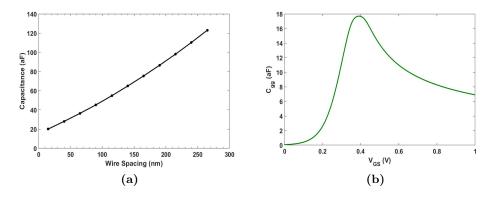

| 6.3 | Nanowire resistance as a function of varied gate-drain dis-<br>tance for a nanowire with a radius of 5 nm. The resistance<br>is normalized with the number of wires in the array                                                                                                                                                                                                                                                                        | 44 |

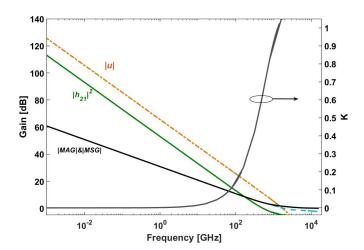

| 6.4 | RF metrics, including the current and power gain in dB, as<br>a function of frequency for the modeled nanowire FET, with<br>$L_g$ of 22 nm. The simulation and the numerical calculation<br>were performed using software Maple.                                                                                                                                                                                                                        | 45 |

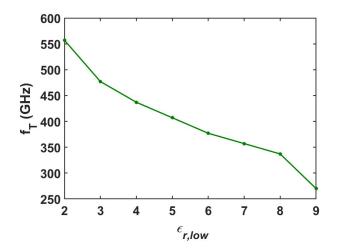

| 6.5 | The calculated $f_T$ as a function of the dielectric constant,<br>$\varepsilon_{r,low}$ , varied between 2.00 and 9.00.                                                                                                                                                                                                                                                                                                                                 | 46 |

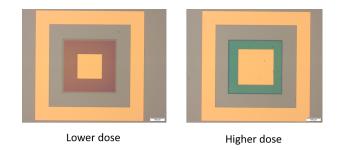

| 6.6 | A microscope image of two of the finished devices. The square pattern, shown here in pink and green, was defined by EBL after HSQ deposition. The metal contacts were defined using UV-photolithography. (a) A component with lower exposure dose and smaller area (b) Another component with a higher exposure dose and larger area.                                                                                                                   | 46 |

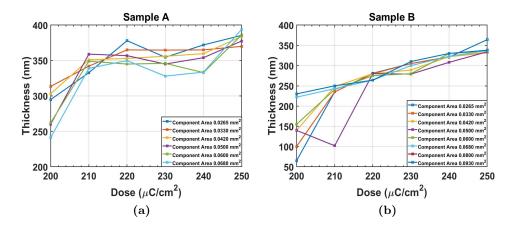

| 6.7 | An overview of the thickness measurement for the designed<br>samples $A$ and $B$ . (a) and (b) show the correlation between<br>the measured HSQ-thickness and the exposure dose for sam-<br>ple $A$ and sample $B$ , respectively                                                                                                                                                                                                                       | 47 |

| 6.8 | The extracted standard derivation for both sample $A$ and $B$ , to determine the distribution in the measurement $\ldots$                                                                                                                                                                                                                                                                                                                               | 48 |

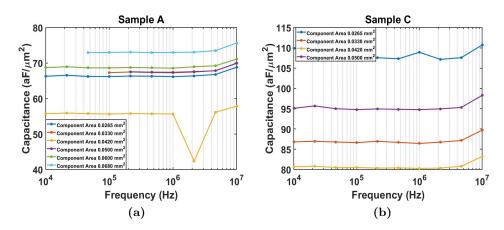

| 6.9  | Cf characteristics at frequency ranged from 10 kHz to 10        |    |

|------|-----------------------------------------------------------------|----|

|      | MHz. (a) The measurement result for sample $A$ (b) The          |    |

|      | measurement result obtained for sample $C$                      | 49 |

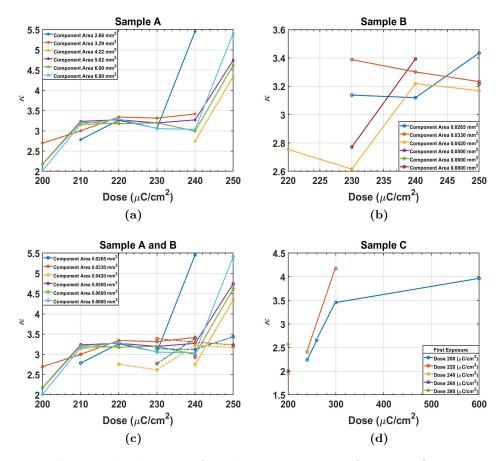

| 6.10 | Overview of $\kappa$ -value measurement at frequency of 70 kHz. |    |

|      | (a)-(b) Show the correlation between the calculated dielec-     |    |

|      | tric constant of HSQ for the all components in samples $A$      |    |

|      | and $B$ . (c) The results for both sample $A$ and $B$ , repre-  |    |

|      | sented by solid lines and dotted lines respectively. (d) The    |    |

|      | measurement result for sample $C$ , where the exposure dose     |    |

|      | during the second exposure varied downwards as illustrated      |    |

|      | in Fig.5.2                                                      | 50 |

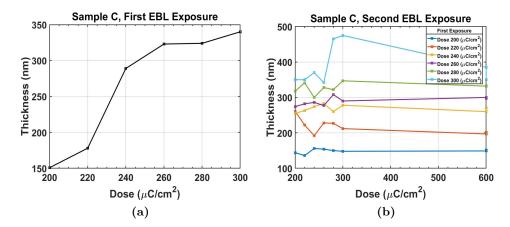

| 6.11 | An overview of the thickness measurement for sample $C$ , out-  |    |

|      | lining the correlation of capacitances and exposure dose, after |    |

|      | first (a) and second (b) EBL exposure                           | 52 |

## CHAPTER 1

## Introduction

Moore's law states that the number of transistors in a dense integrated circuit (IC) will roughly be doubled every two years via geometrical downscaling [1]. Downscaling of transistors has been the most popular approach since it allows for increasing the packing density of metal-oxide-semiconductor (MOS) transistors. Nonetheless, continued device scaling contributes to an increase in dissipated power, limiting the performance of the integrated circuits [1]. Scaling of silicon transistors has reached its limits. Therefore, it is important to turn attention to other materials and technologies to address these problems, and to achieve enhanced circuit performance [2].

Over the past few decades, improved performance of the planar MOS-FET transistors has mainly been achieved by reducing the size of transistors to increase the packaging density. This has been achieved by implementing more transistors, up to milliard, onto a small chip. Continued downscaling of transistors gives rise to some unwanted issues which for example can be related to short channel effects (SCEs) and signal delay [1].

III-V based field-effect transistors are among the promising candidates to enhance transistor performance, and to extend the International Technology Roadmap for Semiconductors (ITRS) [3]. InAs and InGaAs have been among the most interesting semiconductor materials in research, due to the enhanced electron transport properties; high electron velocity and injection velocity [5, 6]. By combining silicon innovations with other novel innovations such as nanotechnology and integrating them onto the silicon platform, downscaling of transistors is expected to continue and with an improved performance. In the last decade, good progress has been made in exploring nanowire-based transistors. The cylindrical gate geometry of nanowires results in an improved electrostatic control and decreased current leakage [4].

Device scaling and increased device packing density require a larger number of interconnects, to connect the devices together in the integrated circuit. This results in an increase in wiring density. The main disadvantage of having a large interconnect wiring density is increased signal delay, resistance-capacitance time delay, RC, and power dissipation [57]. Although feature size downscaling provides an improved device speed, the interconnect delay can constitute a major fraction of the total delay. This will result in devices with limited performance [7, 8].

Fabrication process of the multilevel interconnections includes spin coating of thin oxide films. The conventionally used insulating material has been based on silicon-based polymer solutions, such as SiO<sub>2</sub> [36]. An improved microprocessor performance can be achieved by for example reducing the circuit signal delay. This is achieved by replacing the traditionally used insulator films with materials of a lower relative permittivity (low- $\kappa$  materials). One of the current leading low- $\kappa$  materials is hydrogen silsesquioxane (HSQ). Due to the excellent planarization properties and gap-filling capability of this material, it has been extensively used in semiconductor fabrication [9].

The purpose of this thesis is to investigate the properties of HSQ and to estimate the  $\kappa$ -value of this material. The expected value of HSQ is 3.00-9.00. Furthermore, the thesis intends to study the performance of nanowire transistors by numerical calculation and modeling of 3D structures. The insulating material between the metal contacts of these vertical transistors is assumed to have  $\kappa$ -value between 2.00 and 3.00, for the best optimized structure. First-principles calculations constitute a valuable tool to achieve a greater understanding of the behavior of nanowire transistors without requiring empirical data. An exact measurement of HSQ  $\kappa$ -value has not been done before, and there is a relatively little measurement data available. To study the possibility of replacing the conventionally used insulating material in nanowire transistors with HSQ, the simulation performed in this thesis is particularly interesting. Performance improvement will be based on parameter and material optimization.

The remainder of this thesis is structured as follows. In Chapter 2 -Transistor Theory, two types of transistors are introduced and some important operational principles are explained. In Chapter 3 - Ballistic 1-D Transistors, analytical theory behind the performance of 1-D MOSFETs is considered. In Chapter 4 - RF-Transistors, numerical calculation of RF metrics of nanowire transistors is performed. Moreover, issues associated with these devices are explained, and how this thesis intends to solve them based on parameter optimization is discussed. In Chapter 5 - Manufacturing Process, properties of HSQ are investigated and the  $\kappa$ -value of this material is calculated based on thickness-measurement and CV - characteristics. In Chapter 6 - Result and Analysis, the results obtained from the simulation part and from the experiment part are presented and discussed. In Chapter 7 - Conclusions and outlook, a summary of the thesis is given together with suggested future improvements.

## CHAPTER 2

### **Transistor Theory**

This chapter introduces the theory of two types of transistors and explains some important concepts associated with these devices.

### 2.1 Planar MOSFET

Metal oxide semiconductor field-effect transistor is the most common type of transistor. It can be used as a switch and also to amplify signals in electronic devices. Being the most common transistor, MOSFET has been used in both analog and digital circuits. In the last decades, MOSFET has developed quickly and nowadays it is the most important device for advanced integrated circuits. This is due to the unique features of this transistor, mainly low-power consumption and high manufacturing yield [10].

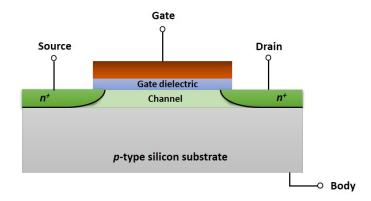

**Figure 2.1:** A schematic overview of a planar *n*-type MOSFET, with highly doped source and drain regions.

Traditionally, MOSFET is composed of a MOS capacitor and two pn -junctions placed adjacent to the MOS capacitor, as illustrated in Fig.2.1.

This transistor comprises four different terminals, source (S), gate (G), drain (D) and body (B). The active region of MOSFET is called channel, along which the charge carries; electrons or holes, flow from the source to the drain. MOSFET works by electronically changing width of the channel, which is controlled by the gate terminal. An extremely thin insulating layer of gate oxide separates the gate contact from the channel. Besides, this layer provides a good insulation by preventing current leakage through the channel [11].

The operation regimes; namely accumulation, depletion and inversion, describe the state of the charge carriers in the channel under different bias conditions. During accumulation, the majority carrier charges, electrons in *n*-type transistors and holes in *p*-type transistors, are induced at the interface between the semiconductor and the oxide. In the depletion region, the majority carrier charges are *depleted* or greatly reduced. By applying a gate bias above a certain threshold voltage  $V_T$ , new minority charge carries start to generate, creating an inversion charge layer at the semiconductoroxide interface. When the number of minority carriers at the surface is greater than the majority carriers, inversion mode is obtained [11].

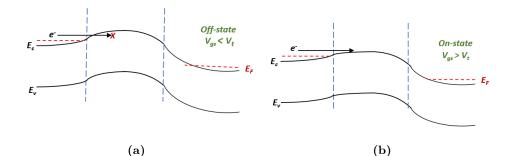

The current through the channel,  $I_{DS}$ , is controlled by source and drain terminals situated at the two ends of the channel. The amount of charges in the channel depends on the height of the energy barrier between the channel and source/drain contact. For *n*-type transistors, the current is small or approximately zero if the applied gate voltage is below the threshold voltage, as shown in Fig.2.2 (a). While having a gate voltage above the threshold voltage makes it possible for the electrons to pass from the source to the drain through the channel, as illustrated in Fig.2.2 (b) [12].

**Figure 2.2:** MOSFET band simulation. (a) Off-state, the thermionic emission of electrons is blocked by the potential barrier, no conducting channel is created as  $V_{gs} < V_t$ . (b) On-state, MOSFET operates above threshold voltage which results in electrons flow across the channel.

MOSFETs offer low leakage current, mainly due to the insulating gate oxide film at the MOS interface [43]. Having a low off-state leakage is one of the most efficient approach to maintain higher energy-efficiency in digital circuit. The oxide insulator plays an important role in controlling the performance of MOSFETs by blocking the flow of the current through the gate contact. The gate oxide capacitance per unit area  $[F/m^2]$  is given by

$$C_{ox} = \frac{\varepsilon_0 \varepsilon_r}{d} \tag{2.1}$$

where  $\varepsilon_0$  is the vacuum permittivity,  $\varepsilon_r$  relative permittivity of the gate oxide and d is dielectric insulator thickness. According to this expression, the gate capacitance is increased as the thickness of the gate dielectric film is reduced. Having a very thin dielectric film might result in some issues. Thin films give rise to increased gate-leakage current, which is related to quantum mechanical tunneling through thin layers [13]. Therefore, improved transistor performance can be achieved by, for example, replacing SiO<sub>2</sub> with high- $\kappa$  oxides such as HfO<sub>2</sub> or Al<sub>2</sub>O<sub>3</sub>. The main advantage of applying these materials is the good ability to preserve the electrostatics coupling to the gate. In addition, gate leakage and tunneling effects are circumvented by keeping the oxide film thickness constant or relativity thick (~ nm). Doing so, a capacitance equal to that for devices with thiner gate oxide is obtained [14].

### 2.2 Vertical MOSFET

Nanometer-scale devices, that are based on quantum or single-electron, are becoming the most promising devices for future electronics generation [15]. The performance advantages of vertical MOSFETs in comparison to their planar contender is making them a viable option to extend the International Technology Roadmap for Semiconductors.

Transistor downscaling has forced the researchers to find new technology solutions to change the gate structure from planar configuration to a more complex 3D structure. This technology makes it possible to avoid undesirable problems inherent in minimization, such as short channel effects and high off-state leakage [16].

The cylindrical geometry of nanowire offers an excellent electrostatics control over the channel, as for example in gate-all-around configuration. The channel is extended in the vertical dimension and the gate electrode is wrapped all-around the nanowire. This contributes to an increased electrostatics, and hence an improved performance. Furthermore, this technology allows for further scaling of the gate length,  $L_g$ , due to the excellent electrostatics of this configuration. Moreover, the vertical geometry offers a unique possibility for more easily relaxation between different crystal planes (lattice constant), resulting in a greater opportunity to create compounds of different materials, so called heterojunctions [56]. Introduction of high mobility III-V channel materials in a transistor structure is making it possible to achieve an enhanced device performance and reduced power dissipation [18]. Besides, the vertical geometry allows for small footprint, decoupled from the gate-length [19].

#### 2.2.1 Transistor Structure

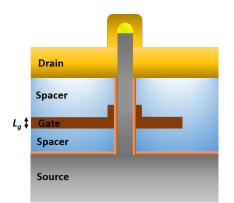

A cross-sectional layout of a vertical nanowire MOSFET structure is illustrated in Fig.2.3. The structure of the vertical nanowire FETs is typically constructed as an array of nanowires arranged perpendicularly to the substrate. The number of nanowires per array is ranged from a single nanowire up to a few hundred, depending on the desired transistor performance. A high- $\kappa$  oxide is implemented on the III-V nanowire to increase the electrostatic coupling to the gate [20].

**Figure 2.3:** A cross-sectional layout of a nanowire transistor, with the gate electrode warped around the wire. A high- $\kappa$  oxide material covers the entire nanowires, shown here in orange. Source and drain contacts are arranged at the bottom and the top of the nanowire, respectively.  $L_g$  corresponds to the gate length. The structure is embedded in an insulating material, shown in blue.

The width of the gate in gate-all-around configuration is defined as the circumference of a single nanowire. To improve the drive current, the number of nanowire per array can be changed, and therefore there is no need of scaling the wire diameter to increase gate width.

The metal contacts in the gate-all-around architecture - gate, source and drain - are vertically stacked on top of each other. The contacts are separated by a spacer insulator material. Ideally, the spacer material should have a low relative perimittivity in order to prevent electronic cross-talk and large parasitic capacitances. Furthermore, the spacer material should be mechanically and thermally stable to withstand further processing, and to increase the ability of controlling the thickness of the deposited film.

### 2.3 Dielectric Materials

Dielectrics or electrically insulated materials are defined as non-conductors of electricity or as materials with high resistance. This is associated with the large band gap offered by these materials, for example, 1.12 eV for Si compared to 8-9 eV for SiO<sub>2</sub> [21]. Studying the dielectric properties of various materials used in semiconductor fabrication is needed to achieve a greater understanding of the desired circuit performance.

Relative permittivity,  $\varepsilon$  or  $\kappa$ , is an important property used to measure the ability of the material to be polarized in an external electric field. The capacitance, which is the ability of the material to hold charge, depends on the permittivity of the material, as expressed in equation (2.1). In some materials, such as polymers, the permittivity is defined as a function of frequency,  $\varepsilon(\omega)$  [58].

There are two types of dielectrics, categorized based on material permittivity. Dielectrics with low permittivity, low- $\kappa$ , are defined as materials with low ability to polarize. Low- $\kappa$  materials are good insulators and provide an excellent insulation between conductors. Therefore, these materials are used in multilevel ICs when coupling between dense metal layers is suppressed [7]. For this reason, these materials can be used as interlayer dielectrics (ILDs) between two metal interconnections, source-gate or gate-drain in vertical FETs. The high non-conduction properties of these materials have made them prominent in preventing the passage of electric current through the insulating layer [22].

The second type of dielectrics is high- $\kappa$  materials, which have a high permittivity and good ability to polarize and hold charge. For further improvement of transistors, the thickness of SiO<sub>2</sub> should be small which contributes to severe leakage problems. To tackle these challenges, SiO<sub>2</sub> can be replaced with high- $\kappa$  materials. The high  $\kappa$ -value of these materials allows for use of a thicker gate oxide, while obtaining a capacitance equal to that of devices with thinner insulating material, as states in equation (2.1).

One example of spacer materials that has been used as interlayer dielectric is organic spacer material. However, using organic materials has difficulties regarding thickness scaling as well as thermal stability. Organic photoresists, such as S1813 or BCB, or inorganic films, such as SiO<sub>2</sub>, Si<sub>2</sub>N<sub>4</sub> or HSQ are typically used as spacer materials. This is due to the improved mechanical stability of these materials, and their ability to withstand higher temperatures. Air spacer can be considered as the best spacer due to its low relative permittivity, close to 1. Although, using air as spacer material can result in mechanically unstable structure.

Silicon dioxide, SiO<sub>2</sub>, has been the most common material to be used as insulating material. Nonetheless, one of the major problems of using SiO<sub>2</sub> is the high  $\kappa$ -value of this material. According to equation (2.1), high  $\kappa$ results in a high parasitic capacitance. Therefore, it is important to find other insulating materials with a lower  $\kappa$ -value. Hydrogen Silsesquioxance is a low- $\kappa$  material that has been utilized for planarization in integrated circuits. The good properties of this material, make it a good candidate to be used as a spacer material between the metal contacts in vertical nanowire transistors.

Replacing the SiO<sub>2</sub> with materials of a different  $\kappa$ -value is a complicated technology. The properties of the material should be comparable to those of SiO<sub>2</sub>. Stability under thermal conditions, low thermal expansion and diffusion coefficients are examples of some material requirements that should be considered [7].

#### 2.3.1 Hydrogen SilsesQuioxane

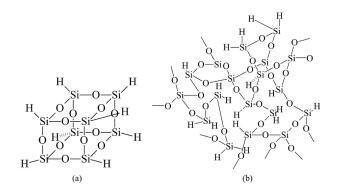

Hydrogen silsesquioxane ( $H_8Si_8O_{12}$ ) is indicated as polyhedral oligomeric silsesquioxane, and is commercially available in solution as FOX, Flow-able Oxide. HSQ ranges as one of the simplest member of the family of spherosiloxanes oligomers. There is a ratio between the two structures of HSQ, so called cage and cross-linked structure [23], illustrated in Fig.2.4, where the cage structure is dominated.

Figure 2.4: The two common structures of HSQ. (a) The monomer or cage structure for an eight-corner oligomer (b) Cross-linked or network form, with some intermediate species involved. The picture is taken from [59].

The non-networked or caged HSQ structure consists of bonding arrangement with Si=H groups. Si atoms sit at the cubic structure corners, forming bridges between three oxygen atoms. Combination of structures with 8 corner oligomer and others with up to 16 corners has been synthesized. The ratio between the two states or structures of HSQ is not constant and changes depending on different fabrication processes [24, 25].

Upon electron-beam irradiation and after treatment of HSQ by heating, silicon hydrogen (Si=H) bonds, which are weaker than SiO bonds, break and additional bonds between the monomer cages are formed. This results in converting the cage structure into a network structure. The physical properties of the network structure are similar to those of SiO<sub>2</sub>. The crosslinking, required for negative tone pattering, is generated consequently. Due to the presence of absorbed moisture in the film, Si=H bonds convert into silanol (Si-OH) groups that subsequently form Si-O-Si bridges at the corner, as shown in 2.4 (b) [26]. The unstable silanol groups condense easily, leading to structure breakage and converting the caged molecule into a linear network [27].

HSQ is a low- $\kappa$  material with low viscosity, providing an excellent gapfilling capability and planarization properties [28]. Furthermore, HSQ is durable and can withstand high processing temperatures. For these reasons, integration of HSQ as an interlayer dielectric in multilevel interconnects has received much attention in semiconductor fabrication [29]. After spincoating of HSQ on the substrate and thermal heating, it transforms into silicon dioxide, as previously mentioned. The curing temperature is a crucial step through the development procedure of HSQ, since it determines the final HSQ-thickness. Furthermore, it has been demonstrated that the final thickness of HSQ can also be obtained by electron exposure dose in electronbeam lithography (EBL) [30].

### 2.4 RC Interconnects Delay Time

Over the past few decades, performance improvement of microelectronic integrated circuits (ICs) has been achieved by reducing the size of device features, from 1  $\mu$ m to a few nanometers. This has resulted in making the ICs faster and with an operational frequency in GHz-range. With continued downscaling of integrated circuits, the performance of these circuit is starting to deteriorate. Performance degradation is mainly due to the increased signal delay originates from the dense interconnect wiring between transistors [31].

The switching speed of MOSFETs is expected to increase as the device dimensions shrink. This results in decreasing the transit time of the carrier across the channel. The intrinsic gate delay is not the only contributory factor in controlling the effective speed of the device, but also the signal propagation through the metal interconnects.

**Figure 2.5:** A schematic view of an interconnect element, capacitance, embedded in a dielectric material (in blue). This schematic overview includes three lines of length T that run in parallel with each other. The capacitance  $C_{LL}$  couples two lines to each other.Capacitance  $C_{LG}$  represents the line-to-ground capacitance.

A model of an interconnect circuit is illustrated in Fig.2.5. W represents the line width, T is the line or wire thickness, S is the spacing between two lines or so called interconnect length, and P represents the line pitch.  $C_{LL}$ and  $C_{LG}$  refer to the contribution of the capacitances from line-to-line and from line-to-ground, respectively. The former mentioned affects both the wiring delay and crosstalk noise, while the second one exclusively affects wiring delay [54].

Resistance-capacitance time delay, RC, is an important figure of merit to characterize the interconnection delay. This time delay can be represented as a series of wires (resistances) and insulating layers between the wires (capacitances). Device downscaling is realized by shrinking the size of transistors to bring the transistors in the device closer together. This can consequently contribute to an increase in the RC interconnect delay time. RC is expressed by equation (2.2) [33].

$$RC = 2\rho\kappa\varepsilon_0(\frac{4L^2}{P^2} + \frac{L^2}{T^2})$$

(2.2)

C is the total interconnect capacitance which is given as  $C = C_{LG} + 2C_{LL}$ , while  $\rho$  represents the metal resistivity and  $\kappa$  is the relative permittivity. According to this equation, the time delay increases quadratically with decreased feature size.

The ongoing development in device processing requires shrinking of device dimensions, thus the usage of multiple metal interconnections becomes more common in manufacturing semiconductor devices. However, this design approach limits the performance of high-speed logic chips. That is due to increased time delay originated from the dense interconnects [34].

The signal through the metal interconnects has the ability to limit the improvement of device performance. This effect becomes more prominent as the dimensions shrink to a few nanometers. Reduced RC delay time can be obtained by replacing the current interlayer dielectric film, silicon dioxide, with low- $\kappa$  materials. Hydrogen silsesquioxane is among the most promising candidates of porous materials to be used as dielectric interlayer at 14 nm technology.

## CHAPTER 3

### **Ballistic 1D Transistors**

Miniaturization of transistors enabled a success in fabricating devices and circuits with high operation frequency. As the demand on high frequency electronics increased, and as the silicon transistor scaling is now reaching its limits, the attention is turning to improve the performance of non-Si electronic materials and non-planar structures [47].

A great progress in studying carbon nanotubes (CNT), semiconductor nanowires and III-V materials has been obtained [48]. III-V materials can be used as channel in for example nanowire transistors, replacing the traditionally used material, silicon. The high electron mobility and injection velocity of these materials together with the improved electrostatics of nanowire-based transistors allow for further gate scaling and better transistor performance [31, 35].

Nanowire transistors can be integrated into CMOS logic. The highperformance and low-power of such logic transistor applications should frequently be benchmarked against the existing Si logic transistor [36].

A theory to characterize ballistic 1-D MOSFETs has been developed by M. Lundstrom and others [37]. The objective of this chapter is to understand the analytical theory behind ballistic 1-D MOSFETs.

### 3.1 Theory of Ballistic 1-D MOSFETs

Ballistic MOSFET can be illustrated as two thermal equilibrium electron reservoirs. The first reservoir is due to source-injection, while the second one is due to drain-injection under low drain bias [36]. These electron reservoirs are separated by an energy barrier whose height is modulated by the gate voltage,  $V_{qs}$  [38].

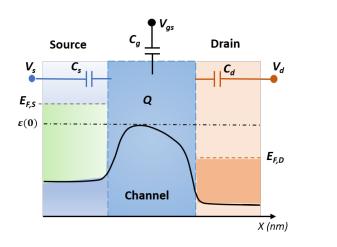

**Figure 3.1:** Conduction band diagram of a MOSFET. The transistor is modeled as a structure consisting of three capacitors with a channel charge of Q.

As it is depicted in Fig.3.1, the Fermi level at the source side is defined as  $E_{F,S}$  and at the drain side as  $E_{F,D} = E_{F,S} - qV_{DS}$ . The height of the energy barrier between the source and the channel is modulated by the gate voltage, while the drain bias has a small effect. Reducing the height of the barrier results in an increased current flow, since this is directly controlled by carriers injection across the barrier.

Assuming occupation of only one sub-band, the total current induced as the carriers inject from each side into the other can be described as  $I_{DS} = I^+ - I^-$ , where

$$I^+ = \frac{q^2 k_B T}{\pi \hbar} F_0(\eta_F), \qquad (3.1)$$

$$I^- = \frac{q^2 k_B T}{\pi \hbar} F_0(\eta_F - U_D) \tag{3.2}$$

$k_B$  is Boltzmann's constant, T represents the temperature,  $\eta_F = \frac{E_F - \varepsilon(0)}{k_B T}$ , which measures the location of Fermi level with respect to the conduction band edge, also so called reduced Fermi energy.  $U_D = \frac{qV_d}{k_B T}$  and  $F_0$  is the zeroth order Fermi-Dirac integral.

The potential at the top of the barrier is determined from the solution of Poissons equation for three-capacitor system. This system represents the effect of the three terminals; gate, drain and source, on the potential of the barrier. An equivalent system is illustrated in Fig.3.1. The potential at the top of the barrier is defined as

$$-\varepsilon(0) = \frac{C_g}{C_{\Sigma}} q V_g + \frac{C_d}{C_{\Sigma}} q V_d + \frac{C_s}{C_{\Sigma}} q V_s - \frac{Q}{C_{\Sigma}} q$$

(3.3)

where the bias-induced charges or so called local density of states at the top of the barrier, Q, are included.  $C_{\sum}$  is the sum of the parallel coupled capacitances,  $C_g$ ,  $C_s$  and  $C_d$ .  $C_g$  is the intrinsic gate capacitance, and is defined as a sum of the parallel coupled capacitances,  $C_{ox}$  and  $C_Q$ .

$$C_g \approx \frac{C_{ox}C_Q}{C_{ox} + C_Q} \tag{3.4}$$

$C_{ox}$  is the gate oxide capacitance, that is determined by the geometry of the considered device.  $C_Q$  represents the quantum or semiconductor capacitance.  $C_g$  can also be defined as the total gate capacitance (per unit gate length),  $C_{gg}$ .

#### **Ballistic 1D Current**

The operation regimes of all transistors can be divided into two categories; the charge controlled or classical limit (CL) and the band controlled or quantum capacitance limit (QCL). The simulations and numerical calculations in this thesis are mainly performed in the QCL regime. This regime is achievable by 1-D nanowire MOSFETS due to their unique scaling potential regarding oxide thickness, body thickness, and channel length.

Under certain assumptions, calculation of the current in the cylindrical nanowire can be simplified. By considering three regions of operation, three equations of  $I_{DS}$  can therefore be derived. For simplicity, the following considerations have been taken into account:

- High degenerate condition, meaning  $\eta_F \gg 1 \Rightarrow F_0(\eta_F) \Rightarrow \eta_F$

- Studying the scaling behavior of the transistor in quantum-capacitance limit (QCL), where  $C_{ox} \gg C_Q \Rightarrow C_g \approx C_Q$ . In the QCL, the potential inside the channel is determined by the gate potential suppressing the short channel effects [49].

- Considering operation in the active region of the transistor, above threshold voltage, where  $E_{F,D} < \varepsilon(0) < E_{F,S}$ . This menas that the channel is occupied only by carriers from the source reservoir, leading to  $I^- = 0$ .  $I_{DS}$  is independent of  $V_{ds}$  and it increases linearly with the applied bias voltage,  $V_{qs}$ .

• Assuming electrostatically well-designed transistor with  $C_g = C_{geo} \gg C_d$ ,  $C_s$ . According to that, equation (3.3) can be rewritten as  $\varepsilon(0) = -qV_{qs}$ .

Following these considerations,  $I_{DS}$  can be defined as

$$I_{DS} = \frac{2q^2}{h} \eta_F \approx \frac{2q^2 k_B T}{h} (E_F - \varepsilon(0)) = \frac{2q^2}{h} (E_F + qV_{gs})$$

(3.5)

q is the elementary charge and h is Planck's constant. The equation is expressed for one sub-band.

## 3.2 Quantum Capacitance

The potential within the channel is determined by the gate voltage in the quantum capacitance limit (QCL). This is assumed since nanowire transistors are expected to operate in the quantum limit as they are downscaled into a few sub-bands regime. Equation (3.4) is approximated to  $C_{gg} \approx C_Q$  in the quantum limit, as  $C_{gg} \gg C_Q$ . Quantum (or semiconductor) capacitance is gate-voltage-dependent, and is evaluated from

$$C_Q = \frac{\partial Q_g}{\partial V_{gs}} = \frac{\partial}{\partial V_{gs}} (L_g N_{1D} F_{-1/2}(\eta_F(V_{gs})))$$

(3.6)

where  $N_{1D} = \frac{\sqrt{2m^* k_B T/\pi}}{\hbar}$ , is the one-dimensional effective density of states,  $Q_g$  is the charge carriers in the channel, and  $F_{-1/2}(\eta_F)$  is the Fermi-Dirac integral of order -1/2.

$$F_{-1/2}(\eta_F) = \frac{1}{\sqrt{\pi}} \int_0^\infty \frac{\varepsilon(0)^{-1/2}}{1 + e^{\varepsilon - \eta_F}} d\varepsilon$$

(3.7)

$m^*$  is the effective mass of the semiconductor. The index of Fermi-Dirac integral indicates the dimension of the semiconductor. Accordingly, an index equals to -1/2 corresponds to one dimensional semiconductor.

Fermi-Dirac integrals have the property that [47]

$$\frac{dF_j}{d\eta_F} = F_{j-1} \tag{3.8}$$

Equation (3.6) can therefore be given by

$$C_Q = \frac{N_{1D}}{2k_B T} F_{-3/2}(\eta_F) \tag{3.9}$$

# 3.3 Ballistic Transconductance

Transconductance,  $g_m$ , is an important performance metric in RF applications as it expresses the efficiency of the gate voltage to modulate the energy barrier of the channel.  $g_m$  is defined as partial derivative of the drain current with respect to gate voltage

$$g_m = \frac{\partial I_{DS}}{\partial V_{as}} \tag{3.10}$$

In the active device region, and in the quantum capacitance limit,  $C_{ox} \gg C_Q$ ,  $g_m$  is obtained by derivation of equation (3.5). Following the assumptions listed in section 3.1 gives

$$g_m = \frac{2q^2}{h} \tag{3.11}$$

The channel transconductance is, indeed, independent of the gate bias as equation (3.11) states [39].

Fully ballistic transistor are assumed. However, truly ballistic devices are difficult to achieve in reality due to scattering in the channel. Modeling quasi-ballistic devices, devices with some amount of scattering, is therefore preferred to obtain an accurate analysis of device performance.

# CHAPTER 4

## **RF-Transistors**

The objective of this chapter is to explore the radio frequency (RF) performance of nanowire transistors. An optimized vertical FET layout is first considered and finite-element modeling software, COMSOL Multiphysics, is used. Performing this simulation is important to emphasize the impact of parasitic capacitances and resistances on transistor performance. RF figures of merit;  $h_{21}$ , U, MAG and MSG, are defined by deriving explicit expressions using admittance (Y) parameters. To estimate these parameters two-port network is considered during the calculation. The two most important metrics for transistors are unity current gain frequency,  $f_T$ , and maximum power gain frequency,  $f_{max}$ . These are determined from the hybrid- $\pi$  small-signal model. Ideally, these frequencies should be large in order to achieve RF applications with high operational frequency.

## 4.1 Simulation details

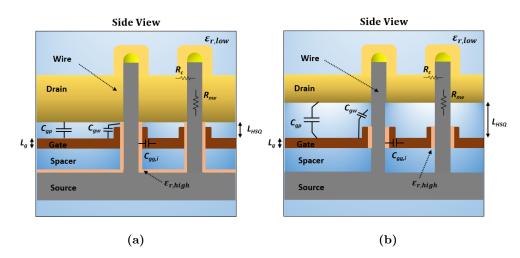

### 4.1.1 Device Structure

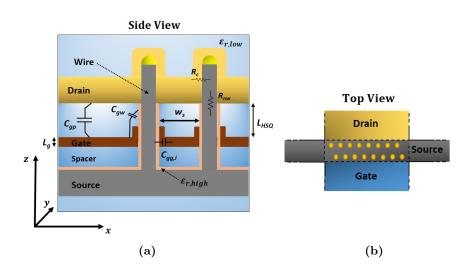

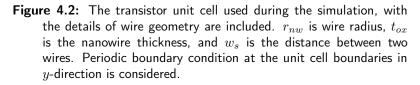

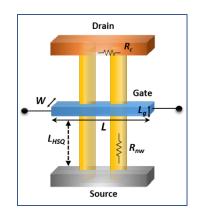

Fig.4.1 (a) illustrates a cross-sectional layout of a nanowire FET structure. A model similar to this structure has been modeled using COMSOL Multiphysics. This structure consists of two rows of semiconductor arranged in a triangular fashion as shown in Fig.4.1 (b), forming transistor unit cell of width of  $2(r_{nw} + t_{nw}) + w_s$ . The distance between two nanowires is represented by  $w_s$ , as illustrated in Fig.4.1 (a) and Fig.4.2. According to [35, 39], the triangular arrangement of nanowires allows for less complicated fabrication methods, Moreover, this configuration results in lower gate resistance in comparison to hexagonal patterns.

The extrinsic and intrinsic capacitances are also included in the structure, together with the specific contact resistance,  $R_c$ , and the nanowire resistances,  $R_{nw}$ .

**Figure 4.1:** A schematic side view illustration of the modeled nanowire FET structure including the extrinsic capacitances ( $C_{gp}$  and  $C_{gw}$ ), intrinsic gate capacitance,  $C_{gg,i}$ , contact resistance,  $R_c$ , and the nanowire resistance,  $R_{nw}$ . The entire structure is embedded in low- $\kappa$  material, where  $L_{HSQ}$  is the distance between two metal contacts. (b) A Top view of a 2D device structure, illustrating the electrode configuration, as well as the triangular arrangement of the nanowire array.

The nanowires are assumed to be heavily doped and here to be considered as metallic leads. The nanowires are covered with high- $\kappa$  oxide,  $\varepsilon_{r,high} \approx 20.0$ , and with an oxide thickness of  $t_{ox}$ . The relatively thick high- $\kappa$ oxide films solve the gate leakage issues by preserving the electrostatics. The gate-contact is symmetrically arranged in the center of the nanowire.  $L_{HSQ}$  depicts the equal separation distance between the gate-source and gate-drain. Source and drain contacts are patterned along the nanowires. The device is embedded in a large box of a low- $\kappa$  material with a relative permittivity of  $\varepsilon_{r,low} \approx 3.00$ . This means that the spacer material has same  $\kappa$ -value as that for embedding material.

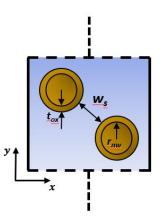

### 4.1.2 Numerical Modeling

3D finite element method (FEM) solver (COMSOL Multiphysics) is used to obtain quantitative values of the extrinsic capacitances of the modeled transistor unit cell illustrated in Fig.4.2. To obtain a deeper understanding of how the transistor structure is best optimized, three structures have been modeled during this thesis. The obtained results from the numerical calculation of parasitic capacitances,  $C_{gs,p}$  and  $C_{gd,p}$ , and intrinsic gate capacitance,  $C_{gg,i}$ , are normalized to one nanowire. Sections (3.2) and (4.2.2) provide further explanation of the origin of these capacitances.

The first model is a symmetric 3D structure, where the source-gate distance and the gate-drain distance are equal. The total capacitance of the structure is evaluated and the effect of varying the  $\kappa$ -value of the embedded material is studied. The result is demonstrated for a single nanowire. The correlation between parasitic capacitance and relative permittivity is explicitly understood when considering plate parallel capacitor equation, expressed as

$$C = \frac{\kappa \varepsilon_0 A}{d_{HSQ}} \tag{4.1}$$

$\varepsilon_0$  is the vacuum permittivity,  $d_{HSQ}$  represents the thickness of HSQ layer, and A is the area of the plate capacitor. According to this equation, the capacitance is linearly depended on the relative permittivity,  $\varepsilon_r$ . Minimized parasitic capacitance is achieved by having a spacer material with low  $\varepsilon_r$ .

The second structure, shown in Fig.4.3 (a), is modeled to study how the contacts overlap capacitance,  $C_{gp}$ , changes as the gate-drain distance,  $L_{HSQ}$ , is varied between 30 nm to 130 nm. In the third 3D structure, the high- $\kappa$  coating material around the nanowires is removed and only remained around the gate surrounded segments of the nanowires, as shown in Fig.4.3 (b). This structure was considered to study the possibility of minimizing the capacitance,  $C_{gw}$ , by replacing the high- $\kappa$  coating film with a low- $\kappa$ material.

**Figure 4.3:** A schematic side view of two additional models of the nanowire FET. (a) The drain contact thickness is varied in order to investigate how the overlap capacitance changes as the distance  $L_{HSQ}$  is varying between 30 to 130 nm. (b) The high- $\kappa$  oxide film is only covering the gated segment of the nanowire.

In these simulations, the terminal input is represented by the gate metal, with a voltage of  $V_0 = 1$  V. The cylindrical nanowires and source/drain metals are modeled as metallic elements with a surface potential of 0 V. The nanowires are coated with a high- $\kappa$  dielectric ( $\varepsilon_{r,high} = 20$ ), of thickness  $t_{ox} = 5$  nm.

The structures are embedded in a large enough bounding box to neglect any considerable effect of the capacitances at the contact edges, which might complicate the capacitance calculation. In order to calculate the parasitic capacitances in the transistor unit cell, periodic boundary condition at the unit cell boundaries in y-direction is considered, as illustrated in Fig.4.2. For those models, symmetric structure around z-axis is assumed, meaning that the total calculated source-gate and gate-drain parasitic capacitances are equal.

To calculate the intrinsic gate capacitance,  $C_{gg,i}$ , section (3.2) is to be considered. According to [34], intrinsic gate capacitance,  $C_{gg,i}$ , is decreased with wire radius. A wire radius of  $r_{nw} = 5$  nm was used in these simulations. However, a radius ranged between 5 - 20 nm has been studied in [31] Fig.2, where a radius of 5 nm showed less possible intrinsic gate capacitance.

## 4.2 Numerical Calculation of RF Metrics

To calculate the RF metrics of nanowire transistors, a small-signal model circuit is first to be considered. Equations necessary to calculate the electrical elements of this circuit are explained in this section.

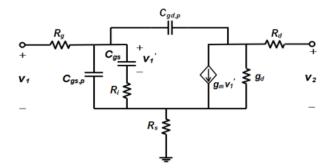

## 4.2.1 Small-Signal Model

The small-signal model of nanowire FETs is represented by using a similar scheme to that of traditional three-terminal MOSFET at an arbitrary frequency. This mainly depends on the fact that the gate metal is insulated from the channel by the high- $\kappa$  coating material [34]. The circuit model consists of elements that are related to the physical behavior of nanowire transistors. Neglecting the effect of body bias, the traditional two-port small-signal hybrid- $\pi$  model, shown in Fig.4.4, is used to study the RF performance of 1-D MOSFETs.

**Figure 4.4:** A small signal hybrid- $\pi$  circuit model with the passive elements of a three-terminal FET. Intrinsic and extrinsic capacitances and resistances are included.

The transconductance,  $g_m$ , and output conductance,  $g_d$ , are included in the small-signal model together with  $R_g$ ,  $R_s$  and  $R_d$  to model the resistances of the effective gate, source and drain, respectively. In general, keeping the output conductance minimized is desired to acquire a large intrinsic voltage gain,  $A_v = g_m/g_d$ . The output conductance is defined as the partial derivative of drain current with respect to source-drain voltage,  $g_d = \frac{\partial I_{DS}}{\partial V_{ds}}$ . Nanowire FETs are suitable for high values of power gain due to the enhanced electrostatics. Therefore, nanowire FETs are expected to show a lower  $g_d$ . For this reason,  $g_d$  can be approximated as

$$g_d \approx \frac{g_m}{5} \tag{4.2}$$

which is a typical value that is used when dealing with nanowire FETs.

The resistive element or the channel resistance,  $R_i$  is also included in the small-signal model. The nanowire FET structure is assumed to operate in non quasi-static condition, which means that a phase-lag RC, due to scattering, is introduced. The channel resistance is defined as

$$R_i = \frac{1}{1.4g_m} \tag{4.3}$$

### 4.2.2 Device Capacitances

The capacitances  $C_{gs}$ ,  $C_{sd}$  and  $C_{gd}$  model the charging currents or how the number of charge carriers changes with the applied voltage at different contacts. These capacitances include both the intrinsic and extrinsic capacitances of the device.

The intrinsic gate capacitance,  $C_{gg,i}$ , is expressed as  $C_{gg,i} = C_{gd,i} + C_{gs,i}$ , and is scaled approximately linearly with the gate length, given  $C_{gg,i} \sim L_g C'_G$ . The effect of the gate capacitance is reduced by decreasing the gate length [31].  $C'_G$  is modeled as the sum of the parallel coupled capacitances  $C_{ox}$ ,  $C_Q$  and  $C_C$ .  $C_{ox}$  is the oxide capacitance,  $C_Q$  represents the quantum capacitance, and  $C_C$  is the centroid or band bending capacitance.

$C_{geo}$  represents the gate oxide capacitance for cylindrical geometry, and is defined as [31]

$$C_{geo} = \frac{2\pi\epsilon_0\epsilon_{ox}}{\ln(\frac{r_w + t_{ox}}{r_w})} \tag{4.4}$$

To predict the AC behavior of the device it is important to take the effect of parasitic capacitances associated with the device into account. These capacitances have a large influence on the operation speed of the digital circuit. By using a simple approximation, the values of the parasitic capacitances can be determined.

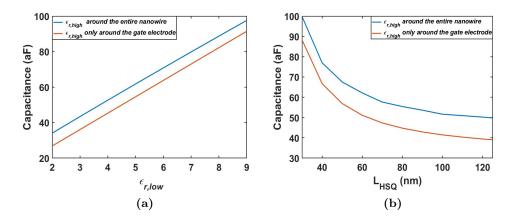

As illustrated in Fig.4.1 (a), the parasitic gate capacitance along the nanowire can be divided into  $C_{gw}$  and  $C_{gp}$ .  $C_{gp}$  is the parasitic capacitance originates from the fringing electric field between the gate electrode and the source/drain reservoir, while  $C_{gw}$  is due to the fringing electric field between the gate electrode and the nanowire source/drain lead [34]. Assuming symmetric structure, the total source and drain parasitic capacitances can be defined as  $C_{gs,p} = C_{gd,p} = C_{gw} + C_{gp}$ . The parasitic capacitances depend on the device geometry where the nanowire spacing is the key parameter in reducing these capacitances. The electric field between the gate electrode and drain/source electrode is more efficiently screened in dense nanowire arrays. Therefore, dense arrays are superior in minimizing both  $C_{gw}$  and  $C_{qp}$  [31, 53].

## 4.2.3 Device Resistances

The performance of any electronic device, especially the energy efficiency and operational frequency in MOSFETs, is further degraded due to the effect of extrinsic resistances. In this thesis, standard transmission line method (TLM) for vertical geometry is demonstrated to characterize the specific contact resistance between the metal contact and the semiconductor nanowire [41].

HSQ - thickness is systemically varied to estimate the nanowire resistance. The total resistance of the nanowire FETs is modeled as two series elements. These include nanowire resistance  $R_{nw}$  and contact resistance,  $R_c$ , between the nanowire and metal contact (source/drain). These resistances are depicted in Fig.4.5.

**Figure 4.5:** A schematic view of a 3D nanowire FET structure with resistances included. The length and width of the gate contact is equal. A similar structure has been modeled in COMSOL to determine the sheet gate resistance.

Due to the cylindrical geometry of the nanowire, equation (4.5) is used to calculate the uniform resistivity of the nanowires.

$$R_{nw} = \frac{\rho_s L_{HSQ}}{\pi r_{nw}^2} \tag{4.5}$$

$L_{HSQ}$  is the distance between the gate and source/drain contacts, which is equal in symmetric structures.  $\rho_s$  is the resistivity of the semiconductor, given by

$$\rho_s = \frac{1}{\sigma_n} = \frac{1}{q\mu_n n} \tag{4.6}$$

$\sigma_n$  is the electron mobility,  $\mu_n$  is electron conductivity and n is the electron concentration. The contact resistance can be modeled as distributed

resistive network, and is defined by equation (4.7).

$$R_c = \frac{\rho_s L_{nw}}{\pi r_{nw}^2} \coth(\frac{L_{nw} - L_{HSQ}}{L_T})$$

(4.7)

$$L_T = \sqrt{\frac{r_{nw}\rho_c}{\rho_s}} \tag{4.8}$$

$$\rho_c = \frac{2L_T^2 \rho_s}{r_{nw}} \tag{4.9}$$

$L_{nw}$  is the total length of the nanowire, and  $L_T$  is the metal-semiconductor transfer length, given by equation (4.8).  $\rho_c$  is the specific contact resistivity and is calculated from equation (4.9) [41].

At low frequencies, the input resistance, or so called  $R_g$ , corresponds to one third of the total end-to-end gate metal resistance. Generally,  $R_g$  is an intrinsic resistance, since it is more likely linked to the manufacturing process.  $R_g$  is a critical parameter that thoroughly impacts the switching performance and power conversion efficiency of the device. Equation (4.10) is used to determine the value of this resistance.

$$R_g \approx \frac{1}{3} \frac{W}{L} R_{SHG} \tag{4.10}$$

W and L represent the width and the length of the considered gate contact, respectively.

To determine the value of  $R_g$ , the gate metal resistance or the sheet gate resistance  $R_{SHG}$  is determined by numerical calculation, considering the model shown in Fig.4.5. This cross-sectional layout illustrates a gate electrode, with W/L ratio of 1.

#### 4.2.4 Nanowire FET Scaling

As previously mentioned, a transistor is more likely to be suitable for RF applications if it displays high  $f_T$  and  $f_{max}$ . Scaling the gate length contributes to a minimized intrinsic gate capacitance, since the last mentioned scaled linearly with the gate length, as explained in section (4.2.2).

In order to understand the relation between scaling of the gate length and an improved transconductance,  $g_m$ , equation (4.11) could be considered. This equation is mainly extracted for devices with a relative long gate length, and operate in the diffusive limit.

$$g_m = \frac{WC_g \mu_n (V_{gs} - V_T)}{L_g}$$

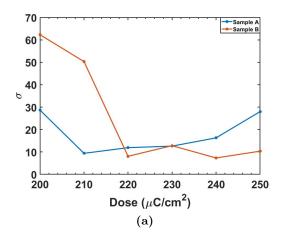

(4.11)