Implementation of an 8-bit Dynamic Fixed-Point Convolutional Neural Network for Human Sign Language Recognition on a Xilinx FPGA Board

RICARDO NÚÑEZ PRIETO MASTER'S THESIS DEPARTMENT OF ELECTRICAL AND INFORMATION TECHNOLOGY FACULTY OF ENGINEERING | LTH | LUND UNIVERSITY

Implementation of an 8-bit Dynamic Fixed-Point Convolutional Neural Network for Human Sign Language Recognition on a Xilinx FPGA Board

> Department of Electrical and Information Technology Lund University

> > MASTER OF SCIENCE THESIS — March 17, 2019 —

Author: Ricardo Núñez Prieto

Supervisor: LIANG LIU Examiner: ERIK LARSSON

© 2019 Printed in Sweden Tryckeriet i E-huset, Lund Para Erik, una pequeña red neuronal que está en camino... Diciembre, 2018

## Abstract

The goal of this thesis work is to implement a convolutional neural network on an FPGA device with the capability of recognising human sign language. The set of gestures that the neural network can identify has been taken from the Swedish sign language, and it consists of the signs used for representing the letters of the Swedish alphabet (a.k.a. *fingerspelling*).

The motivation driving this project lies in the tremendous interest aroused by neural networks in recent years for its ability for solving complex problems and its capacity to learn by example. More specifically, convolutional neural networks are being extensively used for image classification, and this project aims to design a hardware accelerator to compute the convolutional layers of such type of network topology and test its accuracy and performance when dealing with human sign language. Further applications for this hardware solution can be placed in the educational field, specially addressed to children with impaired hearing or as a translation system in specific situations.

The network topology of choice is Zynqnet, proposed by Gschwend in 2016, which is a topology that has already been implemented successfully on an FPGA platform and it has been trained with the large picture dataset provided by ImageNet, for its popular image recognition contest. In this regard, the aim of this work is not to propose a new neural network topology but to re-use an existent one by introducing some improvements like the utilisation of an 8-bit dynamic fixed-point scheme and challenge it with a different but related task, like human sign language recognition.

The methodology followed to carry out a successful hardware implementation has consisted, first, of the installation and setup of a reliable framework used for the training of the neural network. Different frameworks were tried out, like MATLAB or Caffe, but finally, DIGITS from NVIDIA was the more convenient due to its graphical environment and because it provides all the compatibility and drivers needed to run together with the GPU used in this project. Then, an image dataset of more than 13,000 pictures of hand gestures has been built up to grant enough input data for the framework to fine-tune ZynqNet for the new task, i.e. to provide the neural network with the ability to classify the different hand-signs into its corresponding alphabet letter. In parallel, the Register-Transfer Level (RTL) abstraction of the hardware architecture has been generated using a High-Level Synthesis tool chain, in which the algorithmic descriptions are written in C/C++. Finally, the validation of the design has been done by means of co-simulation techniques where the golden data obtained with the C test bench is compared with the output data of the RTL implementation, and all of it within the simulation environment provided by the Vivado Design Suite.

As a result, the best-performing obtained solution achieved an accuracy of 80.1% in the inference test and a frame rate of 6.4 FPS with a clock frequency of 250 MHz.

## **Popular Science Summary**

Neural networks are becoming more and more ubiquitous in our everyday lives, many times in ways that we do not even realise. Artificial Intelligence (AI) is extensively used nowadays to improve the user's experience with digital technologies, for instance, the on-the-fly translation service provided by Skype and Google. In other fields like robotics, improvements in object detection from the hand of machine learning, allow robots and autonomous cars to take better decisions. And in medicine, automatic detection of blood diseases like leukaemia and lymphoma, powered by neural networks algorithms, have accelerated and improved diagnosis. So the list of applications found in many diverse fields goes on and on.

Now, let's picture yourself in the hypothetical situation in which you have a friend or a relative who has been born with a hearing impairment. This person has been taught sign language from an early age on a specialised school, and you would like to learn sign language too so you both can have meaningful and pleasant communication. Furthermore, you want to be able to help this person in day-to-day situations where deaf people can be in clear disadvantage like a routine visit to the doctor or administrative processes.

You learn from one of your classmates at the university about a mobile app which employs a deep neural network to recognise human sign language just by using the phone camera. The application translates the captured sequence of gestures from video to written text in real-time and automatically reproduces the message in the phone speaker. It also includes a sign language tutorial which can help you to rapidly learn to communicate by using your hands. The software records your gestures and improves your learning abilities by telling how accurate are your movements.

Well, the situation just described is something that I believe it is not far to happen. The computational power found in embedded systems such as mobile phones is growing by the day. So far, at least, one can find mostly solutions that work one-way, that is, they convert speech into sign language, by mapping spoken language to signs and using a virtual animated human-like avatar. Fewer solutions can translate sign language into speech. Some of them use special gloves with position sensors not so pleasant to wear by the *signer* person, and others use 3D cameras that can pick the speaker's body gestures and then compare the obtained frame sequence with a reference frame stored in a dictionary. These solutions though, rely on mapping methods and are limited in terms of the number of gestures they can interpret.

I really believe that neural networks are a game changer and they will bring powerful, elegant solutions to the kind of problems described above. This thesis work aims to provide proof-of-concept of a feasible implementation of a neural network trained for recognition of human sign language. The number of gestures to recognise is limited to the Swedish alphabet, and the network must show an acceptable level of prediction accuracy, throughput and area utilisation.

The content of this thesis is addressed to a variety of public: from people interested in neural networks in general, and the significant development experienced in the field in recent years, to people interested in learning the basic concepts and the methodology for training neural networks, or practitioners who look to implement a deep learning model on an AI accelerator.

## Acknowledgements

First, I am grateful to professor Liang Liu for supervising this work and for providing fruitful ideas and support.

I want to express my gratitude to Lund University for giving me the opportunity to take this Master Program in Embedded Electronics Engineering and also for the four years I spent working for the MAX-IV project.

Thanks a lot to my teachers and classmates with whom I have shared these three years: Arun, Leo, Luis, Berta, Mayra, Shenba... thanks for the inspiring and funny little moments we have passed together and made of this a more pleasant journey. I wish you all the best of luck in both your professional and life projects.

Last but not least, I would like to thank especially my wife and my daughter for their love and support that carried me through every challenge I have faced, and also to my parents for their esteem and being always there.

Ricardo Núñez Prieto Lund, February 2019

# Table of Contents

| Abstract |       |                                                    | iii |

|----------|-------|----------------------------------------------------|-----|

|          |       |                                                    |     |

|          |       |                                                    |     |

| Li       | st of | Figures                                            | xi  |

| Li       | st of | Tables                                             | xv  |

| 1        | Intr  | oduction                                           | 1   |

| -        | 1.1   | Background and Motivation                          | _   |

|          | 1.2   | Project Goals and Main Challenges                  |     |

|          | 1.3   | Approach and Methodology                           | 4   |

| 2        | Basi  | ic Concepts                                        | 7   |

|          | 2.1   | Foundations of Artificial Neural Networks          | 7   |

|          | 2.2   | Backpropagation Algorithm                          | 16  |

|          | 2.3   | Neural Networks are Universal Approximators        | 19  |

|          | 2.4   | Example of a Convolutional Neural Network: ZynqNet | 21  |

| 3        | Trai  | ning of a Deep Neural Network                      | 25  |

|          | 3.1   | Training Framework                                 | 25  |

|          | 3.2   | Making of a Training Dataset                       | 26  |

|          | 3.3   | 5 5                                                | 31  |

|          | 3.4   | Training Hyper-Parameters                          | 32  |

|          | 3.5   | Post-Training Network Quantisation                 | 34  |

|          |       | 3.5.1 CNN Quantisation with Ristretto              | 35  |

|          | 3.6   | Training Results                                   | 36  |

| 4   | Desi  | gn and Implementation of a CNN Hardware Accelerator | 43 |

|-----|-------|-----------------------------------------------------|----|

|     | 4.1   | Project Goals and System Requirements               | 43 |

|     |       | 4.1.1 Memory Requirements                           | 44 |

|     | 4.2   | Adapting the ZynqNet Topology                       | 46 |

|     | 4.3   | Design Strategy                                     | 48 |

|     |       | 4.3.1 Block Processing                              | 48 |

|     |       | 4.3.2 Array Partitioning                            | 50 |

|     | 4.4   | Model Operation and Hardware Description            | 50 |

|     |       | 4.4.1 Main Process Unit                             | 53 |

|     |       | 4.4.2 Memory Controller                             | 55 |

|     |       | 4.4.3 Convolution Core                              | 55 |

|     |       | 4.4.4 Arithmetic Logic Unit                         | 59 |

|     | 4.5   | Behavioural Model Validation and RTL Verification   | 61 |

|     |       | 4.5.1 Validation of the C-based Model Description   | 61 |

|     |       | 4.5.2 Post-Synthesis RTL Verification               | 62 |

|     | 4.6   | HLS Limitations and Issues                          | 63 |

| 5   | Resi  | Ilts and Conclusions                                | 65 |

|     | 5.1   | Accuracy Results                                    | 65 |

|     | 5.2   | Resource Utilisation and Performance                | 68 |

|     | 5.3   | Conclusions                                         | 74 |

|     | 5.4   | Future Work                                         | 75 |

| Re  | feren | ices                                                | 77 |

| Lis | st of | Acronyms                                            | 83 |

| Ap  | pend  | lix A ZynqNet                                       | 85 |

| Ap  | pend  | lix B Test Dataset                                  | 86 |

# List of Figures

| 2.1  | Representation of an artificial neuron with multiple inputs. The       |    |

|------|------------------------------------------------------------------------|----|

|      | bias $b_i$ is added to the linear combination of the neuron weighted   |    |

|      | inputs $x_1, x_2, x_r$ and the obtained sum $a_i$ is then used as the  |    |

|      | input parameter of the activation function $f$ to generate the         |    |

|      | neuron output $y_i$ (Source: derived from Tanikić and Despotović,      |    |

|      | 2012 [18]).                                                            | 8  |

| 2.2  | Graphs for the sigmoid and the Rectified Linear Unit (ReLU)            |    |

|      | functions.                                                             | 8  |

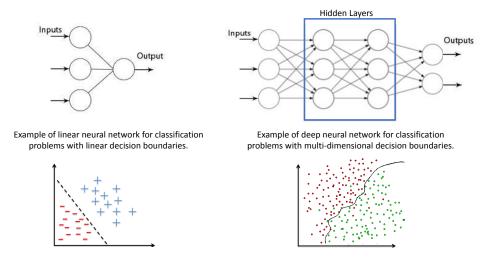

| 2.3  | Example of a neural network without hidden layers used in a            |    |

|      | binary classification problem (left) versus a neural network with      |    |

|      | hidden layers performing as a non-linear classifier (right)            | 10 |

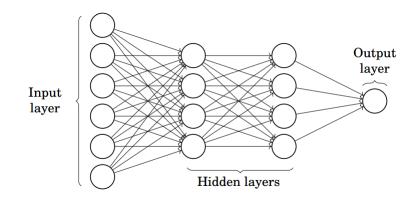

| 2.4  | Diagram of a Multilayer Perceptron Network (Source: Pavlovsky,         |    |

|      | 2017 [19])                                                             | 11 |

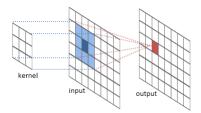

| 2.5  | 2-D discrete convolution obtained by sliding the kernel along          |    |

|      | the input image (Source: Intel Labs [20]).                             | 11 |

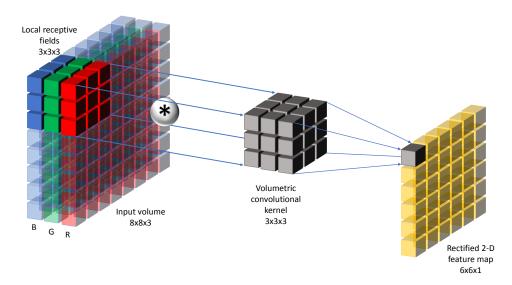

| 2.6  | Representing a full-colour RGB input image as a volume and             |    |

|      | applying a volumetric convolutional filter                             | 12 |

| 2.7  | Example of 2-D matrix convolution with zero-padding (Source:           |    |

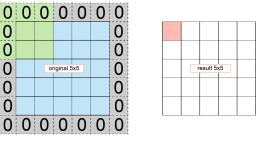

|      | derived from Dertat, 2017 [22])                                        | 14 |

| 2.8  | 3-D representation of a convolutional neural network with pool-        |    |

|      | ing layers (Source: Cord, 2017 [23])                                   | 15 |

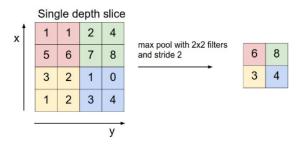

| 2.9  | Example of a <i>max</i> pooling operation using 2x2 filters and stride |    |

|      | 2 (Source: Karpathy [24])                                              | 15 |

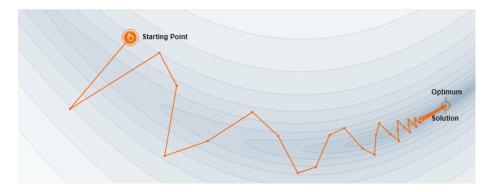

| 2.10 | Stochastic Gradient Descent algorithm searching for the local          |    |

|      | minimum (Source: Goh, 2017 [27])                                       | 18 |

| 2.11 |                                                                        |    |

|      | den layer. The network output corresponds to the contribution          |    |

|      | of the top hidden neuron alone (Source: Nielsen, 2015 [31]).           | 19 |

| 2.12 | Network output re-shaped like a step-function by modifying             |    |

|      | parameters $w$ and $b$ (Source: Nielsen, 2015 [31])                    | 20 |

|      |                                                                        |    |

| 2.13 | The network output corresponds to the linear combination of both hidden neuron activations ( <i>Source: Nielsen, 2015 [31]</i> ).                                                                                                                                                       | 20 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.14 | Approximation of an arbitrary function by adding additional neurons in the hidden layer ( <i>Source: Nielsen, 2015 [31]</i> )                                                                                                                                                           | 21 |

| 2.15 | Detail of the fire module in SqueezeNet (Source: derived from Netscope CNN Analyzer [32] and Iandola, 2016 [26])                                                                                                                                                                        | 22 |

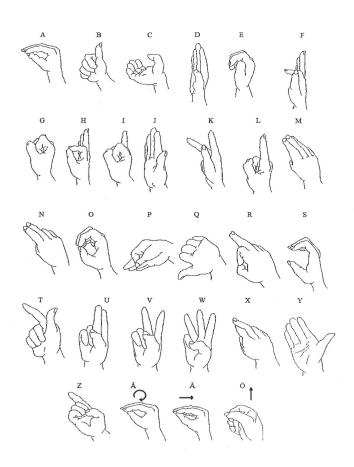

| 3.1  | Swedish hand alphabet (Source: Ene, 2015 [37])                                                                                                                                                                                                                                          | 27 |

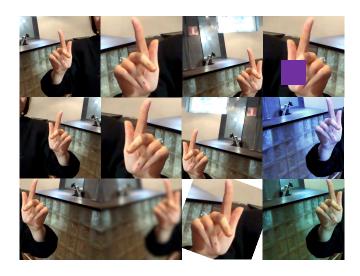

| 3.2  | Representation of the Swedish sign alphabet by using sample images used for the training.                                                                                                                                                                                               | 28 |

| 3.3  | Data augmentation techniques applied on a same picture                                                                                                                                                                                                                                  | 30 |

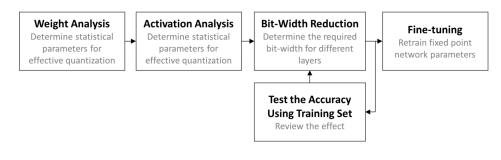

| 3.4  | Ristretto's network approximation flow to compress a floating-<br>point network into fixed-point ( <i>Source: Gysel, 2016 [46]</i> )                                                                                                                                                    | 35 |

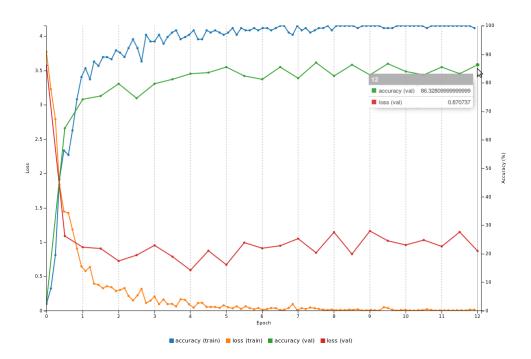

| 3.5  | DIGITS. Graph showing the progression of the training along<br>the different epochs. The quantities of interest are the training<br>accuracy, the validation accuracy and the value of the loss                                                                                         |    |

|      | function for both the training and the validation data                                                                                                                                                                                                                                  | 37 |

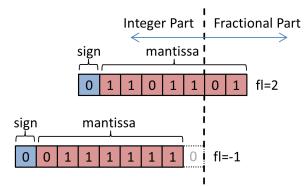

| 3.6  | Example of 8-bit dynamic fixed-point numbers. A number with a negative fractional length of -1, means that its integer length                                                                                                                                                           |    |

|      | is 9, although its bit-width is 8 <i>(Source: derived from Gysel, 2018 [47])</i>                                                                                                                                                                                                        | 40 |

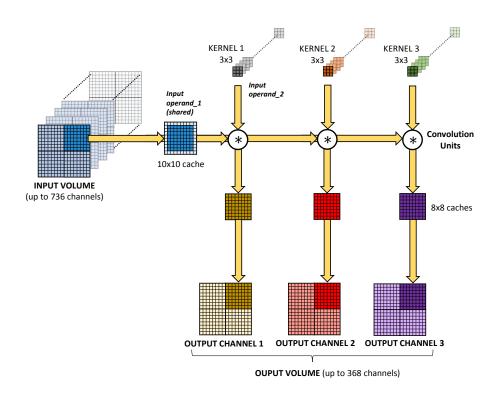

| 4.1  | Dataflow representation of the block processing approach. $\ . \ .$                                                                                                                                                                                                                     | 49 |

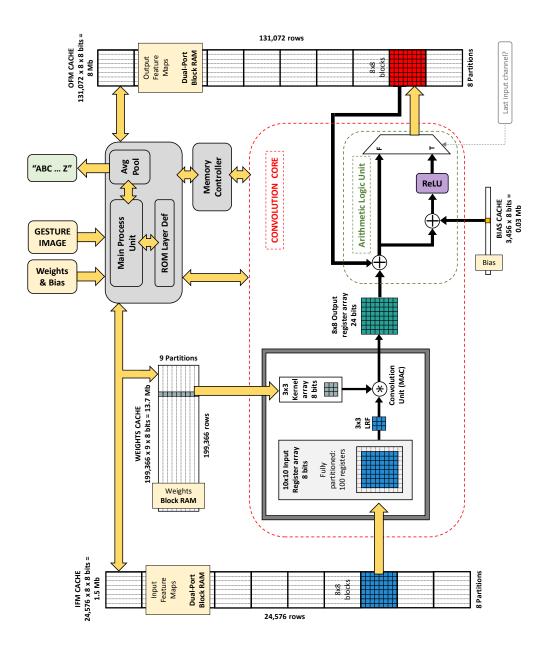

| 4.2  | Block diagram of the CNN hardware accelerator.                                                                                                                                                                                                                                          | 54 |

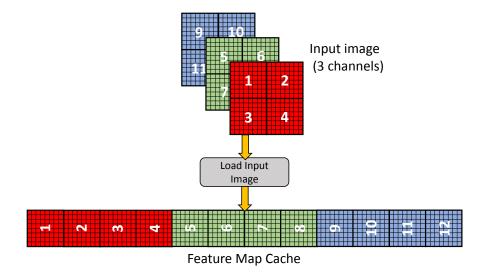

| 4.3  | Representation of the loading process of the input image into the internal cache.                                                                                                                                                                                                       | 55 |

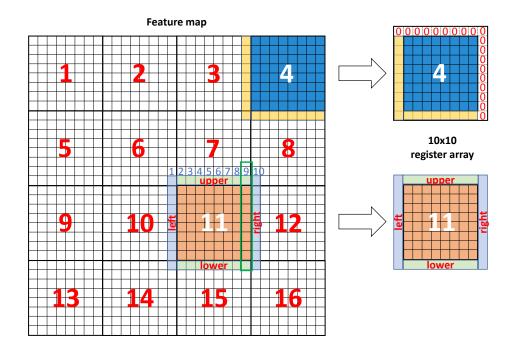

| 4.4  | Examples of the padding of the blocks forming the feature maps.<br>The numbering in the blocks indicates the processing order,<br>row-wise from left to right.                                                                                                                          | 57 |

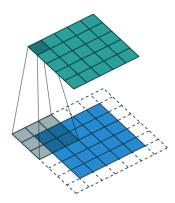

| 4.5  | The kernel (grey 3x3 matrix) slides over the padded block (blue matrix with white borders) producing one pixel at a time in the output matrix (in green). The grey area covered by the kernel corresponds to the <i>local receptive field (Source: Dumoulin and Visin, 2016 [50])</i> . | 58 |

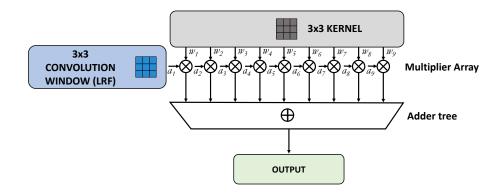

| 4.6  | Multiply-accumulate unit.                                                                                                                                                                                                                                                               | 59 |

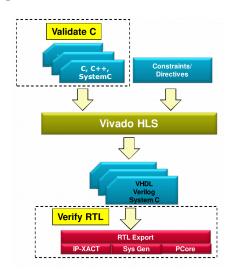

| 4.7  | Vivado HLS Flow: C Validation and RTL Verification <i>(Source: Xilinx Inc., 2013 [52])</i>                                                                                                                                                                                              | 61 |

| 5.1  | Example of a confusion matrix for a test dataset with five                                                                                                                                                                                                                              | 01 |

| 5.1  | different classes labelled as 0, 1, 2, 3 and 4 (Source: derived from Aditya, 2015 [55]).                                                                                                                                                                                                | 66 |

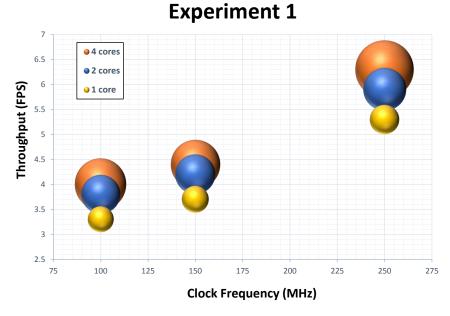

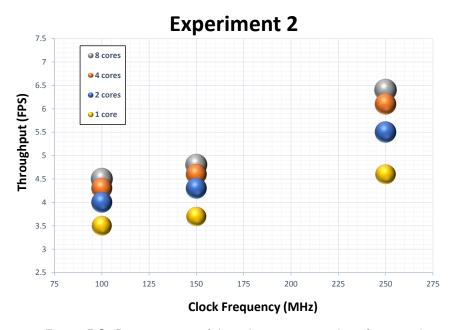

| 5.2 | Representation of throughput versus number of cores and FPGA clock frequency. The width of the spheres is proportional to the total resource utilisation of the FPGA. | 70 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.3 | Representation of throughput versus number of cores and FPGA clock frequency. The width of the spheres is proportional to the total resource utilisation of the FPGA. | 72 |

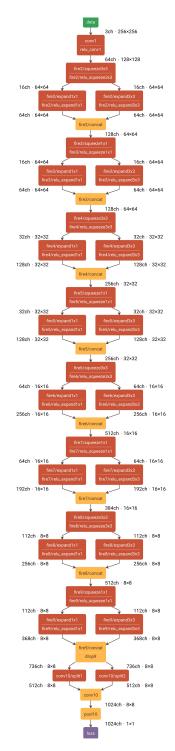

| A.1 | ZynqNet architecture (Source: Netscope CNN Analyzer [32]).                                                                                                            | 85 |

| B.1 | Images from the test dataset (categories from A to J)                                                                                                                 | 86 |

# List of Tables

| 2.1 | ZynqNet CNN architecture. Description of layers and hyper-<br>parameters.                                                                                                                          | 23 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | List of the hardware installed in the computer used as training station                                                                                                                            | 26 |

| 3.2 | Relative energy and area saving factors by comparing INT8 with FP32 operations.                                                                                                                    | 35 |

| 3.3 | Summary of the top-1 validation accuracy results obtained for different training jobs.                                                                                                             | 38 |

| 3.4 | List of the fractional lengths estimated by Ristretto for an 8-bit fixed-point quantisation of the model. Values are given layer by layer, for the input and output activations, weights and bias. | 39 |

| 3.5 | Evolution of the model validation accuracy along the different training stages. Quantisation and fine-tuning are performed using an 8-bit fixed-point format.                                      | 40 |

| 4.1 | Estimated memory requirements expressed in megabits                                                                                                                                                | 45 |

| 4.2 | Modified architecture of ZynqNet CNN for classification of 32 categories (each category is a letter of the alphabet).                                                                              | 47 |

| 4.3 | Cache sizes declared as two dimensional arrays                                                                                                                                                     | 50 |

| 5.1 | Rate of true positives (recall) and precision of the model for<br>each one of the classes, obtained from the simulation of the<br>RTL description model.                                           | 67 |

| 5.2 | Accuracy comparison of previous works with the model proposed in this thesis work.                                                                                                                 | 68 |

| 5.3 | Experiment 1. Post-synthesis resource utilisation and latencies as a function of the clock frequency and the number of convolution cores in parallel (FPGA device: Xilinx XCKU060)                 | 70 |

| 71 |

|----|

|    |

|    |

| 73 |

| -  |

| Chapter \_

## Introduction

Artificial Neural Networks (ANNs) are computational models inspired by the human brain's neural circuits that aim to solve complex real-world problems in fields as diverse as statistical data analysis, biology or economics.

ANNs consist of anything from hundreds to thousands, or even millions of processing nodes (a.k.a. neurons) that are organised in a series of layers. A typical neural network has an input layer, which connects the system to the external inputs, an output layer, and the remaining layers in between called hidden layers which are fully-connected with the layers on either side, meaning that each neuron of a hidden layer is connected to every neuron in the previous layer.

A neural network mimics a human brain mainly in two ways: 1) it learns by example, through a process of training, hence the knowledge is not programmed *a priori*, and 2) the knowledge is stored in the inter-connections or synapses between the different neurons in the form of synaptic weights, which can be understood as the grade of influence of an individual neuron over the surrounding ones when fired.

During the 80s and the 90s, neural networks were developed as software applications and were simulated in computers that used general-purpose microprocessors because they offered a good trade-off among features like small size, low price, low power and high performance. These computer systems could perform complex tasks such as mammographic analysis [1] in the field of medical imaging, or prediction of the sea-surface water temperatures [2] in the field of palaeoceanography. The drawback of this approach is that microprocessors have sequential von-Neumann architectures and are not fully able to replicate the massive parallelism present on neural networks. For that reason, efforts were made to implement ANNs as custom hardware accelerators, since many applications, in fact, require high-speed operations. The first successful ANN implemented in hardware was realised in 1991 using reconfigurable hardware, concretely on a logic cell array (LCA) from Xilinx [3]. It could compute 4.48 billion CPS (or inter-connections per second, meaning the rate of multiplication-accumulate operations during testing phase), making it suitable for applications in computing vision and, in particular, in industrial inspection tasks. Since then, technology advancements in VLSI have accelerated the transition of artificial neural networks from standard desktop computers and supercomputers to applications in embedded systems. The possibility of having available neural networks as a microelectronic component is very appealing as there is a need for its use in decentralised or mobile/embedded systems (like the upcoming IoT devices).

### 1.1 Background and Motivation

Convolutional Neural Networks (CNNs) or ConvNets are a class of specialised neural networks, known as deep neural networks, that are mostly used for image recognition tasks because they are very efficient in pattern recognition and feature extraction from the input images. In effect, they can be used in any task where the input data presents some hierarchical structure, with simple local patterns assembled in larger patterns which, in turn, are part of bigger complex arrangements.

CNNs belong to a new category of networks known as Deep Neural Networks (DNNs), which differ structurally from the early neural networks in the fact that they have more than one hidden layer. Aside from convolutional networks, there are other types of deep neural networks like autoencoders, deep belief networks (DBN) and recurrent neural networks (RNN). In particular, CNNs introduce a particular type of layer called convolutional layer which is simply a filter sliding, or convolving, around the input image computing element-wise multiplications.

Modern CNNs, as we know them today, derive from the works of LeCun et al. [4] who in 1998 presented the first successful one, named LeNet5, inspired by the ideas and previous works published by Fukushima [5]. The novelty here was to use an already known algorithm for the training of the network, named backpropagation. Essentially, backpropagation is what causes the network to learn. It is a feedback process where the output produced by the network is compared with the output it is meant to produce. The difference between them is used to modify the synaptic weights of the connections between the nodes in the network, working backwards, that is, from the output layer, through the hidden layers, back to the input layer.

After the appearance of LeNet5, research in CNNs continued progressing, although slowly. At the same time, more computing power began to be available thanks to the development of powerful parallel Graphics Processing Units (GPUs) which also became general-purpose computing tools due to the arrival of CUDA, a C-like programming language for parallel computing, especially suited for GPUs and developed by NVIDIA. It was not until 2010 that it was published one of the first implementations of a ConvNet in a GPU [6]. Thanks to the parallel processing capabilities of GPUs, the time spent for the training of CNNs could be reduced in two orders of magnitude as compared with using a CPU [7]. The latter represented a significant advance, as until then it had been not possible to study deep CNNs with high-resolution input images due to the tremendous computational power required for their training. Since then, deep neural networks have been pushing the research in machine learning with renewed interest. In particular, deep learning methodology is behind the best performing systems in machine learning applications such as self-driving cars [8], grandmasterlevel computer chess programs with self-learning capabilities [9], machine translator engines [10], speech-recognition [11] and so on.

It is indisputable that deep neural networks are one of today's hot topics in the research field of artificial intelligence. The potential for possible applications is clearly growing by the day and companies like Google, Facebook and Microsoft are investing a considerable amount of resources in the development of new products and exploring different hardware architectures that can take over GPUs. As an example, Intel recently announced the release of its Neural Network Processor (NNP) [12] that will compete with Google's Tensor Processing Units (TPUs) [13], both new custom ASIC chips made specifically for running deep neural networks. Given the above-stated background, the main motivation behind this thesis work is twofold: to gain insight into the mechanisms of artificial learning processes, and to bring together one of the more exciting fields in today's research with the aspiration to develop applications that can contribute to society.

### 1.2 Project Goals and Main Challenges

The aim of this Master's thesis is to design and implement a hardwareaccelerated convolutional neural network for the recognition of human sign language. The system should be able to recognise the different hand positions corresponding to each of the letters of the sign language alphabet. The purpose is to endow the system with the ability to interpret fingerspelling which is a method of spelling words just by using hand gestures.

In a first version, the input images are previously preprocessed and fed to the neural network as a predetermined sequence of static images. In a more elaborated version, the user can provide the input by means of a digital camera, and the video stream of images is captured and analysed by the neural network.

To simplify things, the sign language of choice is preferably the Swedish sign language (*Svenskt teckenspråk* or STS) because it is one-handed when used for fingerspelling (in opposition, for instance, to the British system that requires the two hands). It has a total of 29 positions, and most of them are static except for the distinctive vowels a,  $\ddot{a}$  and  $\ddot{o}$  that require additional hand motion.

The system's goal is to be able to recognise and translate STS into a written text message, thus the communication works only in one direction. A possibility to be explored in a future stage is to transform the system into a translation node allowing the communication in both directions between two users.

The main challenges identified *a priori* for the realisation of the project encompass different issues like the following:

- Selection of the proper CNN topology to perform the intended task.

- Selection of the proper hardware platform to implement the neural network.

- Efficient hardware implementation of the algorithm with particular attention to the on-chip memory limitations.

- Efficient number representation with minimal impact in the network's inference accuracy.

- Build a training dataset as large as possible from a broad group of volunteers in order to obtain a trained model with the highest prediction accuracy.

### 1.3 Approach and Methodology

Regarding the suitable hardware platforms, while GPU architecture is remarkably like that of a neural network, an FPGA implementation is ideal due to its compatibility with the high level of parallelism existent in artificial neural networks. The limiting factor of such parallelism is the possible lack of on-chip memory and the memory bandwidth causing bottlenecks when moving data across physical chip boundaries. Furthermore, the option of an FPGA seems more fitted than an ASIC for the implementation of a hardware-accelerated CNN for prototyping purposes.

For the training of the network, a compelling approach that is known as *transfer learning* is the preferred option. This method takes the computational model of a ConvNet that has been already pretrained on a related task, preferably with the help of an extensive dataset. Then, the output layer or *classifier* is removed and replaced by another one that fits the number of categories required for the new task. Finally, the modified network is retrained with the new dataset to fine-tune the weights by means of *backpropagation*. The obtained new weights can be either hard-coded or read from external memory by the hardware version of the neural network implemented in the FPGA.

Finally, the following are additional aspects to be considered regarding the FPGA implementation of a neural network that one can find in the related literature:

- 1. Data types and bit-width. Floating-point operations are not natively supported in most of FPGAs and its implementation adds computational complexity. So, the alternative is to use fixed-point arithmetic, much more straightforward and less resource consuming. Regarding the number of bits needed to represent the network weights, neither a broad dynamic range nor very high precision is needed. Because the weights obtained during the training phase are represented in floating-point format, conversion to fixed-point format is required when transferring these weights to the FPGA. By reducing the bitwidth, it is also reduced the size of the computation units, allowing more operators within the same area of logic. According to Guo *et al.* [14], 8-bit is the limit to ensure negligible accuracy loss although very high-performance designs can be even achieved by using binary weights (1 bit-width), as reported in [15] at the expense of accuracy loss.

- 2. All-convolutional network approach. Neural networks that consist only of convolutional layers are called *all-convolutional* networks. Making use of this design strategy results in a more simpler design and saves FPGA resources mainly in two ways: first, all-convolutional networks need less memory bandwidth since they do not contain any fully-connected layers (without the latter, there is no need to load a new weight for every single MAC operation). Second, pooling layers can also be eliminated from the network; pooling operations are periodically inserted between successive convolutional layers to perform down-sampling of the previous layer output, hence reducing the number of parameters and computation in the network. However, as demonstrated by Springenberg in a recent publication [16], adding pooling operations in a network does not always improve the CNN performance. Instead, it seems that if the network is large enough relative to the dataset that it is being trained on, it can learn all the necessary features and its invariants just with convolutional layers.

3. Efficient convolution operations. Convolutional layers make extensive use of concurrent multiply-accumulate units (MAC units). An efficient way to implement the convolution operation may be using parallel computing structures like *systolic arrays*, as proposed by Kung [17]. It is efficient because exploits locality: all operand data and partial results are stored within the processor array itself, and there is no need for any memory access during each operation. Each of the processing elements in the array performs its computation as soon as all the required data is available, and when finished, the resulting data is propagated on to its neighbours, with no need of synchronism with a global clock.

# **Basic Concepts**

First things first. This chapter covers the basic foundations and concepts that will help the reader to understand how a neural network works, its building blocks and different types of network structures or topologies. Furthermore, the learning algorithm used by neural networks to learn from a set of input examples is also explained. And finally, it introduces ZynqNet, the neural network topology that has been implemented in the hardware accelerator.

### 2.1 Foundations of Artificial Neural Networks

#### Neurons

Many of the terminology used for neural networks is borrowed from the field of neuroscience which is not a surprise at all as the idea behind neural networks is to try to solve complex problems by mimicking the human brain structure. Of course, even the simplest brain of the humble fruit-fly still presents an organisational complexity far from being replicated by any artificial neural network developed by humans nowadays. Living brain cells present complex behaviours which are not yet fully understood so the concept of *neuron* in the context of artificial neural networks is just an approximation of the functionality of a real biological neuron.

Hereby, in this context, a neuron is just a computational node with one or more numerical data inputs and a single output. This output is broadcasted, therefore allowing neurons to be interconnected with other neurons in the fashion of super-structures known as *layers*. Each neuron performs the linear combination of its weighted inputs, that is, it sums all of the inputs, each one previously multiplied by its corresponding constant, also known as *weight*. An additional extra term, the *bias*, is added to the final sum of weighted inputs. The purpose of adding the bias is to work as an offset value, and this is better understood after reading the next paragraphs.

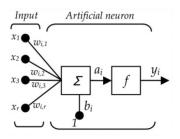

**Figure 2.1:** Representation of an artificial neuron with multiple inputs. The bias  $b_i$  is added to the linear combination of the neuron weighted inputs  $x_1, x_2, ...x_r$  and the obtained sum  $a_i$  is then used as the input parameter of the activation function f to generate the neuron output  $y_i$  (Source: derived from Tanikić and Despotović, 2012 [18]).

By definition, neurons are non-linear units, and this is a valuable property a neuron must have in order to be able to interpret non-linear real-world data. The latter is achieved by applying a non-linear function, also known as *activation* function, to the linear combination of weighted input. By extension, neurons are also referred to as *activations*, and it is a term often used in the field. Figure 2.1 is a representation of an artificial neuron as described above.

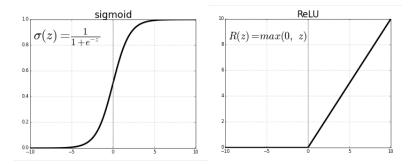

Figure 2.2: Graphs for the sigmoid and the ReLU functions.

Sigmoid functions have been used in the past as activation functions when modelling neural networks. They have a characteristic S-shape, and the output of these functions tends to saturate when the input reaches certain levels. Typical examples of sigmoid functions are the hyperbolic tangent, tanh(z) or the logistic function,  $1/(1+e^{-z})$ . More recently, sigmoid functions have been abandoned as they proved very difficult to train due to its computational complexity and have been replaced by a much more popular and still effective activation function known as ReLU defined as f(z) = max(0, z). It states that the output of the activation function will be zero for negative values (inactive) or the identity function for positive values of the linear combination of the inputs.

The ReLU function is a much simpler, elegant solution, and very cheap to implement in hardware. Essentially, sigmoid functions as well as the ReLU function, aim to imitate the behaviour of the biological neurons by transiting from an inactive state to an active state when the input signals reach a certain threshold level.

Sigmoids belong to a larger family of functions known as *discriminant* functions, as it squishes or maps the inputs into one of two possible values (-1, +1) or (0, +1) depending on the sigmoid function of choice. Due to this property, the neural network can be modelled as a decision tree providing different outputs based on the value of its inputs.

In connection with the activation function, the purpose of the *bias* term is to shift the activation output in order get better fitting between the prediction and the input data. During the training phase of the neural network, both the bias and the weights are refined in each iteration, achieving better fitting and providing the neuron with the capability of learning. Very often weights and bias are also referred to as the *trainable parameters* of the network.

#### Layers

As mentioned in the previous section, neurons are grouped in bigger structures named *layers*. Typically, a neural network consists of an input layer, an output layer and one or more layers in between also known as *hidden* layers. The latter have no direct connection with the outside world (hence the name "hidden"). The hidden layers are, in fact, the source for the ability of the neural network to interpret non-linearities in the input data. Without hidden layers, the output is directly connected to the inputs, and its value corresponds to a linear combination of such inputs. Hence, this type of network would be limited to be used only in linear decision problems, such as linear classifiers.

By adding hidden layers, with its corresponding neurons performing nonlinear activations, the capabilities for problem-solving of the neural network become greatly enhanced. With the proper training, neurons grouped in the same layer get specialised at looking to some unique features in the input data. For instance, in a neural network performing image recognition, each layer is engaged in extracting specific features from the previous layer, such as edges, shades or colours. What precisely a convolutional neural network considers to be a significant feature is defined while learning.

**Figure 2.3:** Example of a neural network without hidden layers used in a binary classification problem (left) versus a neural network with hidden layers performing as a non-linear classifier (right).

#### Fully-Connected and Convolutional Layers

Depending on the way neurons are connected to other neurons from the adjacent layers, the latter can be classified as *fully-connected* layers or *convolutional* layers, although convolutional layers are a subset of the fully-connected ones. On a *fully-connected layer*, each neuron is connected to all of the other neurons in the previous layer. An example of a very popular neural network with this type of architecture is the so-called *multilayer* perceptron (Figure 2.4) that has been used in the past for image and speech recognition tasks.

Because each connection has associated its own weight, it is easy to see that in the particular case of image recognition, where the input data consist of relatively large pictures with thousands of pixels, the number of weights required by a multilayer perceptron would grow enormously. A way to deal with that is by using *convolutional layers*, where each neuron is connected to a limited number of neurons in the previous layer. Not only the number of weights gets reduced by limiting the number of connections, but all the neurons in the same layer also share the weights. That is what is known as *weight sharing* and allows to reduce the number of trainable parameters drastically, which is particularly important if the neural network is implemented on an FPGA with limited memory resources.

Figure 2.4: Diagram of a Multilayer Perceptron Network (Source: Pavlovsky, 2017 [19]).

In principle, a convolutional neural network should have the same learning capabilities than a fully-connected one. The difference is that fullyconnected layers perform a *global* operation, as they can introduce any kind of dependence derived from the input data, and convolutional layers perform a *local* operation as each neuron is *looking* at a small portion of the data in the previous layer and that is why they perform so well in image analysis tasks. That small portion of data that is being analysed is also known as the *local receptive field* or *convolution window* and the set of weights used to calculate the weighted sum is known as *kernel* or *filter*. One can think about it as applying a filter to an image by sliding it all along the pixels. Each pixel of the output image is a linear combination of the values contained in its corresponding local receptive field, which is formed by the current input pixel and its neighbouring pixels, as depicted in Figure 2.5.

Figure 2.5: 2-D discrete convolution obtained by sliding the *kernel* along the input image (Source: Intel Labs [20]).

Typically, in convolutional neural networks, a fully-connected layer is placed at the final stage of the neural network as a *classifier*, to separate the

data into the various categories. Because each of its neurons has connections to all the elements in the previous layer, they can extract any kind of relevant dependencies from the input data. The fully-connected layer is the cause for the high-level reasoning in the neural network.

#### **Activation Volumes and Feature Maps**

At this point, it is necessary to introduce the idea of *volumes* since the input data is not organised just as a two-dimensional array but in a threedimension matrix or *volume*. Let's consider an input image of size 8x8 and composed of 3 channels (Fig. 2.6), namely the standard RGB colour channels. The latter adds a new dimension to the input data, in this case, a depth of three channels, also referred as *slices*. Hence, the input data constitutes, in reality, a volume of data of size 8x8x3. It follows that the same applies to the kernel, which is not a 2-dimensional array of weights; for instance, a typical 3x3 kernel forms a volumetric filter of size 3x3x3 actually, as the kernel always has to have the same depth as the input volume.

Figure 2.6: Representing a full-colour RGB input image as a volume and applying a volumetric convolutional filter.

Following with the example, after convolving each channel of the input volume with its corresponding kernel slice, the obtained output is a set of three *feature maps*. Then, these feature maps or matrices are added together with its corresponding bias, and the final sum is passed to the activation function or ReLU. The resultant 2-D matrix is an *activation output* or *rectified feature map* obtained from the input. As might be expected, in order to extract more feature maps from the input, it just takes another different set of kernels and to convolve the input volume with them. One can generate as many features as needed, depending on different factors like the computational power, available memory or the type of input images one wants to analyse. Eventually, all these feature maps are piling up creating a 3-D volume of data again, often referred to as *activation* or *feature volume*.

#### Hyper-Parameters: Kernel Size, Stride and Padding

Complementary to the weights and the bias, which are network parameters that are refined or modified during the learning process, there is another set of parameters intrinsic to the neural network that is used to specify the structure of the layers. These parameters are known as *hyper-parameters* and are configurable values which are set before starting the training process. The main hyper-parameters of a CNN are the size of the receptive field, the kernel size, the padding, the stride length, and the dimensions of the activation volumes. Some of these hyper-parameters have been already mentioned in the previous sections, and the rest are detailed by following. There are other hyper-parameters, that are not listed here, that dictate the behaviour of the training algorithm and how it learns the parameters from the data. They are detailed in Chapter 3 which refers to the training of the CNN.

#### Kernel size

The size of the kernels that is used in the tapestry of convolutional neural network topologies available nowadays can be quite diverse. Typical sizes are 1x1, 3x3, 5x5 and 7x7. The heuristic rule for using a specific dimension relies upon the relative size of the feature that one needs to capture: the smaller the size of the feature to be extracted, the smaller the filter.

#### Stride

Another parameter to be considered is the *stride*, which refers to how the kernel slides along the input image. Typically, after performing the convolution operation on a local receptive field, the filter is shifted by one pixel, row-wise or column-wise, and placed over the next receptive field, and the process goes on until completing the output feature. The term *stride* is used to refer to the length of this displacement. It is also possible to use a shift bigger than one pixel, or *non-unity* strides, as a way to reduce the dimensionality of the activation volumes and the computational effort. For instance, a stride of 2 will produce an output with half the dimensions of the input (that is to say, the spatial dimensions of the input, height and width) with a reduction factor of 4 in the total number of elements. An interesting discussion about the heuristic motivations for using different stride values is given by Kong and Lucey [21], who demonstrate that any non-unity stridden convolution can be replaced by a unity stridden convolution without loss of performance.

#### Padding

Padding is needed to keep the dimensions of the output volumes the same size of the input volumes. The standard method is to use *zero-padding* which consists in filling with zeros around the borders of the feature maps. If no padding were applied, the spatial dimensions of the activation volumes (height and width) would be reduced after each convolution progressively, washing quickly away all the information data contained in the borders. This effect can be seen more clearly by considering the following example, where a 5x5 matrix is convolved with a 3x3 kernel. Without padding, the result is a 3x3 matrix, and attempting to convolve that matrix with another 3x3 kernel will result in a 1x1 matrix. However, if the original 5x5 matrix is padded with zeros all around the borders, the result would be another 5x5 matrix (dimensions keep the same size), and by padding this matrix again, one can perform as many 3x3 convolutions as wished.

Stride 1 with Padding

Feature Map

Figure 2.7: Example of 2-D matrix convolution with zero-padding (Source: derived from Dertat, 2017 [22]).

#### **Pooling Layers**

Another commonly used type of layer is the *pooling layer*. Its purpose is to reduce the spatial size (height and width, but not the depth) of the feature volumes, and this is achieved by inserting pooling layers along the structure of the network in a distributed way (see Figure 2.8).

Figure 2.8: 3-D representation of a convolutional neural network with pooling layers (*Source: Cord, 2017 [23]*).

Mainly there are three types of pooling: max, min and average pooling. As a matter of example, Figure 2.9 shows a typical max pooling layer, with a filter of size 2x2 and a stride of 2. It decimates every slice of the feature volume, discarding exactly 75% of the activations. The max pooling operation would, in this case, take the maximum over four elements on the receptive field delimited by the filter.

**Figure 2.9:** Example of a *max* pooling operation using 2x2 filters and stride 2 (*Source: Karpathy* [24]).

More recently, neural network topologies have shown up with a new approach, the *all-convolutional net*, consisting in to get rid of the pooling layers, based on a late paper from Springenberg *et al.* [16], who propose to discard the pooling layers in favour of an architecture that only consists of successive convolutional layers. To reduce the size of the activation volumes, they suggest the use of larger strides (typically a stride of 2) in the convolutional layers once in a while. As a matter of fact, that approach has also been implemented in Zynqnet [25], the network topology used in this project.

It is worth to mention that the ZynqNet architecture shown in Figure A.1

has only a pooling layer located at the final stage of the neural network, right after the convolutional layer *conv*10. This pooling layer performs a *global average pooling* operation that generates a flattened vector with dimension equal to the number of categories. That is an improvement also inherited from the authors of the SqueezeNet [26] architecture, who replaced the last fully-connected layer of the network with a convolutional layer and a global average pooling. The main advantage behind this modification is to reduce the memory requirements significantly, due to the vast amount of parameters associated with a fully-connected layer. That, together with the *all-convolutional net idea*, makes ZynqNet very suitable for FPGA implementations.

### 2.2 Backpropagation Algorithm

In the previous section, it was stated that during the training phase of the neural network, weights and bias are refined to get a better fitting between the obtained output and the desired output, iteration after iteration. This refinement mechanism is the one that makes possible that the neural network learns from the given examples and get the ability to generalise when later, during the test phase, is presented to new examples never seen before. This learning algorithm is known as *backpropagation* and consists in nothing more than the optimisation of a cost function, sometimes referred also as loss function. The input parameters of this function consist of all of the trainable weights and bias of the neural network, as many as hundreds of thousands, or millions. During the training phase, the examples are fed to the input layer of the neural network, and the data is propagated through the different layers all the way to the output, where the neurons on the fully-connected layer (which acts as a classifier) throw different values ranging on a specific interval. Ideally, only the output neuron which corresponds to the right category for the given input image should be active, and the rest of neurons should be inactive or zero-valued, but in reality, all of the output neurons display some value and the one with the most significant value will be the answer given by the CNN. The approach for optimising the cost function is to use the standard method of minimising the sum of the squared errors (SSE), where the errors are the difference between the actual value of each one of the output neurons and its target value. That needs to be done for all of the hundreds of thousands of training samples so, this technique takes the average of all of the SSE, and the result will be the total cost of the network that needs to be minimised.

To find out the amount of change to be applied to the weights and bias to minimise the cost function, the backpropagation algorithm calculates the gradient of the function at a given starting point. Actually, it is the *negative* of the gradient that is the vector pointing towards the local minimum. Consequently, some weights will need to be increased whereas other weights will need to be reduced. The amount of change will depend on how significant is the activation value of the neuron in the previous layer associated to that weight. Hence, the change should be proportional; the bigger the activation, the bigger the change on the weights, and vice versa, therefore reinforcing the connections between neurons that have a desired effect on the output, and dimmering the ones that not. The net effect is to reduce the error and approach the desired output to its target value.

The algorithm is computing the changes needed in the weights and bias in order to find the local minimum of the cost function, by searching for the optimal path downhill along the *cost surface*, which ideally is in the direction of the negative gradient vector, and moving along that surface in small iterative steps or *deltas*. However, it should be noted that this calculation is done for each one of the training examples. For another training example, these changes will have different values, and hence, in the end, it is necessary to do an average of all of the desired changes in order to obtain an average value that will be kind of proportional to the gradient of the cost function. The name for this technique used for the training of neural networks is known as *gradient descent*.

Given the large size of the training datasets, it takes so much computational effort to calculate each one of the steps downhill the cost surface by trying to follow the optimal path, because the algorithm is taking into account all of the training examples at once. In practice, a very handy optimisation technique to speed-up the algorithm consists of randomly shuffling the whole set of the training examples and divide it into small lots or *batches* (also called *mini-batches*). Then, the backpropagation algorithm will calculate the deltas, and the obtained gradient will not be optimal, but just an approximation, as it will depend on the pictures contained in that mini-batch. The next step will be taken by applying the algorithm in the next mini-batch and so on.

Once the algorithm goes through all the mini-batches, which is called an *epoch*, the algorithm reshuffles the training examples and creates new mini-batches. This technique is extensively used nowadays and is known as Stochastic Gradient Descent (SGD). As shown in Figure 2.10, the path followed by the algorithm in order to find the local minimum is not a smooth optimal path but rather a random path, although oscillating around the optimal one.

At this point, a couple of question arises: How likely is it for the SGD

algorithm not to get trapped in a saddle point<sup>1</sup>? If not, is the local minimum found by the SGD algorithm the best one among all of the minima contained in the cost surface?

Figure 2.10: Stochastic Gradient Descent algorithm searching for the local minimum (Source: Goh, 2017 [27]).

Given the fact that the cost function is a non-convex function in a high-dimensional space, finding its absolute global minimum can be just a daunting computational task. One can visualise the loss function as a surface populated with thousands of local minima, maxima and even worse, saddle points were the SGD algorithm can get stuck. An analytic answer providing mathematical proof to this question is given by LeCun *et al.* [28] who demonstrate that while multilayer networks present numerous local minima, they are relatively easy to find, and they are all more or less equivalent in terms of quality when trying to minimise the cost function. Complementary, for the gradient descent algorithm may converge on a saddle point and spoil further optimisation of the cost function, a recent work from Lee *et al.* [29] demonstrates that the gradient descent can overcome this problem with random initialisation of parameters of the cost function (bias and weights), and the algorithm will almost surely converge to a local minimum.

Given the works mentioned above and prior experiences provided by numerous practitioners, it can be concluded that the backpropagation algorithm using the stochastic gradient descent is so far a mature and proven method for the training of convolutional neural networks.

<sup>&</sup>lt;sup>1</sup>A saddle point is a singular point on the surface of a multivariable function where all the partial derivatives in the orthogonal directions are equal to zero, but the saddle point is neither a local maximum nor a local minimum of the function.

## 2.3 Neural Networks are Universal Approximators

Neural networks are the ultimate regression algorithm. That is an attractive and alternative approach for understanding what hides behind such fancy name of *neural networks*. One can look at them as universal function approximators, in the same way as the Taylor and Fourier series are function approximation techniques. The mathematical proof for this statement relies on the *universal approximation theorem* proven by Cybenko [30], who demonstrated that feed-forward<sup>2</sup> neural networks with only a single hidden layer containing a finite number of neurons can approximate any continuous function. Cybenko demonstrated the theorem for sigmoid activation functions, but the theorem can be extended to other nonlinear activation functions, provided they are continuous and bounded.

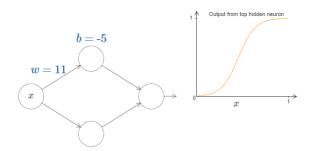

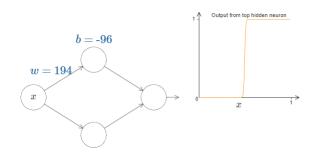

The following is an interesting and straightforward graphical demonstration provided by Nielsen [31] in his online inter-active book on how a neural network can compute any arbitrary function. Let's consider the most simple case, represented in Figure 2.11, namely a single input neuron, a single output neuron and a hidden layer with two neurons. The activation function in the hidden neurons is a sigmoid. The graph in the right accounts only for the effect of the top hidden neuron in the output. Initially, the parameters w (weight) and b (bias) associated with that neuron are arbitrary values, and the output still resembles a sigmoid curve. By changing those values, as shown in Figure 2.12, the output becomes almost a step-function.

**Figure 2.11:** Single-input, single-output neural network with a 2-neuron hidden layer. The network output corresponds to the contribution of the top hidden neuron alone *(Source: Nielsen, 2015 [31])*.

The b parameter controls the amount of shifting in the horizontal axis, and the w parameter controls how steep the step-like function is.

<sup>&</sup>lt;sup>2</sup>Feed-forward neural networks are a type of networks where there are no feedback connections. Convolutional neural networks belong to this group.

Figure 2.12: Network output re-shaped like a step-function by modifying parameters w and b (Source: Nielsen, 2015 [31]).

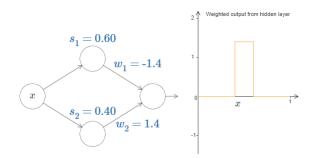

In Figure 2.13 the output reflects the combined effect of both hidden neurons. The amount of shifting for each sigmoid function has been replaced now by the bias parameters s1 and s2, and two extra weights, w1 and w2have been added. The output is a linear combination of the activation functions of both hidden neurons, where w1 and w2 are the coefficients. These two parameters have the same magnitude but opposite sign, and this produces a rectangular function at the output. The height of this rectangular pulse is proportional to the magnitude of w1 and w2, and the difference between s1 and s2 gives the width.

**Figure 2.13:** The network output corresponds to the linear combination of both hidden neuron activations (*Source: Nielsen, 2015* [31]).

The next step is to add more pairs of neurons to the hidden layer in order to concatenate a series of rectangular pulses in the output, as shown in 2.14. Now, the values inside the circles representing each one of the hidden neurons correspond to the bias value, the before mentioned s parameter, and again they correspond to the amount of shifting given to the sigmoid function delimiting the rectangular pulses. Also, for each couple of hidden neurons, there is associated a h parameter which corresponds to the height of the rectangular pulses.

Figure 2.14: Approximation of an arbitrary function by adding additional neurons in the hidden layer (Source: Nielsen, 2015 [31]).

At this point, it should be clear how by adjusting these parameters it is possible to approximate any arbitrary function, like the blue curve in the output plot, to a reasonable deviation degree, and also explains why neural networks perform so well as non-linear classifiers, as mentioned in earlier sections.

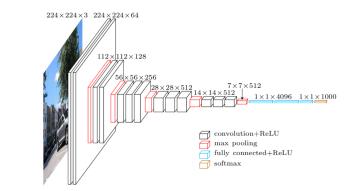

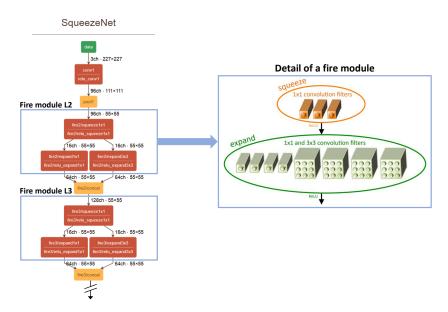

## 2.4 Example of a Convolutional Neural Network: ZynqNet

ZynqNet [25] is a modified version of a very recent architecture known with the name of SqueezeNet [26]. The latter was released in 2016, and the most remarkable trait of this CNN is that it can obtain the same level of accuracy of other networks, but by using a factor x50 fewer parameters, which makes it very suitable for mobile applications. Although SqueezeNet is already a highly optimised architecture, ZynqNet pushes its design one step forward and provides a series of improvements that make it more convenient for FPGA implementations.

Table 2.1 is a description of the ZynqNet architecture, layer by layer,

together with their associated hyper-parameters. However, the architecture of both ZynqNet and SqueezeNet is best envisaged using Netscope [32], a web-based tool developed for visualising and analysing convolutional neural network architectures. A visual representation of ZynqNet generated by Netscope is illustrated in Figure A.1. In short, the core component of SqueezeNet/ZynqNet is the so-called *fire module*, which can be split into two layers, a *squeeze layer* followed by an *expansion layer*:

- 1. the squeeze layer consists of a 1x1 matrix convolution; although the receptive field is just 1x1, one should note that the main effect of this operation is on the third dimension, or depth, of the input volume, where the depth is equal to the number of input channels. Hence, the 1x1 convolution results in the combination of all the input channels into one, thus reducing the depth of the activation volume effectively.

- 2. the *expansion layer*, in reality, combines two parallel convolutional layers that use different kernel sizes (1x1 and 3x3) and concatenates both results into a single activation volume. The 1x1 convolutions are not fitted to detect spatial structures, but as mentioned above, they combine the channels in different ways. However, the 3x3 convolutions can, indeed, detect structures and patterns in the images. Thus, by combining different kernel sizes, one can obtain a much more expressive model and, at the same time, reduce the number of parameters needed.

Figure 2.15: Detail of the fire module in SqueezeNet (Source: derived from Netscope CNN Analyzer [32] and Iandola, 2016 [26]).

SqueezeNet uses 8 of these fire modules (Figure 2.15) and a couple of convolutional layers as an input and output layer. It also completely avoids the use of fully-connected layers, which require large amounts of parameters. Instead, SqueezeNet uses four pooling layers (three max and one average) distributed along the network architecture, which does not require any weights.

| Layer name       | Туре         | Kernel | Stride | CH in | WxH in           | CH out | WxH out |

|------------------|--------------|--------|--------|-------|------------------|--------|---------|

| conv1            | Convolution  | 3x3    | 2      | 3     | $256 \times 256$ | 64     | 128x128 |

| fire2/squeeze3x3 | Convolution  | 3x3    | 2      | 64    | $128 \times 128$ | 16     | 64x64   |

| fire2/expand1x1  | Convolution  | 1x1    | 1      | 16    | 64x64            | 64     | 64x64   |

| fire2/expand3x3  | Convolution  | 3x3    | 1      | 16    | 64x64            | 64     | 64x64   |

| fire3/squeeze1x1 | Convolution  | 1x1    | 1      | 128   | 64x64            | 16     | 64x64   |

| fire3/expand1x1  | Convolution  | 1x1    | 1      | 16    | 64x64            | 64     | 64x64   |

| fire3/expand3x3  | Convolution  | 3x3    | 1      | 16    | 64x64            | 64     | 64x64   |

| fire4/squeeze3x3 | Convolution  | 3x3    | 2      | 128   | 64x64            | 32     | 32x32   |

| fire4/expand1x1  | Convolution  | 1x1    | 1      | 32    | 32x32            | 128    | 32x32   |

| fire4/expand3x3  | Convolution  | 3x3    | 1      | 32    | 32x32            | 128    | 32x32   |

| fire5/squeeze1x1 | Convolution  | 1x1    | 1      | 256   | 32x32            | 32     | 32x32   |

| fire5/expand1x1  | Convolution  | 1x1    | 1      | 32    | 32x32            | 128    | 32x32   |

| fire5/expand3x3  | Convolution  | 3x3    | 1      | 32    | 32x32            | 128    | 32x32   |

| fire6/squeeze3x3 | Convolution  | 3x3    | 2      | 256   | 32x32            | 64     | 16x16   |

| fire6/expand1x1  | Convolution  | 1x1    | 1      | 64    | 16x16            | 256    | 16x16   |

| fire6/expand3x3  | Convolution  | 3x3    | 1      | 64    | 16x16            | 256    | 16x16   |

| fire7/squeeze1x1 | Convolution  | 1x1    | 1      | 512   | 16x16            | 64     | 16x16   |

| fire7/expand1x1  | Convolution  | 1x1    | 1      | 64    | 16x16            | 192    | 16x16   |

| fire7/expand3x3  | Convolution  | 3x3    | 1      | 64    | 16x16            | 192    | 16x16   |

| fire8/squeeze3x3 | Convolution  | 3x3    | 2      | 384   | 16x16            | 112    | 8x8     |

| fire8/expand1x1  | Convolution  | 1x1    | 1      | 112   | 8x8              | 256    | 8x8     |

| fire8/expand3x3  | Convolution  | 3x3    | 1      | 112   | 8x8              | 256    | 8x8     |

| fire9/squeeze1x1 | Convolution  | 1x1    | 1      | 512   | 8x8              | 112    | 8x8     |

| fire9/expand1x1  | Convolution  | 1x1    | 1      | 112   | 8x8              | 368    | 8x8     |

| fire9/expand3x3  | Convolution  | 3x3    | 1      | 112   | 8x8              | 368    | 8x8     |

| conv10/split1    | Convolution  | 1x1    | 1      | 736   | 8x8              | 512    | 8x8     |

| conv10/split2    | Convolution  | 1x1    | 1      | 736   | 8x8              | 512    | 8x8     |

| pool10           | Avg. Pooling | 8x8    | -      | 1024  | 8x8              | 1024   | 1x1     |

| loss             | Softmax      | -      | -      | 1024  | 1x1              | 1024   | 1x1     |

By contrast, ZynqNet does some optimisation on the SqueezeNet architecture:

Table 2.1: ZynqNet CNN architecture. Description of layers and hyper-parameters.

• SqueezeNet uses a 7x7 kernel in conv1, the first layer; this is typical

in many CNNs that use large kernels in the very first convolutional input layer. ZynqNet replaces the 7x7 kernel by a 3x3, reducing the number of MACC operations by a 5.4 factor while still maintaining almost the same final accuracy (it only drops by a 0.8%).

- ZynqNet sticks to the *all-convolutional-network* design principle, and does it so by replacing each one of the max pooling layers (together with its subsequent 1x1 squeeze layer) by a 3x3 convolution with a stride of 2. Although this modification increases the number of parameters and MACC operations, it results in a very consistent and unified architecture plus an increase of the final accuracy of 1.5 % [25]. Only the average pooling layer is left in the last stage of the network for classifying purposes.

- ZynqNet implements a design where all the spatial dimensions of the feature volumes are rounded to the nearest power of 2 (height, width and number of channels) which assures that multiplications or divisions, needed when accessing the feature elements from the FPGA block RAM, are done with inexpensive shift operations.

Chapter 3

# Training of a Deep Neural Network

This chapter covers different aspects related to the training process of the neural network model. It gives an overview of the training framework and the hardware details of the workstation used for the training. It also explains the making of the training image dataset and the training-related basic concepts such as data augmentation, overfitting and transfer learning. Furthermore, a description of the most relevant training hyper-parameters is given, and a summary of the training results is presented.

Finally, it brings some insight about an advantageous post-training technique known as *network quantisation* that allows for further size reduction of the network and its implementation onto small embedded platforms by using dynamic fixed-point representation.

## 3.1 Training Framework

The NVIDIA Deep Learning GPU Training System (DIGITS) [33] is the software used for the training of the neural network model used in this thesis work. DIGITS is an open-source deep learning software for image classification; it is not a training framework as such but rather a *wrapper* for the most popular training frameworks used nowadays, namely Caffe [34], Torch [35] and TensorFlow [36]. All the latter are back-ends that integrate open-source computer vision GPU libraries (OpenCV).

DIGITS provides a graphical web-based interface instead of dealing with the command line as it is typically the case with the above-mentioned frameworks. By doing so, it facilitates to monitor and manage neural network training jobs, and analyse accuracy and loss in real time. The primary goal is to rapidly train the proposed model from large image datasets to make highly accurate image classifications. A very first step is obviously to create a large enough dataset which is discussed in the following sections.

The computations performed by the training framework consist in the optimisation of the cost function described previously in Section 2.2 using the backpropagation algorithm together with the stochastic gradient descent (SGD). By this means, the neural network model acquires the feature hierarchies from the raw training data and gains the ability to infer real-world data. This capability is what is known as *machine learning*.

#### Overview of a GPU-based Training System

The training system (DIGITS) has been installed on a standard desktop computer running on a Linux distribution (CentOS). An NVIDIA GPU was added plus a new power supply, to power the GPU properly. The following is a description of the hardware that can be found in the computer used for the training of the neural network model:

| Part         | Model Description                           |

|--------------|---------------------------------------------|

| Mother board | ASUS P8Z77-M PRO                            |

| CPU          | Intel i7-2600K (3.4 GHz)                    |

| GPU          | NVIDIA GeForce GTX 1080 Ti MSI Aero OC 11GB |

| RAM          | Corsair XMS3 4x16 GB (1.3 GHz)              |

| HDD          | Western Digital WD10EZRX (1 TB, 6 GB/s)     |

| Power Supply | Corsair Builder Series CX600 V2 (600Watt)   |

Table 3.1: List of the hardware installed in the computer used as training station.

As illustrated in Table 3.1, the training station makes use of one GPU only which is enough to run a training job in just a few minutes. Most likely, for a much more extensive training dataset than the one used for this project, more GPU computation power is required otherwise so that the training time can be kept at reasonable levels.

## 3.2 Making of a Training Dataset

As already stated in the preliminaries, the objective is that the neural network can recognise human sign language, specifically the Swedish hand alphabet used for *fingerspelling*, which is used in sign language to spell out names of people and places for which there is not a sign. The Swedish hand alphabet is illustrated in Figure 3.1. It is composed of 29 different hand poses, of which three of them correspond to the distinctive vowels a,

$\ddot{a}$  and  $\ddot{o}$ . It should be noted that these vowels are accompanied by a whole hand movement in the direction indicated by the arrows in the picture. For that reason, they have been excluded from the training as they are not static hand positions. Hence, it is 26 signs that the CNN should be able to recognise.

Figure 3.1: Swedish hand alphabet (Source: Ene, 2015 [37]).

In order to have a better algorithm that can take better decisions, it should learn from data that reflects the variety of the real world. For that reason, the larger the training dataset, the better. But not only quantity matters: a dataset with a million different cars would be useless if all of them were facing to the left in the picture. Therefore, the dataset should provide different points of view of the same object, and this is achieved by using *data augmentation* techniques.