# Image Processing Architectures for Binary Morphology and Labeling

Hugo Hedberg

Lund 2008

The Department of Electrical and Information Technology Lund University Box 118, S-221 00 LUND SWEDEN

This thesis is set in Computer Modern 10pt, with the  $IAT_EX$  Documentation System using Pontus Åströms thesis template.

Series of licentiate and doctoral thesis No. 2 ISSN 1654-790X

© Hugo Hedberg 2008 Printed in Sweden by Tryckeriet E-huset, Lund. March 2008

### Abstract

Conventional surveillance systems are omnipresent and most are still based on analog techniques. Migrating to the digital domain grants access to the world of digital image processing enabling automation of such systems, which means extracting information from the image stream without human interaction. The resolution, frame rates, and functionality in these systems are continuously increasing alongside the number of video streams to be processed. The sum of all these parameters imposes high data rates and memory bandwidths which are impossible to handle in pure software solutions. Therefore, accelerating key operations and complex repetitive calculations in dedicated hardware architectures is crucial to sustain real-time performance in future advanced high resolution and frame rate systems.

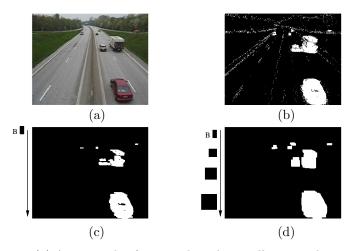

To achieve this goal, this thesis presents four architectures of hardware accelerators to be used in real-time embedded image processing systems, implemented as an FPGA or ASIC. Two morphological architectures performing binary erosion or dilation, with low complexity and low memory requirement, have been developed. One supports static, and the other locally adaptive flat rectangular structuring elements of arbitrary size. Furthermore, a high-throughput architecture calculating the distance transform has also been developed. This architecture supports either the city-block or chessboard distance metric and is based on adding the result of parallel erosions. The fourth architecture performs connected component labeling based on contour tracing and supports feature extraction. A modified version of the morphological architecture supporting static structuring elements, as well as the labeling architecture, has been successfully integrated into a prototype of an automated digital surveillance system for which implementation aspects are presented. The system has been implemented and is running on an FPGA based development board using a CMOS sensor for image acquisition. The prototype currently has segmentation, filtering, and labeling accelerated in hardware, and additional image processing performed in software running on an embedded processor.

In loving memory of my father

## Contents

|   | Abstract                                                                                                                                | iii                              |

|---|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|   | Acknowledgment                                                                                                                          | xi                               |

|   | Preface                                                                                                                                 | xiii                             |

|   | List of Acronyms                                                                                                                        | xv                               |

|   | List of Definitions and Mathematical Operators                                                                                          | xvii                             |

| 1 | Introduction1.1Research Project1.2Main Contribution and Thesis Statement1.3Thesis Overview                                              | 1<br>2<br>3<br>3                 |

| 2 | Digital System Design2.1Implementation Platform2.2Design Flow2.3Real-time Processing2.4Low Power Circuit Design2.5Low Power FPGA Design | <b>9</b><br>12<br>15<br>16<br>17 |

| 3 | Digital Image Processing         3.1 Digital Image Acquisition         3.1.1 Human Vision                                               | <b>19</b><br>19<br>20            |

vii

|   |     | 3.1.2 Sensor Techniques                                       |   |

|---|-----|---------------------------------------------------------------|---|

|   |     | 3.1.3 CCD versus CMOS Sensors                                 | 2 |

|   |     | 3.1.4 Raster Scan Order                                       | ł |

|   | 3.2 | Fundamental Pixel to Pixel Based Relationships                | ł |

|   |     | 3.2.1 Neighborhood                                            | ł |

|   |     | 3.2.2 Connectivity                                            | ) |

|   |     | 3.2.3 Clusters                                                | ) |

|   |     | 3.2.4 Spatial Filters                                         | ) |

|   | 3.3 | Basic Set Theory Definitions                                  | , |

|   |     | 3.3.1 Reflection                                              | , |

|   |     | 3.3.2 Translation                                             | , |

|   |     | 3.3.3 Minkowski Addition and Subtraction                      | ) |

|   | • • |                                                               |   |

| 4 |     | phology 31                                                    |   |

|   | 4.1 | Structuring Element                                           |   |

|   | 4.2 | Erosion and Dilation                                          |   |

|   |     | 4.2.1 Erosion                                                 |   |

|   |     | 4.2.2 Dilation                                                |   |

|   | 4.3 | Opening and Closing                                           |   |

|   | 4.4 | Structuring Element Decomposition                             |   |

|   | 4.5 | Duality with Respect to Complementation                       |   |

|   | 4.6 | Handling the Borders                                          |   |

| 5 | Lab | eling 41                                                      |   |

| - | 5.1 | Algorithms                                                    |   |

|   | 5.2 | Sequential Local Operation Based Algorithms                   |   |

|   | 5.3 | Resolving Label Collisions                                    | ; |

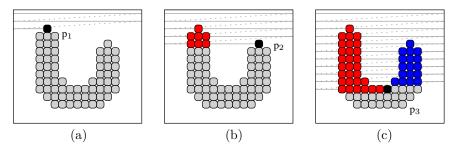

|   | 5.4 | Contour Tracing Based Algorithms                              |   |

|   |     | 5 5                                                           |   |

| I |     | -Complexity Binary Morphology with Flat Rectangular Structur- |   |

|   | ing | Elements 51                                                   |   |

|   | 1   | Introduction                                                  |   |

|   |     | 1.1 Previous Research                                         |   |

|   | 2   | Architecture                                                  |   |

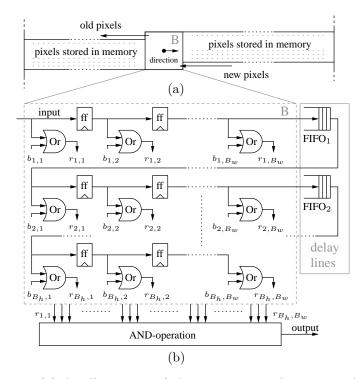

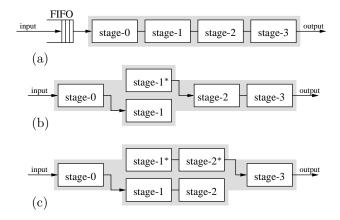

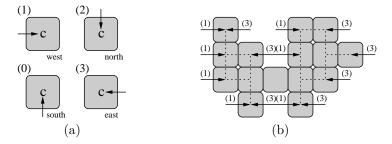

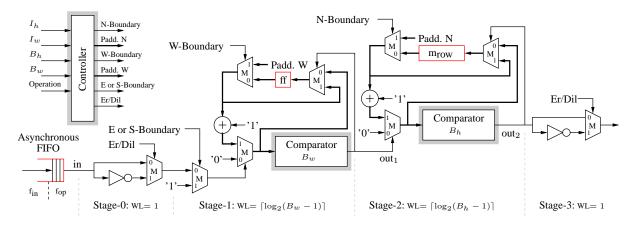

|   |     | 2.1 Delay-line Architecture                                   |   |

|   |     | 2.2 Low Complexity Architecture                               |   |

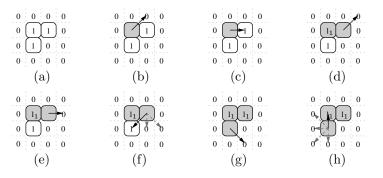

|   |     | 2.3 Stall-Free Low Complexity Architecture                    |   |

|   |     | 2.4 Extended Morphological Operations                         |   |

|   | 3   | Implementation                                                |   |

|   |     | 3.1 Memory Architecture                                       |   |

|   | 4   | Results and Performance                                       | , |

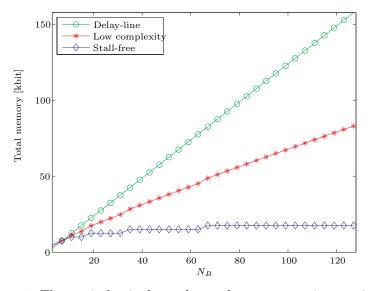

|    |       | 4.1      | Computational Complexity                                 | 66  |

|----|-------|----------|----------------------------------------------------------|-----|

|    |       | 4.2      | Execution Time                                           | 66  |

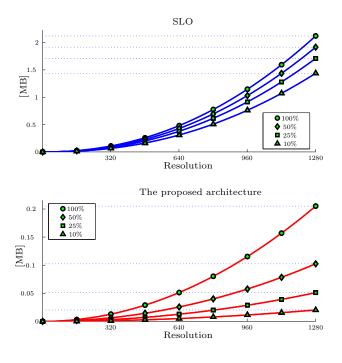

|    |       | 4.3      | Memory Requirement                                       | 67  |

|    | 5     | Conclu   | sion                                                     | 70  |

| П  | Bina  | ry Mor   | phology with Locally Adaptive Structuring Elements: Al-  |     |

|    | gorit | hm and   | d Architecture                                           | 71  |

|    | 1     | Introdu  | lction                                                   | 73  |

|    |       | 1.1      | Previous Research                                        | 74  |

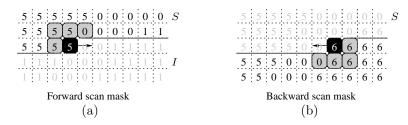

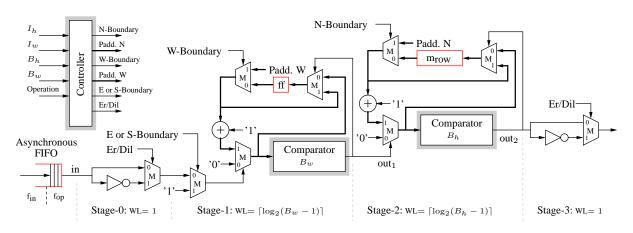

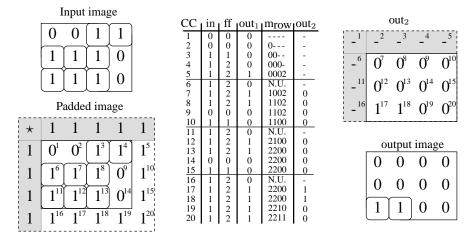

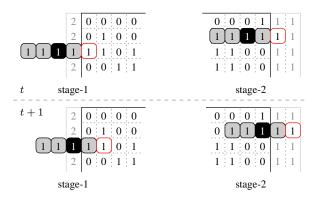

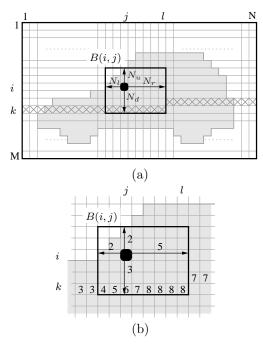

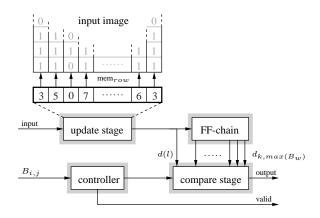

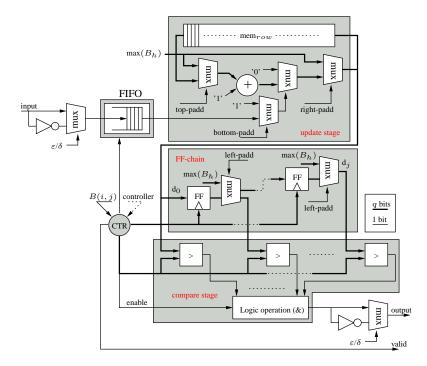

|    | 2     | Algorit  | hmic Issues                                              | 75  |

|    | 3     | Algorit  | hm Description                                           | 78  |

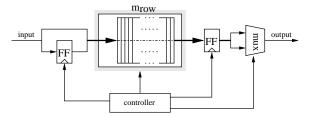

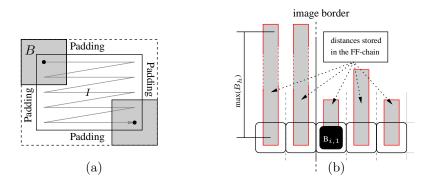

|    | 4     | Archite  | ecture                                                   | 82  |

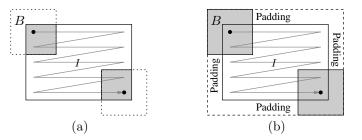

|    |       | 4.1      | Handling the Borders                                     | 84  |

|    |       | 4.2      | Coding the Structuring Element Size                      | 85  |

|    |       | 4.3      | Memory Requirements                                      | 85  |

|    | 5     | Implem   | nentation Results and Performance                        | 87  |

|    | 6     | Conclu   | sion                                                     | 89  |

| ш  | An A  | Archited | cture for Calculation of the Distance Transform Based on | I   |

|    | Mat   | hematio  | cal Morphology                                           | 91  |

|    | 1     | Introdu  | lction                                                   | 93  |

|    | 2     | Geome    | try Metrics                                              | 94  |

|    |       | 2.1      | Previous Research                                        | 96  |

|    | 3     | Archite  | ecture                                                   | 96  |

|    |       | 3.1      | Execution Time                                           | 98  |

|    |       | 3.2      | Memory Requirement                                       | 98  |

|    | 4     | Implem   | nentation Results and Performance                        | 100 |

|    | 5     | Conclu   | sion                                                     | 101 |

| IV | Impl  | ementa   | ation of Labeling Algorithm Based on Contour Tracing     |     |

|    | with  | Featur   | re Extraction                                            | 103 |

|    | 1     | Introdu  | lction                                                   | 105 |

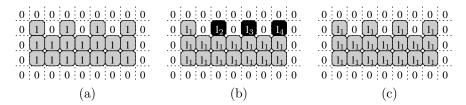

|    | 2     | Hardwa   | are Aspects of Labeling Algorithms                       | 105 |

|    |       | 2.1      | Complexity                                               | 105 |

|    |       | 2.2      | Memory Requirements                                      | 106 |

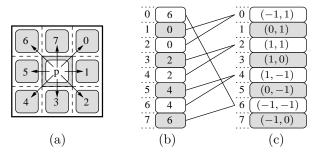

|    |       | 2.3      | Memory Accesses                                          | 108 |

|    |       | 2.4      | Execution Time                                           | 110 |

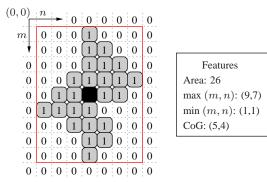

|    |       | 2.5      | Feature Extraction                                       | 110 |

|    | 3     | -        | hm Evaluation                                            | 113 |

|    | 4     | Implem   | nentation                                                | 114 |

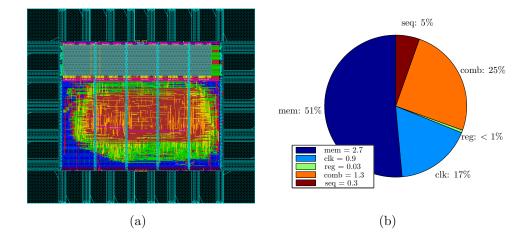

|    | 5     |          | and Performance                                          | 116 |

|     | Embedded Real-Time Surveillance System: Implementation a |

|-----|----------------------------------------------------------|

| Eva | lluation                                                 |

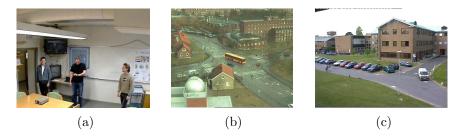

| 1   | Introduction                                             |

|     | 1.1 Systems of Today                                     |

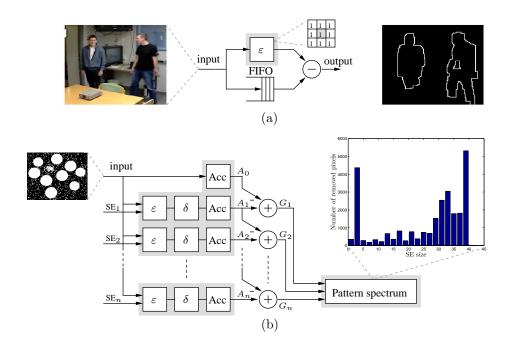

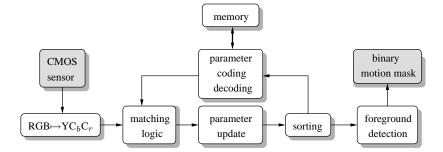

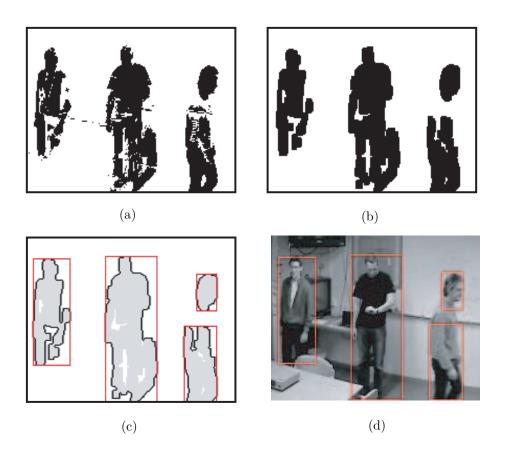

| 2   | Segmentation                                             |

|     | 2.1 Algorithm Formulation                                |

|     | 2.2 Color Space Transformation                           |

|     | 2.3 Segmentation Architecture                            |

|     | 2.4 Wordlength Reduction                                 |

|     | 2.5 Pixel Locality                                       |

| 3   | Morphology                                               |

|     | 3.1 Morphology Architecture                              |

| 4   | Labeling                                                 |

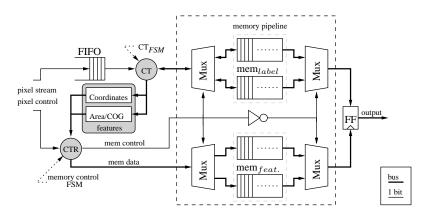

|     | 4.1 Labeling Architecture                                |

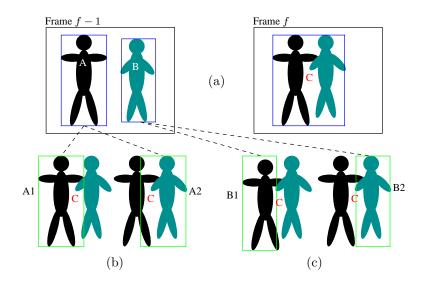

| 5   | Tracking                                                 |

| 6   | System Implementation and Performance                    |

|     | 6.1 Bottlenecks                                          |

Conclusion

153

### Acknowledgment

I would like to express my gratitude to all the people who have inspired me and contributed to the writing of this thesis. What a journey this has been! From nightswimming in the crystal-clear waters of lake Geneva, to strolling the beaches of sunny California, and experiencing the beautiful Fiji islands, I feel privileged to have been given the possibility of gathering an amazing collection of memories from all the traveling, the discussions, and hard work, that has taken place during these years.

First of all, I would like to express my deepest gratitude to my supervisor associate professor PhD Viktor Öwall. Your guidance and helping hand throughout my years at the department made it all possible. Not to forget, thank you for all the constructive criticism regarding this thesis and for keeping calm when receiving messages during late nights and weekends.

The second person I owe a great deal of gratitude to is PhD Fredrik Kristensen. Thank you for providing valuable input to my work, for being a constant support, and a good friend. You even spent some of your spare time reading parts of this thesis though you left the group some time ago.

I would like to thank PhD Petr Dokladal at the Center of Mathematical Morphology in France for your guidance and support. My research visit to you in Fontainebleau during fall'06 was one of the most exiting experiances during my entire PhD studies.

My gratitude goes to all my colleagues in the whole Electroscience department, nowadays the department of Electrical and an Information Technology; you have all contributed to my work in various ways. I am especially grateful to the past and present members of the DASIC group: Thomas Lenart, Henrik Svensson, and Joachim Neves Rodrigues, for reading parts of this thesis, Johan Lövgren, Mattias Kamuf, Deepak Dasalukunte, and Jiang Hongtu, for all the interesting discussions about all and nothing. Thank you all for your profound knowledge in our field of research, and for being good friends, taking care of more socially related events, which made my time at the department a pleasant journey. I am also very grateful for the work of Elsbieta Szybicka, Erik Jonsson, Pia Bruhn, and Lars Hedenstjerna, who have been taking care of administrative, practical and computer related issues for me during these years.

xi

I would like to thank the other persons involved in this research project, especially associate professor PhD Peter Nilsson. I would also like to thank Anders Olsson, and Daniel Elvin from AXIS Communications AB for their valuable input and professional perspective, setting the pace in this research project.

This work has been financed by the Competence Center for Circuit Design (CCCD) and sponsored by the Xilinx University Program by donating development platforms and software.

To my family, Christina, Björn, and Jonatan, thank you for all the joy, help, and support you have given me so far along the way. Christina, thank you for helping me to straighten out some of the tricky formulations in this thesis.

Last but certainly not least, I would like to say a few words to my love, Tove. From the bottom of my heart, thank you for being who you are, constantly re-energizing my batteries, and complementing the perspective of developing hardware architectures with other things in life. So, let us begin a new journey...

March, Lund, 2008

Hugo Hedberg

### Preface

This thesis summarizes the author's academic work in the digital ASIC group at the Department of Electrical and Information Technology for the PhD degree in circuit design. The main contributions to the thesis are derived from the following journal publications:

H. Hedberg, P. Dokladal, and V. Öwall, "Binary Morphology with Locally Adaptive Structuring Elements: Algorithm and Architecture," first round of revision for publication in *IEEE Transactions on Image Processing*.

H. Hedberg, F. Kristensen, and V. Öwall, "Low Complexity Binary Morphology Architectures with Flat Rectangular Structure Elements," accepted for publication in *IEEE Transactions on Circuits and Systems I*.

F. Kristensen, H. Hedberg, H. Jiang, P. Nilsson, and V. Öwall, "An Embedded Real-Time Surveillance System: Implementation and Evaluation," accepted for publication in *Journal of VLSI Signal Processing Systems*, Springer.

And the following peer-reviewed international conference contributions:

H. Hedberg, and V. Öwall, "An Architecture for Calculation of the Distance Transform Based on Mathematical Morphology," to be submitted for publication, 2008.

H. Hedberg, F. Kristensen, and V. Öwall, "Implementation of Labeling Algorithm Based on Contour Tracing with Feature Extraction," in *Proc.* of *IEEE International Symposium on Circuits and Systems (ISCAS'07)*, New Orleans, USA, May 2007.

F. Kristensen, H. Hedberg, H. Jiang, P. Nilsson, and V. Öwall, "Hardware Aspects of a Real-Time Surveillance System," in *Proc. of IEEE International Workshop on Visual Surveillance* held at *European Conference on Computer Vision (ECCV'06)*, Graz, Austria, May 2006.

H. Hedberg, F. Kristensen, P. Nilsson, and V. Öwall, "A Low Complexity Architecture for Binary Image Erosion and Dilation using Structuring Element Decomposition," in *Proc. of IEEE International Symposium on Circuits and Systems (ISCAS'05)*, Kobe, Japan, May 2005. The papers "Hardware Aspects of a Real-time Surveillance System" and "An Embedded Real-Time Surveillance System: Implementation and Evaluation" are common efforts, the first focusing on the outline of the research project and the second on the details of a prototype of a complete automated digital surveillance system. The author's main contributions in both these publications are the parts addressing morphology and labeling. However, the author has also been involved in the integration of the system and, therefore, system level results are included in the thesis.

The following papers concerning education are also published but not considered part of this thesis:

H. Hedberg, J. N. Rodrigues, F. Kristensen, H. Svensson, M. Kamuf, and Viktor Öwall, "Teaching Digital ASIC Design to Students with Heterogeneous Previous Knowledge," in *Proc. of Microelectronic Systems Education, MSE'05*, pp. 15–16, Anaheim, California, USA, June 12-13, 2005.

J. N. Rodrigues, M. Kamuf, H. Hedberg, and Viktor Öwall, "A Manual on ASIC Front to Back end Design Flow," in *Proc. of Microelectronic Systems Education*, *MSE'05*, pp. 75–76, Anaheim, California, USA, June 12-13, 2005.

H. Hedberg, T. Lenart, and H. Svensson, "A Complete MP3 Decoder on a Chip," in *Proc. of Microelectronic Systems Education*, *MSE'05*, pp. 103–104, Anaheim, California, USA, June 12-13, 2005.

H. Hedberg, T. Lenart, H. Svensson, P. Nilsson and V. Öwall, "Teaching Digital HW-Design by Implementing a Complete MP3 Decoder," in *Proc.* of Microelectronic Systems Education, MSE'03, pp. 31–32, Anaheim, California, USA, June 1-2, 2003.

## List of Acronyms

- ASIC Application-Specific Integrated Circuit

- ADC Analog-to-Digital Converter

- BW Bandwidth

- CC Clock Cycle

- CCD Charge-Coupled Device

- CCTV Closed Circuit Television

- CoG Center of Gravity

- CMOS Complementary Metal Oxide Semiconductor

- DDR Double Data Rate

- EDA Electronic Design Automation

- DSP Digital Signal Processor

- FIFO First In, First Out

- FPGA Field Programmable Gate Array

- fps frames per second

- FSM Finite State Machine

- GMM Gaussian Mixture background Model

- GPP General Purpose Processor

- HDL Hardware Description Language

- HW Hardware

- LUT Lookup Table

- MAC Multiply-Accumulate

- MM Mathematical Morphology

- PCB Printed Circuit Board

#### XV

| PPC   | PowerPC                                                          |

|-------|------------------------------------------------------------------|

| P&R   | Place and Route                                                  |

| RAM   | Random-Access Memory                                             |

| SE    | Structuring Element                                              |

| SDRAM | Synchronous Dynamic Random Access Memory                         |

| SW    | Software                                                         |

| VGA   | Video Graphics Array                                             |

| VHDL  | Very high-speed integrated circuit Hardware Description Language |

| WL    | Word-Length                                                      |

WLAN Wireless Local Area Network

## List of Definitions and Mathematical Operators

All definitions listed here are taken from [1] and [2].

| $\mathbb{Z}$        | 1-D integer space                                                          |

|---------------------|----------------------------------------------------------------------------|

| $\mathbb{Z}^+$      | Positive integer space                                                     |

| $\mathbb{Z}^2$      | 2-D integer space                                                          |

| $\mathbb{R}$        | 1-D real (continuous) space                                                |

| $\lfloor i \rfloor$ | Floor function, rounds $i$ to nearest lower integer towards minus infinity |

| $\lceil i \rceil$   | Ceiling function, rounds $i$ to the nearest upper integer towards infinity |

| $\exists x$         | There exists an x such that                                                |

| $\forall x$         | For all x,                                                                 |

| $x \in A$           | The element x belongs to the set A                                         |

| $x \notin A$        | The element <b>x</b> does not belong to the set A                          |

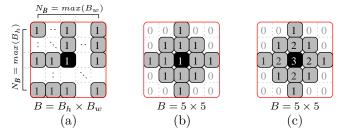

| В                   | Structuring element                                                        |

| $\ominus$           | Erosion                                                                    |

| $\oplus$            | Dilation                                                                   |

| 0                   | Opening                                                                    |

| •                   | Closing                                                                    |

| Ø                   | Empty set                                                                  |

| $A'=A^c$            | Complementation or inverse                                                 |

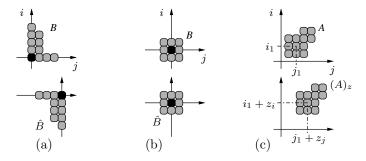

| Â                   | Reflection, i.e. geometric inverse                                         |

| $(A)_z$             | The translation of A by z                                                  |

| $A\subseteq B$      | A is a subset of B                                                         |

| $A\cap B$           | Intersection of set $A$ and $B$                                            |

| $A\cup B$           | Union of set $A$ and $B$                                                   |

|                     |                                                                            |

xvii

### Introduction

Ever since the introduction of television, real-time monitoring has been a growing market. Adding a video recorder opened up a new world for the security industry. Video surveillance soon made its way into the court rooms and became convicting evidence. Today, video surveillance systems are omnipresent and part of everyday life and can be found in department stores, banks, bus terminals, etc. They are not only used for crime prevention purposes but also play their role in more social and industry related applications, e.g. traffic monitoring, processing monitoring, and customer statistics. With continuously increasing fields of application and integration into our lives, at least two serious questions arise: What about personal integrity? How will this information be used? Naturally, none of these questions will be answered in this thesis, but the author is aware of the possible link between the presented technology and social interests that are attached to this field of research. The only conclusion that can be drawn is that some of these applications are easier to accept than others but the boundary for acceptance is, of course, subjective. Without knowing what the future of automated surveillance will bring, as technology advances, the applicability of such systems is continuously increasing and is nowadays part of everyday life.

Conventional real-time surveillance systems are known as Closed Circuit Television (CCTV) systems. A typical system is traditionally controlled by a human operator, and supports multiple cameras, event recording, Pan-Tilt-Zoom (PTZ), auto-focusing etc. Automating such a system would not only reduce the time spent on monitoring the system itself, but can also increase the number of attached cameras in the system, thus increasing surveillance efficiency. Stepping into the digital domain and applying digital image processing

1

is a natural evolution, since it enables the possibility to extract information from the image stream without human interaction. The extracted information can be used as decision support in an effort to reduce the number of errors or false alarms caused by human operators. For those concerned with the personal integrity in such automated systems, some argue that this will even increase, since the image processing gives the possibility of hiding the identities of the objects present in the scene, e.g. by blurring faces or even replacing the complete object with a synthetic model.

However, the ever increasing demands on higher resolutions and functionality within the automated systems impose a high bandwidth requirement that is not possible to handle in software running only on a general purpose processor which attempts to achieve real-time performance. Therefore, a design challenge in any automated surveillance system is to handle or reduce the bandwidth. In this thesis, to be able to address the high bandwidth, the system is implemented as an embedded system in which the main idea is to have key operations and repetitive calculations placed in dedicated hardware accelerators which efficiently reduces the amount of data needed to be processed in the software. This is identified as crucial to sustain real-time performance and simultaneously have a high resolution and frame rate. Therefore, the need for such dedicated hardware accelerators that can be deployed in an embedded system environment becomes evident.

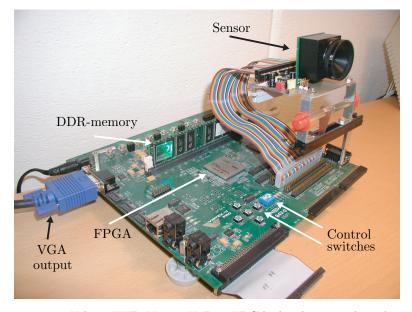

### 1.1 Research Project

The research presented in this thesis is part of the development and implementation of a complete automated surveillance system based on a single self contained network camera in hardware. The aim of the system is to be able to detect, track and classify objects in consecutive frames. Such a system not only competes in terms of a higher frame rate and higher system resolution compared to other general processor solutions, but also with a reduced power dissipation due to higher hardware resource utilization. Integrating the single camera system with more cameras, or sound, would certainly increase the accuracy of the system but is beyond the scope of the project. Furthermore, although the system resolution, i.e.  $320 \times 240$ , is low compared to commercial products, this resolution is sufficient for development purposes, and is therefore often used when developing the hardware accelerators.

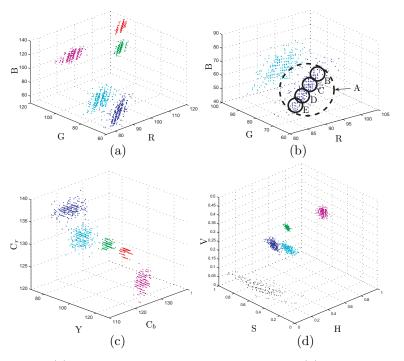

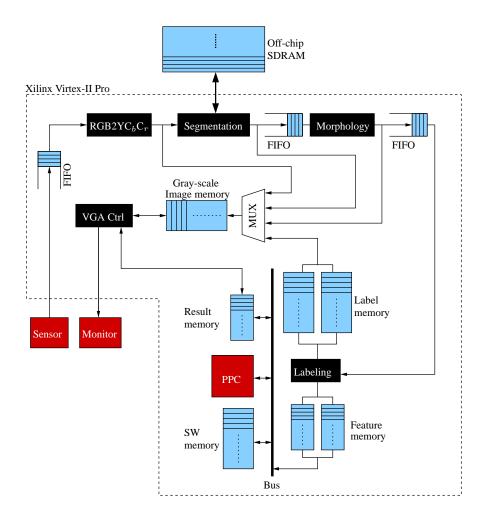

Three PhD students have been involved in developing different parts of the system. The author of this thesis is responsible for morphology and labeling, J. Hongtu for implementation of the sensor interface and segmentation [3], and F. Kristensen for feature extraction and tracking Software (SW). He is also responsible for implementation of additional Hardware (HW) units, e.g. the

PowerPC (PPC) interface. Furthermore, F. Kristensen also performed an investigation of the impact different color spaces have on shadows [4]. All three are involved in developing the system architecture and integration. The work is carried out in close collaboration with Axis Communication AB [5] thought the Competence Center for Circuit Design (CCCD).

### 1.2 Main Contribution and Thesis Statement

The main contribution of this thesis is to present four hardware architectures together with their corresponding implementation results. The architectures are to be used as hardware accelerators in embedded image processing systems, and are compiled in the following list:

- Two low complexity morphological architectures performing binary erosion or dilation with flat rectangular structuring elements, where one of them supports locally adaptive structuring elements,

- an architecture calculating the city-block and chessboard distance transform on binary images, and

- an architecture for connected component labeling based on contour tracing.

A general overview of a complete embedded automated surveillance system will be presented, outlining and setting the goals for this research project. Additional implementation aspects of a prototype of such a system will also be presented, but is not considered to be a part of this thesis' main contribution. Furthermore, incorporating two of the hardware accelerators in the prototype, means that the following thesis statement can be derived:

• Accelerating key operations in hardware is crucial to achieve real-time performance in an automated digital surveillance system.

### 1.3 Thesis Overview

This thesis consists of five chapters and five parts. The chapters comprise introductions, backgrounds, overlapping definitions and commonly shared concepts from the parts, while the main contributions of this thesis, as described in Section 1.2, are placed in the five parts. The research project has resulted in a number of articles and conference contributions, of which the most important constitute the foundation of this thesis. In order to highlight the correlation between the publications and in which part they are placed, an overview of the content in the form of a compilation of the abstracts from these publications are compiled below:

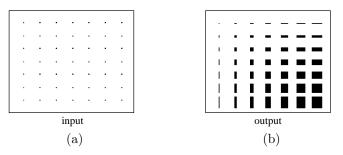

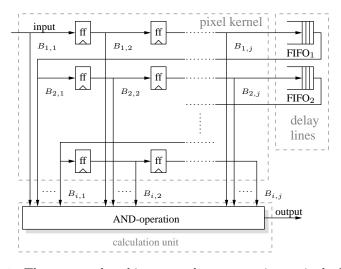

### Part I - Low Complexity Binary Morphology With Flat Rectangular Structuring Elements

This part describes and evaluates three hardware architectures for binary morphological erosion and dilation. Since the architectures are intended to be used as hardware accelerators in real-time embedded system applications, the objective is to minimize the number of operations, memory requirement, and memory accesses per pixel. Therefore, a fast stall-free low complexity architecture is proposed that takes advantage of the morphological duality principle and structuring element decomposition. The main advantage of this architecture is that for the common class of flat and rectangular structuring elements, complexity and number of memory accesses per pixel is independent of both image and structuring element size. Furthermore, by exploring parallelization, the memory requirement can be minimized. An evaluation of the three architectures is presented in terms of complexity, memory requirements and execution time, both for an actual implementation, and as a function of image resolution and structuring element size. The architecture is implemented in the UMC 0.13  $\mu m$  CMOS process using a resolution of  $640 \times 480$  and supporting a maximum structuring element of  $63 \times 63$ .

The content in this part are modified versions of the following publications:

- H. Hedberg, F. Kristensen, and V. Öwall, "Low Complexity Binary Morphology Architectures with Flat Rectangular Structuring Elements," accepted for publication in *IEEE Transactions on Circuits and Systems I*.

- H. Hedberg, F. Kristensen, P. Nilsson, and V. Öwall, "A Low Complexity Architecture for Binary Image Erosion and Dilation using Structuring Element Decomposition," in *Proc. of IEEE International Symposium on Circuits and Systems (ISCAS'05)*, Kobe, Japan, May 2005.

The main contribution of these publications has been developed in close cooperation with PhD colleague F. Kristensen.

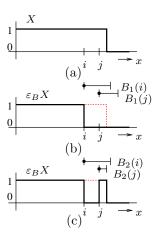

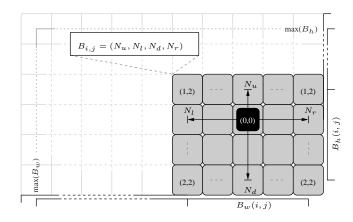

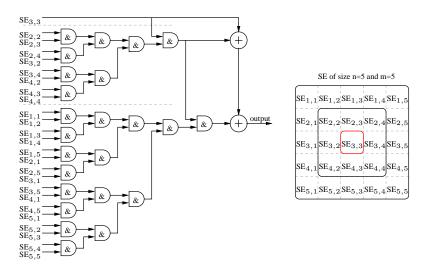

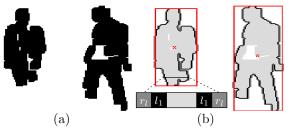

## Part II - Binary Morphology with Locally Adaptive Structuring Elements: Algorithm and Architecture

This part describes a novel algorithm with a corresponding architecture which supports a locally adaptive structuring. Allowing locally adaptive structuring elements is advantageous whenever one can let the structuring element locally adapt to certain high-level information, e.g. apparent size of the objects, texture, or direction. For example, in real-time automated video surveillance applications, letting the structuring element locally adapt to the apparent size of the objects, i.e. explore the depth information, makes processing of the binary segmentation result more efficient and accurate. Therefore, in an effort to enhance performance, this paper presents a novel algorithm for binary morphological erosion with a flexible structuring element, together with a corresponding hardware architecture. The algorithm supports resizable rectangular structuring elements, and has a linear computational complexity and memory requirement. In order to achieve high throughput, the proposed architecture maintains the important raster-scan pixel processing order, and requires no intermediate storage for the image data. The paper concludes with implementation results of the architecture when targeted for both FPGA and ASIC.

The content in this part is a modified version of what has been submitted for publication in:

• H. Hedberg, P. Dokladal, and V. Öwall, "Binary Morphology with Locally Adaptive Structuring Elements: Algorithm and Architecture," first round of revision for publication in *IEEE Transactions on Image Processing*.

The foundation of this publication was initiated during a research visit to the Center of Mathematical Morphology (CMM) in Fontainebleu, France. The work has been carried out in close cooperation with PhD P. Dokladal, and the author's main responsibility in this publication concerns the hardware architecture and its implementation result.

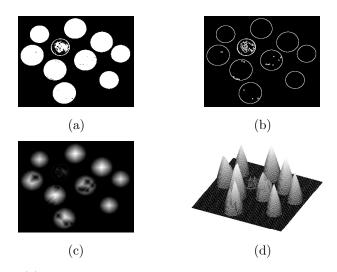

# Part III - An Architecture for Calculation of the Distance Transform Based on Mathematical Morphology

This part presents a hardware architecture for calculating the city-block and chessboard distance transform on binary images. It is based on applying parallel morphological erosions and adding the result, enabling preservation of the raster pixel scan order and having a well defined execution time. The low memory requirement makes the architecture applicable in any streaming data real-time embedded system environment with hard timing constraints, e.g. set by the frame rate. Depending on the application, if a priori knowledge of the image content is known, i.e. the maximum size of the clusters, this information can be explored reducing execution time and memory requirement even further. An implementation of the architecture has been verified on an FPGA in an embedded system environment with an image resolution of  $320 \times 240$  at a frame rate of 25 fps running at 100 MHz. Implementation results when targeted for ASIC are also included.

• H. Hedberg, and V. Öwall, "An Architecture for Calculation of the Distance Transform Based on Mathematical Morphology," to be submitted for publication, 2008.

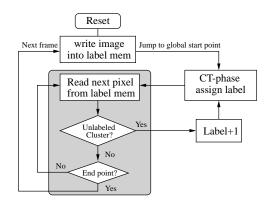

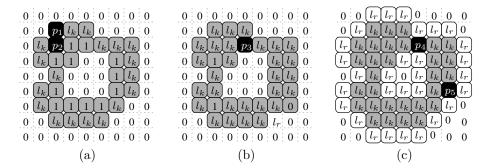

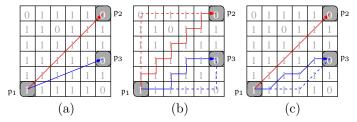

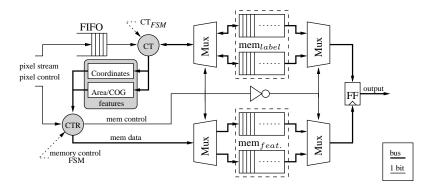

## Part IV - Implementation of Labeling Algorithm Based on Contour Tracing with Feature Extraction

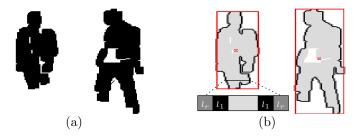

This paper describes an architecture of a connected-cluster labeling algorithm for binary images based on contour tracing with feature extraction. The implementation is intended as a hardware accelerator in a self contained real-time digital surveillance system. The algorithm has lower memory requirements compared to other labeling techniques and can guarantee labeling of a predefined number of clusters independent of their shape. In addition, features especially important in this particular application are extracted during the contour tracing with little increase in hardware complexity. The implementation is verified on an FPGA in an embedded system environment with an image resolution of  $320 \times 240$  at a frame rate of 25 fps. The implementation supports the labeling of 61 independent clusters, extracting their location, size and center of gravity.

The content in this part is a modified version of the following publication:

• H. Hedberg, F. Kristensen, and V. Öwall, "Implementation of Labeling Algorithm Based on Contour Tracing with Feature Extraction," in *Proc.* of *IEEE International Symposium on Circuits and Systems (ISCAS'07)*, New Orleans, USA, May 2007.

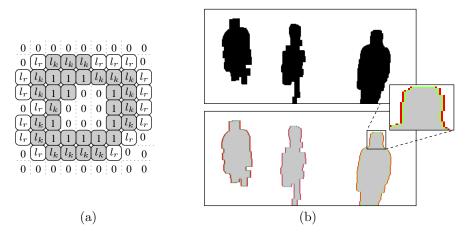

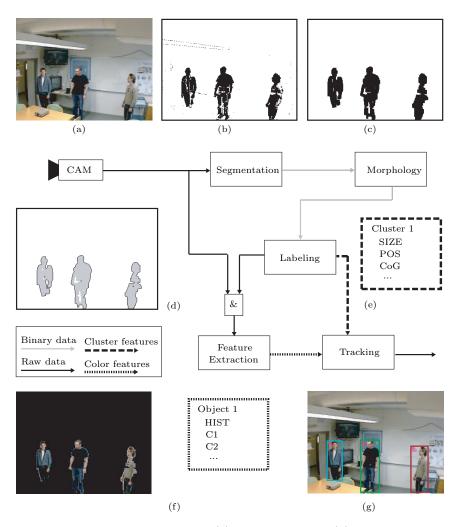

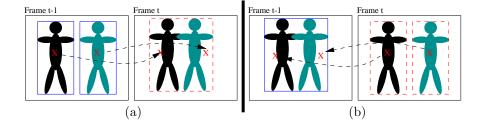

#### Part V - An Embedded Real-Time Surveillance System: Implementation and Evaluation

This part describes an HW implementation of an embedded automated digital video surveillance system with tracking capability. The system is partitioned so that it has key operations implemented as dedicated HW accelerators, e.g. video segmentation, morphological filtering and labeling, while tracking is handled in software running on an embedded processor. By implementing a complete embedded system, bottlenecks in computational complexity and memory requirements can be identified and addressed. Accordingly, a memory bandwidth reduction scheme for the video segmentation unit is deployed together with the development of efficient low memory requirement architectures for morphological and labeling operations. Furthermore, system level optimizations are also explored and applied, e.g. the application does not require unique labels which reduce the memory requirement in the labeling unit and thereby also the total memory requirement in the system. The hardware accelerators provide

#### 1.3. THESIS OVERVIEW

the tracking software with object properties, i.e. metadata, resulting in the complete decoupling of the tracking algorithm from the image stream, which is crucial to achieve and sustain real-time performance. A simplified system prototype is running on an FPGA development board using a resolution of  $320 \times 240$  and a frame rate of 25 fps. Furthermore, the impact on the system's resource utilization (scalability) when increasing the resolution is also investigated.

The content in this part is mainly a reprint of the following publication:

• F. Kristensen, H. Hedberg, H. Jiang, P. Nilsson, and V. Öwall, "An Embedded Real-Time Surveillance System: Implementation and Evaluation," accepted for publication in *Journal of VLSI Signal Processing Systems*, Springer.

Despite earlier efforts to avoid repetition and overlap, since the content in this part is mainly an unmodified reprint, overlapping definitions, figures, tables, and results regarding morphology and labeling are obvious. The author's main responsibility in this contribution are the parts concerning morphology and labeling.

## **Digital System Design**

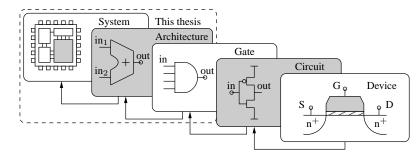

Designing digital processing systems is a complex task that involves many abstraction levels of digital circuit design. A traditional overview of the abstraction levels used in digital circuit design is illustrated in Figure 2.1 [6]. The major part of work presented in this thesis is located at the system- and architecturelevels. Furthermore, there are many design specific parameters to consider, e.g. design time, cost, throughput (speed), power, area, and flexibility. Many of these parameters depend on each other, e.g. increasing the throughput may result in an increased power dissipation and area, making the design process even more difficult. The subsequent sections will describe some of the design parameters considered during the development of the architectures presented in this thesis.

#### 2.1 Implementation Platform

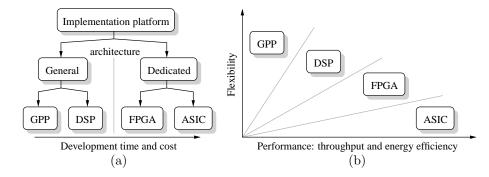

One of the most important decisions to make when developing a digital signal processing system is the choice of implementation platform. Here, the implementation platform is used as the designation for the hardware on which the actual processing is performed. The choice involves a trade-off between design time, development cost, flexibility, and performance in terms of throughput and energy efficiency, i.e. energy consumed per operation. There are mainly four implementation platforms to choose from:

GPP – General Purpose Processor,

**DSP** – Digital Signal Processor,

**Figure 2.1:** An overview of typical abstraction levels used in the field of digital circuit design, where the arrows indicate increasing level of abstraction. The figure also shows on which level the main part of the work in this thesis has been carried out, i.e. architecture and system level.

FPGA – Field Programmable Gate Array, and

ASIC – Application-Specific Integrated Circuit,

which are categorized and placed in Figure 2.2(a) depending on the degree of specialized architecture they are based upon. The more specialized the architecture, the more optimized it is for a specific application. This makes the categorization stretch from a GPP being the most general, to a dedicated full custom ASIC being the most optimized. Note that since the categorization is based on the architecture, a GPP implemented as an ASIC still falls under the category of GPP, a DSP implemented on an FPGA is still a DSP, and so on. There are also hybrids that can be placed in several categories, e.g. structured ASICs being a combination of an FPGA and an ASIC. However, since these hybrids do not add anything to the conceptual discussion conducted here, they are simply omitted.

A GPP is found in common desktop computers, typically having a generic instruction set that is not optimized for any particular application [7]. Since a GPP offers the possibility of running practically any code, thus supporting both floating point and fix-point operations, there are several issues limiting their applicability in real-time processing systems. The main reason for this limitation is due to the fact that a GPP does not offer any type of specialized hardware support for specific or repetitive operations found in digital processing algorithms. As a consequence, this type of implementation platform has a throughput and an energy efficiency among the lowest of all four categories.

The second category is the DSP, which is a type of processor specialized for digital signal processing applications [8]. A DSP has a specialized instruction

**Figure 2.2:** (a) The four categories divided by their architectural properties. (b) Flexibility as a function of performance for the four major categories of implementation platforms.

set with dedicated hardware support for operations commonly used in digital signal processing algorithms, e.g. Multiply-Accumulate (MAC), and extended memory support [9]. Having these extensions, this type of processor has both higher throughput and a better power efficiency. Regarding the supported number representation, there are DSPs that support floating point operations, but the majority only supports fix-point operations [10].

An FPGA is a reconfigurable implementation platform which typically consists of logic blocks, interconnects (routing), and I/O blocks [11]. Their reconfigurability comes from the fact that the logic blocks and routing can be programmed. Therefore, an FPGA offers the possibility of exploiting parallelism, resulting in an increased performance compared to GPPs and DSPs. Nowadays, most FPGAs come with embedded on-chip macro blocks (dedicated HW blocks), e.g. multipliers, memory, and in some cases even embedded GPPs. In addition, the vendors may provide the user with software tools to generate common arithmetic components, increasing their applicability in digital processing systems even further. However, one major drawback of this implementation platform is the limited support of floating point-arithmetic operations. Another drawback is the increased development time of an FPGA solution compared to the one based on a GPP or a DSP, somewhat taking the focus from the actual algorithmic development. However, the support for floating-point operations is continuously increasing as well as the ease-of-use of the Electronic Design Automation (EDA) tools from the FPGA vendors. From a power perspective, the configurability comes at the cost of a high power dissipation, e.g. due to the over dimensioned interconnect structure and the use of Lookup Tables (LUT) instead of dedicated gates, making this implementation platform less applicable in low power applications.

The last category is the ASIC, which offers the highest performance in terms of throughput and power efficiency, but has the longest development time of all categories. ASICs and FPGAs have many properties in common, e.g. the possibility of exploiting parallelism, but with the main difference that the architecture in ASICs can not be altered. Hence, all algorithmic flexibility and reconfigurability must be supported and included in the design before fabrication. The increased performance in terms of throughput and power consumption in an ASIC over an FPGA is due to optimized arithmetic operations, design structures, and routing, together with the possibility of being able to apply more refined low power techniques, discussed further in Section 2.4 and 2.5. Furthermore, if the implementation is to be mass produced, implementing an ASIC may be more cost effective (even if maximum performance is not required) since the production cost per chip will decrease. This leads to the conclusion that if flexibility may be traded for high throughput and low power consumption together with the fact that the budget may cover the increased design time associated with developing an ASIC, this is the best implementation platform for the job. In fact, the superior performance makes this implementation platform the only choice in certain applications, e.g. medical applications [12].

Traditionally, the four categories are shown as a function of flexibility and performance. Performance is relatively easy to measure and the horizontal axis in Figure 2.2(b) very well corresponds to reality. However, since flexibility is not easy to measure, the placement of the categories on the vertical axis may be argued. As an example, an FPGA with a hard embedded GPP macro block is more flexible than a single GPP core, since it gives access to both the strengths of the GPP and offers the possibility of placing key operations in dedicated hardware accelerators (architectures). Again, by omitting the hybrids and by letting the vertical axis correspond to the applicability of a system solution based on this category to various applications, stating that the GPP is the most flexible and an ASIC is the least, is not that far from the truth.

To summarize: No matter how fast a GPP or DSP will become in the future, having a dedicated hardware accelerator placed in an FPGA or an ASIC will always be advantageous in terms of throughput, due to the ability to exploit parallelism [9]. Although the FPGAs of today are not really targeted for low power applications, the continuous development of new low power techniques incorporated in every new FPGA generation is closing the gap between FPGAs and ASICs in terms of low power consumption.

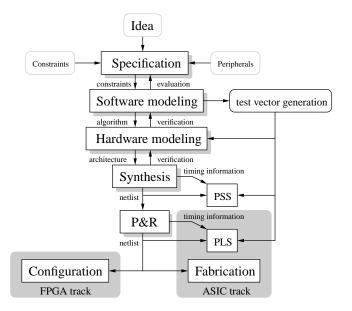

**Figure 2.3:** An overview of the design flow used when developing the architectures presented in this thesis.

### 2.2 Design Flow

A digital hardware design flow defines the steps when transforming a specification into a reproducible implementation, e.g. an embedded system running on an FPGA or an ASIC. A well defined design flow not only ensures the quality of the outcome but also reduces design time, since the time spent in each step can be estimated and measured, so resources may be allocated accordingly. Figure 2.3 illustrates details of a simplified design flow for hardware design using a Hardware Description Language (HDL) targeted for an FPGA or an ASIC, that covers the main development process used in this research project. Naturally, a design flow is application dependent, and so is the time spent in each step, which is dependent on several factors, e.g. algorithmic complexity, size of the design, and speed constraints.

The design process starts with an idea about what is to be developed, e.g. a hardware accelerator or a complete embedded system, which is turned into a specification. Starting at the top of Figure 2.3, the main steps in a hardware design flow are:

- **Specification** contains detailed information of what is to be developed with available resources, e.g. design time, budget, technology, interfaces, and peripherals.

- **Software modeling** is used to identify and model key components, typically performed using a high level description language, e.g. C, C++, or Matlab. Software modeling is a fundamental step in the design flow since it includes algorithm selection, software/hardware partitioning, timing evaluation, deciding arithmetic precision, evaluation of parameter settings, and complexity analysis of the components. In addition, test vectors to and from the components are generated to be used for verification of succeeding steps.

- **Hardware modeling** describes the hardware components' behavior on a bit-level, typically described in VHDL or Verilog. This step determines the actual hardware architecture of the components.

- **Synthesis** transforms the hardware model into a netlist. A netlist is a description of the hardware model in terms of physical gates, which are selected from a standard cell library, and their relative interconnection.

- **Place and route (P&R)** physically places the gates, and routes the interconnections of the netlist on the FPGA or the die (in case of an ASIC implementation).

- **Configuration/Fabrication** depending on the target implementation platform, the FPGA track ends in a programming file that configures the FPGA, and the ASIC track ends by sending the design for fabrication.

When designing an ASIC, a good strategy to verify the functionality of the design is to extract timing information for the netlist and to perform a Post Synthesis Simulation (PSS) or Post Layout Simulation (PLS) before manufacturing the design, illustrated in Figure 2.3. Rapid prototyping may also be performed using an FPGA to test the functionality and interfaces between the processing units. Naturally, there are practical situations when functional verification on an FPGA is superfluous or even not feasible, e.g. when the design is too large, or when full custom blocks on a circuit level are being developed. This is due to the fact that full custom blocks may consist of gates, transistors, or have a routing that is not possible to achieve in an FPGA. However, if possible, performing PSS, PLS or prototyping on an FPGA, minimizes the risk of sending erroneous designs for fabrication and should therefore always be considered. Note that the netlists may also be used to simulate the power

consumption of the design, which gives an indication of how much power will be dissipated in the design.

### 2.3 Real-time Processing

In a general real-time processing system, the system is required to respond to an input event within a predestined time using given resources so that it keeps up with an external process [7]. In an image sensor based processing system, the outside process is the image acquisition step. The speed of the image acquisition step is equivalent to the frame rate  $f_{rate}$  and is measured in frames per second (fps) or Hz. The frame rate is a critical parameter for system performance since it affects the timing budget by putting an overall constraint on the system processing time  $t_p$ , i.e. the total time it takes for the system to process a complete frame. System latency is also an important property which corresponds to the delay between an event and the system's response to this event. In practice, the latency corresponds to the delay between input and output data, and should be kept as low as possible. Assuming a single processing block, regardless of latency and other system parameters and settings, e.g. resolution, the following relation must hold

$$t_p \le \frac{1}{f_{rate}}.\tag{2.1}$$

The frame rate depends on the system resolution and may have limited degrees of freedom, as they are sensor specific. This means that a particular sensor supports certain modes of operation, i.e. a certain resolution results in a given  $f_{rate}$ . The higher the  $f_{rate}$ , the shorter the time which has elapsed between two consecutive frames, and the more "similar" or more quasi-stationary the two images become. This may be important in certain applications, e.g. automated surveillance, since object motion predictions become more accurate resulting in a more robust tracking. However, a high frame rate imposes a high bandwidth or bit rate to and from the hardware blocks, e.g. memories, which is a major bottleneck in many image processing systems [13]. A high bandwidth also consumes more power, which is always an issue in any system design and may be critical in battery operated devices. From a system perspective,  $f_{rate}$ should be kept as low as possible while still being able to process the fastest event in the scene.

Deciding a frame rate is more than just a question of processing speed and algorithmic robustness, particularly if the output is a video sequence that is to be viewed by humans. In general, humans perceive a motion as continuous if  $f_{rate} \geq 20$  [14], but this figure depends to a large extent on the image content. However, many people still experience discontinuities in the motion at this

frame rate, and as a consequence, common television standards use  $f_{rate} \geq 25$ , e.g. PAL=25 and NTSC=30 fps [15](PAL=50 and NTSC=60 fps interlaced). Based on this discussion, in this thesis, real-time video performance is defined as  $f_{rate} \geq 25$  fps and as presenting the result within a latency of a few frames.

### 2.4 Low Power Circuit Design

The total power dissipation  $P_{tot}$  in a digital integrated circuit consists of three components [6]: static power  $P_{stat}$ , dynamic power  $P_{dyn}$ , and direct-path power  $P_{dp}$ .  $P_{stat}$  is due to leakage currents,  $I_{leak}$ , which are both temperature and technology dependent: increasing as temperature rises, and as the threshold voltage in the transistors is lowered, which occurs when technology is scaled down.  $P_{dyn}$  is due to the charging and discharging of capacitive loads  $C_l$  of a transistor.  $P_{dp}$  is due to the nature of the Complementary Metal Oxide Semiconductor (CMOS) design in which a direct-path between the supply voltage and ground is present during the switching phase of the gates. This direct path results in a short circuit current  $I_s$ , present during a short period of time  $t_s$ , when both transistors are conducting.

All power contributions,  $P_{stat}$ ,  $P_{dyn}$ , and  $P_{dp}$ , are dependent on the supply voltage  $V_{dd}$ , but only  $P_{dyn}$  and  $P_{dp}$  are proportional to the clock frequency f. The total power dissipation in a design is defined as

$$P_{tot} = P_{stat} + P_{dyn} + P_{dp} = V_{dd} \cdot (I_{leak} + f \cdot (C_l \cdot V_{dd} + I_s \cdot t_s)), \qquad (2.2)$$

where  $P_{dp}$  may be neglected since it is small compared to the other two components. Traditional low power design techniques and tools focus on minimizing the dynamic power since it is traditionally the largest component in (2.2). Typical low power design techniques are: voltage scaling, power-gating, multiple threshold cell libraries, and clock-gating, among which voltage scaling is popular due to the square relationship in (2.2). Furthermore, the propagation delay  $t_p$  of a given gate depends on the threshold voltage  $V_t$ , and the supply voltage according to

$$t_p \propto \frac{V_{dd}}{(V_{dd} - V_t)^2},\tag{2.3}$$

which shows that power is traded for speed [16]. Both increasing  $V_t$ , which reduces the static power, and decreasing  $V_{dd}$ , which reduces the dynamic power dissipation in (2.2), result in a longer propagation delay, and hence slower circuitry. In practice, (2.3) is the basis of lowering the supply voltage so that the  $t_p$  of the design matches the timing constraint imposed by the application, e.g. resolution and frame rate. To further refine this technique, (2.3) may be applied on specific regions of the chip, resulting in multiple power domains with an optimal supply voltage within that region [17]. Based on this reasoning, any time slack in the timing model may be used to decrease the dynamic power consumption by lowering the supply voltage.

### 2.5 Low Power FPGA Design

In FPGA design, the power contribution principles discussed in Section 2.4 still holds but the freedom of applying various low power techniques is limited to what is supported by the specific FPGA model, e.g. voltage scaling and power-gating [18]. Due to the recent power awareness among the FPGA vendors, nowadays, low power techniques are also included in the EDA tools, e.g. power driven placement [19]. The power saving when applying these techniques is highly application dependent, but their applicability to the design should always be explored. In addition, there are also other less FPGA model and vendor dependent low power techniques that may be applied to the design:

- **System level** manipulates the switching activity, e.g. multiple clock domains each operating at the lowest possible frequency and clock-gating.

- Architectural level reduces the number of memory accesses and computational complexity.

A typical system level power saving technique is to optimize the throughput frequency balance. This means minimizing the operating frequency of the individual blocks but keeping the throughput constraint (assuming a fixed  $V_{dd}$ ). This technique will save power since the clock distribution network has high switching activity together with large capacitances, f and  $C_l$  in (2.2). This may be achieved since the FPGA typically supports multiple clock domains. Clock-gating may effectively reduce the switching activity in the clock tree by not letting the clock toggle inside unused blocks. If a block is unused, gating the clock to the registers prohibits unnecessary switching activity in the combinatorial parts and signals to further propagate through the system, dissipating unnecessary power. However, the power savings when applying clock-gating in an FPGA are not as high as in the ASIC counterpart, which is due to the high static power consumption in an FPGA [20]. Furthermore, clock-gating is not applicable when the blocks are continuously executing, limiting the power savings in certain applications even further, e.g. the system described in Part V.

On the architectural level, memories and memory accesses are power consuming since they typically have high switching activity and large capacitances on the bit-lines. This is especially true for off-chip memories which have additional capacitances on the I/O-ports. Thus, much effort should be spent on developing algorithms with a minimized memory requirement. Furthermore, another strategy to save power is to reduce the computational complexity. As an example, a(b+c) is preferred over ab + ac, since one multiplier less is used and will therefore consume less power [21].

# **Digital Image Processing**

This chapter presents basic digital image processing concepts and definitions relevant to this thesis. The intention is that it should supply the reader with a theoretical background which is used and referenced in subsequent chapters.

### 3.1 **Digital Image Acquisition**

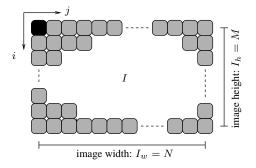

A first step in any digital image processing system is to capture an input image or frame I, typically performed by an image sensor. The sensor produces a frame by spatially dividing a light sensitive region into an ordered array of picture elements referred to as pixels, which are aligned to a grid or lattice, with  $I_h = M$  rows and  $I_w = N$  columns. This spatially ordered light capturing procedure is referred to as *spatial sampling*. The lattice constitutes the domain D of I and is typically a subset of  $\mathbb{Z}^2$  for image sensors. Image resolution is defined as the number of pixels per frame, i.e.  $M \times N$ . Although M < N holds for most commercial resolutions, for the sake of simplicity when describing algorithmic properties, e.g. memory requirement, an image is sometimes assumed to be a square with a resolution of  $N^2$  pixels. Inferring a coordinate system on the array, the origin with coordinates (0,0) is often defined to be located in the upper left corner, as depicted in Figure 3.1. Having the origin defined, each pixel p has corresponding coordinates (i, j), where  $i = \{0, \dots, M-1\}$ and  $j = \{0, \dots, N-1\}$ , defining the pixel's spatial position in the grid. Furthermore, each pixel is mapped onto a set of discrete values corresponding to the light intensity level. This value is quantized and taken from a set of discrete values  $V = \{v_{min}, \ldots, v_{max}\}$ , where  $v_{min}$  and  $v_{max}$  are the minimum and maximum possible intensity values. Mathematically, I can now be described

19

Figure 3.1: A digital image and the coordinate convention used in this thesis, where the pixels are shown in gray and the origin is marked in black.

as a function that maps a certain spatial domain onto this set of values V, and may be written as  $I: D \to V$ . Without color processing, the cardinality of V corresponds to the number of gray levels in the frame, typically a power of two, i.e.  $2^1 = 2$  or  $2^8 = 256$ . Typically,  $v_{min} = 0$  which makes the binary representation of  $v_{max}$  determine the number of bits in hardware required to represent the maximum pixel value and thereby also the dynamic range for this frame. As an example, to represent and store a binary image I in a memory, since  $V = \{0, 1\}$  which implies |V| = 2, only one bit per pixel is required.

#### 3.1.1 Human Vision

A color is a light source with a certain wavelength distribution, where the wavelengths that stretch from about 400 to 700 nm lies within the human visual spectrum [22]. A light source with a uniform wavelength distribution within the visual spectrum is referred to as white, and a light source containing only one wavelength is monochromatic (dirac distribution). The sum of the wavelength distribution is equal to the intensity. Furthermore, since a sensor only measures spatial light intensity, it becomes gray scale by nature. However, to be able to keep the wavelength distribution information, a color space is inferred, splitting the intensity into different and separate wavelength contributions: each color pixel is represented as a point in the color space with each color component contribution as the projection onto each respective axis. A common technique to create a multi-dimensional color space, e.g. RGB, is to separate the wavelengths of the incoming light by inferring a color filter on top of the pixel grid. The filter, called a Color Filter Array (CFA), is periodic and the actual colors in the filter corresponds to the desired color component. As an example, a

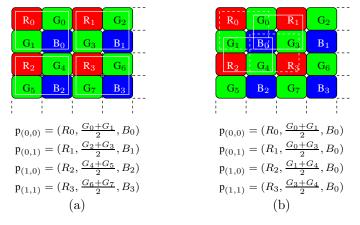

Figure 3.2: An illustration of a Bayer mask together with examples of two pixel setups. (a) is the one used in the system described in Part V.

CFA with one red, two green, and one blue filter component will produce the RGB color space. This filter, depicted in Figure 3.2, is of special interest since it is commonly used by sensor manufacturers and is named as the Bayer filter after its inventor [23]. After the RGB color intensities have been measured, the sensor output pixels are created as a set of three color components. Since there are four color components in the CFA and only three in a pixel, a decision on how to create the three output values has to be made. When using the Bayer CFA, this is usually done by manipulating the green components with various techniques, e.g. calculating the mean of two green values, illustrated in Figure 3.2(a), or by using each color value in multiple pixels, illustrated in Figure 3.2(b).

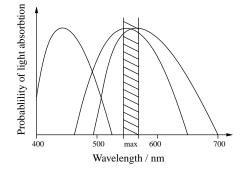

The human eye has two types of receptors [24]: rods and cones. Rods are only sensitive to incoming light intensity and cones only to color information. Furthermore, cones are divided into three subtypes each sensitive to a specific color: blue, green, and red. The reason for choosing two green pixels in the CFA is that the human eye is more sensitive to green than to red or blue. This is due to the fact that the sum of the probability of the color receptors absorbing a light quantum with a certain wavelength has its maximum around  $\approx 550$  nm, which corresponds to a greenish color, illustrated in Figure 3.3.

#### 3.1.2 Sensor Techniques

There are two major sensor techniques: Charge Coupled Device (CCD), and CMOS. Both techniques were developed in the late 60's and early 70's. First,

**Figure 3.3:** Normalized spectrum sensitivity of the human eye for each of the three cone receptor subtypes versus wavelength [14]. The sensitivity is proportional to the probability of a receptor absorbing a light quantum with a specific wavelength.

CCDs became dominant due to superior image quality, and not until the 90's could the fabrication methods deliver the dimensions and uniformity needed when using the CMOS technology. As a consequence, CCDs were found in highend cameras and CMOS sensors in budget models. However, nowadays this distinction is not valid anymore, since CMOS sensors are also placed in highend models [25]. The subsequent section presents a brief comparison between the two techniques [26] [27]. However, before going into details, some important parameters are presented that may be used to compare the two techniques and which are of special interest in automated digital surveillance systems:

- **Dynamic range** The ratio between a pixel's saturation level and its signal threshold, i.e. the ratio between maximum and minimum signal level which should be kept as high as possible.

- Uniformity Consistency in pixel response for different spatial locations under identical illumination conditions, i.e. the same light intensity at different locations of the sensor should result in the same output pixel value. The uniformity may vary at different illumination intensities.

- **Speed** The data rate of the sensor output pixel stream, measured in MHz.

### 3.1.3 CCD versus CMOS Sensors

Both CCD and CMOS techniques are Metal Oxide Semiconductors (MOS) and function as spatial light samplers; they both have a light sensitive region that

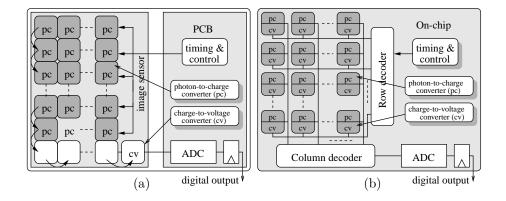

**Figure 3.4:** (a) A typical CCD sensor, where the photon-to-charge converter is placed inside the pixel array and the charge-to-voltage converter is placed outside of the pixel array. (b) A typical CMOS sensor, where both the photon-to-charge and charge-to-voltage converters are placed directly in the pixels.

converts photon quantums into charge at each location in the pixel grid. The electrical charge is converted into a voltage and finally sent to the output. However, it is the read-out procedure of the charge that is the major difference between the two techniques.

A CCD sensor transfers the charge quantum sequentially from one photonto-charge converter to another towards the output charge-to-voltage converter. A typical CCD sensor with some required circuitry and logic blocks is depicted in Figure 3.4(a).

In a CMOS sensor, illustrated in Figure 3.4(b), the photon-to-charge and charge-to-voltage conversions takes place directly in the pixel. Therefore, signal routing to each pixel is required, reducing the pixel density to some extent.

Comparing the dynamic range between the sensor techniques, the CCD has an advantage due to less noise in the substrate. Traditionally, the uniformity was problematic in CMOS sensors, but the gap is continuously decreasing. The image pixel output speed is one of the most important parameters since at a given frame rate, a faster pixel output speed results in a longer processing time per frame for the system. In general, CMOS sensors have a slight advantage over CCDs in terms of speed. Another important issue is the amount of required post-processing. CMOS sensors typically have more post-processing integrated on-chip, e.g. timing generation, Analog-to-Digital Conversation (ADC), and noise reduction, as opposed to the CCD which has most post-processing on the

| Sensor property | CCD    | CMOS   |

|-----------------|--------|--------|

| Dynamic range   | Better | Good   |

| Uniformity      | Better | Good   |

| Speed           | Fast   | Faster |

| Power           | Higher | Lower  |

| Cost            | More   | Less   |

**Table 3.1:** A comparison of important parameters between the CCD and theCMOS sensor techniques.

camera Printed Circuit Board (PCB). This, together with the fact that CMOS sensors can be manufactured in standard MOS processes, makes the cost per sensor less for CMOS than for CCDs. Based on this brief evaluation, summarized in Table 3.1, together with the fact that the CMOS sensor consumes less power, this type of sensor is more suitable in our application.

#### 3.1.4 Raster Scan Order

An important concept in real-time processing is the data pattern of the input stream. This is important since it has a large impact on several aspects of hardware design, e.g. the required amount of hardware resources, the timing model, and type of memory. In many digital real-time image processing applications, the data pattern is a stream of sequential pixels starting in the top left and ending in the bottom right corner of the image, which is referred to as the raster scan order. This is a typical read-out pattern from a sensor or when multiple pixels are burst read from a memory source. To avoid intermediate data storage and random memory accesses during the pixel processing, and to achieve minimal system latency, the pixel processing chain should maintain the raster scan property as long as possible. In practice, this means sequential input and sequential output, to and from the included HW blocks.

## 3.2 Fundamental Pixel to Pixel Based Relationships

### 3.2.1 Neighborhood

A commonly used spatial pixel neighborhood defined on a square lattice can be formed by taking a square of size  $3 \times 3$ , centered around a pixel p at location (i, j). This pixel has two horizontal and two vertical neighboring pixels at coordinates

$$(i, j+1), (i+1, j), (i, j-1), (i-1, j),$$

(3.1)

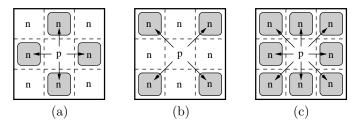

**Figure 3.5:** (a) A pixel p and its 4-neighbors  $(N_4(p))$ , (b) D-neighbors  $(N_D(p))$ , (c) and 8-neighbors  $(N_8(p))$ .

defined as the 4-neighbors of p(i, j) and denoted  $N_4(p)$ , depicted in Figure 3.5(a). Furthermore, p(i, j) also has four diagonal neighbors at coordinates

$$(i-1, j+1), (i+1, j+1), (i+1, j-1), (i-1, j-1), (3.2)$$

denoted  $N_D(p)$ , depicted in Figure 3.5(b). These pixels, together with  $N_4(p)$ , are defined as the 8-neighbors denoted  $N_8(p) \in N_4(p) \cup N_D(p)$  [28]. In words, a pixel and its closest neighboring pixels in all directions, are often referred to as nearest neighbors, illustrated in Figure 3.5(c).

### 3.2.2 Connectivity

The relationship between two or more pixels is called *connectivity* [29]. For two pixels  $p_1$  and  $p_2$  to be connected, they must both fulfill the *adjacency criterion* and be in the same neighborhood. The *adjacency criterion* or *adjacency* considers the pixels' intensity value. Given the intensity values of two pixels  $p_1$  and  $p_2$  taken from a discrete set V, defined in 3.1, the adjacency criterion is fulfilled if a predefined condition is met, e.g.  $|p_1 - p_2| < T_{threshold}$  or  $p_1 = p_2$ , where the latter is typical in binary images.

Two pixels  $p_1$  and  $p_2$ , in a binary image are

- 4-connected if  $p_1 \in N_4(p_2)$

- 8-connected if  $p_1 \in N_8(p_2)$

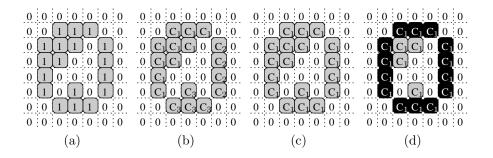

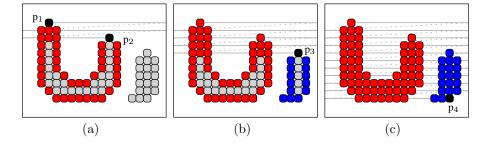

if they simultaneously fulfill the adjacency criterion. Connectivity is a fundamental concept in digital image processing from which other important concepts are derived, e.g. contours, regions, and distance measures. An example of how 4- and 8-connectivity affects clustering is illustrated Figure 3.6(a)-(c). Notice how the 4-connectivity rule misses diagonal transitions as opposed to the 8-connectivity rule, resulting in three clusters instead of one.

**Figure 3.6:** (a) An arbitrary binary image, (b) corresponding 4-connected clusters, i.e.  $C_1$ ,  $C_2$ , and  $C_3$ , (c) corresponding 8-connected cluster  $C_1$ , (d) and corresponding 8-connected contour pixels marked in black.

#### 3.2.3 Clusters

A cluster C is a set of pixels defined by their connectivity, typically 4- or 8connected. Each cluster has a contour P, which consists of contour pixels pand is defined as

$$P = \{ p \mid p \in C, \exists q \in N_4(p), q \notin C \},$$

$$(3.3)$$

which means that a contour pixel p has at least one 4-connected neighboring pixel outside of C. An example of 8-connected contour pixels of an arbitrary-shaped cluster is illustrated in Figure 3.6(d).

#### 3.2.4 Spatial Filters

A spatial filter is a mathematical function that typically applies to the center pixel of the sliding window taking input data from the pixels that are currently coinciding with the window in the input frame [30]. A general spatial operator is defined as

$$g(i,j) = T[f(i,j)],$$

(3.4)

where f(i, j) is the input pixel, T is the filter operation, and g(i, j) is the output at position (i, j) in the resulting image. The filters are defined as linear if the following condition is fulfilled

$$T[af(i,j) + bg(i,j)] = aT[f(i,j)] + bT[g(i,j)],$$

(3.5)

where a and b are any two scalars, and nonlinear if not. Image convolution is an example of a typical linear spatial filter which may be used in a variety of applications depending on the coefficients in the kernel, e.g. image smoothing and sharpening [31]. Let I be a grayscale image in  $\mathbb{Z}^2$  of size  $M \times N$ , then the 2-D image convolution in the spatial domain can be defined as

$$g(i,j) = I(i,j) * b(i,j) = \sum_{s=-\lfloor \frac{S}{2} \rfloor}^{\lfloor \frac{S}{2} \rfloor} \sum_{t=-\lfloor \frac{T}{2} \rfloor}^{\lfloor \frac{T}{2} \rfloor} b[s,t]I[i+s,j+t]$$

(3.6)

where  $i = 0, 1, \ldots, M - 1$  and  $j = 0, 1, \ldots, N - 1$  and b(s, t) is the convolution kernel of size  $S \times T$  containing the coefficients [30] (S and T are assumed to be odd numbers). Examining (3.6), two key arithmetic operations may be distinguished: multiplication and summation. These two operations characterize image convolution, since each value in the input image that is covered by the superimposed convolution kernel is first multiplied with the coinciding coefficient which then are all accumulated, forming the result. When the kernel reaches outside the borders, i.e. when 0 > i + s > M - 1 and 0 > j + t > N - 1, these values are set in such a way that they do not affect the result.

Rank filters are based on internally ordering or *ranking* the intensity values in the input image currently covered by the superimposed kernel, and then performing a nonlinear operation on these values, i.e. which does not fulfill the criterion in (3.5). Typical nonlinear rank filters are formed by taking the median, average, minimum, and maximum, of these values, where the median is particularly important, since it is widely used for noise suppression [30].

## 3.3 Basic Set Theory Definitions

A general set is a cluster of objects or members, referenced as a whole. The members are grouped by certain rules certifying their membership in the set. In image processing, the sets are collections of pixels that are grouped by their connectivity and/or by fulfilling the adjacency criterion (refer to Section 3.2.2) and are mapped onto a certain lattice, e.g.  $\mathbb{Z}^2$  in the 2-D case. Each pixel is associated with a *n*-tuple of values where *n* is the smallest integer required to describe the properties of this particular pixel, e.g. its coordinates and intensity [32]. As an example, let *A* be a set in  $\mathbb{Z}^2$  describing foreground pixels in a binary image, i.e. pixels with intensity value 1, then *n* is equal to 2 since only a pair of coordinates, i.e. *i* and *j*, are required to describe the pixels in the set (the intensity is omitted). Throughout this thesis, sets are referenced with capitals and their corresponding elements with the same lower case letter, i.e. *A* is the set and *a* its elements.

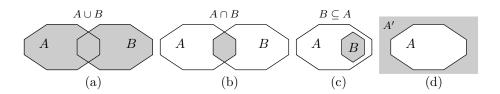

Let A, B be sets in  $\mathbb{Z}^2$ , then there are some basic concepts defined on these sets relevant to this thesis, which are

**Figure 3.7:** Venn Diagram illustrations of basic set theory concepts. (a) Union, (b) intersection, (c) subset, (d) and complement of A.

- union,  $(\cup)$

- intersection  $(\cap)$

- subset  $(\subset \text{ or } \subseteq)$

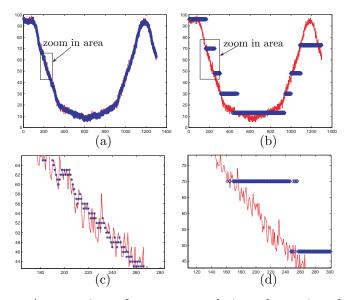

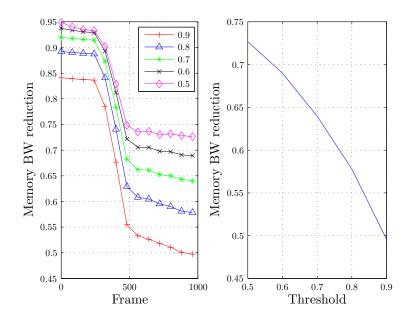

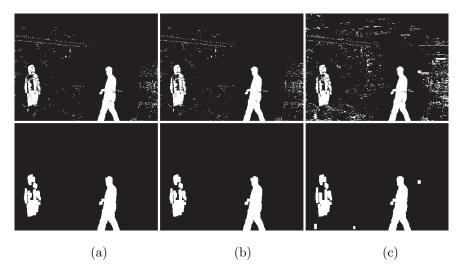

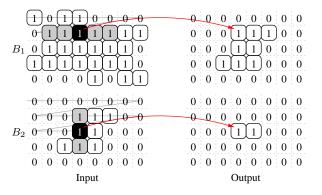

- complement ( $^c$  or ')