UDP readout system for the physics department

Dimitar Dikov

2/22/2017

# Table of Contents

| ١.   |    | Assignment: Readout system                                  | 2  |

|------|----|-------------------------------------------------------------|----|

| ā    | a. | Assignment specification:                                   | 2  |

| k    | э. | System Implementation:                                      | 2  |

| ١١.  |    | Implementation of the Serial Readout Unit (SRU):            | 3  |

| ā    | э. | CMD/STATUS UDP Ethernet EMAC and UDP command/status payload | 4  |

| k    | э. | UDP command distribution                                    | 7  |

| C    | 2. | DCS command decoder                                         | 8  |

| C    | J. | DTC TX                                                      |    |

| e    | ₽. | DTC RX (Deserializer and Memory)                            | 11 |

| f    | •  | UDP Readout FSM and UDP EMAC.                               |    |

| Ę    | g. | Clock Generation                                            | 13 |

| III. |    | Implementation of the CPLD:                                 | 14 |

| ā    | a. | RDOClk and ADC clock                                        | 15 |

| k    | э. | Trigger Detection                                           | 15 |

| C    | 2. | DTC RX Decoder                                              | 16 |

| C    | ł. | Address/Data demux and Reply packer                         | 17 |

| e    | 2. | Saltro Interface Controller                                 | 19 |

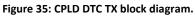

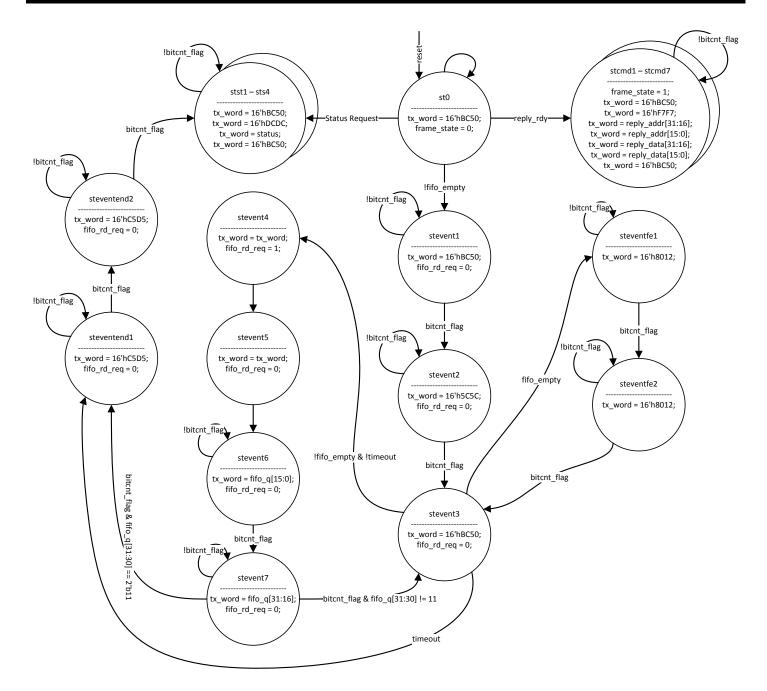

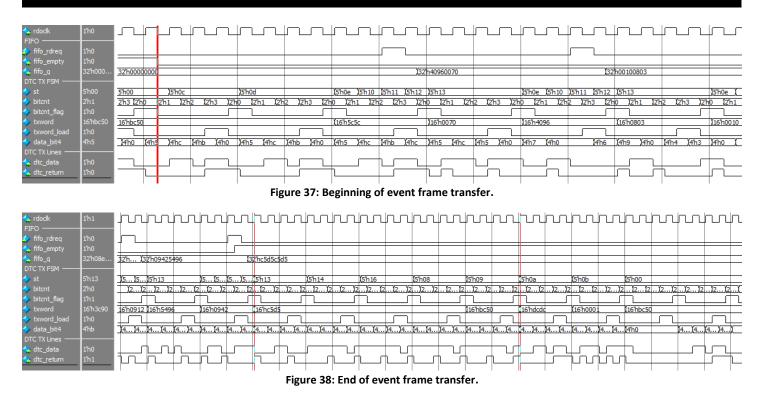

| f    |    | DTC TX FSM and Serializers                                  | 21 |

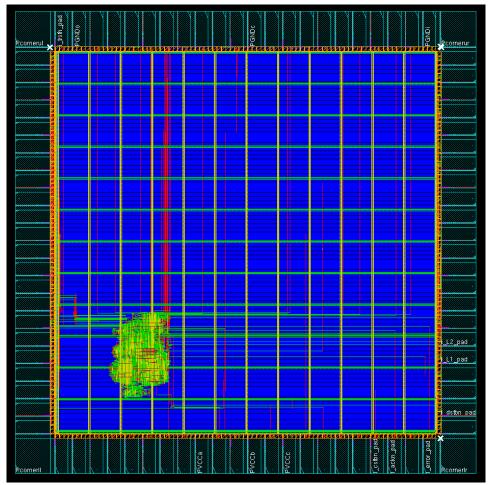

| IV.  |    | ASIC Synthesis & Place and Route implementation             | 24 |

| ā    | э. | Synthesis constraints used                                  | 24 |

| ł    | э. | Place and Route                                             | 24 |

| V.   |    | FPGA & CPLD Synthesis                                       | 25 |

| VI.  |    | Implementation Results & Verification                       | 26 |

| VII. |    | Conclusion                                                  | 27 |

| VIII | •  | Literature                                                  | 27 |

| Ap   | pe | endix 1: Synthesis script                                   |    |

| Ap   | pe | endix 2: Place and route script                             | 29 |

|      |    |                                                             |    |

# I. Assignment: Readout system

## a. Assignment specification:

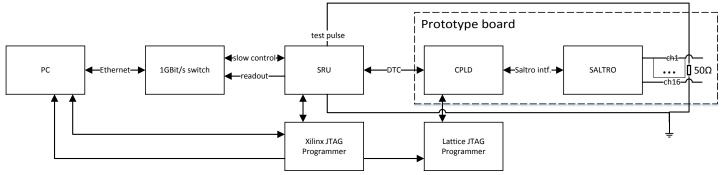

A prototype detector is to be developed that contains one SALTRO ADC chip and a CPLD Lattice LCMX02. The communication between the CPLD and SALTRO is described in [1]. The CPLD will need to communicate via Data Trigger Control (DTC) link [2] using Cat. 6 twisted pair cables with RJ45 connectors to a Scalable Readout Unit (SRU). The SRU consist of a Xilinx Virtex-6 FPGA and it needs to convert the DTC link data to UDP packages. The task of this project is to develop the logic in the CPLD and modify the existing FPGA RTL, including readout protocols, data formatting, system controller, and clock management.

## b. System Implementation:

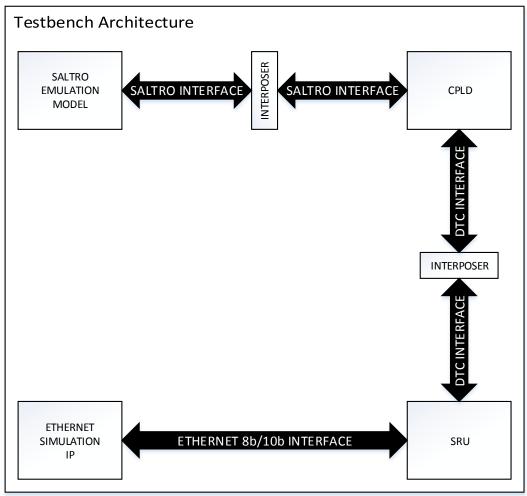

The system contains 1 CPLD (Lattice MACHXO 2) and 1 FPGA (Xilinx Virtex-6 130T). The testbench implementation of the system is shown on fig. 1. It consists of 5 main blocks:

- Saltro Emulation model An emulation model of the digital part of the SALTRO ADC chip.

- Interposers Delay blocks emulating a transmission delay over copper cables.

- CPLD Provides decoding of DTC commands to the SALTRO chip and data serialization when reading out the channels.

- SRU (Serial Readout Unit) Generates trigger sequence for the CPLD/SALTRO, encodes DTC commands and packages the readout data in UDP packets.

- Ethernet Simulation IP Ethernet IP generated using Xilinx Custom IP Generator. Reads UDP packets in raw format and sends them to the SRU, in 8b/10b encoded format.

Figure 1: Testbench Architecture.

# II. Implementation of the Serial Readout Unit (SRU):

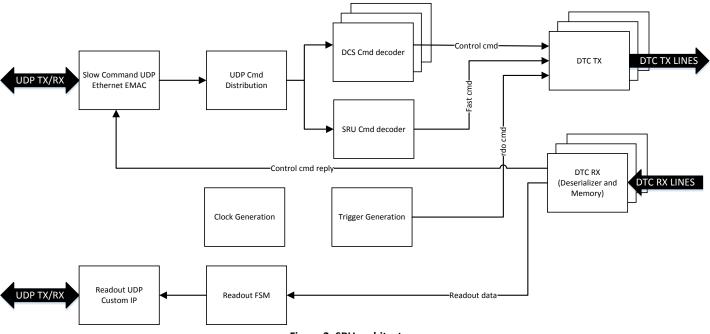

On fig. 2. is shown the simplified SRU architecture.

Figure 2: SRU architecture.

The SRU can support up to 40 DTC connections to 40 CPLDs. The architecture consists of:

- Slow control UDP Ethernet EMAC This IP block contains Xilinx Custom IP Ethernet transceivers, MAC and IP frame decoding [3]. Takes care of ARP and ICMP replies. Read/Write to CSR commands must be send through this EMAC.

- UDP Cmd Distribution Based on the Nodesel bits in the UDP packet, this module distributes the command to each of the DCS Cmd decoders or the SRU Cmd decoder.

- SRU Cmd Decoder This module contains the SRU CSRs, when Nodesel[40] is 1, the SRU would access them.

- DCS Cmd Decoders A total of 40 decoders. 1 for each DTC link. Decodes the 8bit data from the UDP/Cmd distribution to 32bit address & data.

- DTC TX Serializer and encoder for DTC commands/trigger information.

- DTC RX Deserializer and memory block. Once the event information is transmitted, it saves it into memory, which is accessed by the Read out FSM as soon as the event finishes.

- Readout FSM Reads out the DTC RX memory and communicates with the Readout UDP Ethernet EMAC by using AXI4 protocol. Currently supports only a single DTC link.

- Readout UDP Ethernet EMAC Packs the AXI4 data into UDP packets. Takes care of retransmitting packets if they are lost.

- Clock generation Generates the necessary clocks and distributes them to each DTC module.

- Trigger generation Generates the necessary trigger sequence for the SALTRO chip. Supports 3 different triggering schemes: periodic, external and via UDP write to a SRU CSR.

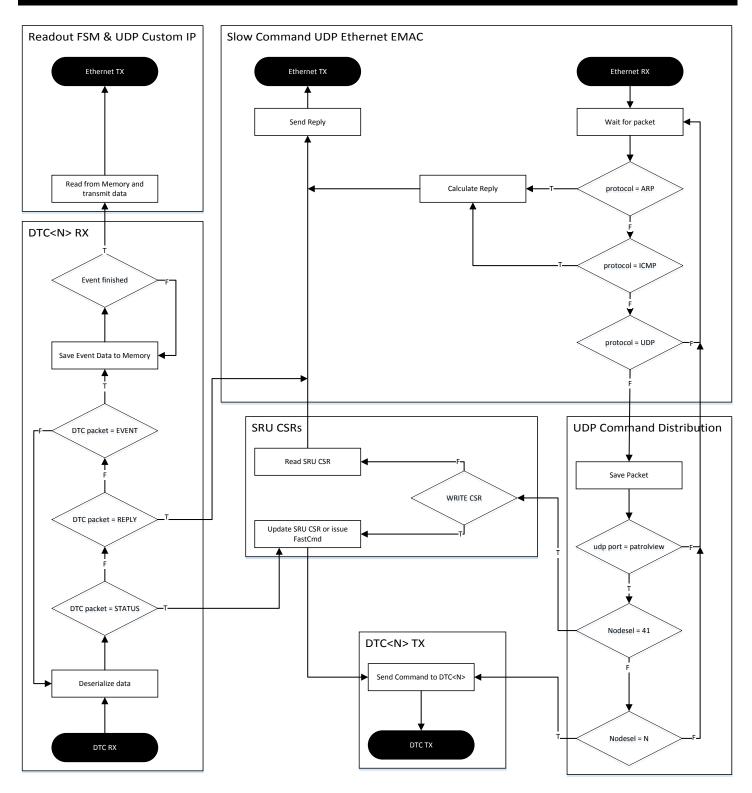

On fig. 3 is shown the ASMD diagram of the SRU.

#### Figure 3: SRU ASMD diagram.

a. CMD/STATUS UDP Ethernet EMAC and UDP command/status payload.

On table 1 is shown the frame structure of the UDP payload of a SRU control packet. This packet must be crafted by the control software.

#### Table 1: UDP payload format for the SRU command frame.

| 31             | Bit      | 0              |

|----------------|----------|----------------|

| RESERVED[10:0] |          | NodeSel[40:20] |

| RESERVED[11:0] |          | NodeSel[19:0]  |

| WR CType RESER | /ED[9:0] | Address[19:0]  |

|                |          | Data[31:0]     |

| WR CType RESER | /ED[9:0] | Address[19:0]  |

|                |          | Data[31:0]     |

|                |          |                |

| WR CType RESER | /ED[9:0] | Address[19:0]  |

|                |          | Data[31:0]     |

- Nodesel[41:0] This field has 41 active bits, corresponding to 41 slave nodes, including one SRU node and 40 DTC nodes. The 41st bit (NodeSel[40]) maps to the SRU. NodeSelH[39:20] maps to DTC39-DTC20. NodeSel[19:0] maps to DTC19-DTC0. If the corresponding bit is set, this command frame will be forwarded to the command buffers in the mapped slave DTC nodes.

- WR This specifies the command type to be performed. "1" is Read, "0" is Write.

- Ctype This bit specifies which chip the CPLD should address: "1" SALTRO, "0" CPLD.

- Address This field depends on which chip is being addressed:

- $\circ~$  For SRU and CPLD The lowest 16 bits are used as a 16 bit address.

- For SALTRO The lowest 20 bits are used as the address defined in the SALTRO specification[1].

- Data Data to be written, if write command, or 0s if read command.

- Reserved Reserved for future use. Set to Os.

Due to fifo limitations the maximum amount of commands per packet is 500.

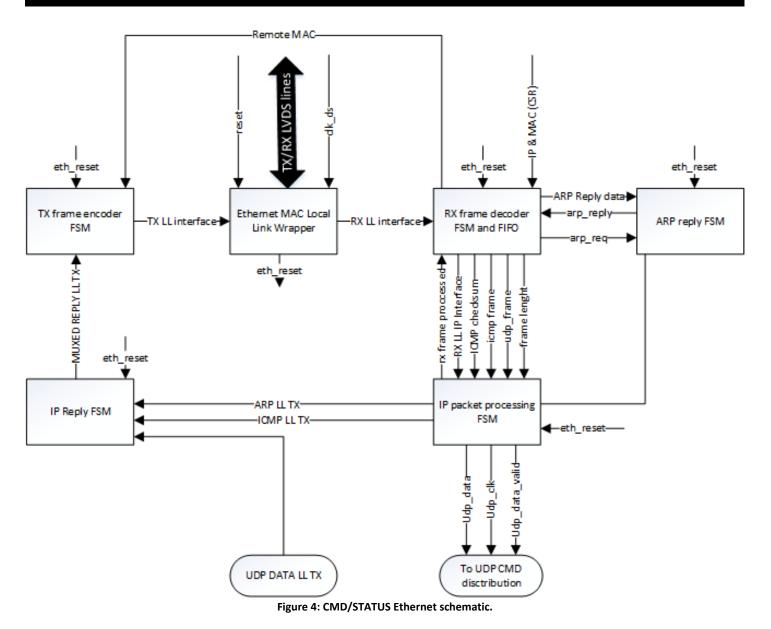

Once the command packet is send from the host computer it is received by the Ethernet CMD/Status Ethernet EMAC module in the SRU. It's schematic is shown on fig. 4. It contains the following modules:

- Ethernet EMAC & LocalLink Wrapper Generated IP core from Xilinx. Transmits/receives 8b/10b encoded signals to/from the Ethernet network. Uses 2 LocalLink interfaces for TX and RX.

- RX frame decoder FSM and FIFO. From all received packets, this module filters out only the ones addressed to specific SRU IP/MAC address and protocol. Supported protocols are UDP, ARP and ICMP. This module extracts some of the necessary data, like Source host, in order to reply correctly on an ARP or ICMP request, Frame length. Contains a FIFO in order to buffer the incoming frame.

- IP Packet processing FSMs. Contains FSMs that check if the packet frames are correct. If there is an error in the received packet it will drop it. Packages the ICMP reply data into a frame, to be transmitted, if the SRU is pinged via ICMP. Send the UDP payload for decoding of NODESEL fields.

- ARP reply FSM Packs the ARP reply data from the RX Frame Decoder into LocalLink interface.

- IP Reply FSM A FSM that select one of the 3 possible replies to send to the TX frame encoder.

- TX Frame encoder Encapsulates the reply data with the Remote MAC/IP addresses and sends it to the Ethernet Xilinx core.

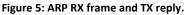

On fig. 5 is shown the ARP RX and TX frame processing. There are 3 time periods. The first one is showing the EMAC transmitting the received frame via the RX\_LL interface. It is received by the RX frame decoder and it is decoded to be an ARP request frame. During this time the reply frame is calculated. In the second period the reply frame is send to the ARP Reply FSM, by asserting arp\_req. This causes the FSM to store the frame in a FIFO and when the whole reply is stored into it, arp\_tx\_good\_frame and arp\_reply are asserted. In the third period the ARP LL TX interface is transmitting the reply frame to the TX reply mux (IP Reply FSM).

ICMP RX frame decoding and TX reply is shown on fig. 6. The reply is processed in 3 stages. In the first stage while the EMAC is transmitting the frame, the RX Frame decoder asserts icmp\_frame signal (if the protocol, ip address and packet type matches) which turns on the calculation of the ICMP checksum. The second stage starts when the final byte of the ICMP request packet is decoded. The IP packet processing FSM starts reading the FIFO soon after that. Since the header of the TX reply is known at this time, the ICMP FSM packs it into another FIFO. After a while the payload of the request packet is inserted as the payload of the reply packet and the rx\_frame\_processed signal is asserted. This releases the RX frame decoder to monitor the next incoming packet, by deasserting the icmp\_frame signal. In the third period the ICMP reply packet is transmitted to the IP reply FSM which selects a packet to be transmitted via the TX frame encoder.

| RX & CLK                     |         |      |        |             |         |       |          |          |                     |         |        |       |         |        |         |         |        |        |           |         |         |          |          |        |         |       |

|------------------------------|---------|------|--------|-------------|---------|-------|----------|----------|---------------------|---------|--------|-------|---------|--------|---------|---------|--------|--------|-----------|---------|---------|----------|----------|--------|---------|-------|

| 🧼 rxp                        | 1'h0    |      |        |             |         |       |          |          |                     |         |        |       | ועועועו |        |         |         |        |        |           |         |         |          |          |        |         |       |

| 👍 dk_ds                      | 1'h1    | າທ   | փորոր  | ກັບບານນັ້ນ  | າການແກ  | փոտո  | ການແກ    | ່າທາກກ   | ທ່ານແຫ່             | փուստ   | ທາກາກກ | MM    | າຫາກຫາກ | փոստ   | ທາການ   | ່າທາກກ  | າທາກກ  | າມມາມ  | ກັບບົບບັນ | ່າກາກກາ | ່ທາການ  | huuuu    | າທາກທ    | ່າທາກກ | ່ທາກການ | իտուն |

| EMAC RX LL Interface         |         |      |        |             |         |       |          |          |                     |         |        |       |         |        |         |         |        |        |           |         |         |          |          |        |         |       |

| ♦ rx_ll_src_rdy_n            | 1'h1    |      |        |             |         |       |          |          |                     |         |        |       |         |        |         |         |        |        |           |         |         |          |          |        |         |       |

| ♦ rx_ll_sof_n                | 1'h1    |      |        |             |         |       |          |          |                     |         |        |       |         |        |         |         |        |        |           |         |         |          |          |        |         |       |

| ♦ rx_ll_eof_n                | 1'h1    |      |        |             |         |       |          |          |                     |         |        |       |         |        |         |         |        |        |           |         |         |          |          |        |         |       |

| 🔶 rx_ll_data                 | 8'h37   | ll-C | Υ X    | 00000       | 000000  | 0000  |          |          | $\overline{\alpha}$ |         |        |       |         |        |         |         |        |        |           |         |         |          |          |        |         |       |

| 🔶 rx_ll_clock                | 1'h0    | ເມ   | ທ່ານແມ | ກ່ານນານ     | າທາກທາ  | փոտո  | ກ່ານແກ   | ່າດດວດກ  | ທ່ານແມ່ນ            | փորող   | ການແກກ | ທາກກ  | າທ່ານແມ | փոտո   | ມ່ນນານນ | ່າດດາດດ | խոսող  | haaaa  | ານນານນີ້  | ່ນທາກກາ | ່ທາກກາກ | haaaa    | ່າທາກການ | ່ທາການ | ່ທາກກາກ | փոտոի |

| ARP Interface                | _       |      | 1      | · · · · · · | 1       | 1     | 1        | [        | 1                   | 1       |        |       | 1       | 1      | 1       |         |        |        | 1         | [       | [       |          |          |        |         | 11    |

| ♦ arp_tx_reply_frame         | 224'h00 |      |        |             |         |       | X        | X        |                     |         |        |       |         |        |         |         |        |        |           |         |         |          |          |        |         |       |

| 🔶 arp_req                    | 1'h0    |      |        |             |         |       |          |          |                     |         |        |       |         |        |         |         |        |        |           |         |         |          |          |        |         |       |

| 🔶 arp_reply                  | 1'h0    |      |        |             |         |       |          |          |                     |         |        |       |         |        |         |         |        |        |           |         |         |          |          |        |         |       |

| ARP TX LL Interface          |         |      |        |             |         |       |          |          |                     |         |        |       |         |        |         |         |        |        |           |         |         |          |          |        |         |       |

| 👍 arp_tx_src_rdy_n           | 1'h1    |      |        |             |         |       |          |          |                     |         |        |       |         |        |         |         |        |        |           |         |         |          |          |        |         |       |

| 👍 arp_tx_sof_n               | 1'h1    |      |        |             |         |       |          |          |                     |         |        |       |         |        |         |         |        |        |           |         |         |          |          |        |         |       |

| 👍 arp_tx_eof_n               | 1'h1    |      |        | -           |         |       | <u> </u> |          |                     |         |        |       |         | -      |         |         |        |        | <u> </u>  |         |         |          |          |        |         |       |

| 👍 arp_tx_data_out            | 8'hxx   |      |        |             |         |       |          |          |                     |         |        |       | _       |        |         |         |        |        | +-        |         |         | $\pm nn$ | mm       | mm     | mm      | frant |

| 👍 arp_tx_dk                  | 1'h0    | hou  | וממממל | dooool      | ninnnnn | hoooo | 100000   | tinnnnnn | honod               | ihaanaa | hooood | INNNN | າທາກການ | nhonon | ומממממל | innnnn  | haaaaa | honnon | honond    | innnnn  | innnnn  |          |          |        |         |       |

| <pre>arp_tx_good_frame</pre> | 1'h0    |      |        |             |         | 1     | 1        |          |                     |         |        |       |         |        |         |         | Π      |        |           |         |         |          |          |        |         |       |

|                              | -       |      |        |             |         |       |          |          |                     |         |        |       |         |        |         |         |        |        |           |         |         |          |          |        |         |       |

Figure 6: ICMP RX Frame and TX reply.

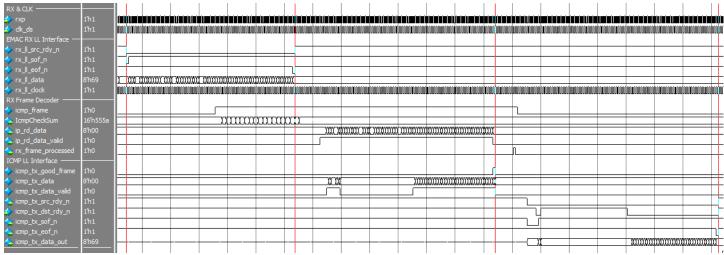

The decoding of a UDP Command packet is done very similarly to the ICMP frame. It consists of 3 periods, shown on fig. 7. While the EMAC is transmitting the packet, the frame decoder is monitoring. if the frame is using UDP and the IP and MAC addresses match, it asserts the udp\_frame signal. When the whole packet is received, the IP packet processing FSM initiates the FIFO in the decoder. A very simple UDP FSM, counts how many bytes have been received, and asserts the udp\_rx\_dv signal, which signifies the UDP packet payload. The UDP bytes are transmitted on the udp\_rxd bus. Once the frame is processed, rx\_frame\_processed is asserted, thus releasing the RX frame decoder to receive new frames.

| RX & CLK               |              |      |         |                                         |                                             |                                         |                                         |           |          |         |           |          |                                         |             |              |                                         |   |           |

|------------------------|--------------|------|---------|-----------------------------------------|---------------------------------------------|-----------------------------------------|-----------------------------------------|-----------|----------|---------|-----------|----------|-----------------------------------------|-------------|--------------|-----------------------------------------|---|-----------|

| <pre></pre>            | 1'h1<br>1'h0 |      |         |                                         | הנות היה היה היה היה היה היה היה היה היה הי |                                         |                                         |           |          |         |           |          |                                         |             |              |                                         |   |           |

| EMAC RX LL Interface — | 110          |      | UUUUUUU |                                         |                                             | 100000000000000000000000000000000000000 |                                         |           | 4000     |         |           |          |                                         |             |              |                                         |   |           |

| rx_ll_src_rdy_n        | 1'h1         |      |         |                                         |                                             |                                         |                                         |           |          |         |           |          |                                         |             |              |                                         |   | _         |

| √ rx_ll_sof_n          | 1'h1         |      |         |                                         |                                             |                                         |                                         |           | -        |         |           |          |                                         |             |              |                                         |   |           |

| ✓ rx_ll_eof_n          | 1'h1         |      |         |                                         |                                             |                                         |                                         |           | h        |         |           |          |                                         |             |              |                                         |   |           |

| 🔷 rx_ll_data           | 8'h00        |      |         |                                         | 000000000000                                |                                         |                                         |           | <u>d</u> |         |           |          |                                         |             |              |                                         |   |           |

|                        | 1'h0         | փոտո | າດທາດທາ | ່ມບົບບົບບົບເຫ                           | היייייייייייייייייייייייייייייייייייייי     |                                         | ווווווווווווווווווווווווווווווווווווווו | իորուսուն | փոս      | າທາທາທ  | Խուստոսու | າດຕາມຕາມ | խոստուս                                 | າມມາມມາມມາມ | ພາກການການການ | ווווווווווווווווווווווווווווווווווווווו |   | ստիստոս   |

| RX Frame Decoder       |              |      |         |                                         |                                             |                                         |                                         |           |          |         |           |          |                                         |             |              |                                         |   |           |

| 💠 udp_frame            | 1'h0         |      |         |                                         |                                             |                                         |                                         |           |          |         |           |          |                                         |             |              |                                         |   |           |

| 綍 ip_rd_data           | 8'h00        |      |         |                                         |                                             |                                         |                                         |           |          |         |           |          | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | 2020202     |              |                                         |   |           |

| 綍 ip_rd_data_valid     | 1'h0         |      |         |                                         |                                             |                                         |                                         |           |          |         |           |          |                                         |             |              |                                         |   |           |

| 💠 rx_frame_processed   | 1'h0         |      |         |                                         |                                             |                                         |                                         |           |          |         |           |          |                                         |             |              |                                         | 1 |           |

| UDP RX FSM             |              |      |         |                                         |                                             |                                         |                                         |           |          |         |           |          |                                         |             |              |                                         |   |           |

| 🖕 udp_rx_dk            |              | կոոտ | າດການກາ | μαααααααααααααααααααααααααααααααααααααα | היייייייייייייייייייייייייייייייייייייי     | ການການການການ                            | ບບບບບບບບບບ                              | ματατοποι | ηπη      | າທາກທາກ |           |          |                                         |             |              |                                         |   | າມປາມບາບປ |

| 💠 udp_rxd              | 8'h00        |      |         |                                         |                                             |                                         |                                         |           |          |         |           | 00000000 | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |             |              |                                         | μ |           |

| 🖕 udp_rx_dv            | 1'h0         | -    |         |                                         |                                             |                                         |                                         |           | -        |         |           |          |                                         |             |              |                                         |   |           |

|                        |              |      |         |                                         |                                             |                                         |                                         | 1         | 1        | I       | I I       |          | 1                                       | 1           |              |                                         |   | I         |

b. UDP command distribution.

After the UDP command frame is extracted from the IPv4 packet, it is received by the UDP command distribution module. There the UDP destination port is matched. The NODESEL fields are decoded and

demultiplexed into separate bus dcs\_rx\_dv[40:0]. Waveforms showing the decoding of a packet with NODESEL0 (i.e. 1st DTC board) and NODESEL40 (i.e. SRU) are shown on fig. 8 and fig. 9. The FSM takes one clock cycle to compute when to assert the dcs\_rx\_dv signal, thus the dcs\_rxd is the delayed udp\_rxd by a cycle. The first 16 bytes from the frame contain the UDP source & destination addresses, frame length and checksum. They also contain the 8 bytes encoding the NODESEL. Thus for the first 16 bytes the dcs\_rx\_dv is always kept low. Then based on what the NODESEL bits that are set in the packet, dcs\_rx\_dv[40:0] is asserted. Thus the dcs\_rxd data is driving the 40 DTC transmitters and the SRU Cmd decoder with the same data, but different "data valid" signals.

|   | RX & CLK                  |        |         |                                          |            |      |         |     |        |     |       |       |                   |       |         |         |        |        |             |         |     |          |   |

|---|---------------------------|--------|---------|------------------------------------------|------------|------|---------|-----|--------|-----|-------|-------|-------------------|-------|---------|---------|--------|--------|-------------|---------|-----|----------|---|

|   | 🖕 rxp                     | 1'h0   |         | ່ມມວກມ                                   | າຫຼາວກາວກາ |      | ໜ່ມມາມ  |     | ມາແບນແ |     | ່າມມາ | նավ   |                   | ՄՈՈՈՈ | רטטטוור | ່ມມາມາມ |        | Մուսու | וריינונווון |         |     |          |   |

|   | 🖕 dk_ds                   | 1'h1   | 1       | hu                                       | 1nn        | hur  | ւու     | hur | ഫ      |     | பி    | Ъľ    | uu                | ഫ     | hur     | inn     | hur    | ഗ്ന    | הייין       | ഫ       | תתו | ותה      | Ľ |

|   | UDP RX FSM                |        |         |                                          |            |      |         |     |        |     |       |       |                   |       |         |         |        |        |             |         |     |          |   |

|   | 🖕 udp_rx_clk<br>🦕 udp_rxd | 1'h1   |         | nn                                       | hu         |      | տո      | nnr | ഫ      | nnr | பி    | Ц     | ഫ                 | ഫ     | nr      | տո      | ŗ      | ഗ്ര    | היינו       | ഫ       | րող | עת       | Ľ |

|   | 🖕 udp_rxd                 | 8'h00  | 8       | 8'h04                                    | ) )8       | ()8) | 8'h00   |     |        | X   | )8'h0 | 0     | ) <mark>8)</mark> | ) )8  | 88      | h00 (   | 8'h00  | X I    | 8'h00 )     | 8'h00   |     |          |   |

|   | 🖕 udp_rx_dv               | 1'h0   |         |                                          |            |      |         |     |        |     |       |       |                   |       |         |         |        |        |             |         |     |          |   |

|   | DCS RX FSM                |        |         |                                          |            |      |         |     |        |     |       |       |                   |       |         |         |        |        |             |         |     |          |   |

| - | 🖕 dcs_rxd<br>🔦 dcs_rx_dv  | 8'h00  | )8      | ) () () () () () () () () () () () () () | 4 ) )8     | ()8) | ) )8'h0 | 0   |        |     |       | 8'h00 | ) (               | ) )8  | ()8)    | 8'h00   | )8'h00 |        | 8'h00       | )8)8'h0 | 0   |          |   |

|   | 🖕 dcs_rx_dv               | 41'h00 | 41'h000 | 0000000                                  | )          |      |         |     |        |     |       | 41'h0 | 00000000          | 01    |         |         |        |        |             |         |     | 41'h0000 | 0 |

| i |                           |        |         |                                          |            | 1    | 1       |     |        |     |       |       |                   |       |         |         | 1      |        |             |         |     |          |   |

Figure 8: UDP payload addressed to NODESEL0, the first DTC board.

| RX & CLK    |        |                |       |      |        |       |                       |       |      |            |        |                       |      |        |         |          |           |        |                        |                       |        |        |         |

|-------------|--------|----------------|-------|------|--------|-------|-----------------------|-------|------|------------|--------|-----------------------|------|--------|---------|----------|-----------|--------|------------------------|-----------------------|--------|--------|---------|

| 👍 rxp       | 1'h1   | ເກັນແກ່ນ       | ທິການ | արան | միրողը | ապիս  | יוונוורוונוור         | າແຫ່ກ | ШШ   |            | רושור  |                       | ήшш  | Մարսան | ורתונון | ՈՈւլալող | າໜໍ່ມີມາໜ |        | ໝ່ານການເ               | Մարու                 |        | ntinut |         |

| 👍 dk_ds     | 1'h1   | huu            | տ     | ഹ    | ហា     | սի    | M                     | സ്    | ากม่ | ww         | hur    | ww                    | ļυ   | uuu    | ԽՈ      | ൝        | സസ        | സസ     | ΨUUU                   | ww                    | huuu   | ւտ     | uuu     |

| UDP RX FSM  |        |                |       |      |        |       |                       |       |      |            |        |                       |      |        |         |          |           |        |                        |                       |        |        |         |

| 🔩 udp_rx_dk | 1'h1   | huu            | UU    | സ    | സ      | ուղ   | nnn                   | സ്    | บป   | vvv        | hun    | ഗഗ                    | ļυ   | ഗഗസ    | hu      | ൝        | ഹം        | സസ     | hυ                     | vvv                   | huuu   | ll     | uuu     |

| 👍 udp_rxd   | 8'h00  | ) <u>8</u> h04 |       |      | ) (8'h | 00    | 8'h00                 |       |      | ) )81      | 100 X  | 8'h00                 | 1)81 | 'h00   | χ       |          | ()8'h00   |        | )8hff )                | 3'h00 (               | 8'h00  |        |         |

| 🔩 udp_rx_dv | 1'h0   |                |       |      |        |       |                       |       |      |            |        |                       |      |        |         |          |           |        |                        |                       | 1      |        |         |

| DCS RX FSM  |        |                |       |      |        |       |                       |       |      |            |        |                       |      |        |         |          |           |        |                        |                       |        |        |         |

| 🔩 dcs_rxd   | 8'h00  | ) ()(8'h       | )4)   |      |        | 8'h00 | ) <mark>(8'h00</mark> |       |      | )          | )8'h00 | ) <mark>)8'h00</mark> | X    | 8'h00  |         | XXX      | ()_)8h    | 00 ) ) | ) ) <mark>8'h</mark> f | f <mark>(8'h00</mark> | )8'h00 |        |         |

| 🔩 dcs_rx_dv | 41'h00 | 41'h000000     | 00000 |      |        |       |                       |       |      | 41'h100000 | 00000  |                       |      |        |         |          |           |        |                        |                       |        | 41'h   | 0000000 |

|             |        |                |       |      |        |       |                       |       |      |            |        |                       | 1    |        | 1       |          | 1         |        |                        |                       | 1      |        |         |

Figure 9: UDP payload addressed to NODESEL40, the SRU.

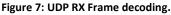

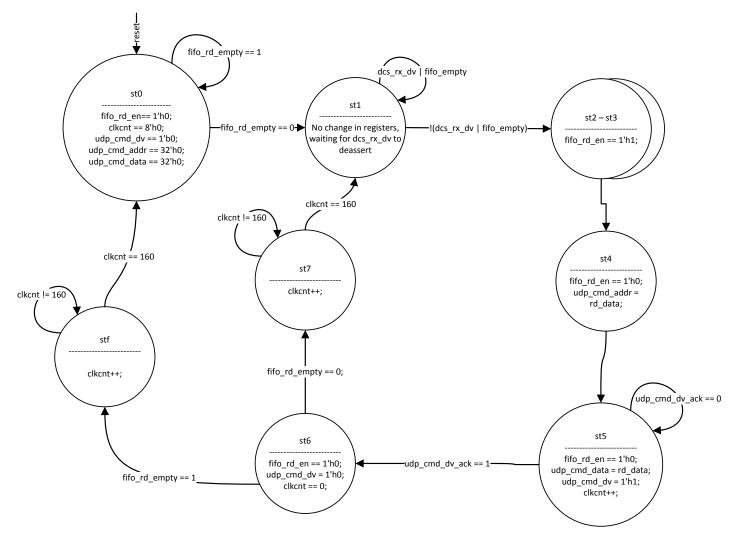

### c. DCS command decoder

In order to support broadcasting read/write operations to 40 DTC boards each of the DTC link must have its own command decoder. The block diagram of the DCS command decoder is shown on fig. 10. It consists of a FIFO and an FSM. The FIFO is used to cross into the DTC clock domain and to store the commands from the packet, since the DTC link is orders of magnitude slower than Ethernet. The FSM reads 2 32bit words, containing the address and the data respectfully. The State diagram of the FSM is shown on fig. 11.

Figure 10: DCS command decoder block diagram.

The FSM initializes in st0, and waits until the FIFO is not empty to proceed to st1. St1 is a state where the UDP frame payload must be fully loaded into the FIFO, this ensures that there is always even number or 32 bit words in the FIFO. During st2 and st3, a single command containing 32bit address and data is readout, to the transmitter. Since the FSM is Moore and the FIFO has 1 cycle RD delay in st4 & st5 the udp\_cmd\_addr and udp\_cmd\_data are available to be assigned. In st5 udp\_cmd\_dv is asserted, signaling

the DTC TX Serializer that there is a command valid and ready to transmit. When the DTC TX Serializer is starting to transmit the command, it asserts udp\_cmd\_ack, releasing the FSM into st6, which select which 2 watchdog states it should go into, based on if this was the last command in the FIFO. The watchdog is set to 160 cycles, since it takes a little over 128 cycles to transmit a command.

Figure 11: DCS Command decoder FSM state diagram.

On fig. 12 waveforms of filling the FIFO with a UDP frame payload (containing 2 command) from the DCS command distribution module, are shown. Soon after the first command is transmitted, followed by the second one in a while.

Figure 12: DCS Command decoder – waveforms.

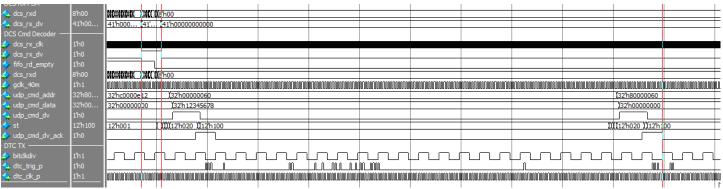

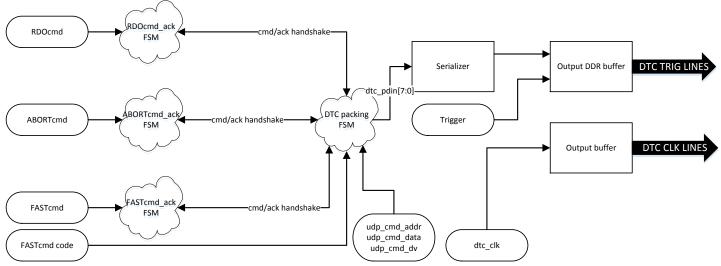

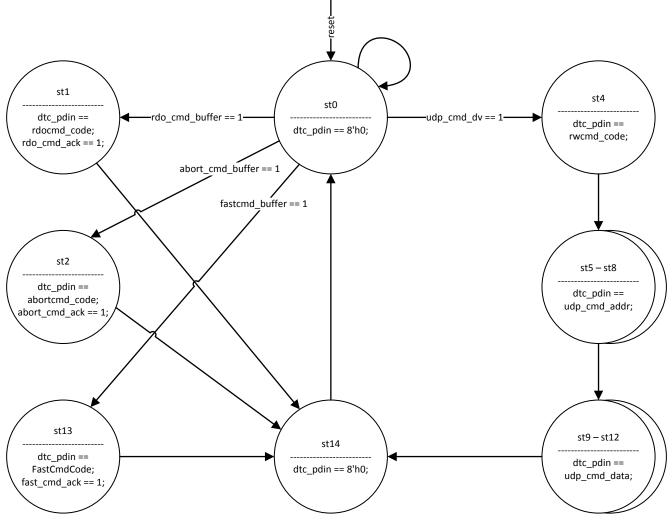

## d. DTC TX

In order to support the 3 types of DTC commands [2] (Trigger, Slow Control Commands and Fast Commands), the DTC TX module is connected to the three modules that issue them. To the DCS command decoder – when issuing a CSR write/read command; The SRU CSR module – when a fast command is issued; the trigger generation unit when triggering and abort command needs to be issued. The block diagram is shown on fig. 13. It consists of a DTC packing FSM, 3 smaller FSMs which convert the command pulses to a handshake interface, a serializer and output buffers. The handshake interface is required in order to ensure the command will be executed, if the FSM is busy with another command.

Figure 13: DTC TX block diagram.

The FSM diagram is shown on fig. 15. The FSM initializes in st0 and wait until a valid command is issued. Based on which command is executed, it enters st1, st2, st4 or st13. In st1, st2 and st13, the corresponding command code is asserted on dtc\_pdin[7:0]. When entering st4, the read/write command code is asserted and then the next 8 states are used to assert the 2 32bit words for address and data. A complete waveform is shown on fig. 14. In the first period the read/write header code (0xE1) is asserted, then in the second period the address, and in the third – the data is asserted. At the end of the waveform, it just so happens there is a trigger sent unrelated to the CSR command.

| DTC TX           |          |        |           |        |        | 1      |            |           |             |     |         |             |          |                         |     |         |          |        |        |        |        |       |      |     |         |    |

|------------------|----------|--------|-----------|--------|--------|--------|------------|-----------|-------------|-----|---------|-------------|----------|-------------------------|-----|---------|----------|--------|--------|--------|--------|-------|------|-----|---------|----|

| 🔙 udp_cmd_addr   | 32'h00   | 32'    | 32'h0000  | 060    |        |        |            |           |             |     |         |             |          |                         |     |         |          |        |        |        |        |       | 1    |     |         | _  |

| 👍 udp_cmd_data   | 32'h12   | 32'h., | . 32h1234 | 5678   |        |        |            |           |             |     |         |             |          |                         |     |         |          |        |        |        |        |       | i    |     |         | -  |

| 🖕 udp_cmd_dv     | 1'h0     |        |           |        |        |        |            |           |             |     |         |             |          |                         |     |         |          |        |        |        |        |       |      |     |         | _  |

| 🔶 st             | 15'h0001 | 15'h0. | (15'h001  | 0 (15" | 10020  | 15'h00 | 40 (15'h00 | 80 (15'h0 | 100 (15'h0: | 00  | (15'h0- | 100 (15'h08 | 00 (15h1 | 00 (15 <sup>°</sup> h40 | 00  | (15'h00 | 01       |        |        |        |        |       | l i  |     |         | _  |

| 🍫 udp_cmd_dv_ack | 1'h0     |        |           |        |        |        |            |           |             |     |         |             |          |                         |     |         |          |        |        |        |        |       |      |     |         | _  |

| 👍 bitclkdiv      | 1'h1     |        |           |        | ᠇ᢩ᠘    |        |            |           |             |     |         |             |          |                         |     |         |          |        |        |        |        |       |      |     |         | _  |

| 🔷 dtc_pdin       | 8'h00    | 8'h00  |           | 8'he   | -1     | 8'h00  |            |           | 8'h60       |     | 8'h12   | 8'h34       | 8'h56    | 8'h78                   |     | 8'h00   |          |        |        |        |        |       | 1    |     |         | _  |

| 👍 FeeTrig        | 1'h0     |        |           |        |        |        |            |           |             |     |         |             |          |                         |     |         |          |        |        |        |        |       | L I  |     |         |    |

| 🖕 dtc_clk_p      | 1'h1     | mm     | տուտի     | ուխո   | າທຸການ | ່ມແກ   | ການແກ      | huuuu     | ທ່ານແບບທ    | hn  | ່າທາກ   | ່ນແບບເບ     | իսոսոս   | າດດາດດາ                 | າກກ | າທາທ    | սոսու    | տուսու | າທາທາກ | ການແນນ | huuunn | ການແກ | huuu | ທາກ | າທາກການ | Ū. |

| 👍 dtc_trig_p     | 1'h0     |        |           |        | ிஸ்ட   | Lı     |            |           |             | hn_ |         |             |          |                         | າທ  | 1       |          |        |        |        |        |       |      |     |         | _  |

|                  |          |        |           |        |        |        |            |           |             | I – |         |             |          | [                       |     |         |          |        |        |        |        |       |      |     |         |    |

|                  |          |        |           |        |        | iaur   | o 1/1 - I  | Dood V    | Vrito c     | ~~  | m -     | nd cor      | ializati | on and                  | 4 T | riaa    | or 14/21 | oform  |        |        |        |       |      |     |         |    |

Figure 14: Read Write command serialization and Trigger waveforms.

The dtc\_pdin[7:0] gets serialized and that signal is driving the Output DDR buffer on negedge, while the Trigger (FeeTrig) is driving it on the posedge, thus the DTC TX transfer is completed [2]. The 40 MHz dtc\_clk is directly driving the DTC CLK lanes.

Figure 15: DTC TX FSM state diagram.

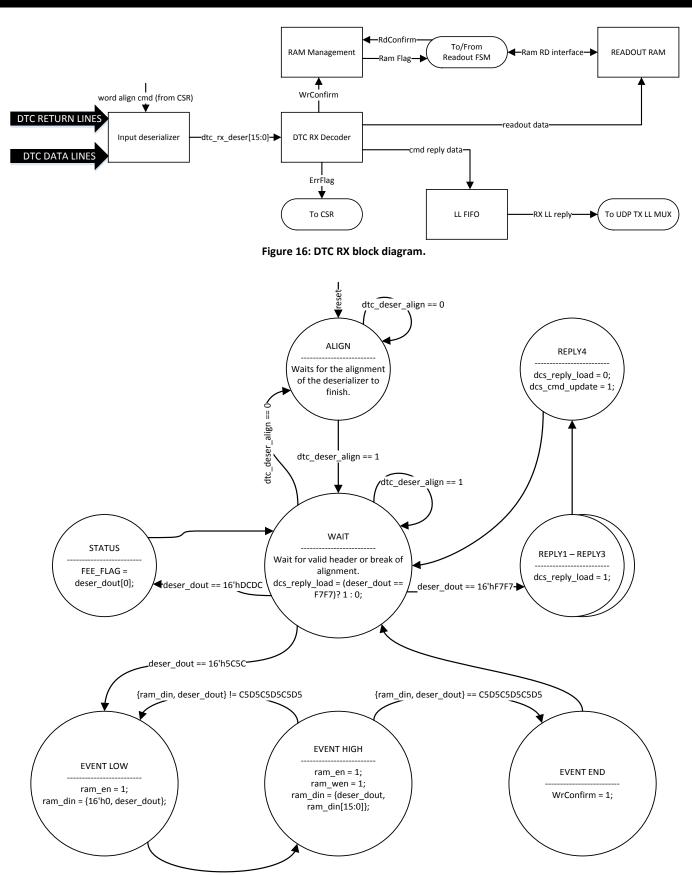

## e. DTC RX (Deserializer and Memory)

The DTC protocol has 3 different packets [2] that are sent from the CPLD. The block diagram of the DTC RX module is shown on fig. 16. The data is deserialized and send to the DTX RX Decoder. It is an FSM whose state diagram is shown on fig. 17. In order to receive correct data, the serializer must be aligned to the sync word "0xBC50". This is done in the ALIGN state. Once that is done, the Decoder enters WAIT state. Once a valid frame header is detected, it proceeds to the corresponding branch: STATUS, REPLY or EVENT. In the STATUS branch, just the LSB bit is used, it signifies if the SALTRO chip has asserted the ERROR flag. The REPLY branch consists of 4 stages, used to get the two 32bit words reply: address and data from a CSR read command. In the EVENT branch, every 2 cycles it writes to the memory a single 32 bit word, until the trailer is detected. Once the end of the event frame is detected, the Decoder signals to the Ram Management that the writing to the ram has finished. The Ram Management asserts RamFlag, which will stay high, until the Readout FSM asserts RdConfirm, when the final word was readout.

Figure 17: DTC RX Decoder state diagram.

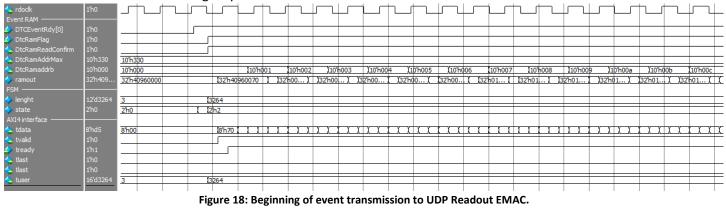

f. UDP Readout FSM and UDP EMAC.

A temporary FSM is implemented in order to convert the readout of a single DTC board to AXI4 stream interface used by the Readout UDP EMAC, which is already synthesized IP, from another project.

In the beginning of a packet transfer shown on fig. 18 the FSM calculates the total amount of data in bytes that will be transferred and asserts it on the tuser input of the AXI interface. Tvalid is asserted, when the first byte is ready to be transmitted. After a while tready is asserted by the EMAC. The transfer continues by sending a new byte each cycle as long as tready is high. When the last byte is to be transmitted, tlast is asserted for a single cycle and tvalid is deasserted.

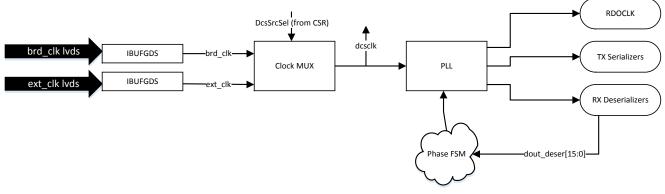

g. Clock Generation

The SRU supports clocks from external source or from on-board XTAL. The block diagram is shown on fig. 19. The LVDS clock lines come from their corresponding pads, and are buffered by an IBUFGS. Then a clock mux can be programmed by software by writing a CSR to switch to the external clock. The dcsclk output is used only when booting up, to drive the flash controller that programs the FPGA.

Figure 19: Clock generation block diagram.

After the clock mux locks, the PLL starts locking and asserts SerClkLockSt when locked. After this point the clocks are stable and can be used by the TX Serializers and the RX Deserializers. On fig. 20 is shown the simulation power up and locking of the clock generation circuit. Since it's crucial that the CPLD boards are triggered at the same moment, the TX serializer clocks' phase is constant and cannot be changed. The RX deserializer clocks' phase is tunable using an FSM and using the data feedback from the serializers. Though this functionality has not been tested as part of this project.

| · Clock Generator   |      |   |            |       |       |        |        |          |        |                                           | L                                      |        |       |          |        |        |       |

|---------------------|------|---|------------|-------|-------|--------|--------|----------|--------|-------------------------------------------|----------------------------------------|--------|-------|----------|--------|--------|-------|

| 👍 brdclk_p          | 1'h1 |   |            |       |       |        |        | hamanan  | muuuum | , ann an | )))))))))))))))))))))))))))))))))))))) |        |       |          |        |        |       |

| 👍 pllckin 1_p       | 1'h0 | L |            |       |       |        |        |          |        |                                           |                                        |        |       |          |        |        |       |

| 👍 RdoClkSel         | 1'h1 |   |            |       |       |        |        |          |        |                                           | i                                      |        |       |          |        |        |       |

| 🖕 dcsclk            | 1'h1 |   | <br>խուսու | ստուս | ստուս | տուսու | խուսու | ມາການການ | huuuuu | աստան                                     | տուղ                                   | າທາການ | ուսու | ການແມ    | խուսու | hhhhhh | www   |

| 👍 rdoclk            | 1'h1 |   |            |       |       |        |        | ມາການການ | huuuuu | խուսուտի                                  | սույ                                   | ການແມ  | ուսու | ກາດແບບເປ | խուսու | hhhhhh | www   |

| 👍 SerBitclk[0]      | 1'h1 | L |            |       |       |        |        | ມາການການ | huuuuu | ատուստ                                    | տուղ                                   | mmm    | ուսու | ການນານ   | խուսող | hunnun | nnnnn |

| 👍 SerBitclkDiv[0]   | 1'h0 |   |            |       |       |        |        |          |        |                                           |                                        |        |       |          |        |        |       |

| 👍 DeserBitclk[0]    | 1'h1 |   |            |       |       |        |        | ມາການການ | huuuuu | ատուտ                                     | տուղ                                   | huuuuu | ուսու | ການແມ    | խուսու | hunnun | www   |

| 👍 DeserBitclkDiv[0] | 1'h0 |   |            |       |       |        |        | ייייו    | hund   |                                           |                                        | hund   | ഫ     | ערען     | זרתן   |        |       |

| 👍 DcsClkLockSt      | 1'h1 |   |            |       |       |        |        |          |        |                                           | i                                      |        |       |          |        |        |       |

| 👍 SerClkLockSt      | 1'h1 | L |            |       |       |        |        |          |        |                                           | J                                      |        |       |          |        |        |       |

|                     |      |   |            |       |       |        |        |          |        |                                           |                                        |        |       |          |        |        |       |

Figure 20: Power-up simulation of the clock generator.

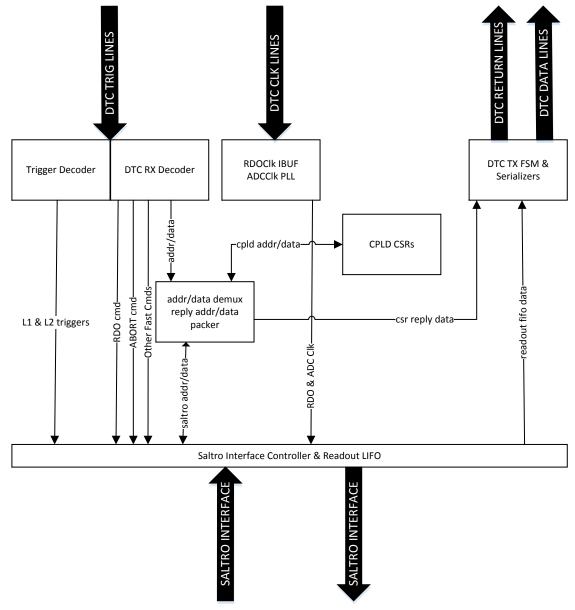

# III. Implementation of the CPLD:

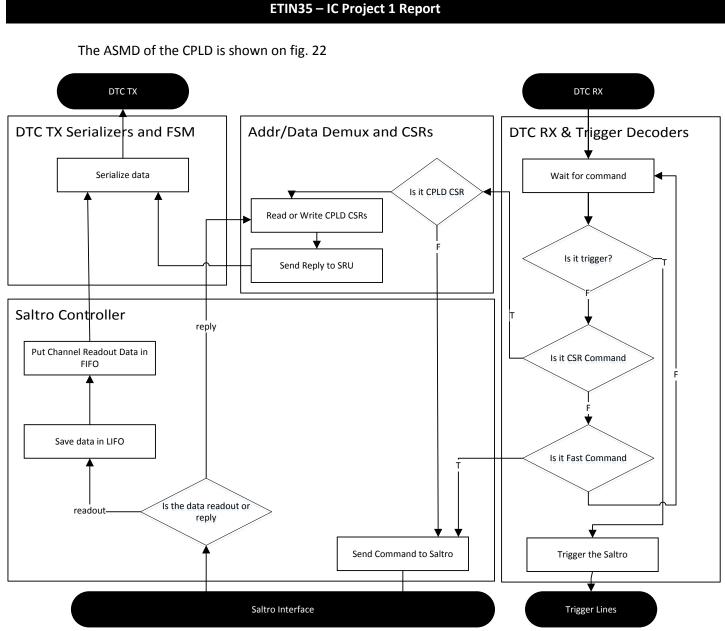

The CPLD architecture is shown on fig. 21. The main functional block are:

- RDOClk input buffer and ADCClk PLL– This module converts the LVDS DTC Clk into single line RDOClk and from it a PLL generated the ADCClk sampling clock which is 2x or 4x slower than the RDOClk.

- DTC RX decoder Decodes the DTC command on the DTC trig line. If it is a Write or Read CSR, it will be sent to the Cmd/Data demux. If it's a fast command it will send it to the Saltro Controller.

- Trigger decode Decodes the Trigger command, and toggles the L1 & L2 lines respectfully.

- Cmd and data demux, Reply data packer Distributes the Address/Data lines according to where they

are for, the CPLD CSRs or the SALTRO chips. Also packs the reply data when a read command is

executed.

- CPLD CSRs Control Status registers for the CPLD.

- Saltro Interface controller & Readout LIFO Converts the commands in the Saltro interface format. Also converts the readout data format using a 40 bit wide LIFO and a 32 bit wide FIFO and sends it to the DTC TX FSM.

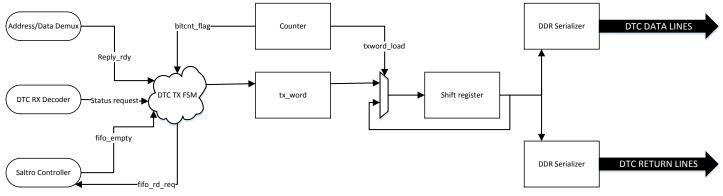

- DTC TX FSM and Serializers An FSM drives 2 DDR serializers which are transmitting readout or reply data on the DTC data/return lines.

Figure 21: CPLD Architecture.

Figure 22: CPLD ASMD Diagram.

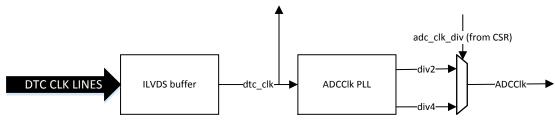

a. RDOClk and ADC clock

The CPLD works on 40 MHz RDOClk which is the same a the DTC clock. In order to control the resolution vs sampling time, the ADC clock can be 2 times or 4 times slower than the RDO clock. The block diagram of the clock generation is shown on fig. 23.

Figure 23: ADC clock PLL and DTC clock buffer.

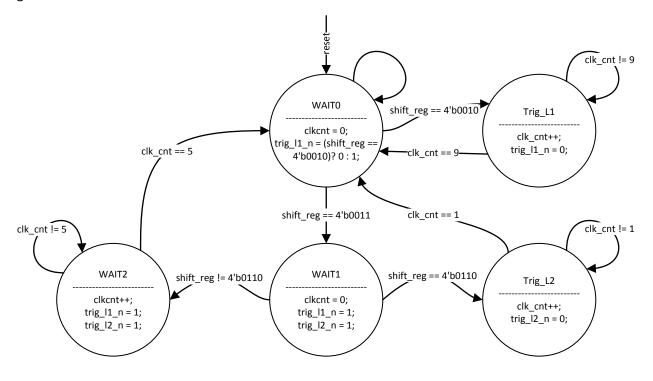

b. Trigger Detection

The trigger sequence is detected by a detector, which consists of a shift register sampling the dtc\_trig line on **negedge**. Then the output of it is monitored by an FSM, which generated the L1 and L2 trigger. The state diagram is shown on fig. 24. The FSM's initial state is WAITO. When the shift\_reg has a value of "0x2"

it means that it has received a L1 trigger. Thus it asserts it on the next cycle, and enters Trig\_L1 state, where L1 trigger is hold low for another 10 clock cycles and then returns to the initial state.

When the shift\_reg is "3", the FSM changes state to WAIT1 where it detects if the L2 trigger is received or there was an error in the trigger command. If a valid L2 trigger is received it enters Trig\_L2 state, where trig\_l2\_n is asserted for 2 cycles. If the trigger was not valid in WAIT1 state, the FSM enters WAIT3 state. There a small timeout is added in order to ignore the false trigger. Since the trigger data is the only data sent on negedge, it can be sent together with a Slow or Fast command, an example of which is shown on fig. 25.

Figure 24: CPLD Trigger decode FSM.

| DTC Trigger Decode - | _    |      |                                         |     |                                         |                                         |                                         |               |                                         |                                         |    |                                         |                                         |                                                                                                                 |         |

|----------------------|------|------|-----------------------------------------|-----|-----------------------------------------|-----------------------------------------|-----------------------------------------|---------------|-----------------------------------------|-----------------------------------------|----|-----------------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------|---------|

| 🍫 dtc_clk            | 1'h1 |      | 000000000000000000000000000000000000000 |     | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000 | 0.0000000000000000000000000000000000000 |               | 000000000000000000000000000000000000000 | 0.0000000000000000000000000000000000000 |    | 000000000000000000000000000000000000000 | ,00000,00000000000000000000000000000000 | 0,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,0 | 0000000 |

| 🍫 dtc_trig           | 1'h0 |      |                                         |     |                                         |                                         |                                         |               |                                         |                                         |    |                                         |                                         |                                                                                                                 |         |

| 🔶 shift_reg          | 4'h0 | 4'h0 | )))))4'h0                               |     |                                         |                                         |                                         |               |                                         |                                         |    |                                         | )))))                                   | )4'h0                                                                                                           |         |

| 🔶 st                 | 3'h0 | 3'h0 | ),3'h1 ),                               | 'h0 |                                         |                                         |                                         |               |                                         |                                         |    |                                         | ) X                                     | 3'h0                                                                                                            |         |

| 🖕 trig_l 1n          | 1'h1 |      |                                         |     |                                         |                                         |                                         |               |                                         |                                         |    |                                         |                                         |                                                                                                                 |         |

| 🖕 trig_l2n           | 1'h1 |      |                                         |     |                                         |                                         |                                         |               |                                         |                                         |    |                                         | 1                                       |                                                                                                                 |         |

|                      |      |      |                                         |     |                                         |                                         |                                         |               |                                         |                                         |    |                                         |                                         |                                                                                                                 |         |

|                      |      |      |                                         | E   | 2F. T.                                  |                                         |                                         | م الماء معر م | of WD /DD                               |                                         | ام |                                         |                                         |                                                                                                                 |         |

Figure 25: Trigger detection in the middle of WR/RD command.

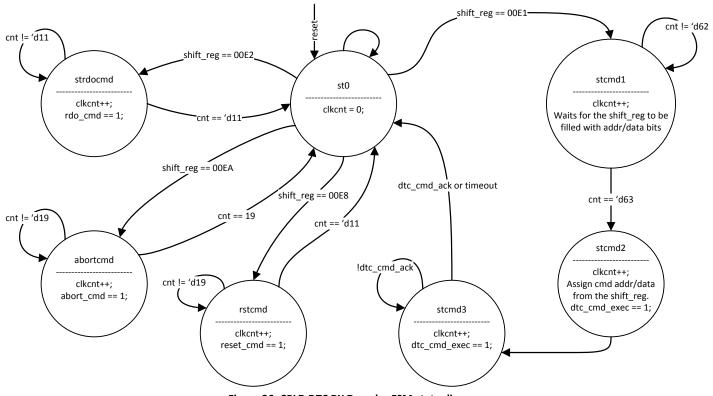

#### c. DTC RX Decoder

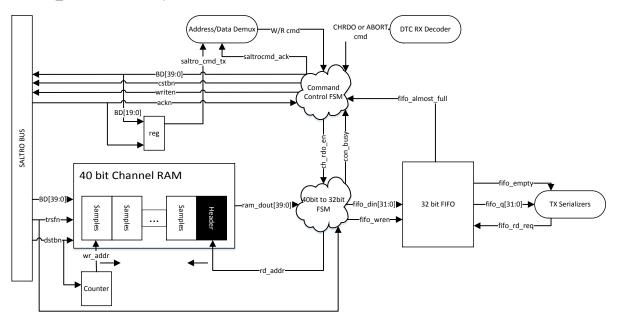

The DTC RX decoder is implemented similarly to the Trigger decoder. The dtc\_trig line is sampled on **posedge** by a shift register which trigger the FSM, that decodes the command. On fig.26 the state diagram of the FSM is shown. It initializes in st0, in which it waits to receive a valid header code in the shift\_reg. If any of the 3 fast commands (channel readout, abort or reset) are received, the FSM enters the corresponding state and asserts the specific command flag and return to the initial state. If a slow WR/RD command header is received, the FSM enters stcmd1 state, where it waits for the shift\_reg to receive the address, data, Ctype and WriteRead flag. Then it enters stcmd2, where it asserts dtc\_cmd\_exec and the address, data etc. fields. It waits in stcmd3 state until a dtc\_cmd\_ack is received from the cmd demux.

Figure 26: CPLD DTC RX Decoder FSM state diagram.

## d. Address/Data demux and Reply packer.

When the RX Decoder receives a Write/Read command, based on the Ctype (dtc\_cmd\_feenal) the demux module sends the command to the CPLD CSRs or the Saltro Interface Controller. On fig.27 and fig.28 are shown waveforms of Read and Write to the CPLD and to the SALTRO.

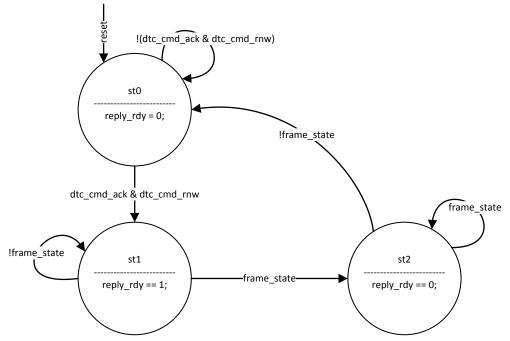

When a RD command is executed and an ack is returned by ether the CPLD CSRs or the SALTRO Controller, and the command is READ, a small FSM shown on fig.29 is triggered. It asserts reply\_ready. Which in turn triggers the DTC TX FSM to start transmitting the reply data. While the TX FSM Is transmitting the data frame\_state is kept high, thus ensuring the CPLD will not send another reply\_rdy request in that time. This handshake is shown on fig.30.

| 🔶 dtc_clk            | 1'h0<br>1'h0 | տուփոտո            | տվկնուտ | միստույ           | սուսու | իսուստի | ມົບບານ | ທທິທທິທ | ໜູ່ໜູ | ທີ່ມີນີ້ນນີ້ນີ້ນ | huuun | hhhhhh    | hunnun     | փուռում | hΜ        |

|----------------------|--------------|--------------------|---------|-------------------|--------|---------|--------|---------|-------|------------------|-------|-----------|------------|---------|-----------|

| dtc_trig             | 1'h0         |                    |         | JЦ <mark>.</mark> |        |         | M      |         |       | ᆛᄕᆣᄔᄕ            |       |           |            |         | +         |

| DTC RX Decoder       |              |                    |         |                   |        |         |        |         |       |                  |       |           |            |         |           |

| shift_reg            | 80'h0000     | 80'h00000000000000 | <u></u> |                   | μιππ   | μιμυ    |        |         |       |                  |       |           |            |         | ull       |

| 🔷 st                 | 4'h0         | 4'h0               |         | )#'h4             |        |         |        |         |       |                  | χ     | 4'h6      | <u>)41</u> | 0       | +         |

| 🖕 dtc_cmd_exec       | 1'h0         |                    |         |                   |        |         |        |         |       |                  |       |           | 4          |         | +         |

| 🖕 dtc_cmd_rnw        | 1'h1         |                    |         |                   |        |         |        |         |       |                  |       |           |            |         | +         |

| 🖕 dtc_cmd_feenal     | 1'h0         |                    |         |                   |        |         |        |         |       |                  |       |           |            |         |           |

| 🖕 dtc_cmd_addr       | 20'h00020    | 20'h00e12          |         |                   |        |         |        |         |       |                  |       | 20'h00060 |            |         |           |

| 🖕 dtc_cmd_data       | 20'h00000    | 20'h00000          |         |                   |        |         |        |         |       |                  |       | 20'h45678 |            |         | +         |

| 🐓 dtc_cmd_ack        | 1'h0         |                    |         |                   |        |         |        |         |       |                  |       | ļ         |            |         | +         |

| CPLD CSR Interface - |              |                    |         |                   |        |         |        |         |       |                  |       |           |            |         |           |

| 🖕 cpld_cmd_exec      | 1'h0         |                    |         |                   |        |         |        |         |       |                  |       | -         | 1 1        |         | +         |

| 🖕 cpld_cmd_rnw       | 1'h1         |                    |         |                   |        |         |        |         |       |                  |       |           |            |         |           |

| 🖕 cpld_cmd_addr      | 8'h20        | 8'h12              |         |                   |        |         |        |         |       |                  |       | 8'h60     |            |         |           |

| 🖕 cpld_cmd_wdata     | 16'h0000     | 16'h0000           |         |                   |        |         |        |         |       |                  |       | 16'h5678  |            |         |           |

| 🐤 cpld_cmd_rdata     | 16'h8834     | 16'h0000           |         |                   |        |         |        |         |       |                  |       |           |            |         |           |

| 🐤 cpld_cmd_ack       | 1'h0         |                    |         |                   |        |         |        |         |       |                  |       |           |            |         | +         |

| SALTRO CMD Interfac  |              |                    |         |                   |        |         |        |         |       |                  |       |           |            |         |           |

| 🖕 saltro_cmd_exec    | 1'h0         |                    |         |                   |        |         |        |         |       |                  |       |           |            |         | +         |

| 🖕 saltro_cmd_rw      | 1'h1         |                    |         |                   |        |         |        |         |       |                  |       | ļ         |            |         |           |

| 🖕 saltro_cmd_addr    | 20'h00020    | 20'h00e12          |         |                   |        |         |        |         |       |                  |       | 20'h00060 |            |         | =         |

| 🖕 saltro_cmd_rx      | 20'h00000    | 20'h00000          |         |                   |        |         |        |         |       |                  |       | 20'h45678 |            |         | $\square$ |

| 🐤 saltro_cmd_tx      | 20'hzzzzz    | 20'h05500          |         |                   |        |         |        |         |       |                  |       | ļ.        |            |         |           |

| 🐤 saltro_cmd_ack     | 1'h0         |                    |         |                   |        |         |        |         |       |                  |       |           |            |         |           |

Figure 27: Write CPLD CSR command waveforms .

| 🐓 dtc_clk            | 1'h0                  | huuuu         | hhhhhhh     | hhunnun | փուսում  | սույ | huuuu | huuuu   | huuuuu | փուստու | huuuuu | hnnn | Muuuuu    | huuuu     | huuuuut  | ໜ |

|----------------------|-----------------------|---------------|-------------|---------|----------|------|-------|---------|--------|---------|--------|------|-----------|-----------|----------|---|

| dtc_trig             | 1'h0                  |               |             | իրոՈ    | <u>h</u> |      |       |         |        |         |        |      |           |           |          |   |

| DTC RX Decoder       |                       |               |             |         |          |      |       |         |        |         |        |      |           |           |          |   |

| 🔷 shift_reg          | 80'h <del>4</del> 000 | 80'h000000000 | 00000000000 |         |          |      |       | 0000000 |        | 0000000 |        |      |           | 00000000  | 10000000 | œ |

| 🔶 st                 | 4'h0                  | 4'h0          |             |         | )(4'h4   |      |       |         |        |         |        | Ι X  | 4'h6      | )4'h0     |          | _ |

| 🖕 dtc_cmd_exec       | 1'h0                  |               |             |         |          |      |       |         |        |         |        |      |           |           |          |   |

| 🖕 dtc_cmd_rnw        | 1'h1                  |               |             |         |          |      |       |         |        |         |        |      | 1         |           |          |   |

| 🖕 dtc_cmd_feenal     | 1'h1                  |               |             |         |          |      |       |         |        |         |        |      | 1         |           |          | — |

| 🖕 dtc_cmd_addr       | 20'h00e12             | 20'h00e10     |             |         |          |      |       |         |        |         |        |      | 20'h00e12 |           |          | _ |

| 🖕 dtc_cmd_data       | 20'h00000             | 20'h00000     |             |         |          |      |       |         |        |         |        |      |           |           |          | _ |

| 💠 dtc_cmd_ack        | 1'h0                  |               |             |         |          |      |       |         |        |         |        |      |           |           |          |   |

| CPLD CSR Interface - |                       |               |             |         |          |      |       |         |        |         |        |      |           |           |          |   |

| 🔩 cpld_cmd_exec      | 1'h0                  |               |             |         |          |      |       |         |        |         |        |      |           |           |          |   |

| 🖕 cpld_cmd_rnw       | 1'h1                  |               |             | 1       |          |      |       |         |        |         |        |      | 1         |           |          | _ |

| 🔩 cpld_cmd_addr      | 8'h12                 | 8h10          |             |         |          |      |       |         |        |         |        |      | 8'h12     |           |          | _ |

| 🔩 cpld_cmd_wdata     | 16'h0000              | 16'h0000      |             |         |          |      |       |         |        |         |        |      |           |           |          | _ |

| 🧇 cpld_cmd_rdata     | 16'h0000              | 16'h0000      |             |         |          |      |       |         |        |         |        |      |           |           |          | _ |

| 🧇 cpld_cmd_ack       | 1'h0                  |               |             |         |          |      |       |         |        |         |        |      |           |           |          |   |

| SALTRO CMD Interfac  |                       |               |             |         |          |      |       |         |        |         |        |      |           |           |          |   |

| 🔩 saltro_cmd_exec    | 1'h0                  |               |             |         |          |      |       |         |        |         |        |      |           |           |          |   |

| 🔩 saltro_cmd_rw      | 1'h1                  |               |             |         |          |      |       |         |        |         |        |      |           |           |          | _ |

| 📥 saltro_cmd_addr    | 20'h00e12             | 20'h00e10     |             |         |          |      |       |         |        |         |        |      | 20'h00e12 |           |          |   |

| 🖕 saltro_cmd_rx      | 20'h00000             | 20'h00000     |             |         |          |      |       |         |        |         |        |      |           |           |          | _ |

| 🤣 saltro_cmd_tx      | 20'h05500             | 20'h05500     |             |         |          |      |       |         |        |         |        |      |           | 20'h05500 |          |   |

| 🧇 saltro_cmd_ack     | 1'h0                  |               |             |         |          |      |       |         |        |         |        |      |           |           |          |   |

|                      |                       |               |             |         |          |      |       |         |        |         |        |      |           |           |          |   |

| 🍫 dtc_dk               | 1'h0      | whomonou               | าโกกการการไ | hnnnnn       | հոռոռող    | հոռոռու        | haaaaa | haaaaa | իոռոռող     | hnnnnn            | hannana  | hannan | haaaaaa | hnnnn    |

|------------------------|-----------|------------------------|-------------|--------------|------------|----------------|--------|--------|-------------|-------------------|----------|--------|---------|----------|

| dtc_trig               | 1'h0      |                        | I           |              |            |                |        |        |             |                   |          |        |         |          |

| DTC RX Decoder         |           |                        |             |              |            |                |        |        |             |                   |          |        |         | 1        |

| 🔶 shift_reg            | 80'h0000  |                        | מססממולו    | בככבבכבב     |            |                |        |        | )80h        | 00000000000000000 | 000000   |        |         |          |

| 🔶 st                   | 4'h0      | 4h4                    |             | 4'h6         | )4'h0      |                |        |        |             |                   |          |        |         |          |

| 💠 dtc_cmd_exec         | 1'h0      |                        |             |              |            |                |        |        |             |                   |          |        |         | L        |

| 💠 dtc_cmd_rnw          | 1'h1      |                        |             |              |            |                |        |        |             |                   |          |        |         |          |

| 綍 dtc_cmd_ack          | 1'h0      |                        |             |              |            | 1              |        |        |             |                   |          |        |         | L        |

| SALTRO CMD Interface   |           |                        |             |              |            |                |        |        |             |                   |          |        |         | 1        |

| 🖕 saltro_cmd_exec      | 1'h0      |                        |             |              |            |                |        |        |             |                   |          |        |         | L        |

| 🖕 saltro_cmd_rw        | 1'h1      |                        |             |              |            |                |        |        |             |                   |          |        |         |          |

| 🖕 saltro_cmd_addr      | 20'h00020 | 20'h00e10              | )           | 20'h00e12    |            |                |        |        |             |                   |          |        |         |          |

| 🖕 saltro_cmd_rx        | 20'h00000 | 20 <sup>°</sup> h00000 |             |              |            |                |        |        |             |                   |          |        |         |          |

| 🤣 saltro_cmd_tx        | 20'hzzzzz | 20h05500               |             |              | (20'h05500 |                |        |        |             |                   |          |        |         |          |

| 🤣 saltro_cmd_ack       | 1'h0      |                        |             |              |            | <u> </u>       |        |        |             |                   |          |        |         | L        |

| Read reply Interface — |           |                        |             |              |            |                |        |        |             |                   |          |        |         |          |

| 💠 reply_addr           | 32'h8000  | 32hc0000e10            |             | 32'hc0000e12 |            |                |        |        |             |                   |          |        |         |          |

| 💠 reply_data           | 32'h0000  | 32h00005500            |             |              | 32'h000055 | bo             |        |        |             |                   |          |        |         |          |

| 💠 reply_rdy            | 1'h0      |                        |             |              |            |                |        |        |             |                   |          |        |         | <u> </u> |

| 💠 frame_st             | 1'h0      |                        |             |              |            |                |        |        |             |                   |          |        |         |          |

| 🔷 st                   | 2'h0      | 2'h0                   |             |              | ,2'h1      | 2'h2           |        |        | <u>2'h0</u> |                   |          |        |         | <u> </u> |

| DTC TX                 |           |                        |             |              |            |                |        |        |             |                   |          |        |         |          |

| 🔷 dtc_return           | 1'h0      |                        |             |              |            |                | 빋╹╹└   | ليت ا  |             |                   | <u> </u> |        | 빋ᆜᆜ     |          |

| 🔷 dtc_data             | 1'h1      | חחרולרו                | μшиш        | рылы         | рылы       | рылы.          | րո լ   |        |             | рстаст.           |          | لمتمرك |         | μωυι     |

|                        |           |                        | I           | ·            |            | l<br>. Delvere |        | ·      | I           | I                 | I        | 1      |         | 1        |

Figure 30: Reply\_Rdy and frame\_state handshake.

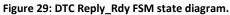

## e. Saltro Interface Controller

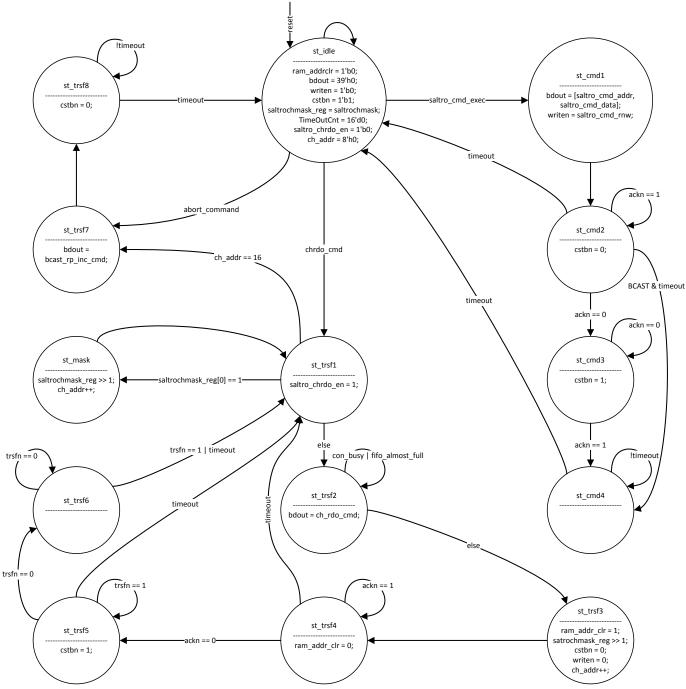

The Saltro Controller consists of 2 FSMs, a dual port RAM and a FIFO. The block diagram is shown on fig.31. Every time the Saltro Controller receives a command, the Command Control FSM (CCFSM) takes control of the bi-directional BD bus. The state diagram of the CCFSM is shown on fig.32. If the command is Write/Read SALTRO CSR, the state machine enters st\_cmd1, where the address and data are sampled, by the bdout registers (those registers drive the BD bus, when cstbn is asserted), also "writen" is sampling the command type. Then in st\_cmd2, the chip select is asserted, sending the command to the SALTRO chip. Based on, if the command is broadcast or not, the state enters a st\_cmd3 (where it waits for ackn to deassert and chip select is deasserted) or st\_cmd4. In st\_cmd4, after a few clock cycles the FSM returns to the initial state.

When a Channel Readout (CHRDO) command is send the FSM enters st\_trsf1, which initializes the handshake with the second FSM in the controller. At his point the second FSM starts to wait for the trsfn to assert and then deassert, which means that a single channel had been readout and put into the Channel RAM. In st\_trsf1 the Control FSM also checks, if the last channel has been readout or if the current channel is masked. If the channel was masked, then the ch\_addr is incremented in st\_mask and the channel mask register is shifted.

If the current channel has not been readout yet, the FSM goes to st\_trsf2, where the bdout registers sample the correct command. In this state, if the second FSM has not yet readout the channel ram from the previous channel, it will delay the execution of the command. Also that will happen, if the 32bit fifo will not be able to fit the new data coming in, since the bottleneck is the DTC TX bandwidth.

Once the Channel RAM has been read and the fifo can accommodate the new data, the FSM executes a channel readout command for channel with address ch\_addr in st\_trsf3. The ram wr\_addr is set to 0 in order to start writing the ram from the start.

In st\_trsf4, the FSM waits for ackn to be asserted or for timeout to occur. In st\_trsf5 the chip select is deasserted and the FSM is waiting for the transfer to initialize. If this doesn't happen a timeout will occurs. In st\_trsf6 the FSM is waiting for the transfer to finish, at this state the wr\_addr of the ram increments, and the Channel ram is filled with data.

When a transfer is occurring the second FSM will assert con\_busy, until all the data has been readout from the RAM. This is because the RAM is implemented as a LIFO, and no new channel data can be read until all of the previous channel data has been readout.

Once all the channels have been readout a Read Pointer increment command is issued in st\_trsf7 & st\_trsf8, which completes the readout of one event.

Figure 31: Saltro Controller block diagram.

Figure 32: Saltro Controller CC FSM block diagram.

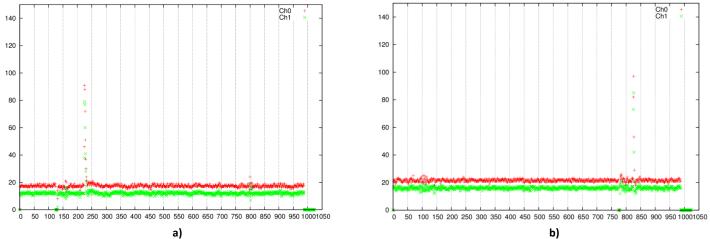

The readout waveforms of the first channel from the SALTRO are shown on fig.33. Once the readout command is issued and the SALTRO chip returns ackn, the transfer of data starts. This causes the wr\_addr to increment and con\_busy to be asserted. Once the transfer finishes, the fifo is starting to be filled with data. Once all the ram has been readout, the next readout command is issued. On fig.34 is shown a complete readout of the 16 analog channels. During the 5<sup>th</sup> channel readout, fifo\_almost\_full is asserted, which prevents the Control Command FSM from issuing readout commands. Thus the spacing between readouts is more spaced away.