### **Data Converters**

# **Nyquist-rate A/D Converters**

### Pietro Andreani

Dept. of Electrical and Information Technology

Lund University, Sweden

### Introduction

The maximum frequency of operation of high-speed ADCs depends on the unity gain frequency  $f_{tech}$  of the used process, whose value determines the maximum obtainable  $f_T$  of an op-amp (assuming we are using op-amps, which is very often the case).  $f_T$  is lower than  $f_{tech}$  by a factor  $\alpha$ , which is at least 2-4 (but ultimately depends on the desired accuracy)

$\alpha = \frac{f_{tech}}{f_T}$

It is of course necessary to provide enough time for the analog signals to settle, thus requiring a suitable margin ( $\gamma$ ) between the op-amp's  $f_T$  and the clock frequency.

### Overview

- Introduction

- Timing accuracy

- · Flash converters

- Sub-ranging and two-step converters

- Folding and interpolating converters

- Time-interleaved converters

- Successive-approximation converters

- Pipeline converters

- Other architectures

**Data Converters**

Nyquist-rate A/D Converters

1

### Introduction – II

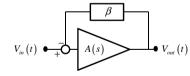

We continue by considering a feedback factor  $\beta$  around the op-amp (which is necessary to implement e.g. a gain stage):

$$A(s) = \frac{V_{out}(t)}{V_{in}(t)} = \frac{A(s)}{1 + \beta A(s)} = \frac{\omega_T/s}{1 + \beta \omega_T/s} = \frac{\omega_T/s}{1 + \beta \omega_T/s} = \frac{\omega_T}{s + \beta \omega_T}$$

The (linear) time response to an input voltage step is:

$$V_{out}(t) = V_{in}(1 - e^{-t/\tau}); \qquad \tau = \frac{1}{2\pi\beta f_T}$$

### Introduction – III

An *n*-bit ADC needs an accuracy better than  $2^{-(n+1)}$ , which means that the settling time must be

$$e^{-t_{sett}/\tau} < 2^{-(n+1)} \longrightarrow t_{sett} > \tau \cdot (n+1) \cdot \ln(2)$$

We may assume that the time allowed for settling is half a clock cycle; thus

$$\frac{1}{2f_{CK}} > t_{sett} \quad \rightarrow \quad f_{CK} < \frac{1}{2t_{sett}} = \frac{\pi\beta f_T}{(n+1)\ln(2)}$$

$$\gamma = \frac{f_T}{f_{CK}} > \frac{(n+1)\ln(2)}{\pi\beta}$$

**Data Converters**

Nyquist-rate A/D Converters

5

### Introduction – IV

For instance, if we have a 1.6GHz process, with  $\alpha$ =2 and  $\beta$  =0.5, we have

$$f_T = f_{tech}/\alpha = 800MHz$$

$\tau = 1/(2\pi\beta f_T) = 0.398ns$

For a 9-bit ADC requiring two clock periods per conversion we have

$$t_{sett} = 0.398ns \cdot (9+1) \cdot 0.693 \approx 2.7ns$$

$$t_{f_B} = 0.398ns \cdot (9+1) \cdot 0.693 \approx 2.7ns$$

$$f_{CK} = \frac{1}{2t_{sett}} \approx 164MHz$$

$f_{sampling} = \frac{f_{CK}}{2} = 82MHz$

With an anti-aliasing filter margin of one octave, the signal band is

$$f_s - f_B = 2f_B \quad \rightarrow \quad f_B = \frac{f_s}{3} = 27.5 MHz$$

**Data Converters**

**Data Converters**

Nyquist-rate A/D Converters

# Timing accuracy - II

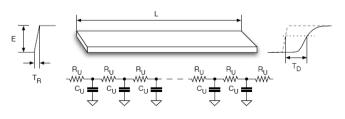

Assume a step with a finite slope,  $e_i\left(t\right) = \begin{cases} \frac{E}{T_R}t & \text{for} \quad 0 \leq t \leq T_R \\ E & \text{for} \quad t > T_R \end{cases}$

The step response is given by  $e_{out}\left(t\right) = V_r\left(t\right) - V_r\left(t-T_R\right)$  , with

$$V_r(t) = \frac{E}{T_R} \left\{ (t + \tau/2) \operatorname{erf}\left(\sqrt{\frac{\tau}{4t}}\right) - \sqrt{\frac{\tau t}{\pi}} e^{-\frac{\tau}{4t}} \right\} \qquad \operatorname{erf}(x) = \frac{2}{\sqrt{\pi}} \int_0^x e^{-y^2} dy$$

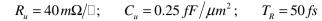

The delay is roughly estimated to be  $T_{\scriptscriptstyle D}=\tau/4$ , and it is easy to see that it does not depend on the width of the interconnection (if larger,  $C_{\rm u}$  increases and  $R_{\rm u}$  decreases by the same amount). Typically,  $R_{\rm u}C_{\rm u}$  is in the order of a few tens of  $as/\mu m^2$ , leading to delays of 1ps over a few hundreds of microns of interconnection.

# Timing accuracy

Recall the error due to sampling jitter:

$$\delta V_{in} = \delta T_{ji} \frac{dV_{in}}{dt}$$

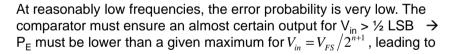

The timing error must be less than  $\frac{1}{2}LSB=V_{fs}/2^{n+1} \rightarrow a$  12-bit ADC with 1V signal at 20MHz requires a jitter below 1ps!

Phase generation and distribution is also an issue, because of the distributed time constants in the metal wires

Data Converters Nyquist-rate A/D Converters

Nyquist-rate A/D Converters

8

# Example

A noise of  $40\,\text{mV}_{FS}$  in the crossing threshold (0.5 normalized amplitude) results in a jitter of 40.8fs and 142.8fs, respectively; e.g.

$$\delta_{jit} = \frac{\Delta V}{slope} = \frac{40 \cdot 10^{-3}}{0.28} = 142.8 \, fs$$

**Data Converters**

Nyquist-rate A/D Converters

9

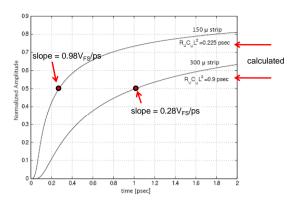

### Metastability error

If the input  $V_{in}$  is not large enough, the comparator output may be undefined at the end of the latch phase  $\Rightarrow$  error in the output code

Input signal → pre-amplified during Sample and positive-feedback regeneration during Latch → even a small input results in a "digital" output \$\\\^{\text{Platch}}\$

Positive feedback with time constant

$$\tau_L = C_p / g_m$$

Metastability probability error is

$$P_{E} pprox rac{V_{o}}{V_{out,d}} = rac{V_{o}}{A_{o}V_{in}}e^{-rac{t_{r}}{ au_{L}}}$$

, where:

$V_o$  is the voltage swing for valid logic levels, and  $t_r$  is the period of the latch phase, typically equal to  $1/2f_s$

Data Converters

Nyquist-rate A/D Converters

40

# Metastability error - II

$$f_s \ln \left( \frac{V_o \cdot 2^{n+1}}{P_{E,\text{max}} A_o V_{FS}} \right) \le \frac{1}{2\tau_L}$$

For example, if

$$V_o \approx V_{FS}$$

,  $n = 8$ ,  $\tau_L = 2 \cdot 10^{-10}$ ,  $A_o = 10^3$ ,  $P_{E,\text{max}} = 10^{-4}$

the maximum sampling frequency becomes

$$f_s = \frac{1}{17\tau_L} = 293MHz$$

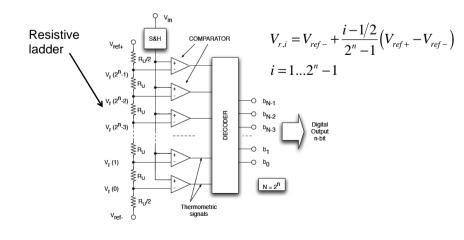

### Flash ADC

Fastest conversion: compares the input with  $2^n-1$  adjacent quantization levels; output is thermometric  $\rightarrow$  needs a decoder

Very high speed, low-to-medium resolution

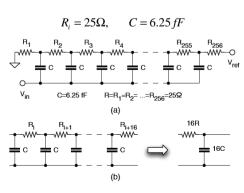

### Resistor values

Each comparator present a time varying load to the ladder → the unit resistance value must be low enough to allow the ladder to pull back all voltages values with en error below ½ LSB before the latch phase → simulation determine the optimal value for minimum power consumption

**Data Converters**

**Data Converters**

Nyquist-rate A/D Converters

13

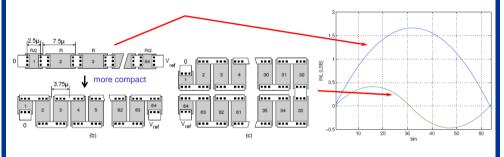

### Distortion and INL

A linear resistivity gradient in the resistance ladder causes INL; the reduced cell pitch in b) is better than a), and even better is the folded layout in c)

Matching in modern technologies is 0.1-0.05%  $\rightarrow$  10-11 bits without trimming

Temperature drift across the ladder can cause INL as well (temperature coefficients as high as 10.000ppm/°C are possible)

**Data Converters**

Nyquist-rate A/D Converters

4.4

### Offset in comparators

The different offset at the input of two contiguous comparators changes the respective quantization interval from  $\Delta$  to  $\Delta_i$ :

$$\Delta \rightarrow \Delta_i = V_{thr,i} - V_{thr,i-1} = \Delta - (V_{os,i} - V_{os,i-1})$$

For example, an 8-bit flash with 1V<sub>FS</sub> requires an  $\sigma_{V_{os}}$  < 0.6mV for a 99.9% yield (i.e.,  $1/2^{8+1}$  >  $3.3\sigma_{V}$  )

The offset in mainly caused by the pre-amplifier in the comparator; if the transistors in the input differential pair are near-minimum length, the mismatch in threshold voltage and device length are much larger that those in width and conductivity; the input-referred total offset (usually, a few mV) becomes

$$\begin{split} V_{os} &= \sqrt{\frac{A_{V_{thr}}^2}{WL}} + \left(\frac{V_{od}}{2} \frac{\Delta L}{L}\right)^2 \qquad \text{with} \qquad \Delta V_{th} = \frac{A_{V_{th}}}{\sqrt{WL}} \\ \text{and} \qquad \frac{I_{ds}}{g_m} &= \frac{V_{gs} - V_{thr}}{2} = \frac{V_{od}}{2} \qquad \text{(long-channel expression)} \end{split}$$

## Offset in comparators – II

Explicit calculation for the offset introduced by  $\Delta L$ : the current equation is

$$I_{ds} + \Delta I_{ds} = \frac{1}{2} \mu C_{ox} \frac{W}{L - \Delta L} V_{od}^2 \approx \frac{1}{2} \mu C_{ox} \frac{W}{L} \left( 1 + \frac{\Delta L}{L} \right) V_{od}^2$$

$$\Delta I_{ds} = I_{ds} \frac{\Delta L}{L}$$

This is the error current at the output of the amplifier; since it is small, the relative  $\Delta V_{in}$  at the input of the amplifier is calculated as

$$\Delta V_{in} = \frac{\Delta I_{ds}}{g_{m}} = \frac{I_{ds}}{g_{m}} \frac{\Delta L}{L} = \frac{V_{od}}{2} \frac{\Delta L}{L}$$

In bipolar implementations, the overall offset is often much lower than in CMOS (better intrinsic matching + exponential voltage-current relation)

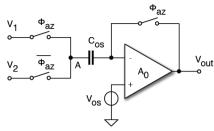

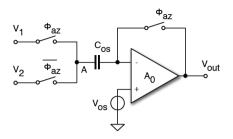

## Offset auto-zeroing

Offset is usually too large → offset cancellation is needed

Two-phase approach  $\rightarrow$  during  $\Phi_{az}$ , opamp in unity-gain configuration  $\rightarrow C_{os}$  is charged to  $V_{os}$ - $V_1$ ; during the second phase, we have

$$V_{diff,in} = V_{+} - V_{-} = V_{os} \left( \overline{\Phi}_{az} \right) - V_{2} - \left( V_{os} \left( \Phi_{az} \right) - V_{1} \right)$$

If the offset does not change → perfect cancellation; also 1/f noise is removed (white noise is instead doubled, because uncorrelated)

Charge injection is an issue (switch in feedback path critical); however, offsets of fraction of mV are possible (with fully differential architectures)

**Data Converters**

**Data Converters**

Nyquist-rate A/D Converters

17

### Offset auto-zeroing - II

One terminal is the input of the flash, the other is the tap from the ladder → the difference between input and reference is not calculated by a differential pair, but by the previous voltage subtraction at node A!

The par. cap. between A and GND is charged to  $V_1$  and then to  $V_2 \rightarrow$  the ladder must charge/discharge quickly enough these capacitances (slowest taps at the middle of the ladder)

Data Converters

Nyquist-rate A/D Converters

4.0

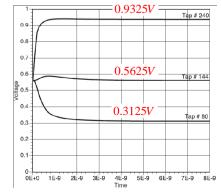

## Example - ladder settling

Simplified example (n=8)  $\rightarrow$  tap #80 takes ~5.6ns to settle to less than ½LSB (of its nominal level of 0.3125V) after converting an input of 0.5625V  $\rightarrow$  if this is too long, and the next input is close to 0.3125V, there could be a code error – notice also that tap #144 is not constant even if 0.5625V is its nominal value – this is because the ladder must (dis)charge all other nodes as well

Nyquist-rate A/D Converters

### **Practical limits**

The speed and resolution of flash converters depend on a number of practical limits:

- Small unit resistors in the resistive divider → improve resolution and speed, but require higher power and a voltage reference with low impedance from DC to f<sub>s</sub> → very difficult to realize

- Exponential increase in complexity and power consumption with # bits (especially power cannot grow beyond budget)

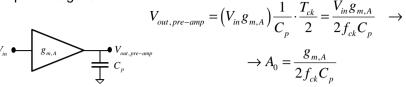

- 3) Effectiveness of comparators, in terms of metastability probability error → at high frequencies, the gain of the pre-amp (i.e., ratio of output signal (at the end of pre-amp phase) and input signal) does not have enough time to reach its low-frequency value

### Practical limits - II

At high frequencies, the "dynamic" gain of the pre-amp is determined by the current delivered by the pre-amp to C<sub>n</sub>, yielding a voltage ramp across  $\Phi_{amp}$  (without reaching its maximum value)  $\rightarrow$  the final value of the output voltage is

More bits  $\rightarrow$  more gain needed  $\rightarrow$  more  $g_{m,A} \rightarrow$  much more current (x4 for 1 more bit, or for doubling the sampling speed)

Example: 7-bit 500MHz flash that needs a pre-amp gain of 20; MOS overdrive  $V_{od}$ =200mV,  $C_p$ =0.4pF. Since  $g_m = 2I_{ds}/V_{od}$ , we obtain for the diff-pair

$I_{diff-nair} = 2I_{ds} = g_m V_{od} = 2A_0 f_{ob} C_n \cdot V_{od} = 1.6 mA$

which means that 200mA are needed only in the pre-amp stages

**Data Converters**

**Data Converters**

Nyquist-rate A/D Converters

### Practical limits - III

Another important limitation is due to the capacitive load on the input S&H from the par. caps of all comparators,  $2^n C_n$

The charge on this cap. after sampling the reference is  $2^{n}C_{p}V_{ref}/2$

A full-scale input voltage drains an equal amount of charge from the S&H; this charge must be provided in a fraction  $\alpha$  of the sampling period; the peak current that the S&H must deliver is

$$I_{S\&H,pk} > f_s 2^n C_p \Delta V_{in,max} / 2\alpha$$

which is easily larger than 10mA.

To summarize, it is impractical to design an 8-bit flash with > 500MS/s. or a 6-bit flash with > 2GS/s (these numbers improve along with the CMOS technology, of course)

**Data Converters**

Nyquist-rate A/D Converters

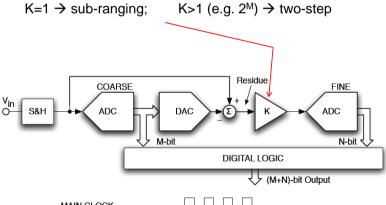

# Sub-ranging / Two-step converter

MAIN CLOCK AUTO-ZERO+S&H COARSE ADC DAC + RESIDUAL FINE ADC + OUTPUT

Nyquist-rate A/D Converters

possible clocking scheme (fast)

### **Data Converters**

# Advantages

# comparators is much reduced: if 8-bit and M=N=4, we need  $2 \cdot (2^4 - 1) = 30$  comparator instead of  $2^8 - 1 = 255$  in the full flash!

The spared area and power are much more than what is needed in the DAC and residue generator – if K=2<sup>M</sup>, the dynamic range of the amplified residue equals that of the input signal → coarse and fine ADCs can share the same reference voltage

S&H loaded only by  $2^{M} - 1$  comparators

Conversion rate is in principle reduced, as 2-3 clock periods are needed per conversion

However, since the speed of the S&H is the bottleneck in mediumresolution full-flash ADCs, the clock of the sub-ranging can actually end up being at higher frequencies, as the reduced capacitive loading of the S&H enables a faster S&H

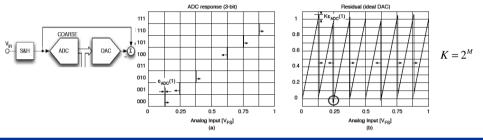

### Accuracy requirements

For medium resolutions, the quantization step is 1mV or more → the capacitance required to keep kT/C smaller than ½ LSB is not very large

For instance, if C=0.5pF,  $\sqrt{kT/C} = 90\mu V$   $\rightarrow$  up to 10b, the input capacitance is not a problem in the S&H design

The residue is given by

$$V_{res}(V_{in}) = K(V_{in} - V_{DAC}(i))$$

for  $V_{coarse}(i-1) < V_{in} < V_{coarse}(i)$

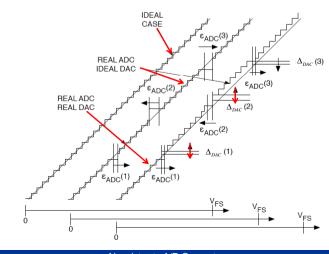

Ideally, the residue is a saw-tooth with amplitude between 0 and  $V_{FS} \cdot K/2^M$ Below is instead the residue with a real coarse ADC and an ideal DAC

**Data Converters**

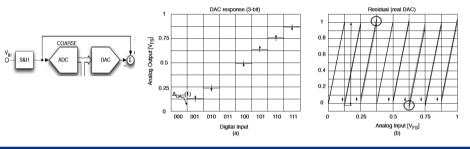

### Accuracy requirements – II

A residue outside the range of the LSB ADC results in all zeros (ones) until the input re-enters the boundaries

The DAC generates the subtractive term → a DAC error alters the residue as in the figure below (where the ADC is ideal)

Important: shift caused by DAC lasts an entire "tooth" → accuracy demands on the DAC are more stringent than on the ADC (whose errors can be corrected, as they are localized around the break points - either by inserting extra thresholds outside the 0-V<sub>FS</sub> region, or with the same technique that will be discussed later within pipeline ADCs)

Data Converters

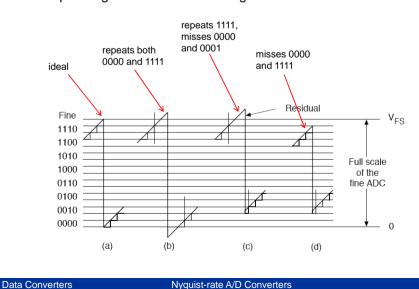

### Residue conversion

Possible situations for the fine conversion, with 4-bit LSB – depending on the errors affecting the residue

Nyquist-rate A/D Converters

### Overall picture

ADC errors (middle curve) → only around MSB transitions; after 1-2 LSB from MSB transitions, response is again on the interpolating line

DAC errors → affect whole LSB range

**Data Converters**

Nyquist-rate A/D Converters

### Two-step as a non-linear conversion

The generation of the residual is equivalent to the action of a non-linear block

Non-linear operations alter the signal spectrum by generating extra tones → in data-sampled systems, a narrow-band input can spread over the Nyquist range → amplifier and LSB flash ADC must work well above Nyquist in order to avoid degradation in the LSB conversion

Spectrum of the residue is only weakly correlated with the input (provided the amplitude is a few MSBs at least) → distortion in the LSB blocks look more like white noise than tones → linearity of the residue generator is not critical → SNDR and SFDR set by first ADC and DAC

Data Converters

**Data Converters**

Nyquist-rate A/D Converters

29

### **Folding**

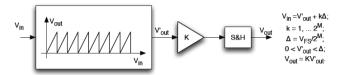

Two-step  $\rightarrow$  dynamic range divided into MSBs, with linear input-output relations inside each MSB

An equivalent non-linear transformation is the folding of a straight line shown below  $\rightarrow$  folding once around  $V_{FS}/2$ : 1 bit; twice around  $V_{FS}/4$ : 2 bits; three times around  $V_{FS}/8$ : 3 bits; and so on

The number of intervals required to quantize the folded signal diminishes accordingly → after an M-bit folding, only 2<sup>N-M</sup>-1 comparators are needed for the N-bit conversion

Obviously, it is necessary to know from which folded segment the input is coming, to determine the MSBs

Data Converters

Nyquist-rate A/D Converters

3

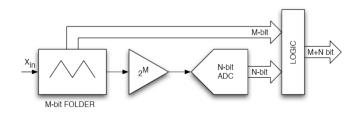

## Folding - II

The M-bit folder produces two signals: the analog folded output, and the M-bit code identifying the segment used in the folded response

The gain stage possibly boosts the dynamic range of the analog folded output to  $V_{\text{FS}}$

The N-bit ADC determines the LSBs, and finally the logic block combines MSBs and LSBs to deliver N+M bits

Nyquist-rate A/D Converters

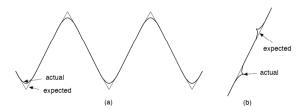

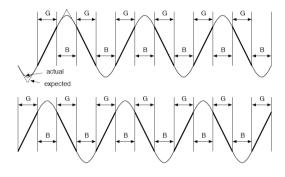

### Real folding

Any circuit implementing folding in not able to achieve infinitely sharp transitions – corners are always more or less rounded

The error is estimated by unfolding the folded response – monotonicity is sure, but INL may be high

In general, working on different segments results in different delays

Folding is normally used for high conversion rates and medium-high resolutions → finite bandwidth and slew-rate in folding block are crucial

### **Double folding**

Double folding avoids the use of the non-linear regions present in simple folding → higher linearity, but also higher complexity

Two transfer characteristics, out-of-phase by  $\mbox{\ensuremath{\%}}$  of the folding period  $\Rightarrow$  one is always in the linear region

The logic must decide which of the two characteristics should be used

**Data Converters**

Nyquist-rate A/D Converters

33

### Interpolation

Interpolation → value intermediate between two other values

With voltages → implemented with resistors, or capacitors → a) and b) below

With currents  $\rightarrow$  implemented with current mirrors  $\rightarrow$  c)

Accuracies of 0.1% can be expected with good layout

$$V_{\text{inter}} = \frac{V_1 R_2 + V_2 R_1}{R_1 + R_2} \qquad V_{\text{inter}} \left( \Phi_2 \right) = \frac{V_1 C_1 + V_2 C_2}{C_1 + C_2} \qquad \frac{\left( W/L \right)_{1,i}}{\left( W/L \right)_1} = \alpha; \qquad \frac{\left( W/L \right)_{2,1}}{\left( W/L \right)_2} = 1 - \alpha$$

$$I_{\text{inter}} = \alpha I_1 + (1 - \alpha) I_2$$

$$I_{\text{inter}} = \alpha I_1 + (1 - \alpha) I_2$$

$$I_{\text{inter}} = \alpha I_1 + (1 - \alpha) I_2$$

$$I_{\text{inter}} = \alpha I_1 + (1 - \alpha) I_2$$

$$I_{\text{inter}} = \alpha I_1 + (1 - \alpha) I_2$$

$$I_{\text{inter}} = \alpha I_1 + (1 - \alpha) I_2$$

$$I_{\text{inter}} = \alpha I_1 + (1 - \alpha) I_2$$

**Data Converters**

Nyquist-rate A/D Converters

3/

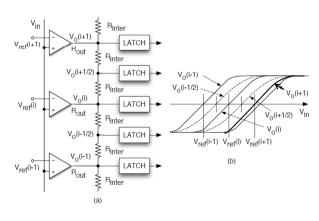

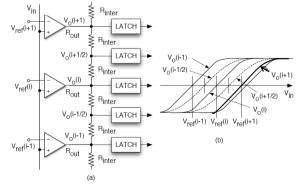

# Interpolation in flash converters

Comparators substituted with pre-amp; reduces # pre-amps and ref. voltages (but not # latches)  $\rightarrow$  cap. load on the S&H diminishes  $\rightarrow$  less power consumption, higher speed; fewer ref. voltages  $\rightarrow$  less "charge-pumping" effect  $\rightarrow$  less stringent settling limit

Often used with 4 or 8 resistors (not just 2 as here)

### Interpolation in flash converters - II

To preserve linearity, pre-amp output should saturate for an input higher than the closest upper threshold, and lower than the closest lower threshold.

The overlapped non-saturated regions, interpolated by the resistors, determine zero-crossings mid-way between the pre-amps zero crossings. Far from the zero crossings, the slope of the interpolated curve diminishes, but then the differential signal is already large enough for the latch.

Data Converters Nyquist-rate A/D Converters

36

Data Converters Nyquist-rate A/D Converters

nverters

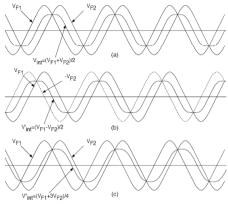

### Interpolation with folding

Multiple interpolators take the place of the fine flash converter  $\rightarrow$  (a) shows the interpolation between two folded responses ( $V_{F1}$  and  $V_{F2}$ ), shifted by half segment; the shape of the interpolated segment is more rounded than the generating signals; but, again, it is important that it is

linear only close to the zero crossing  $v_{F1}$   $v_{F2}$

- (b) → interpolating V<sub>F1</sub> and -V<sub>F2</sub> yields a second set of zero crossings, detected by additional comparators

- (c)  $\rightarrow$  if R<sub>1</sub> = 3R<sub>2</sub>, the zero crossing is at ½ distance from the zero crossing of V<sub>F2</sub>  $\rightarrow$  multiple interpolations can yield a sufficient number of crossings to obtain the LSB conversion  $\rightarrow$  avoids the use of an explicit flash ADC, possibly increasing the conversion rate

Data Converters

Nyquist-rate A/D Converters

37

### Interpolation and linearity

Interpolation resistances load the pre-amps  $\rightarrow$  if output resistance is not much lower, voltage drop alters the generated voltages  $\rightarrow$  however, this is in fact an advantage! For the first, the voltage error depends on the generated voltage, and is zero for zero output voltage  $\rightarrow$  ininfluent at zero crossing, which is where it really matters!

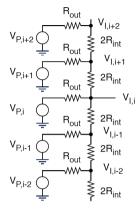

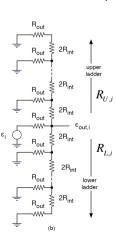

Besides this, interpolating resistors + pre-amps with finite output resistance average the offsets of the pre-amps, improving the overall linearity The current flowing into the i-th pre-amp is

$$I_{P,i} = \frac{V_{I,i+1} + V_{I,i-1} - 2V_{I,i}}{2R_{int}}$$

→ if the i-th interpolated voltage is the average of its neighbors, its current is zero → ideal output voltages are not affected by the interpolating network → we need to consider only the effect of the errors

**Data Converters**

Nyquist-rate A/D Converters

00

# Interpolation and linearity - II

We assume an error on the output voltage of the i-th op-amp:  $V_{p,i} \rightarrow V_{p,i} + \varepsilon_i$ The error at the output *i* becomes

$$\varepsilon_{out,i} = \varepsilon_i \frac{1}{1 + R_{out}/R_{T,i}} = \varepsilon_i T_{i,i} < \varepsilon_i; \quad R_{T,i} = R_{U,i} \parallel R_{L,i}$$

where  $T_{i,i}$  is a damping factor introduced by the finite output resistance of the pre-amp

Using the circuit on the left, it is possible to estimate the error induced by  $\varepsilon_i$  at a node j;  $T_{i,j}$  diminishes with |i-j| increasing, and is usually negligible for |i-j| > 4. In general, we must superpose the effects of all errors:

$$\varepsilon_{tot,i} = \sum_{j=1}^{2^n-1} \varepsilon_j T_{i,j}$$

The above averaging effect benefits shortdistance errors → reduces the DNL

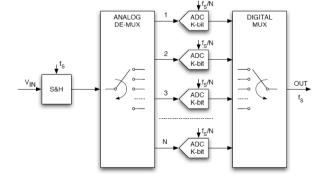

### Time-interleaved converters

Increase the conversion rate by having N converters working in parallel → the equivalent conversion rate is N times that of the single converter; the S&H must work at full rate; or, there can be #N S&H working at the reduced rate, but with a very high precision in the distribution of the phases. Important remark: gain and offset errors on each ADC, which are usually of minor weight, are very important here, because they become dynamic errors!

### Accuracy requirements

Clock misalignment across the ADCs  $\rightarrow$  looks like clock jitter, but with N·T<sub>S</sub> periodicity. If the clock misalignment between the K-th and 1st channel is  $\delta_k$ , the error introduced is

$$\varepsilon_{ck,K}(nT) = \delta_K \frac{dV_{in}}{dt}\Big|_{nT}$$

;  $n = iN + K$

which, for the sinusoidal input  $V_{in} = A_{in} \sin(\omega_{in}t)$ , becomes

$$\varepsilon_{ck,K}(nT) = \delta_K A_{in} \omega_{in} \cos(\omega_{in} nT)$$

The power of the error due to clock misalignment becomes, as a function of the input power and N:

$$P_{\varepsilon_{ck}} = P_{in} \delta_k^2 \omega_{in}^2 / N$$

Furthermore, because of the down-sampling of the input with a clock error at frequency  $f_s/N$ , the clock misalignment gives rise to images located at

$$\frac{kf_S}{N} \pm f_{in}$$

**Data Converters**

Nyquist-rate A/D Converters

41

### Accuracy requirements – offset

Offset  $\rightarrow$  identical offsets in all ADCs have no impact; offset mismatch causes tones  $\rightarrow$  offset on a signal channel causes a pulse of amplitude equal to the offset  $\rightarrow$  tones at  $f_s/N$  and its multiples

Interleaved converter is for large bandwidths  $\rightarrow$  signal occupies a large fraction of the Nyquist interval  $\rightarrow$  even tones at relatively high frequencies are likely to fall into the signal band

Worst case  $\rightarrow$  alternate sequence of positive and negative offsets  $V_{os} \rightarrow$  square wave of amplitude  $V_{os} \rightarrow$  1st harmonic with amplitude  $4V_{os}/\pi$ ; SFDR with full-scale input sine wave becomes

$$SFDR = 20\log \frac{\pi V_{FS}}{8V_{co}}$$

If the SFDR requirement for maximum input equals the SNR, the offset mismatch should obey the relation

$$\frac{1}{2} \left( \frac{4}{\pi} V_{os} \right)^2 \le \frac{\Delta^2}{12} \qquad \rightarrow \qquad V_{os} \le \frac{\pi}{4} \sqrt{\frac{1}{6}} \cdot \Delta = 0.32 \Delta = 0.32 LSB$$

**Data Converters**

Nyquist-rate A/D Converters

12

# Accuracy requirements – gain error

Identical gain errors in all ADCs have no impact; gain mismatch between the channels causes tones  $\rightarrow$  worst case if gains alternate between (1+ $\epsilon_{\rm G}$ ) and (1- $\epsilon_{\rm G}$ ), which gives rise to an error equal to the multiplication of the input signal with a square wave of amplitude  $2\epsilon_{\rm G}$  at  $f_{\rm s}/2$  (or its submultiples)

Largest spur tone occurs at  $f_s/2 \pm f_{in}$  (or  $f_s/4 \pm f_{in}$ , ...), and has amplitude

$$A_{spur} = \frac{4}{\pi} \varepsilon_G A_{in}$$

resulting in

$$SFDR = 20\log\frac{\pi}{4\varepsilon_G}$$

Thus, even with  $\epsilon_G$  as low as 0.1%, the SFDR is not higher than 58dB Bottom-line: time-interleaved ADCs always need trimming/calibration if

high resolution is desired

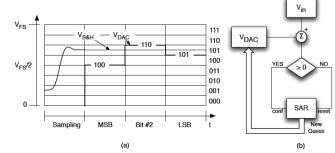

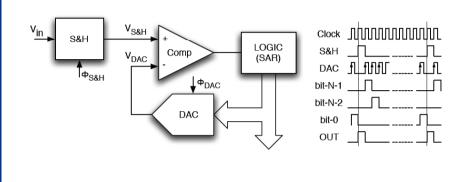

# Successive-approximation converter

1 bit converted per clock cycle (+ 1 or 2 cycles for signal sampling + settling)

Binary search → reduced complexity and power, but lower conversion rate

The MSB distinguishes between input signals that are above or below  $V_{FS}/2$ ; depending on this result, the threshold for determining the 2nd bit is either  $V_{FS}/4$  or  $3V_{FS}/4$ ; and so on (below: 3-b conversion)

The voltages used in the comparisons are generated by a DAC driven by a successive-approximation register (SAR)

### SA – timing diagram

After signal S&H, the SAR sets the MSB to 1; if the comparator confirms, the 1 is retained, otherwise is set to zero; then the 2nd bit is processes, and so on until all bits have been generated; then a new signal sample is taken

**Data Converters**

Nyquist-rate D/A Converters

45

### SA – algorithm

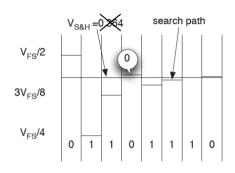

The name of the algorithm comes from the fact that the voltage from the DAC is an improving approx. of the voltage from the S&H - occasionally, the error can be larger than in the previous step (as from  $4^{th}$  to  $5^{th}$  bit below), but surely is not larger than successive divisions by 2 of the full-scale amplitude

Example below: search path for  $V_{S\&H} = 0.4296875V_{FS}$

Data Converters

Nyquist-rate A/D Converters

16

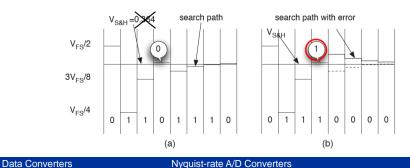

## Algorithm with error

If there is an error in the bit evaluation, the error propagates along all successive steps – for instance, this may happen if  $V_{DAC}$  changes from a level well below  $V_{S\&H}$  to a level just above  $V_{S\&H}$  (4<sup>th</sup> clock period below) – if the comparator recovery from overdrive is not fast enough, an error may occur – in the case below, we end up with a conversion error of 2 LSBs.

Occurs typically at the beginning of the conversion, when overdrive is large

Error correction techniques expand the search range near the end, to accommodate for initial inaccuracies→ however, extra clock cycles needed

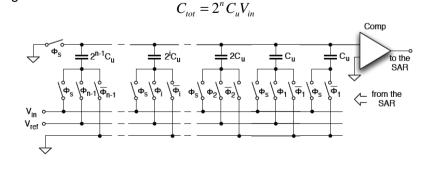

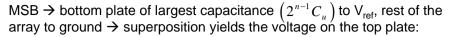

### Charge-redistribution SA-ADC

Charge sampled at the beginning of the conversion is redistributed on the capacitor array, to obtain a top-plate voltage close to zero at the end

Binary-weighted capacitances + a comparator → only one active-device block, which is not even particularly critical → very attractive for nanometer CMOS processes

During  $\Phi_{\text{S}},$  sampling  $\Rightarrow$  array connected between  $V_{\text{in}}$  and ground – total charge becomes:

Data Converters Nygu

Nyquist-rate A/D Converters

# Charge-redistribution SA-ADC - conversion

$$V_{comp}\left(1\right) = \frac{V_{ref}}{2} - V_{in}$$

This voltage is the difference between MSB and input  $\rightarrow$  only necessary to compare it to zero = ground, very convenient; if MSB=1, the connection of the largest cap to  $V_{ref}$  is kept during the  $2^{nd}$  comparison; otherwise it is restored to ground

**Data Converters**

**Data Converters**

Nyquist-rate A/D Converters

49

### SA-ADC conversion – II

Thus, during the second comparison, the top plate voltage becomes

$$V_{comp}(2) = \frac{V_{ref}}{2} \cdot MSB + \frac{V_{ref}}{4} - V_{in}$$

which is used to find the 2<sup>nd</sup> bit; and so on for all bits

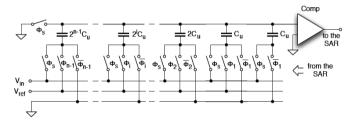

The parasitic capacitance at the top plate attenuates the generated voltage by a factor  $\alpha$ :

Data Converters

Nyquist-rate A/D Converters

50

# SA-ADC conversion – good features

$\alpha$  reduces the voltage value, but not its sign, which is the relevant info – this is a consequence of pre-charging the top-plate to zero – the top-plate voltage is zero at sampling, and almost zero at the end of the conversion

The input common-mode range of the comparator is zero without using op-amps or OTAs

Only the comparator and charging/discharging the array determine the power consumption  $\rightarrow$  very power efficient (however, this does not take into account the generation of  $V_{RFF}$ )

Auto-zeroing of the comparator to avoid offset errors → comparator is connected as a unity-gain buffer and used to pre-charge the top plate during sampling

Capacitive attenuation can be used to limit the capacitive spread in the array

Nyquist-rate A/D Converters

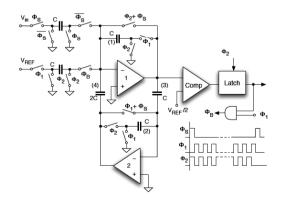

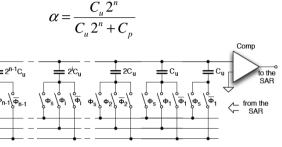

## **Example of SA-ADC**

# A Programmable 10b up-to-6MS/s SA-ADC Featuring Constant FoM with On-Chip Reference Voltage Buffers

| CMOS Technology           | 0.13 μm<br>1P6M |  |  |

|---------------------------|-----------------|--|--|

| Core area [mm²]           | 0.75            |  |  |

| Power Supply [V]          | 1.2             |  |  |

| Power consumption [mW]    | 3.2             |  |  |

| Sampling frequency [MS/s] | 5.5             |  |  |

| INL/DNL [LSB]             | 0.6/0.55        |  |  |

| ENOB [bits]               | 9.2             |  |  |

| HD3≈IM3 [dBs-FS]          | 72              |  |  |

| FoM [pJ/conversion]       | 1               |  |  |

F. Borghetti , J.H. Nielsen , V. Ferragina , P. Malcovati , P. Andreani , A. Baschirotto – presented at ESSCIRC 2006

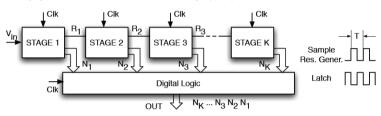

### Pipeline ADC

Cascade of individual stages, each performing one of the elementary functions required by a sequential algorithm

The pipeline unwinds over space what would be performed over time by a sequential scheme

The simplest sequential scheme is the two-step algorithm, which uses two clock periods, one for MSBs and one for LSBs → the pipeline version delivers MSBs and LSBs in one clock period, in this way: the first stage yields the MSBs of the current sample, and the second stage yields the LSBs of the previous sample

In general, pipeline ADCs are multi-step (> 2)

**Data Converters**

Nyquist-rate A/D Converters

53

### Pipeline ADC - II

SA with pipeline → each stage of the pipeline generates 1 bit, plus the difference between input and internal DAC voltage – accuracy of analog signal must comply with the desired # of bits (each stage may deliver more than 1 bit, and/or different stages may deliver different # of bits)

Digital logic combines the bits coming from K stages  $\rightarrow$  outputs at <u>full rate</u>, but with a delay (latency) of K+1 clock cycles  $\rightarrow$  not a problem, unless the ADC is inside a feedback loop

|         | S&H                            | S&H                            | S&H                            |                                |                                |                                |                                | Ì |

|---------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|---|

| S&H     | n                              | n+1                            | n+2                            |                                |                                |                                |                                |   |

| Stage 1 | b <sub>9</sub> -b <sub>8</sub> |                                |                                |                                |   |

| n-1     | n-1                            | n                              | n+1                            | n+2                            |                                |                                |                                |   |

| Stage 2 |                                | b <sub>7</sub> -b <sub>6</sub> |                                |                                |   |

| Olugo Z |                                | n-1                            | n                              | n+1                            | n+2                            |                                |                                |   |

| Stage 3 |                                |                                | b <sub>5</sub> -b <sub>4</sub> |                                |   |

| 9       |                                |                                | n-1                            | n                              | n+1                            | n+2                            |                                |   |

| Stage 4 |                                |                                |                                | b <sub>3</sub> -b <sub>2</sub> |   |

| Olage 4 |                                |                                |                                | n-1                            | n                              | n+1                            | n+2                            |   |

| Stage 5 |                                |                                |                                |                                | b <sub>1</sub> -b <sub>0</sub> | b <sub>1</sub> -b <sub>0</sub> | b <sub>1</sub> -b <sub>0</sub> |   |

|         |                                |                                |                                |                                | n-1                            | n                              | n+1                            |   |

| Digital |                                |                                |                                |                                |                                | OUT                            | OUT                            |   |

|         |                                |                                |                                |                                |                                | n-1                            | n                              |   |

|         |                                | I                              | ı                              | I                              | I                              |                                |                                | _ |

|         | n                              | n+1                            | n+2                            | n+3                            | n+4                            | n+5                            | n+6                            | t |

We see here a timing example for a 10-b, 5-stage, 2-b per stage pipeline ADC – the 6<sup>th</sup> clock cycle is used by the digital logic to combine the 10 bits and make them available

Data Converters

Nyquist-rate A/D Converters

E /

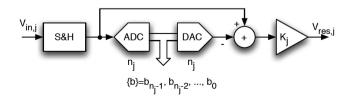

# Generic pipeline stage

The subtraction of  $V_{DAC}$  from  $V_{in}$  gives the quantization error, which, after amplification, determines the new residue voltage

$$V_{res}(j) = K_{j} \left\{ V_{res}(j-1) - V_{DAC}(b_{j}) \right\}$$

The dynamic range of the residue equals that of the input if, for an  $n_j$ -bit DAC, the gain is  $2^{n_j} \rightarrow$  this is frequently used, as it allows the use of the same reference voltages in all stages

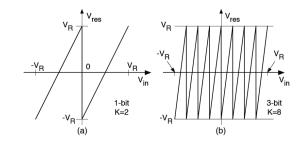

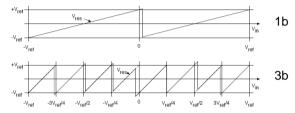

### Residue generation

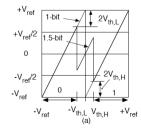

- (a)  $\rightarrow$  input between -V<sub>R</sub> and V<sub>R</sub> ,1 bit  $\rightarrow$  the DAC subtracts -½V<sub>R</sub> when the input is negative, and ½V<sub>R</sub> when the input is positive; with K=2, the residue varies again between -V<sub>R</sub> and V<sub>R</sub>

- (b) 3 bits  $\rightarrow$  the amplitude of the quantization error is at most  $\pm V_R/8$ , and K=8 makes the residue vary again between -V<sub>R</sub> and V<sub>R</sub>

### Accuracy requirements

Accuracy requirements are of course greater in the first few stages – most demanding is the input S&H

Non-idealities of ADC, DAC, and K cause limitations similar to those studied in the two-step ADC – threshold errors in the ADC cause the residue to be either greater or lower than full scale at the break points

However, the residue generator can still correctly provide the difference between the analog input and the quantized signal from the DAC – the error will be generated by the ADC in the next stage, since this ADC will not be able to correctly convert residues outside  $\pm V_{ref} \rightarrow$  this observation is the basis of the digital error correction technique to be treated next

Data Converters

Nyquist-rate A/D Converters

57

### Accuracy requirements – II

We observed that in the two-step ADC the DAC errors modified the residue over a whole LSB segment, impacting the INL → also in the pipeline ADC the accuracy of any DAC, referred to the input of the pipeline, must be better than the required INL, and lower than 1LSB to ensure monotonicity (after a few stages, DAC linearity is of minor concern)

If the interstage gain has an error,  $G = 2^{n_j} \left(1 + \delta G\right)$ , the slope of the residue is either increased or decreased, causing an error that is zero in the middle, and maximum at the endings of the segments – at the break points, the error invert its sign, giving rise to a step change

$$\Delta V = 2V_{ref} \delta G$$

which, referred to the input, must again comply with INL requirements and monotonicity

**Data Converters**

Nyquist-rate A/D Converters

---

## Digital error correction

We observed that the dynamic range of the residue can exceed the reference, but no error is made until the following ADC cannot convert correctly an out-of-range signal

Reduce the interstage gain? Difficult, as an attenuation different from 1/2 is difficult to account for

Add additional levels to the ADC of the stage? yes, because: 1) the redundant levels avoid generating out-of-range residues, and 2) provide info to the digital domain (hence the name of the technique) to fully compensate for the ADC error

Consider a 1-b DAC, which usually requires an ADC with 1 threshold – to ensure enough redundancy, at least 2 thresholds are needed

Since a 1-b ADC needs 1 threshold and a 2-b ADC needs 3, the use of 2 thresholds is referred to as a 1.5-b conversion (very popular)

It is possible to apply the same approach to multi-bit DACs

# Digital error correction – II

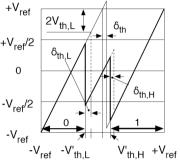

The input is divided into 3 regions: one below the lower threshold ( $V_{th,L}$ ), one between the two thresholds, and one above the upper threshold ( $V_{th,H}$ ) – if the separation of the two thresholds is large enough, a signal below  $V_{th,L}$  is "certainly negative", and above  $V_{th,H}$  is "certainly positive" Uncertainty arises in the middle region  $\rightarrow$  close to the zero crossing, an error may lead to a residue exceeding the limits

The residue generator adds  $V_{ref}/2$  if the ADC provides a certain 0, and subtracts  $V_{ref}/2$  if the ADC provides a certain 1 – but does not do anything in the uncertainty region  $\rightarrow$  here the residue is the simple amplification by 2 of the input, shown below with correct (left) and incorrect thresholds

### Digital error correction - III

Errors  $\delta_{th,L}$ ,  $\delta_{th,H}$  on the thresholds change the value of the residue at the break points, but the residue remains within  $\pm V_{ref}$  if  $\delta_{th,L}$  ( $\delta_{th,H}$ ) is lower than  $V_{th,L}$  ( $V_{th,H}$ ) – in the case below, the input range for "certain" 0 diminishes, and increases for "certain" 1

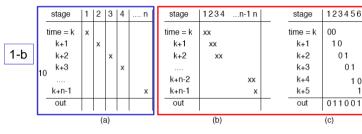

The info provided by the 1.5-b converter is a flag in the LSB position, which is set to 1 when the uncertainty region is detected → the whole code becomes therefore: 00 for certain 0; 10 for certain 1; and 01 for uncertainty.

**Data Converters**

Nyquist-rate A/D Converters

61

### Digital error correction – IV

The digital logic sums the outputs, taking into account the weight of each stage – the gain of each stage is  $2 \rightarrow$  the weight of the uncertainty flag is equal to the MSB in the next stage (adders are needed)

In the example below, notice that the uncertainty in the  $3^{rd}$  stage is corrected by the 10 of the next two stages, while the 01 of the  $4^{th}$  and  $5^{th}$  stages are fixed to 0

The last stage does not have an extra threshold, as its uncertainty cannot be resolved by further comparisons

1.5-b

**Data Converters**

Nyquist-rate A/D Converters

62

# Digital error correction – example

Assume  $\pm V_{ref} = \pm 1$ , and  $V_{in} = 2V_{ref} (1/4 + 1/8 + 1/64 + 10^{-3}) - V_{ref} = -0.21675 = 011001$

If  $V_{th,L}$  = -0.25,  $V_{th,H}$  = 0.25, we have the following residue sequence: -0.21675, -0.4335, 0.133, 0.266, -0.468, 0.064, corresponding to the binary outputs: 01, 00, 01, 10, 00, 1  $\rightarrow$  011001, as expected

If now shift on thresholds:  $V_{th,L}$  = -0.30,  $V_{th,H}$  = 0.10, the sequence becomes -0.21675, -0.4335, 0.133, -0.734, -0.468, 0.064, corresponding to the binary outputs: 01, 00, 10, 00, 00, 1  $\rightarrow$  still 011001 !

With thresholds  $V_{th,L}$  = -0.10,  $V_{th,H}$  = 0.30, the sequence becomes -0.21675, 0.5665, 0.133, 0.266, 0.532, 0.064, corresponding to the binary outputs: 00, 10, 01, 01, 10, 1 → again 011001 !

# Dynamic performances

Depend on slew-rate and bandwidth of S&H and residue generator – a step with amplitude  $\overline{V_{out}}$  becomes a ramp during slewing, and turns into an exponential when feedback takes over – the equations are (as already derived in an earlier lecture)

$$egin{align*} V_{out}\left(t

ight) = SR \cdot t & t < t_{slew} \\ V_{out}\left(t

ight) = \overline{V_{out}} - \Delta V \cdot e^{-(t-t_{slew})/ au} & t > t_{slew} \\ \Delta V = SR \cdot au; & t_{slew} = \overline{V_{out}}/SR - au; & au = 1/eta \omega_T \end{aligned}$$

feedback factor

The next stage S&H samples after  $T_{\rm S}/2$ , and the (non-linear) settling error becomes

$$\Delta V_{err} = \Delta V \cdot e^{-(T_S/2 - t_{slew})/\tau}$$

It is important to have a small error in the first stages, but in later stages is less important, because the input-referred error is divided by the gain of all preceding stages  $\rightarrow$  op-amps in later stages do not need to be as high-performing  $\rightarrow$  it is possible to save power

# Much faster than transistor-level simulations, give a good starting point for the design – here, the achievable SFDR and SNR vs. the slew-rate of the key blocks are estimated – the different impact of the different blocks is also very easy to determine

# Residue generator – II

Nyquist-rate A/D Converters

**Data Converters**

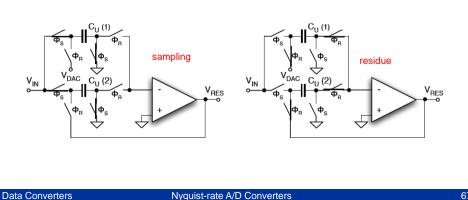

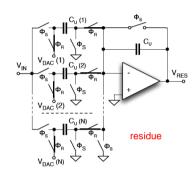

With 1 bit  $\rightarrow \beta$ =1/3 (2 caps are needed at the input to implement the gain x2) – speed can be improved with the flip-around circuit shown below, where  $\beta$ =1/2, since input and feedback capacitance are equal (however, is the op-amp really open-loop during sampling?)

If  $C_U(1)=C_U(2)$ , the input voltage is doubled (one cap changes polarity compared to the other), but the gain for  $V_{DAC}$  is only -1  $\rightarrow$  it is necessary to double the value of the references.

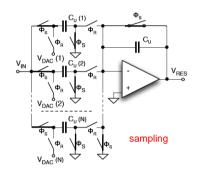

### Residue generator

Capacitors are used for both sampling and D/A conversion; the residue is

$$V_{res} = NV_{in} - \sum_{1}^{N} V_{DAC}(i)$$

where the DAC control bits are thermometric from the ADC

An amplification of  $2^n$  gives rise to a feedback factor  $\beta = 1/(2^n + 1) \rightarrow$  to keep the same  $\tau$ , the unity-gain frequency of the op-amp must grow as  $2^n \rightarrow$  more than 3 bits per stage not suitable for high conversion rates

Data Converters

Nyquist-rate A/D Conve

66

## Cyclic (or algorithmic) converter

Uses the same cell for converting one bit per clock cycle  $\rightarrow$  n+1 clock periods to convert n bits; the voltage at the output of OTA 1 is the same as the residue of the first stage of a 1-b per stage pipeline:

$$V_{OTA1} = 2V_{in} - V_{REF} = 2\left(V_{in} - \frac{V_{REF}}{2}\right)$$