## **Contents: Power and Delay**

#### **CMOS Static and Dynamic Power Consumption:**

J Rabaey et al "Digital Integrated Circutis"

#### Integration of III/V HEMTs on Si:

S Datta et al IEEE Electron Dev. Lett. 28, 2007 p 685 " Ultrahigh-Speed 0.5 V Supply ..."

#### **HEMTS for Beyond-CMOS:**

D-H Kim et al IEEE Trans. Electron Dev. 54, 2007 p 2606 "Logic Suitability of 50 nm ..."

# CMOS Dynamic and Static Power Consumption

#### Advantages with CMOS:

Full logic swing

High noise margin

Superior robustness

Low steady state power consumption

Robust low-power digital technology

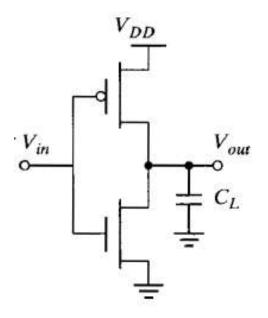

V<sub>out</sub>=V<sub>in</sub> for next stage C<sub>L</sub> both parasitics and gate capacitance

## **Dynamic Power Consumption**

#### Advantages with CMOS:

Full logic swing

High noise margin

Superior robustness

Absence of steady state power consumption

#### Calculate the charging energy during one switching event!

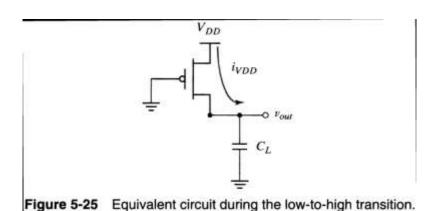

Calculate the charging energy:

$$E_{VDD} = \int_{0}^{\infty} i_{VDD}(t) V_{DD} dt = V_{DD} \int_{0}^{\infty} C_{L} \frac{dv_{out}}{dt} dt = C_{L} V_{DD} \int_{0}^{VDD} dv_{out} = C_{L} V_{DD}^{2}$$

Calculate the stored energy:

$$E_{C} = \int_{0}^{\infty} i_{VDD}(t) v_{out} dt = \int_{0}^{\infty} C_{L} \frac{dv_{out}}{dt} v_{out} dt = C_{L} \int_{0}^{VDD} v_{out} dv_{out} = \frac{C_{L} V_{DD}^{2}}{2}$$

## **Dynamic Power Consumption**

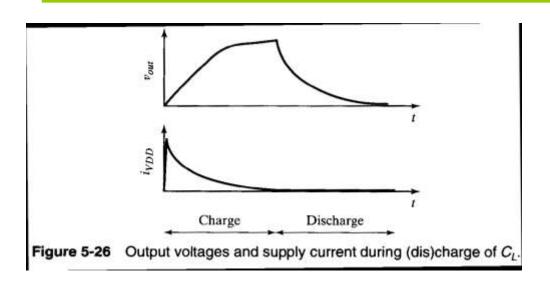

During charging (low-to-high transition) half energy is stored on capacitor, half energy is dissipated in the transistor

During discharging (high-to-low transition) half energy is stored on capacitor, the stored energy (half energy) is dissipated in the transistor

$$P_{dyn} = C_L V_{DD}^2 f_{0->1}$$

Example: 50 nm CMOS

$f=2 GHz C_1=3 fF/gate$

$V_{DD}=1.0 V$

$P_{dvn}=6 \mu W$

Note: Not all transistors active! (effectively reduces frequency) Voltage scaling reduces P<sub>dvn</sub> Scaling reduces gate capacitance, but increases parasitic capacitance!

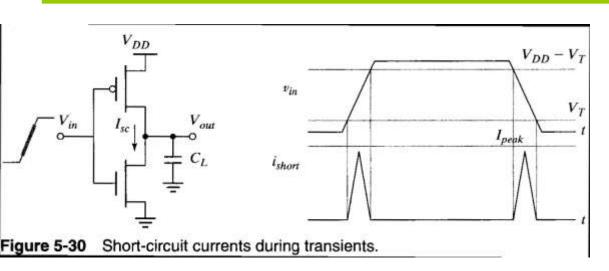

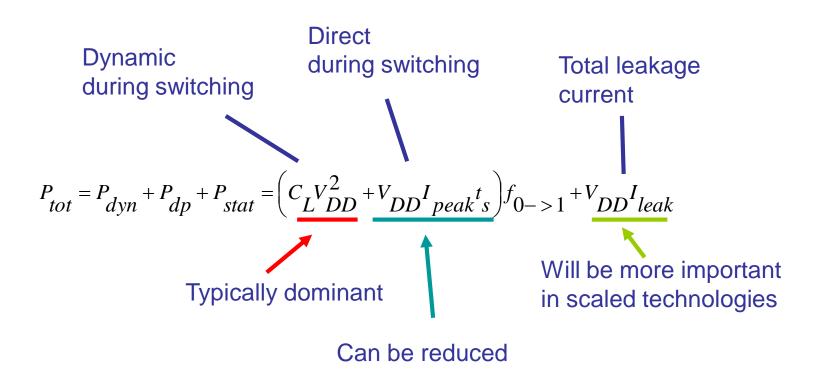

## **Direct-Path Current Power Consumption**

During the finite time switching, a direct current is flowing in the transistor pair

Assume triangular current peaks

$$E_{dp} = V_{DD} \frac{I_{peak}t_{sc}}{2} + V_{DD} \frac{I_{peak}t_{sc}}{2} = t_{sc}V_{DD}I_{peak}$$

$$P_{dp} = t_{sc} V_{DD} I_{peak} f = C_{sc} V_{DD}^2 f$$

This is typically a minor part of the power consumption

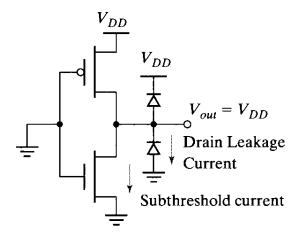

## Static Power Consumption: Drain Leakage

Leakage current typically 10-100 pA/ $\mu$ m<sup>2</sup>. Drain area 50 nm<sup>2</sup> and 1 billion gates with V<sub>DD</sub>=1.0 V gives 0.5  $\mu$ W.

$$P_{stat} = I_{stat} V_{DD}$$

#### Solution:

Use NWs to reduce channel leakage

Use SOI technology to reduce contact leakage

**Figure 5-34** Sources of leakage currents in CMOS inverter (for  $V_{in} = 0 \text{ V}$ ).

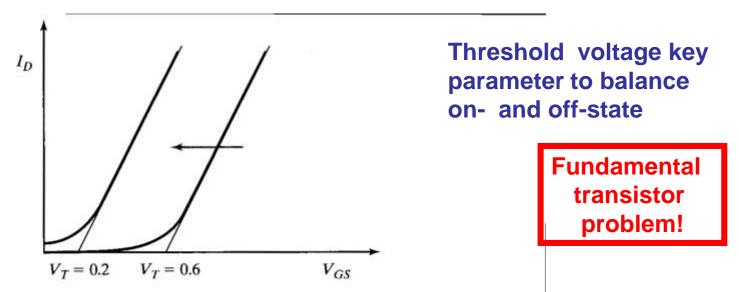

# Static Power Consumption: Subthreshold Leakage

As the drive voltage is reduced, the threshold voltage should also be scaled (recall  $V_t \sim V_{DD}/3!$ ). This implies that the subthreshold current is substantially increased.

Consider a 50 nm NMOS transistor with SS of 60 mV/dec. and  $V_t$ =0.4 V. At  $V_{GS}$ =0 V it consumes about  $10^{-12}$  A. Reducing the threshold to 0.2 V increased the current a factor 300! In a 1 billion transistor operating at 1 V, we get a power consumption of  $10^9$ x300x10<sup>-12</sup>x1.0=300 mW!

Figure 5-35 Decreasing the threshold increases the subthreshold current at  $V_{GS} = 0$ .

## Put It All Together!

## **The Power-Delay Product**

Introduce the power-delay product as a quality measure of a logic gate:

$$PDP = P_{av}t_p$$

If the gate is switched at full speed, the PDP corresponds

To the <u>average energy consumed per switching event</u>

(0->1 or 1->0 transition)

$$PDP = C_L V_{DD}^2 f_{\text{max}} t_p = \frac{C_L V_{DD}^2}{2}$$

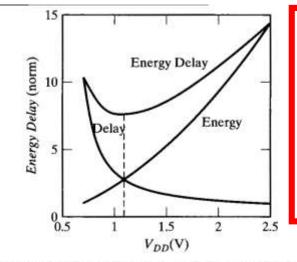

## **Better, The Energy-Delay Product**

Introduce the energy-delay product, which balances the <u>performance and energy consumption!</u>

$$EDP = PDP \times t_p = P_{av}t_p^2 = \frac{C_L V_{DD}^2}{2}t_p$$

$t_p$  is the propagation delay (gate delay) and  $f_{max}=1/(2t_p)$

## Voltage Dependence on EDP!!!

$$EDP = PDP \times t_p = P_{av}t_p^2 = \frac{C_L V_{DD}^2}{2}t_p$$

$$t_p \approx \frac{\alpha C_L V_{DD}}{\left(V_{DD} - V_T\right)^2}$$

$$EDP = \frac{\alpha C_L^2 V_{DD}^3}{2(V_{DD} - V_T)^2}$$

**Increase V<sub>d</sub>:**

Speed improves

(higher current)

Energy increases

(more charge)

Optimum!

Figure 5-36 Normalized delay, energy, and energy-delay plots for CMOS inverter in 0.25-μm CMOS technology.

#### Extra (model validation):

$$t_{p} = \frac{t_{pHL} + t_{pLH}}{2} = \ln 2 \times C_{L} \left( \frac{R_{eqn} + R_{eqp}}{2} \right)$$

$$t_{pHL} = \ln 2 \times \frac{3}{4} \frac{C_{L}V_{DD}}{(W/L)_{n} \left( \mu_{n} \varepsilon_{ox} / t_{ox} \right) \left( V_{DD} - V_{Tn} \right)^{2}}$$

RC-time constant during switching

Use transistor equations to derive the effective transistor resistance

## Ultrahigh-Speed 0.5 V Supply Voltage In<sub>0.7</sub>Ga<sub>0.3</sub>As Quantum-Well Transistors on Silicon Substrate

Suman Datta, Senior Member, IEEE, G. Dewey, J. M. Fastenau, Member, IEEE, M. K. Hudait, D. Loubychev, W. K. Liu, Senior Member, IEEE, M. Radosavljevic, W. Rachmady, and R. Chau, Fellow, IEEE

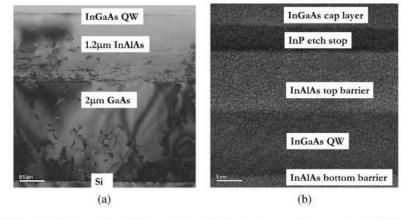

Fig. 1. Cross-sectional TEM images of In<sub>0.7</sub>Ga<sub>0.3</sub>As QW structures on Si using metamorphic buffer architecture; (a) Entire layer structure. (b magnification of In<sub>0.7</sub>Ga<sub>0.3</sub>As QW along with bottom and top barrier layers. The misfit dislocations are predominantly contained in the buffer layer.

- buffer layer techniques are available

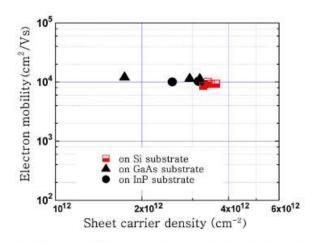

- comparable mobility

Fig. 2. Electron mobility versus sheet carrier density in n-channel In<sub>0.7</sub>Ga<sub>0.3</sub>As QW device layers grown on Si, GaAs, and InP substrates. In all cases, In<sub>0.52</sub>Al<sub>0.48</sub>As is the bottom and top barrier layer.

## **Comparable RF-data!**

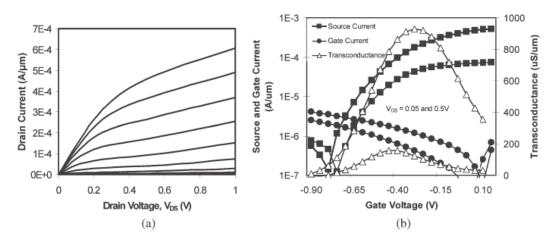

Fig. 3. (a) Output characteristic for 80-nm  $L_g$  In<sub>0.7</sub>Ga<sub>0.3</sub>As QW transistor on 3.2- $\mu$ m metamorphic buffer on silicon (gate voltage  $V_G$  is swept from 0.0 to -0.8 V in -0.1-V steps). (b) Transfer characteristic for 80-nm  $L_g$  In<sub>0.7</sub>Ga<sub>0.3</sub>As QW transistor on 3.2- $\mu$ m buffer on silicon with  $V_{DS}=0.5$  and 0.05 V. Peak transconductance  $g_{\rm m}$  for this device was 930  $\mu$ S/ $\mu$ m at  $V_{DS}=0.5$  V.

- well behaved IV characteristics!

- good DC numbers at 80 nm Lg

- comparable RF data to lattice matched devices

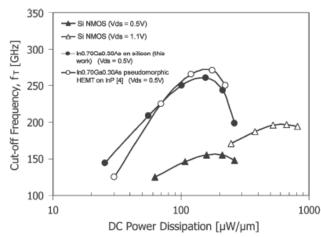

Fig. 4. Plot of deembedded unity gain cutoff frequency as a function of dc power dissipation for 0.5-V  $V_{\rm DS}$  80-nm  $L_g$  In<sub>0.7</sub>Ga<sub>0.3</sub>As QW transistors on both silicon and InP substrates, benchmarked against 60-nm  $L_g$  silicon NMOS transistors at  $V_{\rm DS}=0.5$  and 1.1 V.

# Logic Suitability of 50-nm In<sub>0.7</sub>Ga<sub>0.3</sub>As HEMTs for Beyond-CMOS Applications

Dae-Hyun Kim, Jesús A. del Alamo, Jae-Hak Lee, and Kwang-Seok Seo

| n+ Cap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | InGaAs, x = 0.53 | 20 nm  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------|

| Stopper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | InP              | 6 nm   |

| Barrier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | InAlAs, x = 0.52 | 8 nm   |

| δ-doping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Si               | (2)    |

| Spacer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | InAlAs, x = 0.52 | 3 nm   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | InGaAs, x = 0.53 | 3 nm   |

| Channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | InGaAs, x = 0.7  | 8 nm   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | InGaAs, x = 0.53 | 4 nm   |

| Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | InAlAs, x = 0.52 | 500 nm |

| The second secon | COMPANY COMPANY  |        |

3 Inch S. I. InP Substrate

TABLE  $\,$  I Detailed Gate Structural Information for Four Types of  $In_{0.7}Ga_{0.3}As$  HEMTs That Are Fabricated in This Paper

|                            | Type-A                                       | Туре-В                                   | Туре-С                                   | Type-D                                   |  |  |  |

|----------------------------|----------------------------------------------|------------------------------------------|------------------------------------------|------------------------------------------|--|--|--|

| Barrier                    | InP/In <sub>0.52</sub> Al <sub>0.48</sub> As | In <sub>0.52</sub> Al <sub>0.48</sub> As | In <sub>0.52</sub> Al <sub>0.48</sub> As | In <sub>0.52</sub> Al <sub>0.48</sub> As |  |  |  |

| Stack                      | Ti/Pt/Au                                     | Ti/Pt/Au                                 | Pt/Ti/Mo/Au                              | Buried-Pt/Ti/Mo/Au                       |  |  |  |

| t <sub>ins</sub> [nm]      | 17                                           | 11                                       | 11                                       | 7                                        |  |  |  |

| $\Phi_{B}\left[ eV\right]$ | ~ 0.4                                        | ~ 0.6                                    | ~ 0.7                                    | ~ 0.8                                    |  |  |  |

Fig. 1. Epitaxial layer structure of the In<sub>0.7</sub>Ga<sub>0.3</sub>As HEMTs that are fabricated in this paper.

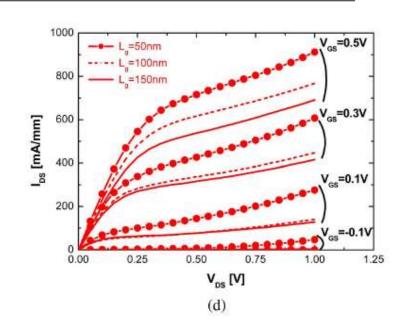

- 4 types of transistors

- Schottky barrier and insulator thickness

- good DC characteristics

- weak scaling with gate length

# 1600 Ti on InP Ti on InAlAs Pt on InAlAs Vos = 0.5 V Vos = 0.5 V Vos [V]

Fig. 5. Transconductance  $(G_m)$  characteristics of all 50-nm  $\rm In_{0.7}Ga_{0.3}As$  HEMTs at  $V_{\rm DS}=0.5$  V.

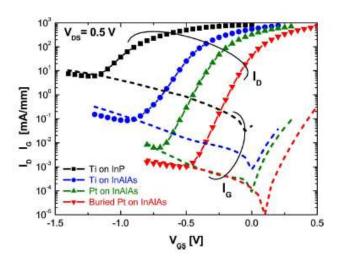

Fig. 6. Semilog plot of  $I_D$  and  $I_G$  of all 50-nm Ino.7Gao.3As HEMTs at  $V_{\rm DS}=0.5~{\rm V}.$

# Scaling with Schottky barrier and insulator thickness

- Tight control needed to improve the performance

$\begin{array}{c} TABLE \quad II \\ SUMMARY \ of \ Logic \ Figures \ of \ Merit \ for \ Four \ Types \\ of \ 50-nm \ In_{0.7}Ga_{0.3}As \ HEMTs \end{array}$

|        | V <sub>T</sub> [V] | DIBL [mV/V] | S [mV/dec] | $I_{\rm ON}/I_{\rm OFF}$ |  |  |

|--------|--------------------|-------------|------------|--------------------------|--|--|

| Type-A | -1.10              | 300         | 200        | 63                       |  |  |

| Туре-В | -0.65              | 220         | 130        | $1 \times 10^3$          |  |  |

| Туре-С | -0.55              | 180         | 100        | $7.2 \times 10^3$        |  |  |

| Type-D | -0.20              | 160         | 86         | $1.7 \times 10^4$        |  |  |

#### Improved speed and/or reduced power consumption

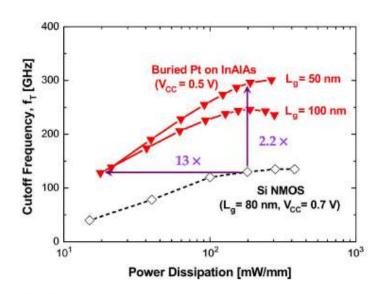

Fig. 11. Cutoff frequency  $(f_T)$  of our 50- and 100-nm type D  $In_{0.7}Ga_{0.3}As$  HEMTs and 80-nm Si MOSFETs as a function of the dc power dissipation.

Well selected technology is required to maximize lon/loff ratio  Depending on bias condition benefits can be found in the areas of speed and/or power dissipation

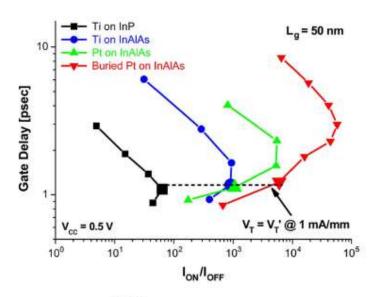

Fig. 14. Gate delay (CV/I) of all 50-nm  $In_{0.7}Ga_{0.3}As$  as a function of  $I_{\rm ON}/I_{\rm OFF}$ .

# 22FFL: A High Performance and Ultra Low Power FinFET Technology for Mobile and RF Applications

B. Sell, B. Bigwood, S. Cha, Z. Chen, P. Dhage, P. Fan, M. Giraud-Carrier, A. Kar, E. Karl, C.-J. Ku, R. Kumar, T. Lajoie, H.-J. Lee, G. Liu, S. Liu, Y. Ma, S. Mudanai, L. Nguyen, L. Paulson, K. Phoa, K. Pierce, A. Roy, R. Russell, J. Sandford, J. Stoeger, N. Stojanovic, A. Sultana, J. Waldemer, J. Wan, W. Xu, D. Young\*, J. Zhang, Y. Zhang and P. Bai

Logic Technology Development, \*Corporate Quality Network, Intel Corporation, Hillsboro, OR, USA email: bernhard.sell@intel.com

|                       | High Performance<br>Logic Transistor |      | Low Power<br>Logic Transistor |      |                  | Ultra Low Power<br>Logic Transistor | Analog<br>Transistor          |      |      | High Voltage<br>Transistor |       |               |       |

|-----------------------|--------------------------------------|------|-------------------------------|------|------------------|-------------------------------------|-------------------------------|------|------|----------------------------|-------|---------------|-------|

| Device                | ULVT                                 | LVT  | LPLVT                         | HP   | Nom              | LP                                  | LL                            | AL   | AL   | AL                         | TGLV  | TGMV          | TGHV  |

| VDD [Volt]            | 0.7                                  | 0.7  | 0.7                           | 0.7  | 0.7              | 0.7                                 | 0.7                           | 0.7  | 0.7  | 0.7                        | 1.2   | 1.5           | 1.8   |

| Gate Pitch [nm]       | 108                                  | 108  | 108                           | 108  | 108              | 108                                 | 144                           | 144  | 216  | 270                        | 216   | 216           | 270   |

| Fin Pitch [nm]        | 45                                   | 45   | 45                            | 45   | 45               | 45                                  | 45                            | 45   | 45   | 45                         | 45    | 45            | 45    |

| Tox                   | Thin                                 | Thin | Thin                          | Thin | Thin             | Thin                                | Thick                         | Thin | Thin | Thin                       | Thick | Thick         | Thick |

| Performance<br>Metric | NMOS/PMOS<br>Idsat/loff [mA/um]      |      |                               |      |                  |                                     | GM*Rout NMOS/PN<br>Idsat [mA/ |      |      | 1000                       |       |               |       |

| Value                 | 1.24/1.22 @ 0.7V,<br>10nA/um         |      |                               |      | 0.81 @<br>00pA/u |                                     | 0.10/0.10 @ 0.7V,<br>1pA/um   | 47   | 54   | 60                         | 0.77/ | 1.01/<br>0.87 | 1.11/ |

Table 1. Transistor design rules and electrical characteristics for logic, analog and high voltage transistors developed for 22FFL.

Fig. 1. Fin and gate cut TEMs of logic and 1.8V IO transistors.

# 22FFL: A High Performance and Ultra Low Power FinFET Technology for Mobile and RF Applications

B. Sell, B. Bigwood, S. Cha, Z. Chen, P. Dhage, P. Fan, M. Giraud-Carrier, A. Kar, E. Karl, C.-J. Ku, R. Kumar, T. Lajoie, H.-J. Lee, G. Liu, S. Liu, Y. Ma, S. Mudanai, L. Nguyen, L. Paulson, K. Phoa, K. Pierce, A. Roy, R. Russell, J. Sandford, J. Stoeger, N. Stojanovic, A. Sultana, J. Waldemer, J. Wan, W. Xu, D. Young\*, J. Zhang, Y. Zhang and P. Bai

Logic Technology Development, \*Corporate Quality Network, Intel Corporation, Hillsboro, OR, USA email: bernhard.sell@intel.com

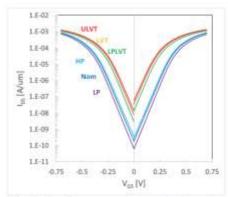

Fig. 5. I<sub>DS</sub>-V<sub>GS</sub> curves demonstrating low subthreshold slope and DIBL for all logic devices.

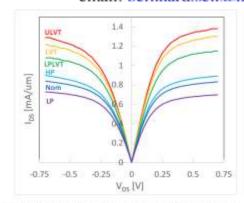

Fig. 6 Balanced I<sub>DS</sub>-V<sub>DS</sub> characteristics for all logic transistors.

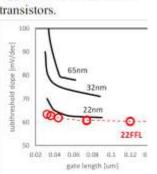

Fig. 7. Channel length dependence of thin subthreshold slope compared to previo technologies.

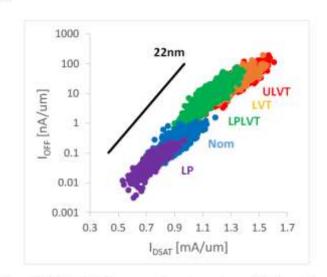

Fig. 3. NMOS I<sub>Dsat</sub> vs. I<sub>off</sub> showing 57% gain over 22nm HP transistors presented in [1].

#### Improved speed and/or reduced power consumption

# Intel 22nm FinFET (22FFL) Process Technology for RF and mmWave Applications and Circuit Design Optimization for FinFET Technology

H.-J. Lee, S. Rami, S. Ravikumar, V. Neeli, K. Phoa, B. Sell, and Y. Zhang Logic Technology Development, Intel Corporation, Hillsboro, Oregon, USA, email: hyung-jin.lee@intel.com

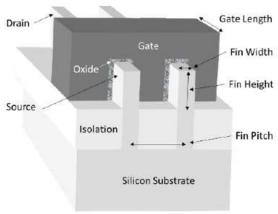

Figure 1: 3D view of FinFET device structure

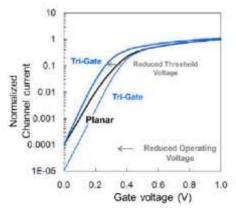

Figure 2:I-V curves of FinFET and Planar demonstrating DIBL improvement by FinFET technologies

Tri-gates optimized for RF-operation

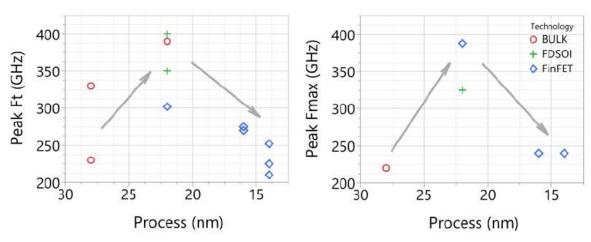

## Parasitics are Limiting Performance at Scaled Nodes

- Currently best performance is obtained at about 20 nm node!

Figure 5:  $f_t$  and  $f_{max}$  trends by process node: both  $f_t$  and  $f_{max}$  reach the peak performance around  $20 \sim 25$ nm due to the excessive parasitic capacitance by high density interconnect

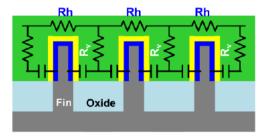

Figure 3: FinFET gate resistance structure: Horizontal resistance (R<sub>h</sub>) and Vertical resistance (R<sub>v</sub>) surrounding fin structures

- Parasitics are related to gate resistance and capacitances (lack of space)