**Research-oriented course**

Learning by reading research articles

- Identify key facts from articles

- Use commencial simulation tool to identify transistor benefits in circuit

- Writing short research article

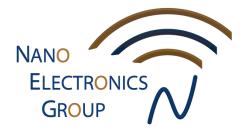

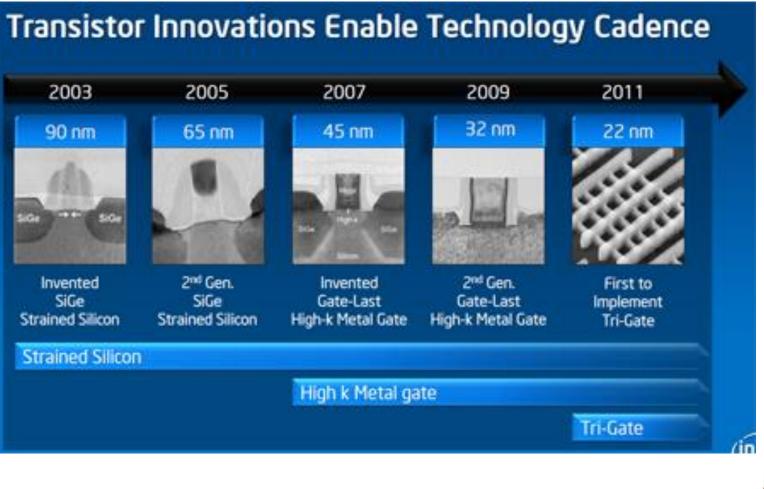

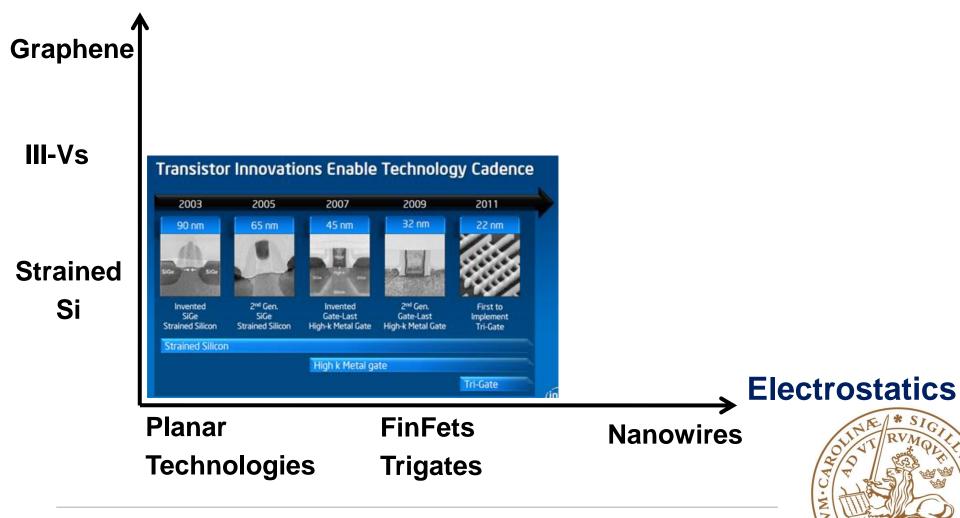

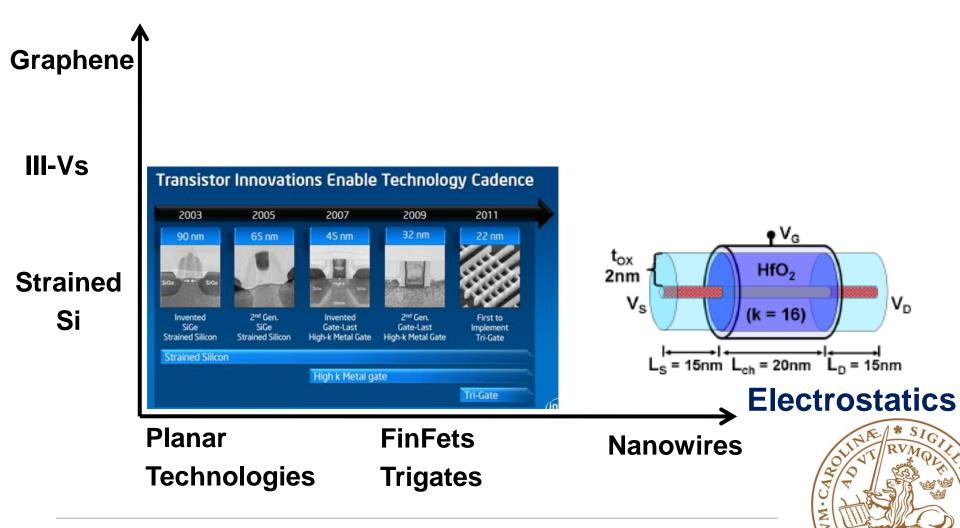

## **Transistor Scaling and Research Roadmap**

Robert Chau, Intel, ICSICT 2004

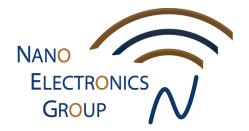

## Scaling Laws 2018...

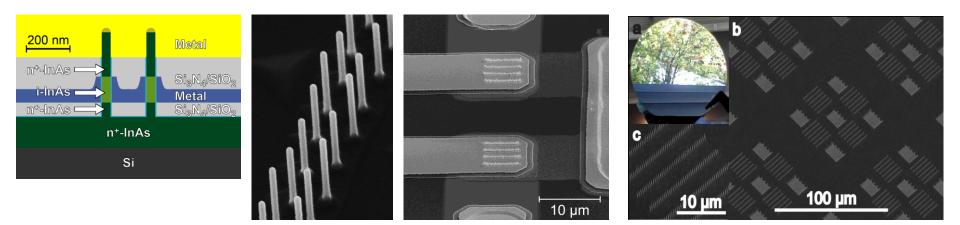

## **Vertical III-V Nanowires in the Roadmaps**

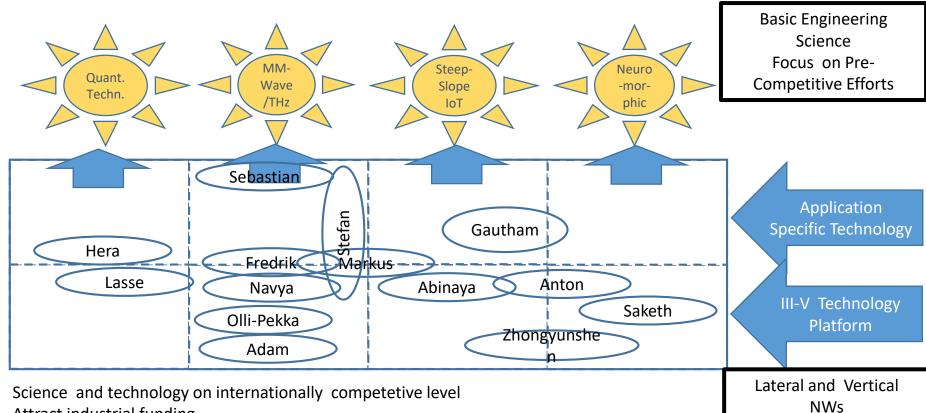

Lateral and vertical III-V nanowires are part of IRDS Roadmap! Lund University has demonstrated state-of-the-art performance devices! How to take advantage of our demonstrated knowledge basis?

Adapted from IRDS, Logic core device technology roadmap, More Moore report, 2017

| Year                     | 2017                              | 2019             | 2021             | 2024                           | 2027                               | 2030                               |

|--------------------------|-----------------------------------|------------------|------------------|--------------------------------|------------------------------------|------------------------------------|

| Device<br>Structure<br>s | FinFET<br>Gete<br>Wates<br>FD-SOI | Lateral Nanowire | Lateral Nanowire | Lateral Nanowire               | Lateral Nanowire                   | Vertical Nanowire                  |

| Channel                  | Si                                | SiGe25%          | SiGe50%          | Ge, <b>III-V</b> ,<br>TFET, 2D | Ge, <b>III-V</b> ,<br>TFET, 2D mat | Ge, <b>III-V</b> ,<br>TFET, 2D mat |

Courtesy of C. Convertino IBM

#### Nanoelectronics 2030-45

Attract industrial funding

**Complex oxides** BEOL

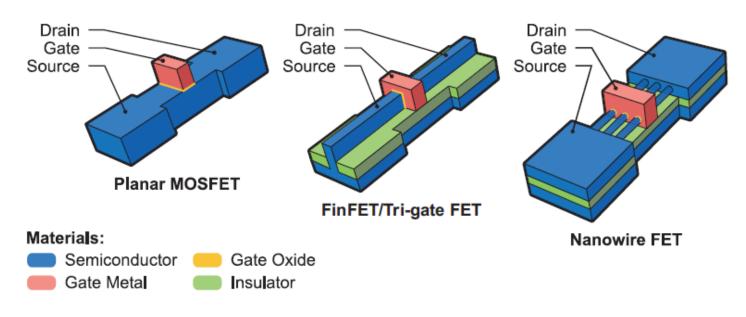

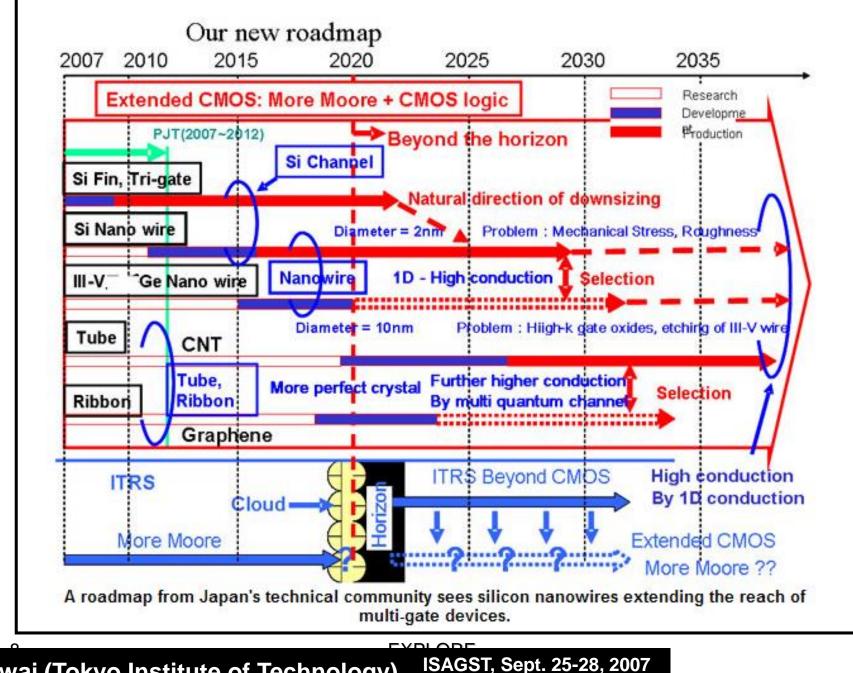

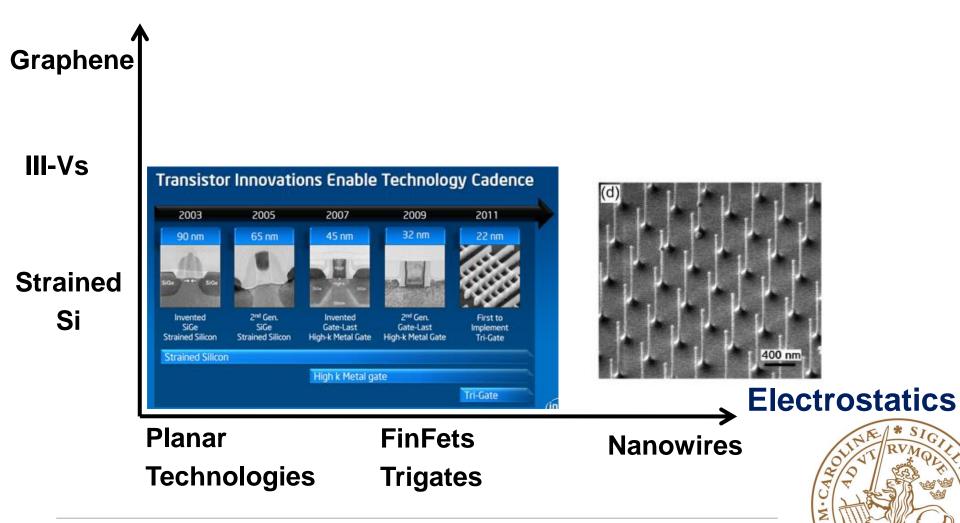

#### Nanowires are a natural extension of the transistor evolution

#### Riel et al, MRS Bulletin 2014

## **Why III-V Nanowires**

Why III-V Nanowires?

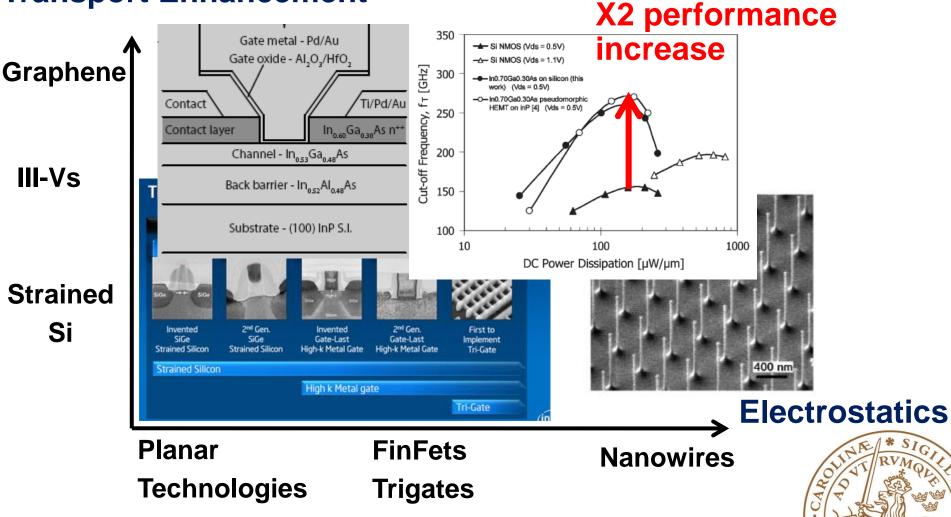

- Advantageous transport

- Wrap-gate geometry

- Band gap engineering

- Small nanowire footprint

- $\rightarrow$  high transconduc. and  $I_{on}$

- $\rightarrow$  low output conduc. and DIBL

- $\rightarrow$  increased breakdown, reduced  $I_{\text{off}}$

- $\rightarrow$  reduced defect propagation probability

H. Iwai (Tokyo Institute of Technology),

Dallas, Texas, USA

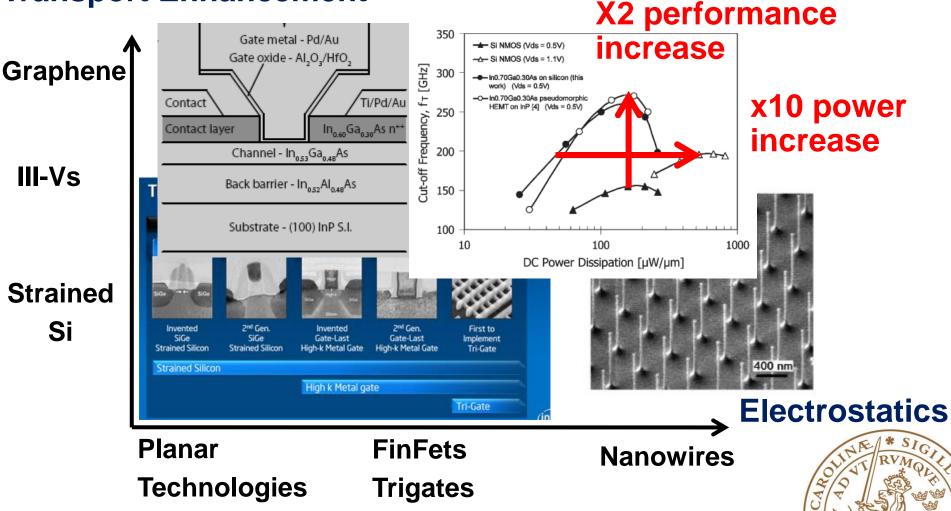

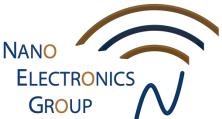

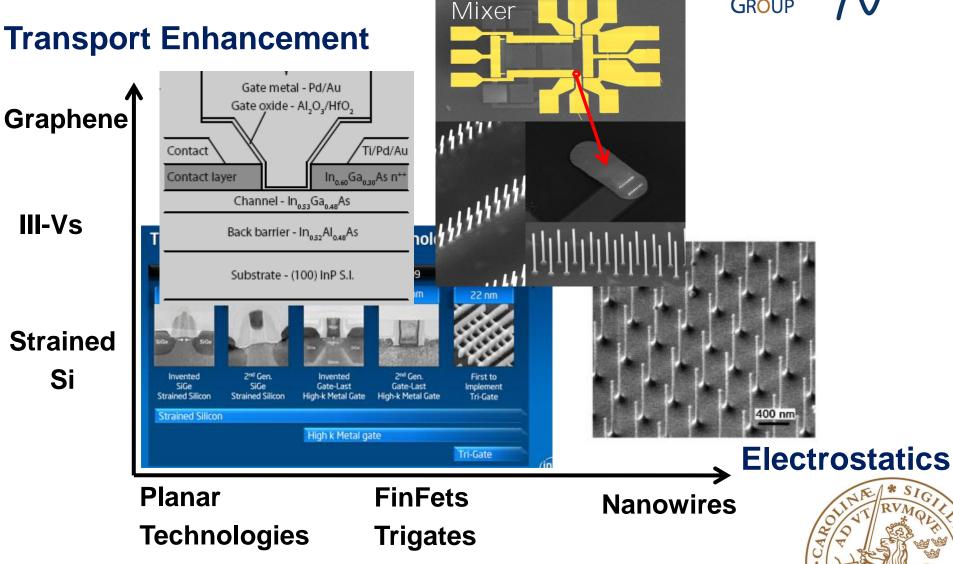

## **Transport Enhancement**

## **Transport Enhancement**

#### **Transport Enhancement**

#### **Transport Enhancement**

#### **Transport Enhancement**

## What will you learn in this course?

How small transistors can we make?

How do we compare data for different transistors?

What are good numbers for a transistor?

What is the relation between the physics, the technology and the performance?

What are the ultimate limits in terms of power consumption?

What are the benefits of nanotechnology?

How can we implement high-speed circuits?