# Inverters with strained Si nanowire complementary tunnel field-effect transistors

L. Knoll, Q. T. Zhao, *Member*, *IEEE*, A. Nichau, S. Trellenkamp, S. Richter, A. Schäfer, D. Esseni, L. Selmi, K. K. Bourdelle, S. Mantl, *Member*, *IEEE*

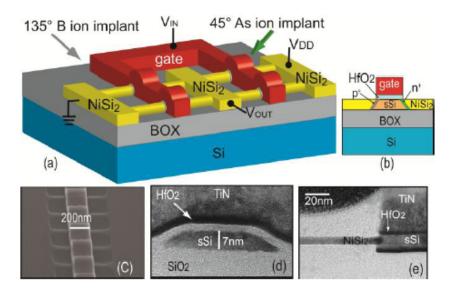

Fig.1 (a) Schematic of sSi NW TFET inverter fabricated using tilted B<sup>+</sup> and As<sup>+</sup> ion implantations into epitaxial NiSi<sub>2</sub> S/D contacts. Highly doped n<sup>+</sup> and p<sup>+</sup> pockets at the silicide edges are created with IIS after a low temperature anneal (b), forming an n-TFET on the left and a p-TFET on the right in Fig.1(a). (c) SEM image of the NW array TFET; (d) XTEM image of single sSi nanowire with gate stack. (e) XTEM cross section along the NW, indicating a perfectly aligned NiSi<sub>2</sub> contact to the channel.

Implantation used to form shallow junctions with low temperature annealing (450 C)

NiSi<sub>2</sub> leads to reduce resistance (silicidation of thin Ni layer 3 nm)

Inverter configuration

### **Device Performance**

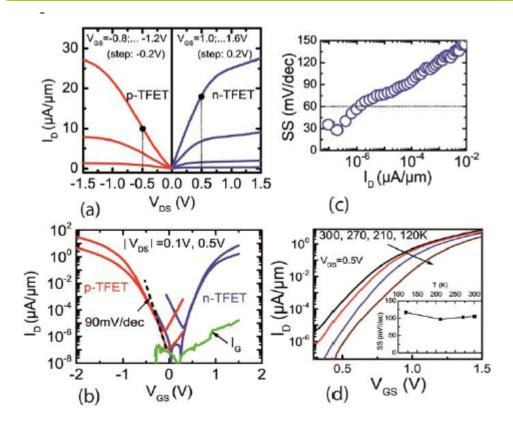

Fig.2. (a)  $I_D$ - $V_{DS}$  characteristics of NW array C-TFETs showing high oncurrents; (b) The corresponding  $I_D$ - $V_{GS}$  characteristics of sSi NW array C-TFETs, providing a minimum SS of 30 mV/dec for the n-FET(c), and of 90 mV/dec for the p-TFETs at 300 K. The  $I_D$ -range with SS < 60 mV/dec extends over one order of magnitude of  $I_D$  (c). The low temperature (T) measurements demonstrate a BTBT dominated transport mechanism (d) with an almost constant SS in the investigated temperature range.

Balanced on-performance  $I_{on}$  about 10µA/µm

n-FET with low SS at low current levels

p-FET higher SS due to Trap-Assisted-Tunneling (TAT) Less abrupt doping profile at the junction

## **Inverter Performance**

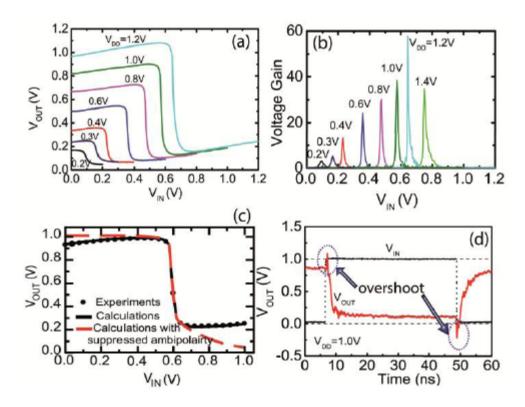

Fig. 3. VTC (a) and voltage gain (b) for NW TFET inverters, functioning at  $V_{DD}$ =0.2V. (c) Experimental and calculated VTC for NW TFET at  $V_{DD}$ =1 V. The calculation confirms that the nominal value of the high  $V_{OUT}$  recovers to  $V_{DD}$ =1 V and the low  $V_{OUT}$  approaches to 0V as the ambipolarities of both the n- and p-type transistors are removed. (d) Transient response of NW C-TFET inverter at  $V_{DD}$ =1.0 V, showing clear voltage overshoots.

Good VTC with high gain and gain also at V<sub>dd</sub>=0.2 V!

Reduction in voltage swing due to ambipolar conduction (confirmed by modeling)

Inverter rise time ~3 ns Inverter fall time ~2 ns (10-90 %)

Propagation delay ~ 1.9 ns

Overshoot due to large Miller capacitance

#### โหลาเบอเองแบบแบร. พบห

### Fabrication and Characterization of an InAlAs/InGaAs/InP Ring Oscillator Using Integrated Enhancement- and Depletion-Mode High-Electron Mobility Transistors

A. Mahajan, G. Cueva, M. Arafa, P. Fay, and I. Adesida

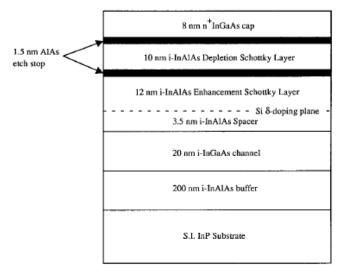

Fig. 1. Cross section diagram of MBE-grown layer structure used in this work.

Use of two etch stop layers to fabricate both E- and D-Mode transistors

#### Nanoelectronics: High-Speed Circuits

**Ring Oscillator**

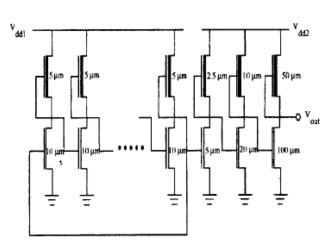

Fig. 6. Schematic for the ring oscillators.

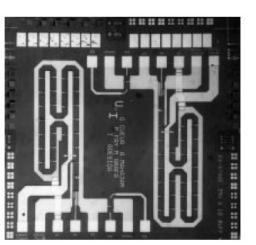

Fig. 7. Die photo of the completed 23 stage ring oscillator.

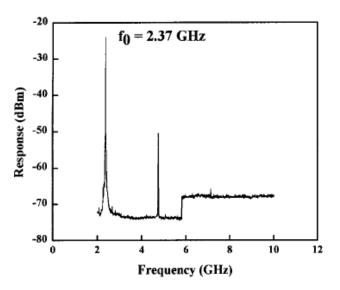

Fig. 8. Spectrum of output of 23 stage 0.25  $\mu m$  gate-length ring oscillator with  $V_{\rm dd}\!=\!0.4$  V.

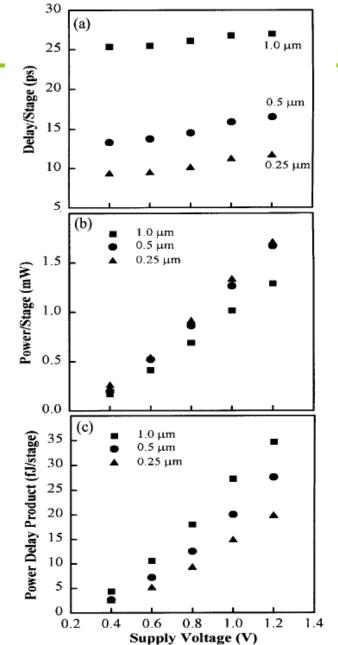

Fig. 9. (a)  $t_{pd}$ , (b)  $P_D$  and (c) PDP as a function of supply voltage for 1.0, 0.5 and 0.25  $\mu$ m gate-length inverters.

### Quantum cellular automata

### Craig S Lent, P Douglas Tougaw, Wolfgang Porod and Gary H Bernstein

Department of Electrical Engineering, University of Notre Dame, Notre Dame, IN 46556, USA

Received 1 August 1992, accepted for publication 24 December 1992

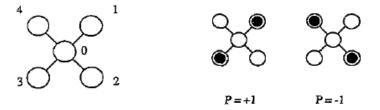

Figure 1. The quantum cell consisting of five quantum dots which are occupied by two electrons. The mutual Coulombic repulsion between the electrons results in bistability between the P = +1 and P = -1 states.

Pure Quantum Mechanics:

Quantum dots with diameter 10 nm Nearest neighbor 20 nm

$$H_0^{\text{sell}} = \sum_{i,\sigma} E_{0,i} n_{i,\sigma} + \sum_{i,\sigma} t(a_{i,\sigma} \dagger a_{0,\sigma} + a_{0,\sigma} \dagger a_{i,\sigma}) + \sum_i E_Q n_{i,\uparrow} n_{i,\downarrow} + \sum_{i>j,\sigma,\sigma'} V_Q \frac{n_{i,\sigma} n_{j,\sigma'}}{|R_i - R_j|}.$$

(1)

$(H_0^{\text{cell}} + H_{\text{inter}}^{\text{cell}})|\Psi_n\rangle = E_n|\Psi_n\rangle.$

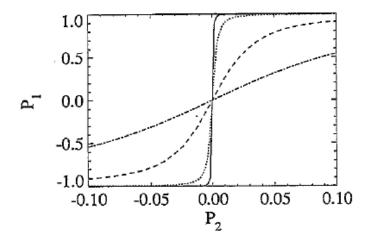

**Figure 2.** The cell-cell response function. The polarization of the right cell is fixed and the induced polarization in the left cell is calculated. (a) The calculated polarization of cell 1 as a function of the polarization of cell 2. Note that the range of  $P_z$  shown is only from -0.1 to +0.1. This is because the transition in the induced polarization is so abrupt. (b) The first four eigen-energies of cell 1. The polarization of the lowest two are shown in (a).

# **Switching behaviour**

Figure 3. The cell-cell response function for various values of the dot-to-dot coupling energy (*t* in equation (1)). The induced cell polarization  $P_1$  is plotted as a function of the neighboring cell polarization  $P_2$ . The results are shown for values of the coupling energy, t = -0.2 (full curve), -0.3 (dotted curve), -0.5 (dashed curve), and -0.7 (dot-dashed curve) meV. Note that the response is shown only for  $P_2$  in the range [-0.1, +0.1].

# **Edge driven computing**

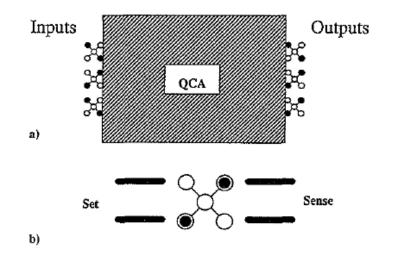

**Figure 4.** The new paradigm for computing with quantum cellular automata (QCAS). The input to the QCA is provided at an edge by setting the polarization state of the edge cells (*edge-driven computation*). The QCA is allowed to dissipatively move to its new ground-state configuration and the output is sensed at the other edge (*computing with the ground state*). The 'set' and 'sense' lines are shown schematically.

#### Transmission lines

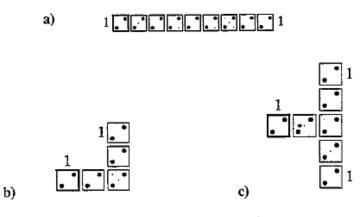

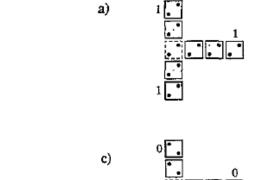

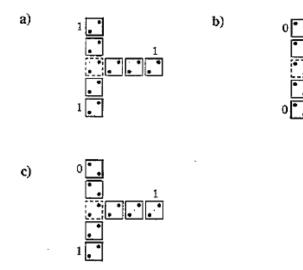

**Figure 5.** QCA wires: (a) the basic wire; (b) a corner in a wire; (c) fan-out of one signal into two channels. In each case the darker (left-hand) cell has a fixed polarization which constitutes the input. Note that these figures are not simply schematic, but are a plot of the results of a self-consistent many-body calculation of the ground state for the cellular array. The diameter of each circle is proportional to the calculated charge density at each site.

### Circuits

0

#### Inverter

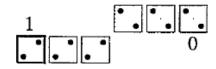

Figure 6. An inverter constructed from a quantum cell automaton.

b)

Figure 8. An AND gate. The cells in darker squares are fixed to the input states. The cell in the dashed square is biased slightly toward the '0' state.

OR gates

Figure 7. An OR gate. The cells in darker squares are fixed to the input states. The cell in the dashed square is biased slightly toward the '1' state.

#### Nanoelectronics: QCA

# **Critical Issues and Benefits**

| Issues:                | Benefits:            |

|------------------------|----------------------|

| Uniform cell occupancy | No interconnects     |

| Dot size control       | High density         |

| Temperature            | Low power            |

|                        | Ultra-fast computing |