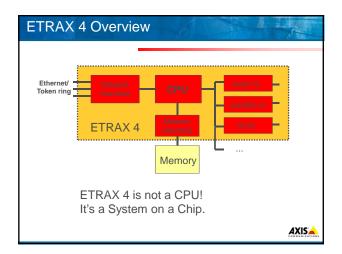

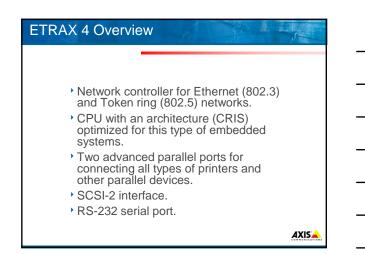

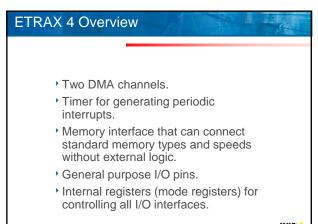

### What is ETRAX?

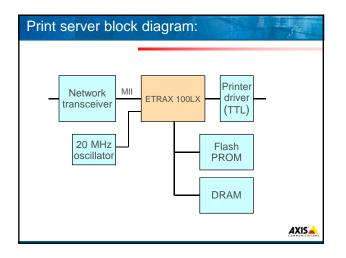

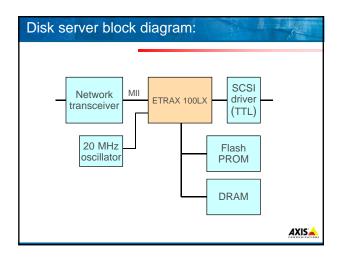

- A family of chips designed by Axis for products that connect peripheral equipment to a LAN (local area network).

- First chip (ETRAX 1) released 1993.

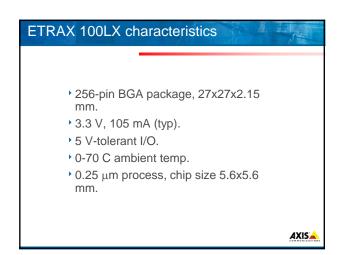

- Latest versions (produced until 2011):

ETRAX 100LX (100 Mbit/s Ethernet)

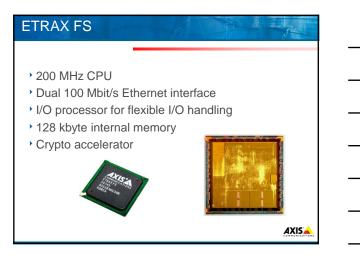

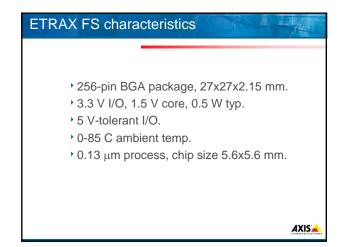

ETRAX FS (dual 100 Mbit/s Ethernet)

- ETRAX 4 (10 Mbit/s Ethernet) will be used in this course.

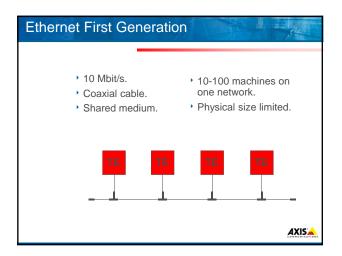

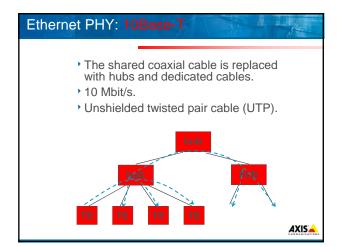

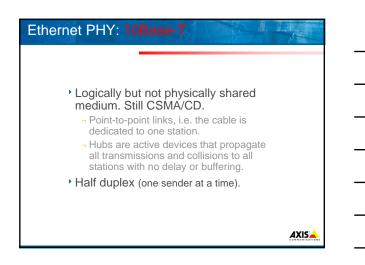

### Ethernet First Generation PHY: 10Base-5

- One sender and multiple receivers.

- Half duplex, i.e. it's not possible to send and receive at the same time.

- Collisions are detected by sensing the voltage levels on the line.

- Cable and cable connectors are expensive and fragile.

AXIS

#

AXIS

AXISA

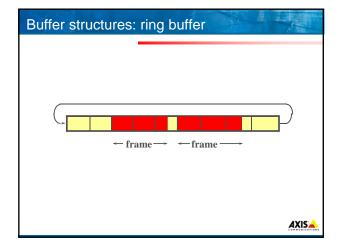

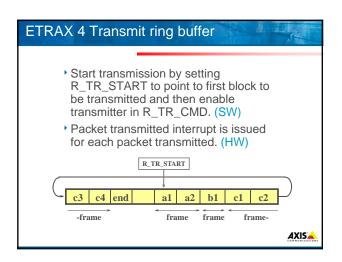

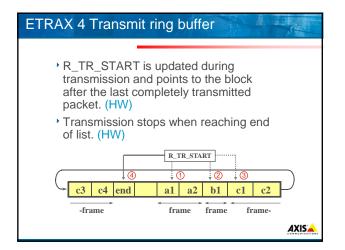

| ETRAX 4: Frames in ring                                                                                                         |  |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| <ul> <li>Frames wrap around at ring buffer end.</li> <li>End of list is indicated by a 256-byte block with cmd == 0.</li> </ul> |  |  |  |  |  |  |  |

| c3     c4     end     a1     a2     b1     c1     c2       -frame     -frame     frame     frame     frame                      |  |  |  |  |  |  |  |

| AXISA                                                                                                                           |  |  |  |  |  |  |  |

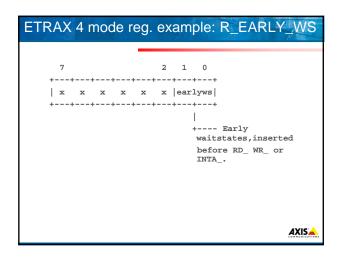

| ETRAX 4 r | node  | registers         |                  | - free |

|-----------|-------|-------------------|------------------|--------|

|           |       |                   |                  |        |

| addres    | S     | register name     | initial<br>value |        |

| 00        | write | R_LATE_WS<7:0>    | FF               |        |

| 01        | write | R_EARLY_WS<1:0>   | 03               |        |

| 02        | write | R_BUS_MODE<7:0>   | 00               |        |

| 04        | write | R_DRAM_MODE<7:0>  | 00               |        |

| 06        | write | R_CLOCK_MODE<7:0> | - FF             |        |

| 07        | write | R_DMA_CONFIG<7:0> | 00               |        |

|           |       |                   |                  |        |

|           |       |                   |                  |        |

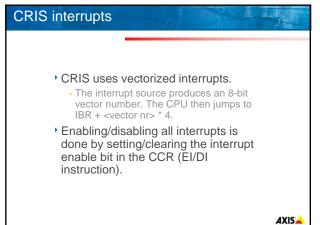

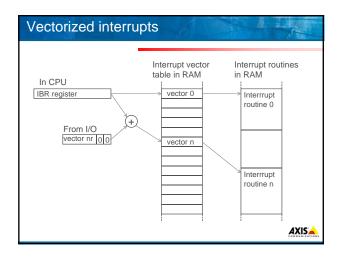

# ETRAX 4 interrupt handling • Before the interrupt handler returns, the interrupt must be cleared (acknowledged). There is therefore an interrupt acknowledge register (or register bit) for each interrupt.

AXIS

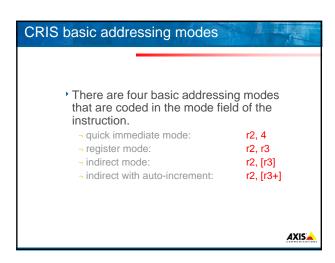

# CRIS complex addressing modes All other addressing modes are implemented using prefix instructions. The prefix instruction generates an address that replaces one of the operands of the next instruction.

AXIS 🖌

| Examples of complex a   | addressing modes                                 |

|-------------------------|--------------------------------------------------|

| add.b<br>add.w          | r1,[1234]<br>r1,[r2+r3.b]                        |

| add.w<br>add.d<br>add.d | r1,[r4=r2+r3.w]<br>r1,[r2+123]<br>r1,[r2=r3+123] |

| add.d                   | r1,[r2+[r3].d]                                   |

|                         | AXISA                                            |

| CRIS branch c                                                     | ondit | tions            | 48  |  | <u>I</u> . | - fe  |  |  |  |

|-------------------------------------------------------------------|-------|------------------|-----|--|------------|-------|--|--|--|

| <ul> <li>There are 16 different branch<br/>conditions:</li> </ul> |       |                  |     |  |            |       |  |  |  |

| bpl                                                               | bmi   | bne<br>bls<br>ba | bhi |  |            |       |  |  |  |

|                                                                   |       |                  |     |  |            | AXISA |  |  |  |

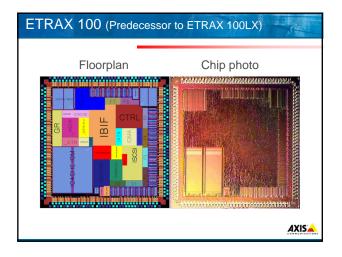

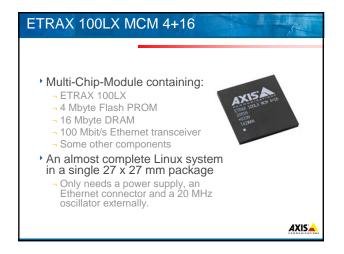

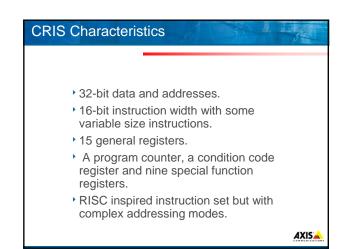

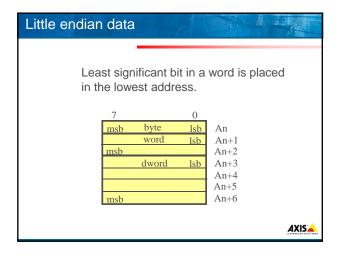

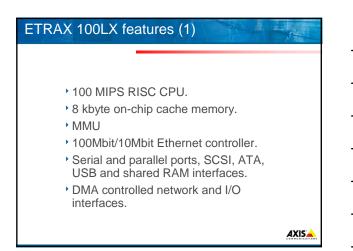

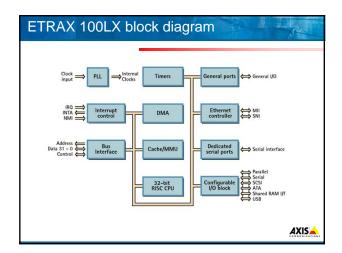

# ETRAX 100LX CPU 100 MIPS 16-bit instruction width. 8, 16 and 32-bit data width. Little endian Supports unaligned data accesses. Axis CRIS instruction set Compatible with ETRAX1-4

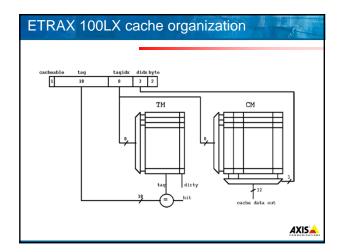

## ETRAX 100LX cache

- Combined instruction and data cache.

- Direct mapped.

- Write allocate.

- · Copy back.

- 8 kbyte

- > 256 entries x 32 byte cache lines

- 32-bit read/write port.

AXIS

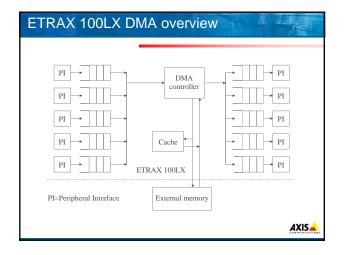

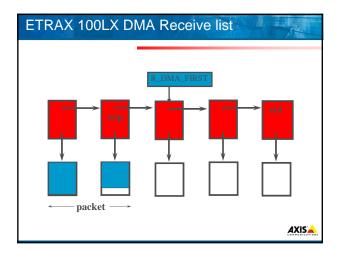

# ETRAX 100LX DMA Characteristics

- Provides low-latency high-throughput data transfer capability to/from peripheral interfaces

- Optimized for block transfers between peripheral interfaces and ETRAX100LX memory

- One DMA controller serving 10 DMA channels

- Connects to 14 peripheral interfaces

- Throughput limited by peripheral interface