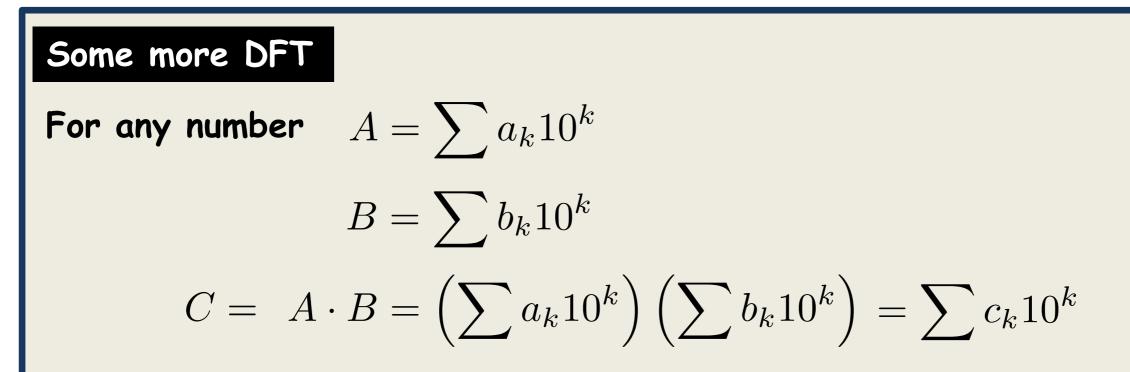

Some more DFT

ap=6 a1=4 a1=5 ...

What is

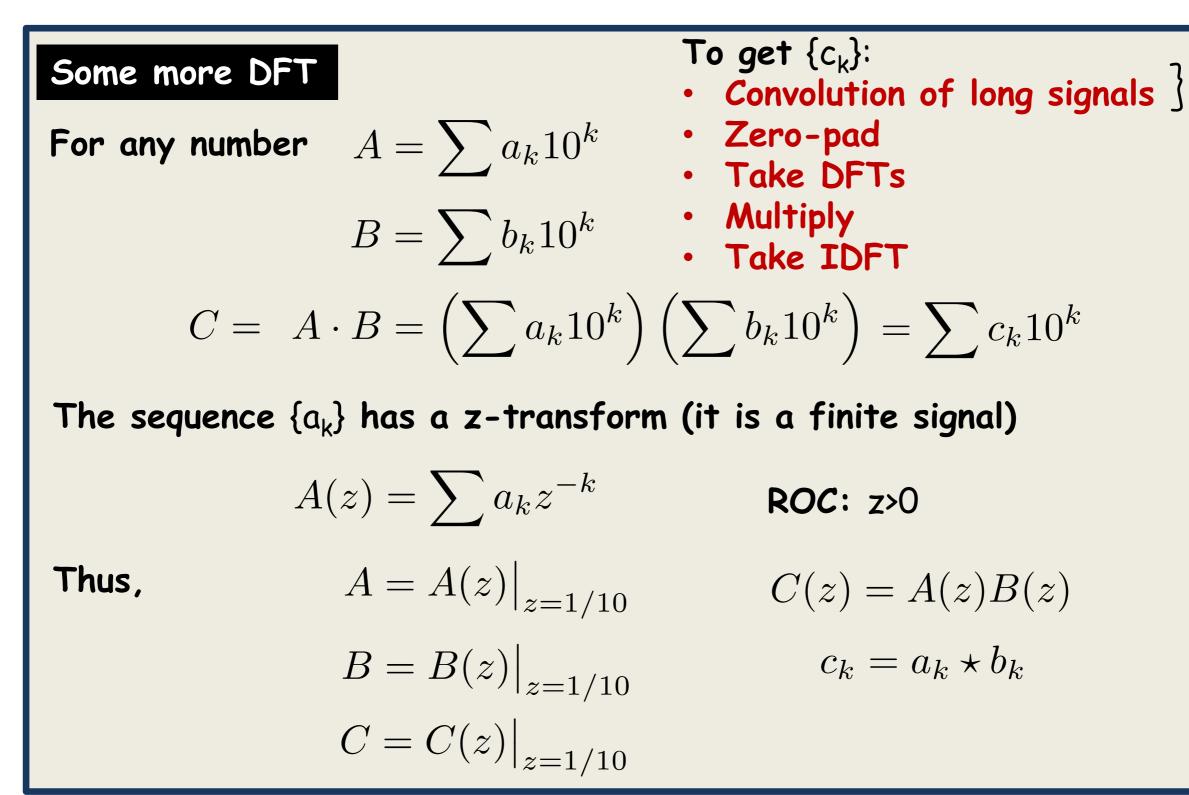

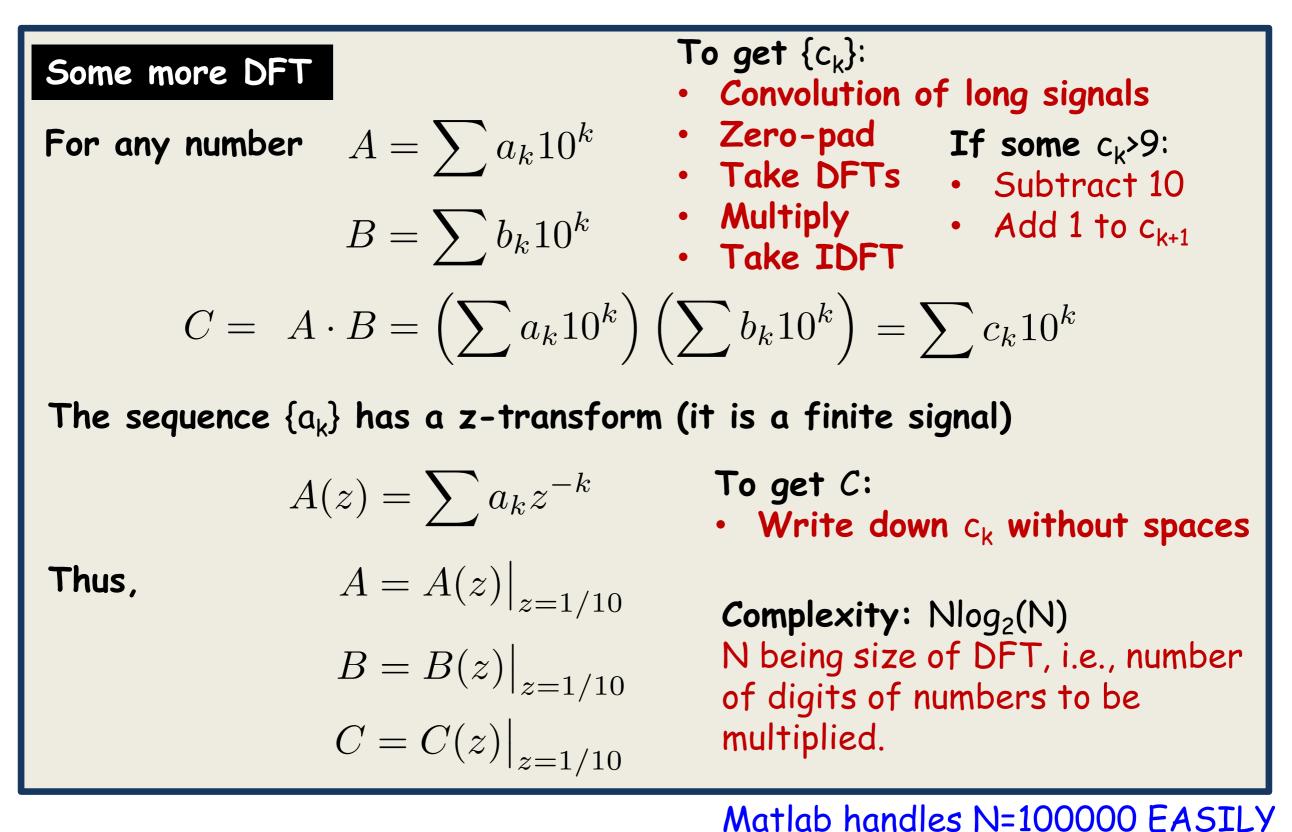

# Some more DFT For any number $A = \sum a_k 10^k$ $B = \sum b_k 10^k$ $C = A \cdot B = \left(\sum a_k 10^k\right) \left(\sum b_k 10^k\right) = \sum c_k 10^k$ The sequence {a<sub>k</sub>} has a z-transform (it is a finite signal)

$$A(z) = \sum a_k z^{-k} \qquad \text{ROC: } z > 0$$

### Some more DFT For any number $A = \sum a_k 10^k$ $B = \sum b_k 10^k$ $C = A \cdot B = \left(\sum a_k 10^k\right) \left(\sum b_k 10^k\right) = \sum c_k 10^k$ The sequence $\{a_k\}$ has a z-transform (it is a finite signal) $A(z) = \sum a_k z^{-k}$ **ROC:** z>0 $A = A(z)\big|_{z=1/10}$ Thus, C(z) = A(z)B(z) $c_k = a_k \star b_k$ $B = B(z)\big|_{z=1/10}$ $C = C(z) \Big|_{z=1/10}$

Some implementation aspects

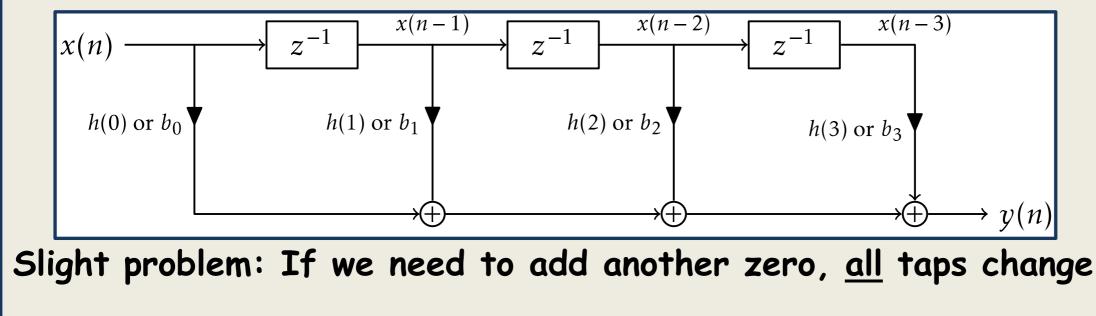

Start with FIR filters

$$y(n) = \sum_{k=0}^{K} h(k)x(n-k) = \sum_{k=0}^{K} b_k x(n-k)$$

(notation for difference equation)

Easy to see that this is an implementation. Direct form I

#### Some implementation aspects

#### Some implementation aspects

#### Some implementation aspects

#### Some implementation aspects

### Some implementation aspects

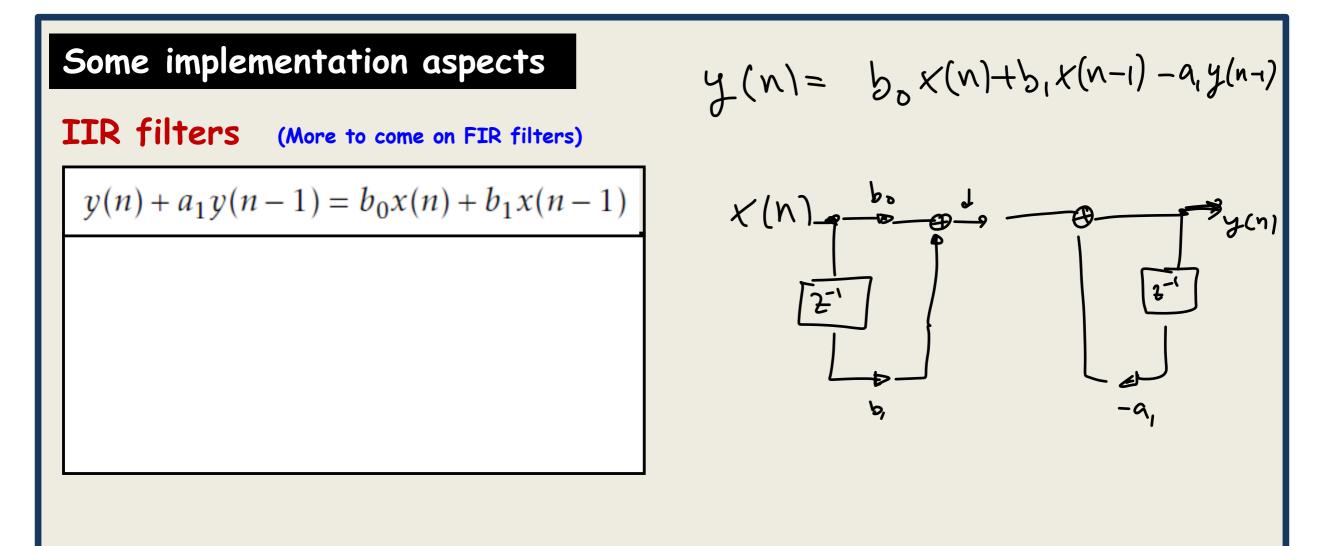

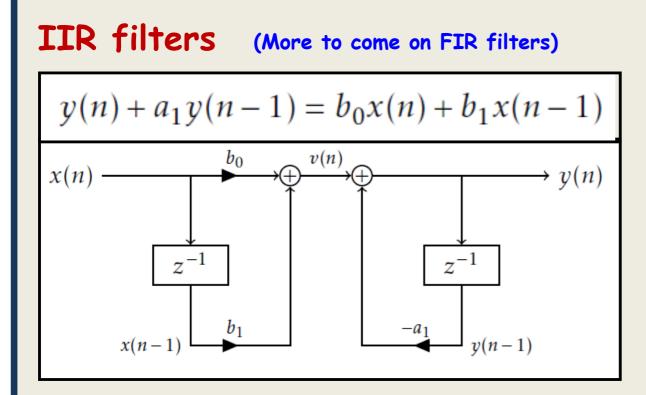

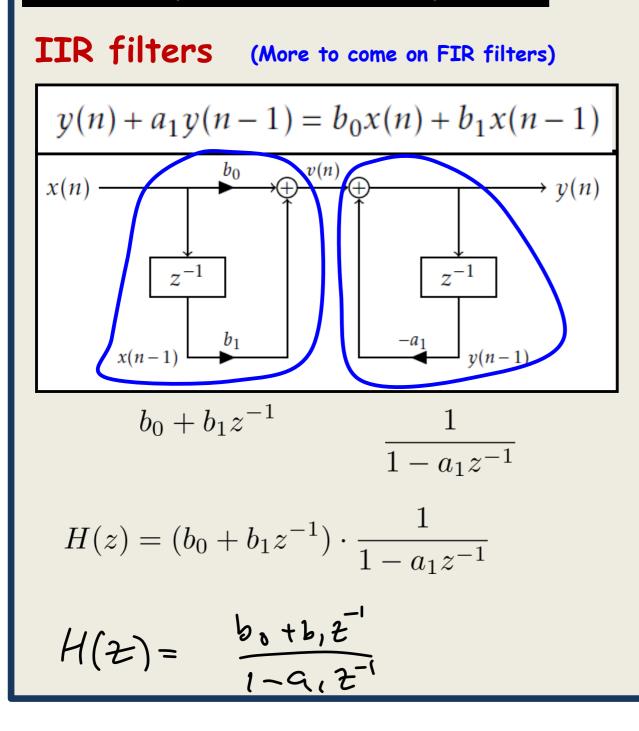

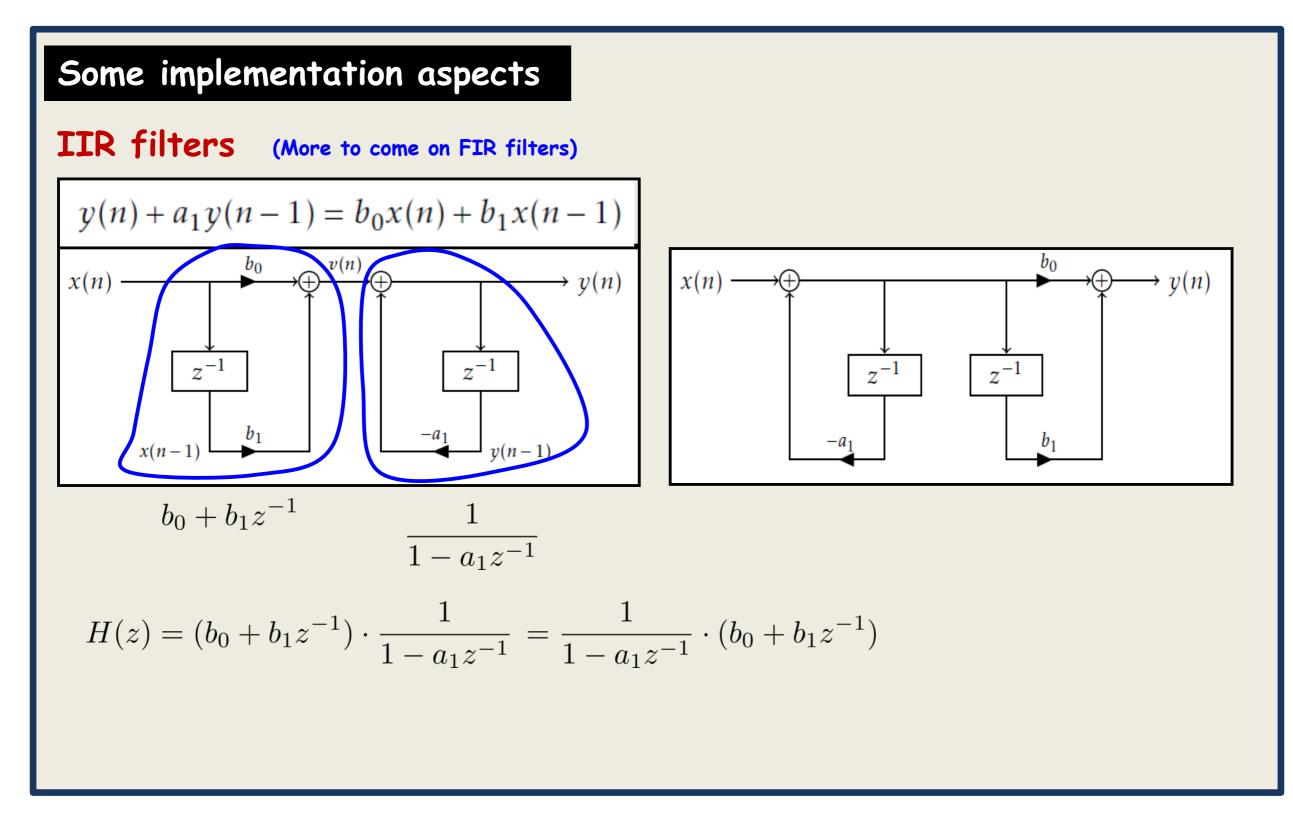

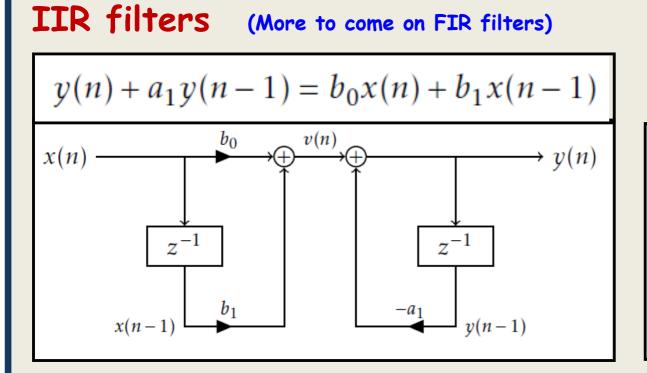

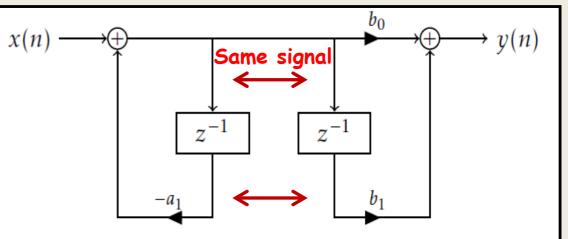

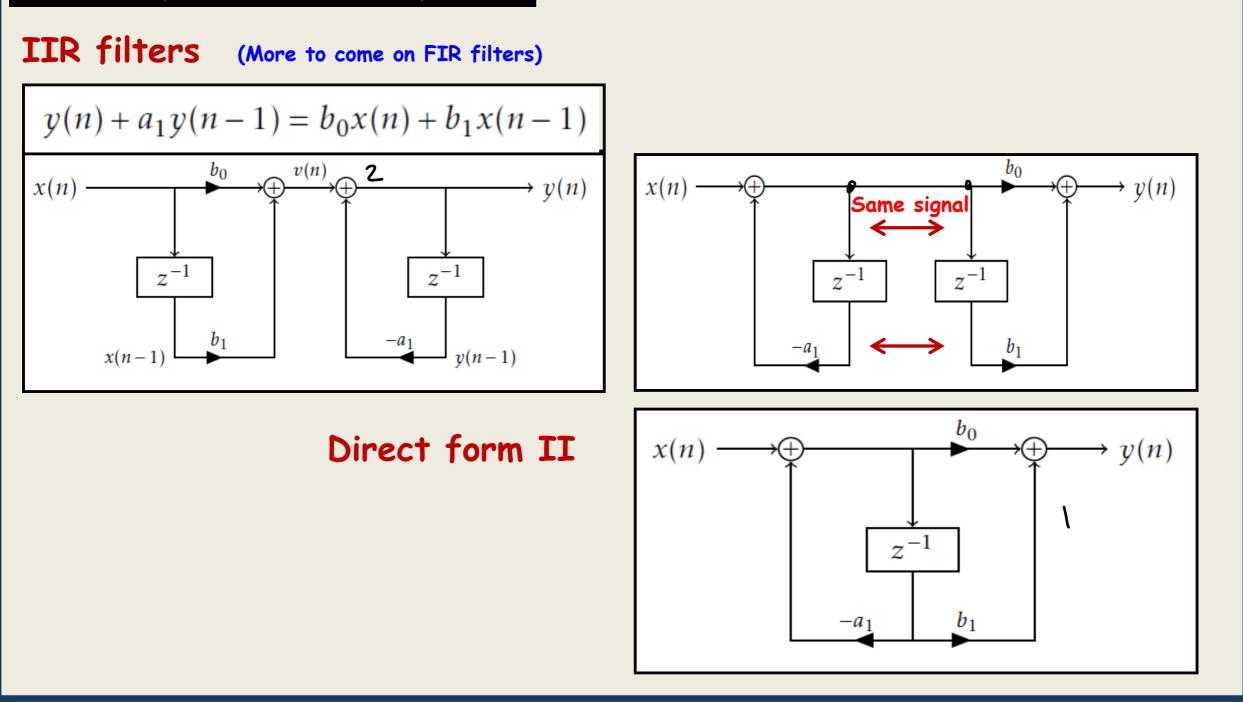

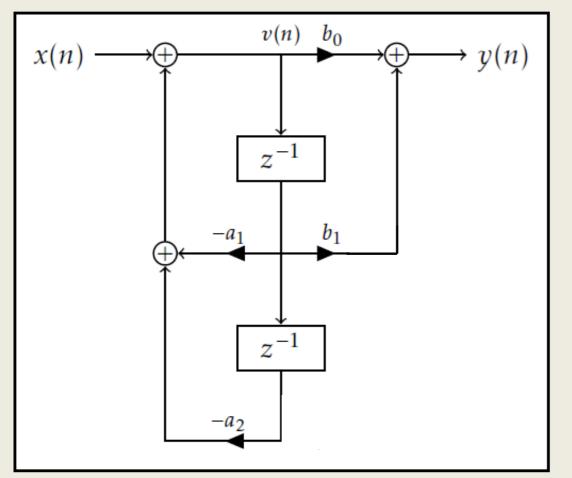

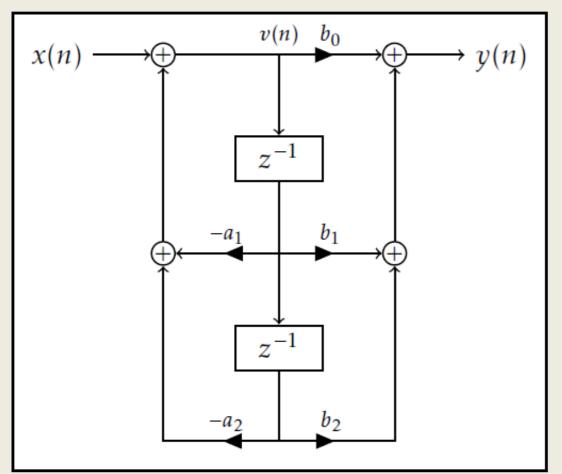

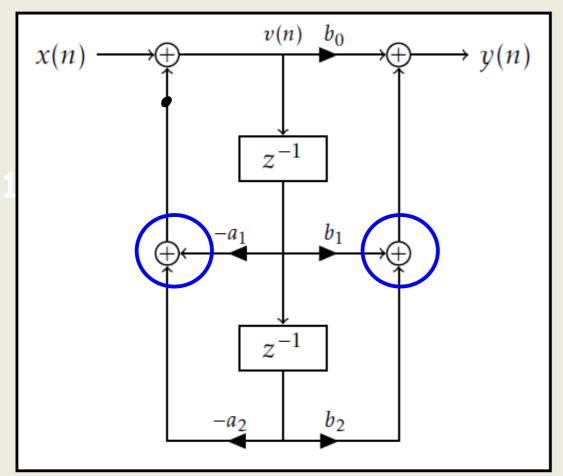

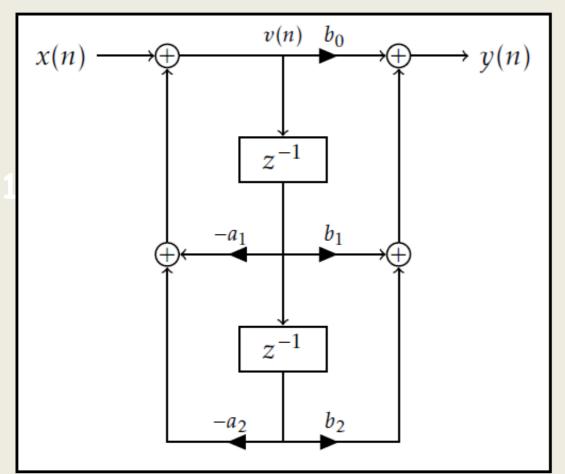

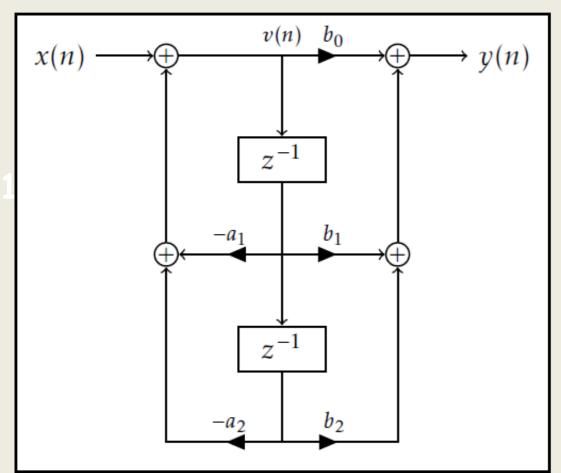

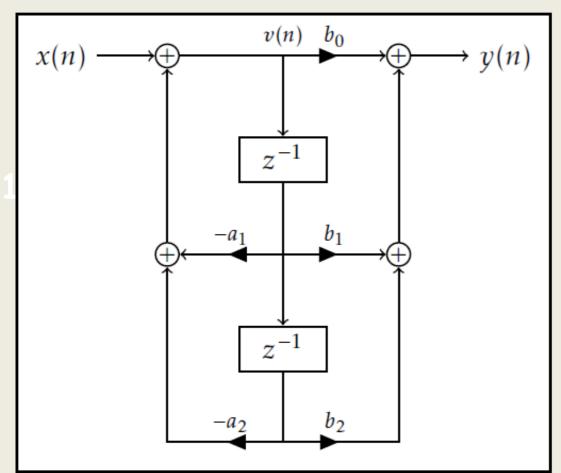

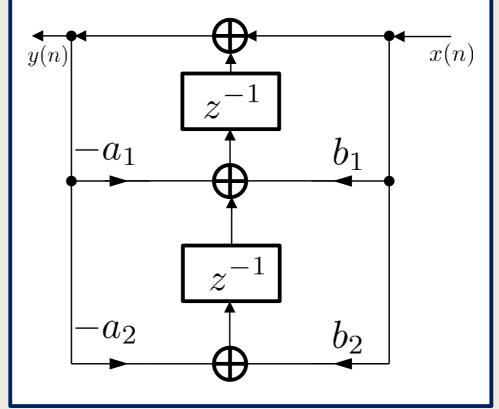

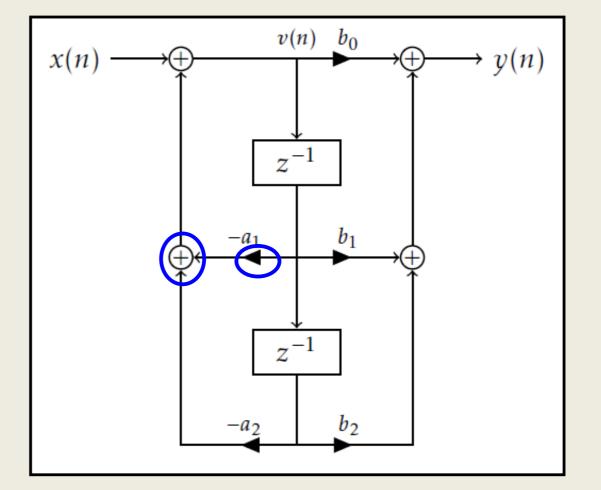

#### **IIR** filters

Second order filter

$$V(t) = -t^{4}a_{1}V(t) - t^{2}a_{2}V(t) + X(t)$$

$$V(t) \left[ 1 + t^{4}a_{1} + t^{2}a_{2} \right] = X(t)$$

$$V(t) = \frac{X(t)}{1 + t^{4}a_{1} + t^{4}a_{2}}$$

$$Y(t) = b_{0}V(t) + t^{4}b_{1}V(t) + t^{4}b_{2}V(t)$$

$$Y(t) = V(t) \left[ b_{0} + t^{4}b_{1} + t^{2}b_{2} \right]$$

$$Y(t) = V(t) \left[ b_{0} + t^{4}b_{1} + t^{2}b_{2} \right]$$

$$Y(t) = \frac{b_{0} + t^{4}b_{1} + t^{2}b_{2}}{1 + t^{4}a_{1} + t^{2}a_{2}} X[t]$$

### Some implementation aspects

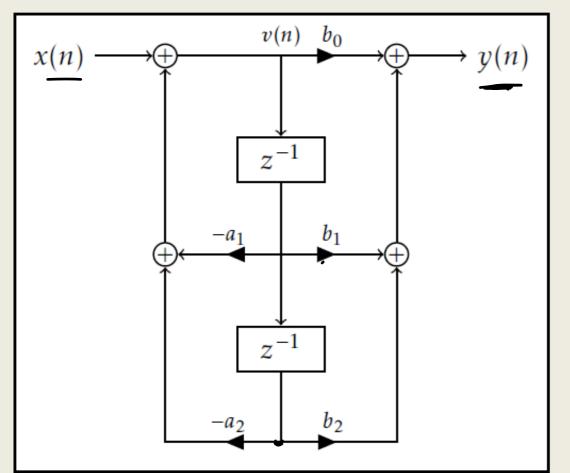

#### **IIR** filters

Second order filter

$$V(z) = -z^{-1}a_1V(z) - z^{-2}a_2V(z) + X(z)$$

$$V(z) + z^{-1}a_1V(z) + z^{-2}a_2V(z) = X(z)$$

$$V(z) \cdot \left(1 + z^{-1}a_1 + z^{-2}a_2\right) = X(z)$$

$$V(z) = \frac{X(z)}{1 + z^{-1}a_1 + z^{-2}a_2} \quad \text{IIR part}$$

$$Y(z) = b_0V(z) + z^{-1}b_1V(z) + z^{-2}b_2V(z)$$

$$Y(z) = V(z) \cdot \left(b_0 + z^{-1}b_1 + z^{-2}b_2\right)$$

$$\text{FIR part}$$

$$Y(z) = \frac{b_0 + z^{-1}b_1 + z^{-2}b_2}{1 + z^{-1}a_1 + z^{-2}a_2} \cdot X(z)$$

### Some implementation aspects

#### **IIR** filters

Second order filter

$$\begin{split} V(z) &= -z^{-1}a_1V(z) - z^{-2}a_2V(z) + X(z) \\ V(z) + z^{-1}a_1V(z) + z^{-2}a_2V(z) &= X(z) \\ V(z) \cdot \left(1 + z^{-1}a_1 + z^{-2}a_2\right) &= X(z) \\ V(z) &= \frac{X(z)}{1 + z^{-1}a_1 + z^{-2}a_2} \quad \text{IIR part} \\ Y(z) &= b_0V(z) + z^{-1}b_1V(z) + z^{-2}b_2V(z) \\ Y(z) &= V(z) \cdot \left(b_0 + z^{-1}b_1 + z^{-2}b_2\right) \\ &\qquad \text{FIR part} \\ Y(z) &= \frac{b_0 + z^{-1}b_1}{1 + z^{-1}a_1 + z^{-2}a_2} \cdot X(z) \end{split}$$

Number of delay elements = max (degree(numerator), degree(denominator))

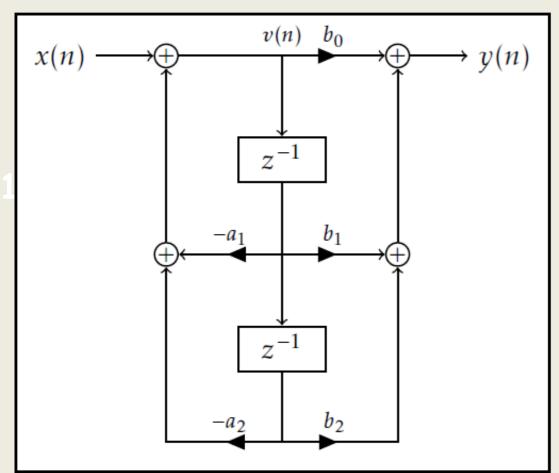

#### Some implementation aspects

#### **IIR** filters

Second order filter

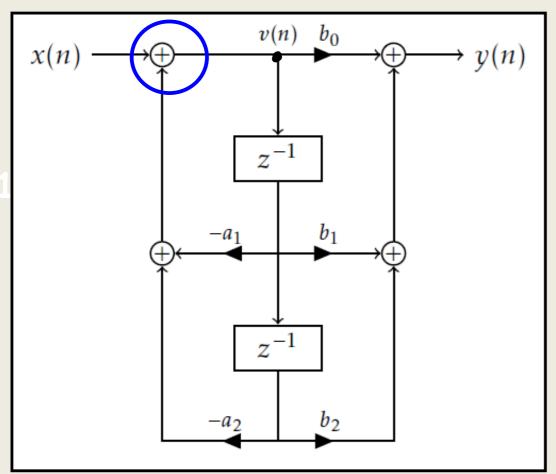

Assume processor with clock frequency 1 MHz

At what rate do we output y(n)?

### Some implementation aspects

#### **IIR** filters

Second order filter

Assume processor with clock frequency 1 MHz

At what rate do we output y(n)?

First we need to do parallell multiplications

#### Some implementation aspects

#### **IIR** filters

Second order filter

Assume processor with clock frequency 1 MHz

At what rate do we output y(n)?

First we need to do parallell multiplications

Clock cycles between updating memory elements:

1 + ...

#### Some implementation aspects

#### **IIR** filters

Second order filter

Assume processor with clock frequency 1 MHz

At what rate do we output y(n)?

First we need to do parallell multiplications

Then, can perform parallell additions

Clock cycles between updating memory elements:

1 + 1 + ...

#### Some implementation aspects

#### **IIR** filters

Second order filter

Assume processor with clock frequency 1 MHz At what rate do we output y(n) ? First we need to do parallell multiplications Then, can perform parallell additions Then, another addition

Clock cycles between updating memory elements:

1 + 1 + 1 + ...

#### Some implementation aspects

#### **IIR** filters

Second order filter

Assume processor with clock frequency 1 MHz At what rate do we output y(n) ? First we need to do parallell multiplications Then, can perform parallell additions Then, another addition Then one more

Clock cycles between updating memory elements:

1 + 1 + 1 + 1 = 4

#### Some implementation aspects

#### **IIR** filters

Second order filter

Assume processor with clock frequency 1 MHz

At what rate do we output y(n)? 250kHz

Assuming 1 cycle per operation (In reality, multiplications are more time consuming than additions.)

Clock cycles between updating memory elements:

1 + 1 + 1 + 1 = 4

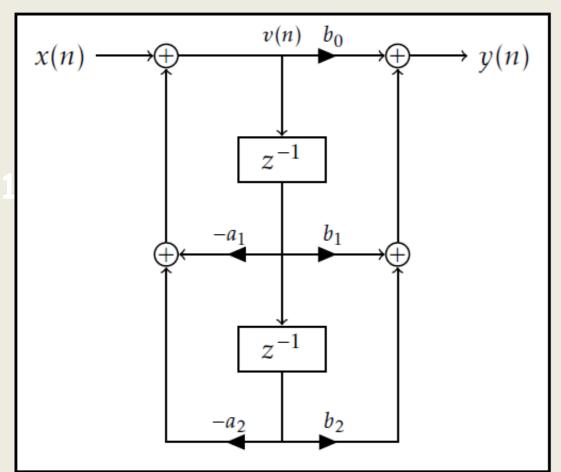

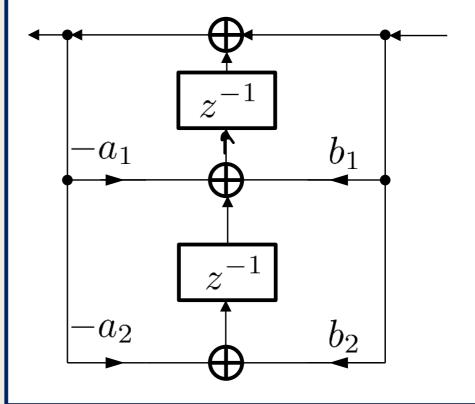

#### Some implementation aspects

#### **IIR** filters

Second order filter

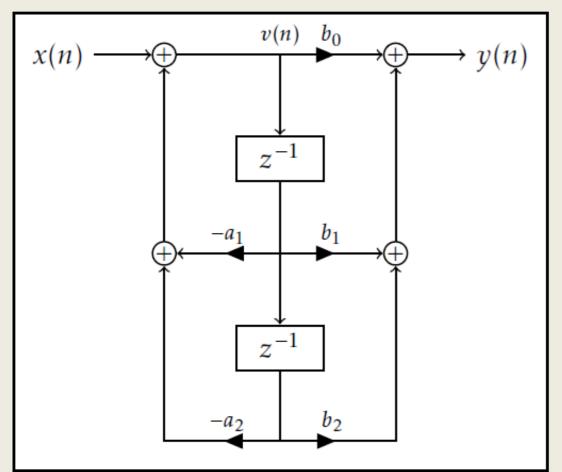

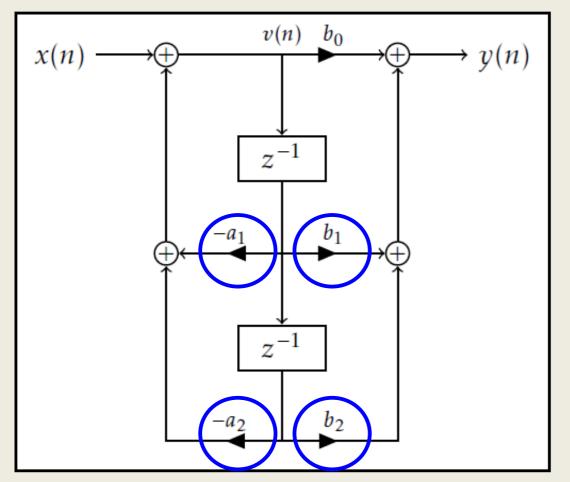

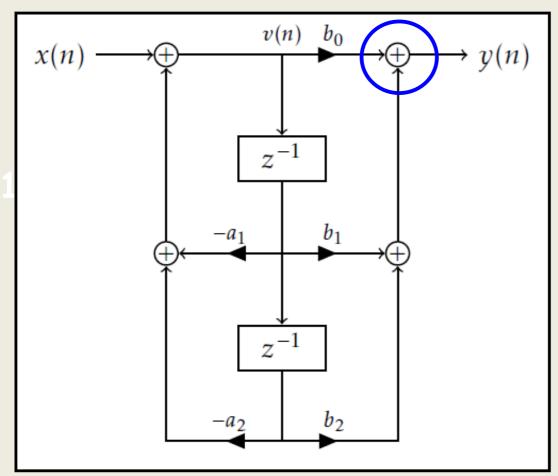

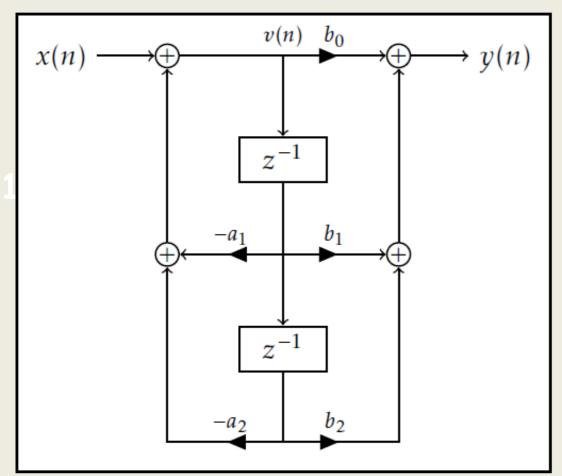

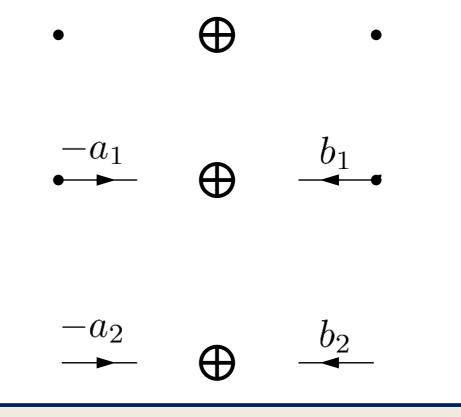

Transposition of systems:

- Reverse direction of each interconnection

- Reverse direction of each multiplier

- Change junctions to adders and vice-versa

- Interchange input and output

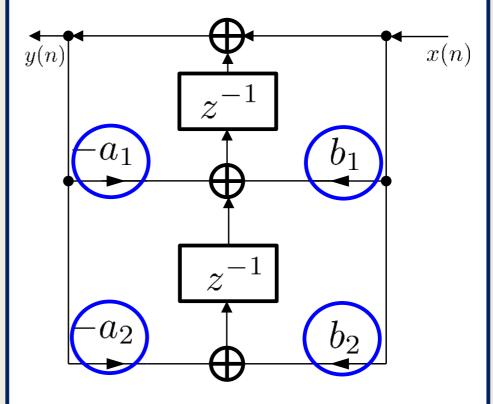

#### Some implementation aspects

#### **IIR** filters

Second order filter

Transposition of systems:

For any block diagram, we obtain an equivalent if we,

- Reverse direction of each interconnection

- Reverse direction of each multiplier

- Change junctions to adders and vice-versa

$b_1$

bs

• Interchange input and output

$-a_1$

$-a_2$

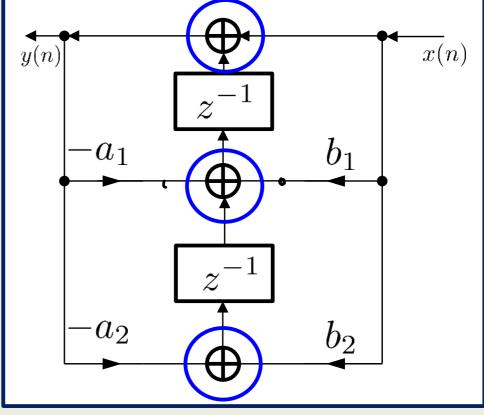

#### Some implementation aspects

#### **IIR** filters

Second order filter

Transposition of systems:

- Reverse direction of each interconnection

- Reverse direction of each multiplier

- Change junctions to adders and vice-versa

- Interchange input and output

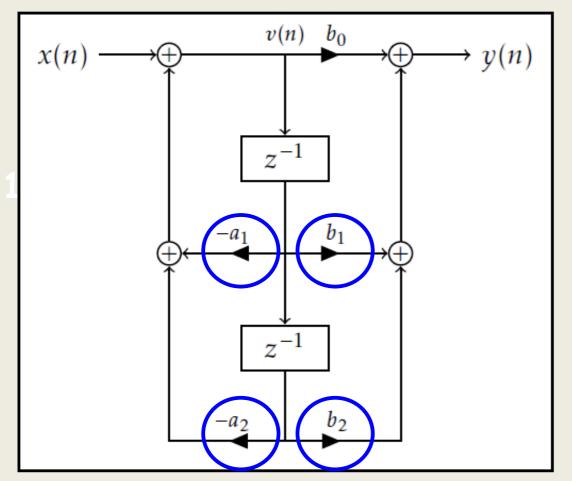

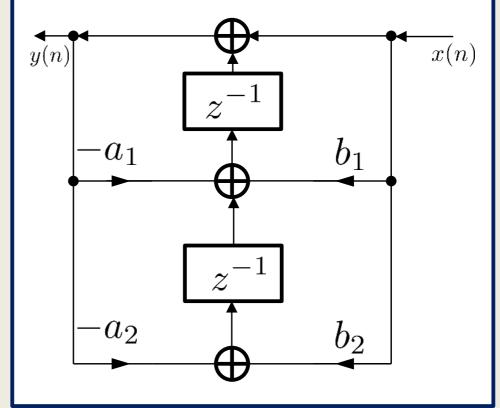

#### Some implementation aspects

#### **IIR** filters

Second order filter

Transposition of systems:

- Reverse direction of each interconnection

- Reverse direction of each multiplier

- Change junctions to adders and vice-versa

- Interchange input and output

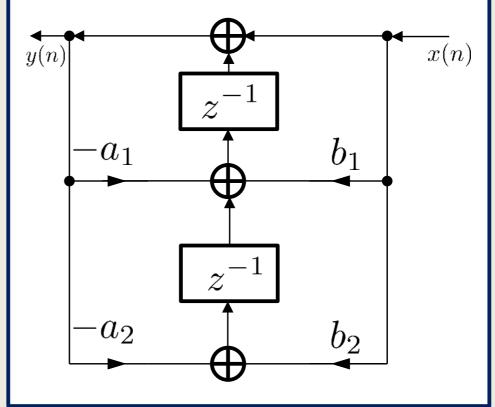

#### Some implementation aspects

#### **IIR** filters

Second order filter

Transposition of systems:

- Reverse direction of each interconnection

- Reverse direction of each multiplier

- Change junctions to adders and vice-versa

- Interchange input and output

#### Some implementation aspects

#### **IIR** filters

#### Second order filter

Assume processor with clock frequency 1 MHz

At what rate do we output y(n)?

Transposition of systems:

- Reverse direction of each interconnection

- Reverse direction of each multiplier

- Change junctions to adders and vice-versa

- Interchange input and output

#### Some implementation aspects

#### **IIR** filters

#### Second order filter

Assume processor with clock frequency 1 MHz

At what rate do we output y(n)?

First parallell multiplications

Clock cycles between updating memory elements:

1 + ...

Transposition of systems:

- Reverse direction of each interconnection

- Reverse direction of each multiplier

- Change junctions to adders and vice-versa

- Interchange input and output

#### Some implementation aspects

#### **IIR** filters

#### Second order filter

Assume processor with clock frequency 1 MHz

At what rate do we output y(n)?

First parallell multiplications

Then parallell additions

Clock cycles between updating memory elements:

1 + 1 + ...

Transposition of systems:

- Reverse direction of each interconnection

- Reverse direction of each multiplier

- Change junctions to adders and vice-versa

- Interchange input and output

#### Some implementation aspects

#### **IIR** filters

#### Second order filter

Assume processor with clock frequency 1 MHz

At what rate do we output y(n)? 500kHz

First parallell multiplications

Then parallell additions

Then done!

Clock cycles between updating memory elements:

1 + 1 = 2

Transposition of systems:

- Reverse direction of each interconnection

- Reverse direction of each multiplier

- Change junctions to adders and vice-versa

- Interchange input and output

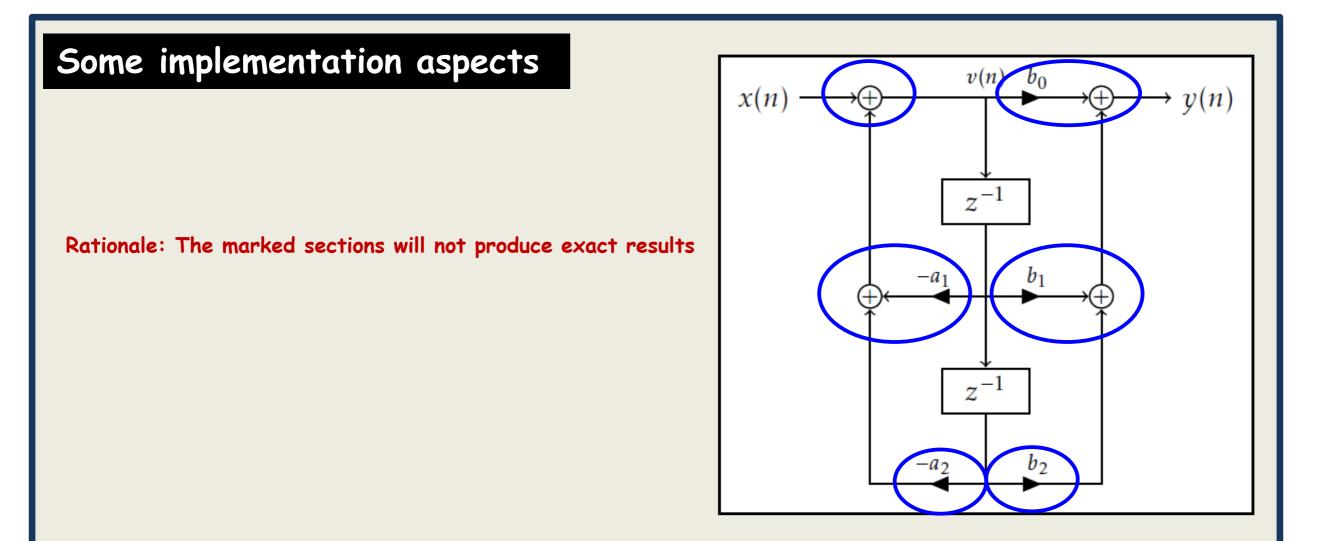

#### Some implementation aspects

#### Numerical precision issues

**Coefficient precision:** Coefficients are stored with finite precision. So implementation is not exact

Arithmetic precision: Done with finite precision, So not exact.

Typical model: Represent these effects as noise

#### Some implementation aspects

#### Numerical precision issues

**Coefficient precision:** Coefficients are stored with finite precision. So implementation is not exact

Arithmetic precision: Done with finite precision, So not exact.

Typical model: Represent these effects as noise

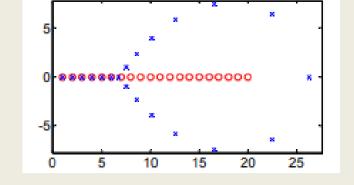

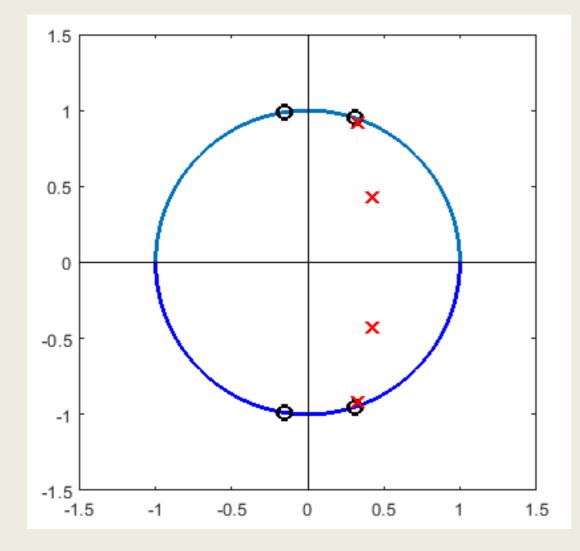

Example: Wilkinson's polynomial

$$f(x) = \prod_{n=1}^{20} (x - n) = x^{20} - 210x^{19} + 20615x^{18} - \dots$$

Zeros: on real axis, well separated

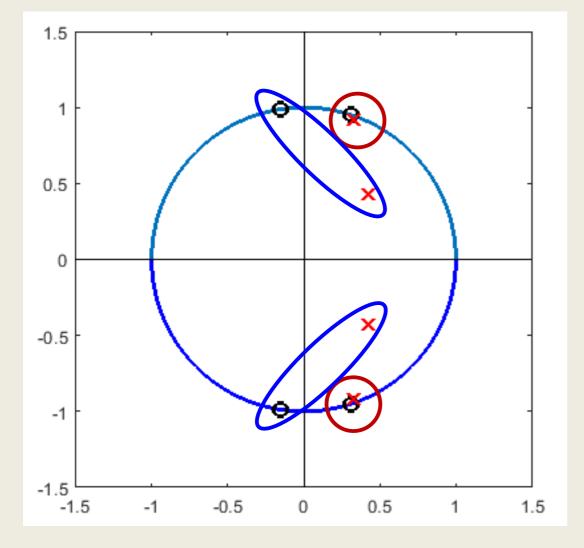

Red: zeros of exact Wilkinson Blue: zeros of imprecise Wilkinson

Assume imprecision: coefficient of  $x^{19}$  is 210.00021 (1.000001 times the real one)

"Speaking for myself I regard it as the most traumatic experience in my career as a numerical analyst", James Wilkinson 1984

#### Some implementation aspects

#### Numerical precision issues

Consider a desired transfer function

$$H(z) = \frac{(z-z_1)(z-z_2)(z-z_3)\cdots(z-z_M)}{(z-p_1)(z-p_2)(z-p_3)\cdots(z-p_M)}$$

General rule: Not wise to implement this as a one-stage filter, i.e., using direct form II (or its transposed version)

Better solution. Typical case: each filter is second order ("biquad"). M' = M/2

$$\xrightarrow{x(n)} H_1(z) \longrightarrow H_2(z) \longrightarrow H_3(z) \longrightarrow \dots \longrightarrow H_{M'}(z) \xrightarrow{y(n)}$$

Two questions:

- 1. Which poles to pair with which zeros?

- 2. In which order should the filters appear ?

#### Some implementation aspects

#### Numerical precision issues

Consider a desired transfer function

$$H(z) = \frac{(z-z_1)(z-z_2)(z-z_3)\cdots(z-z_M)}{(z-p_1)(z-p_2)(z-p_3)\cdots(z-p_M)}$$

General rule: Not wise to implement this as a one-stage filter, i.e., using direct form II (or its transposed version)

Better solution. Typical case: each filter is second order ("biquad"). M' = M/2

$$\xrightarrow{x(n)} H_1(z) \longrightarrow H_2(z) \longrightarrow H_3(z) \longrightarrow \dots \longrightarrow H_{M'}(z) \xrightarrow{y(n)}$$

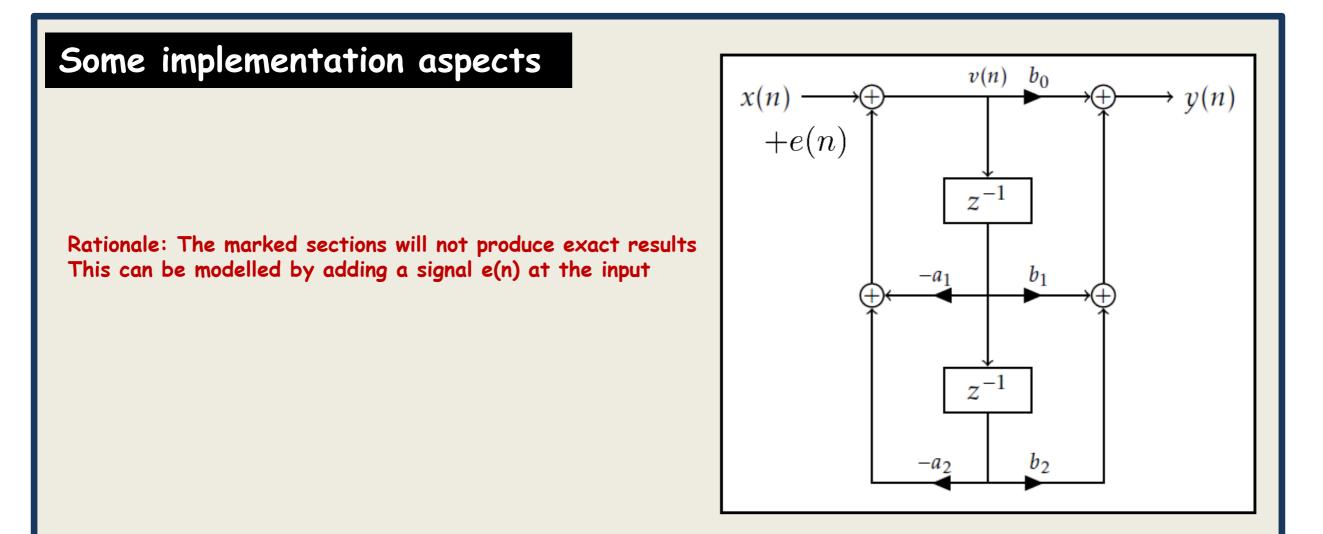

Model: Each filter produces noise that is being added to the input of itself

Model: Each filter produces noise that is being added to the input of itself

Model: Each filter produces noise that is being added to the input of itself

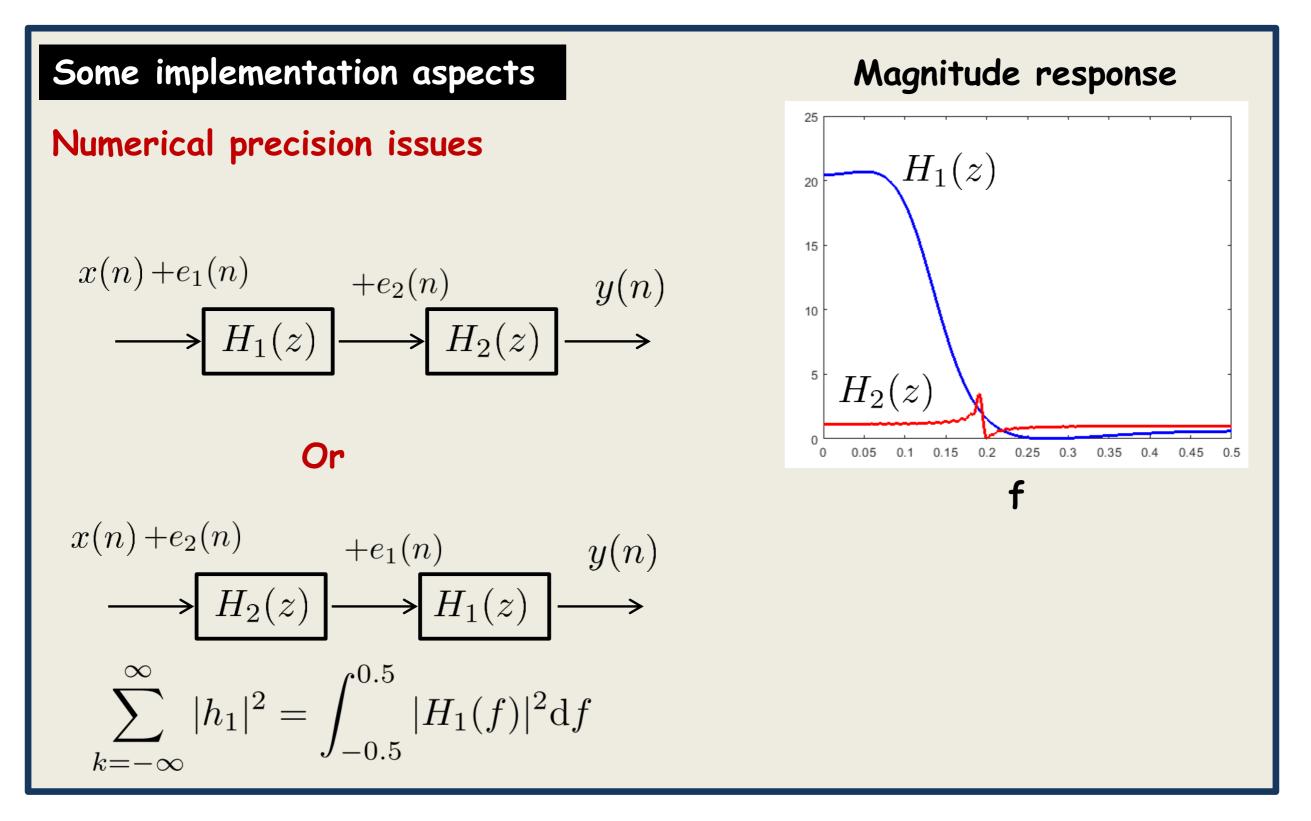

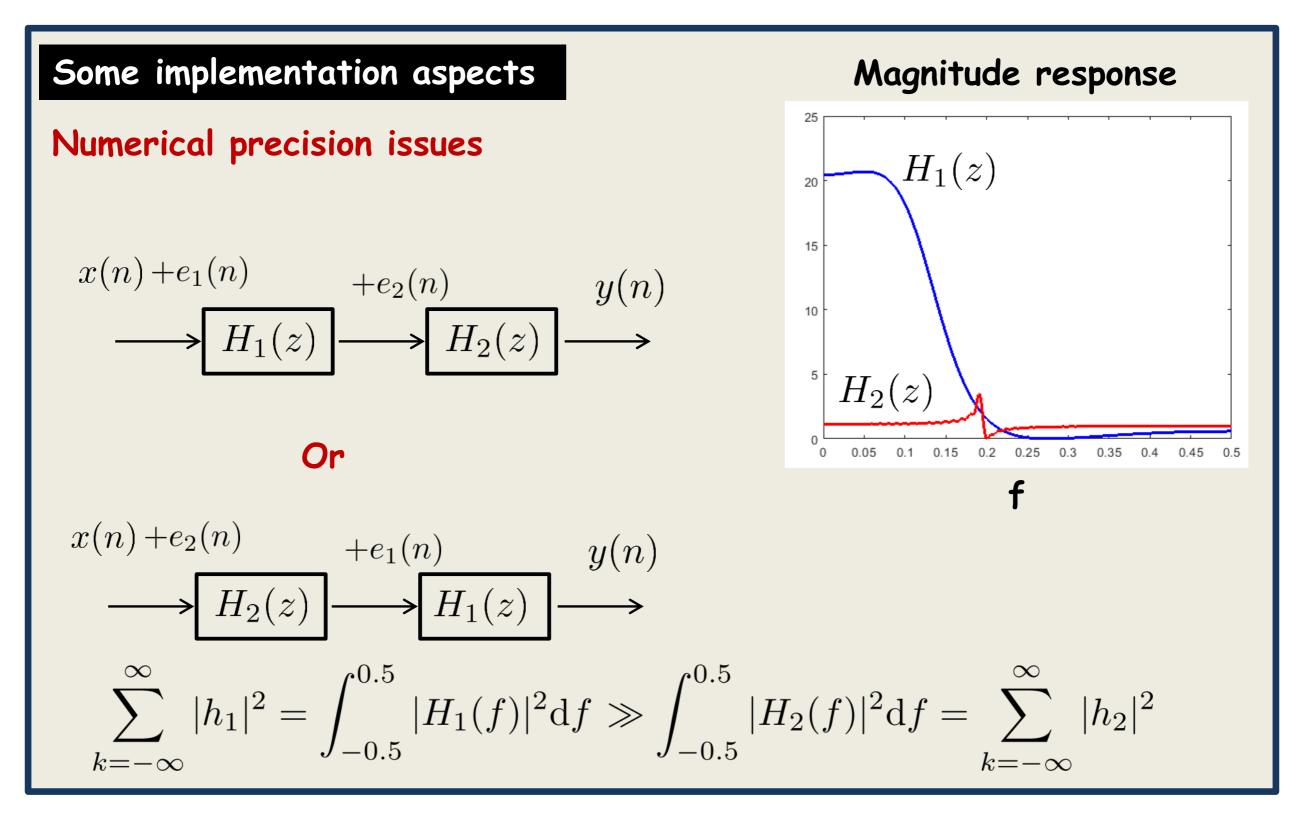

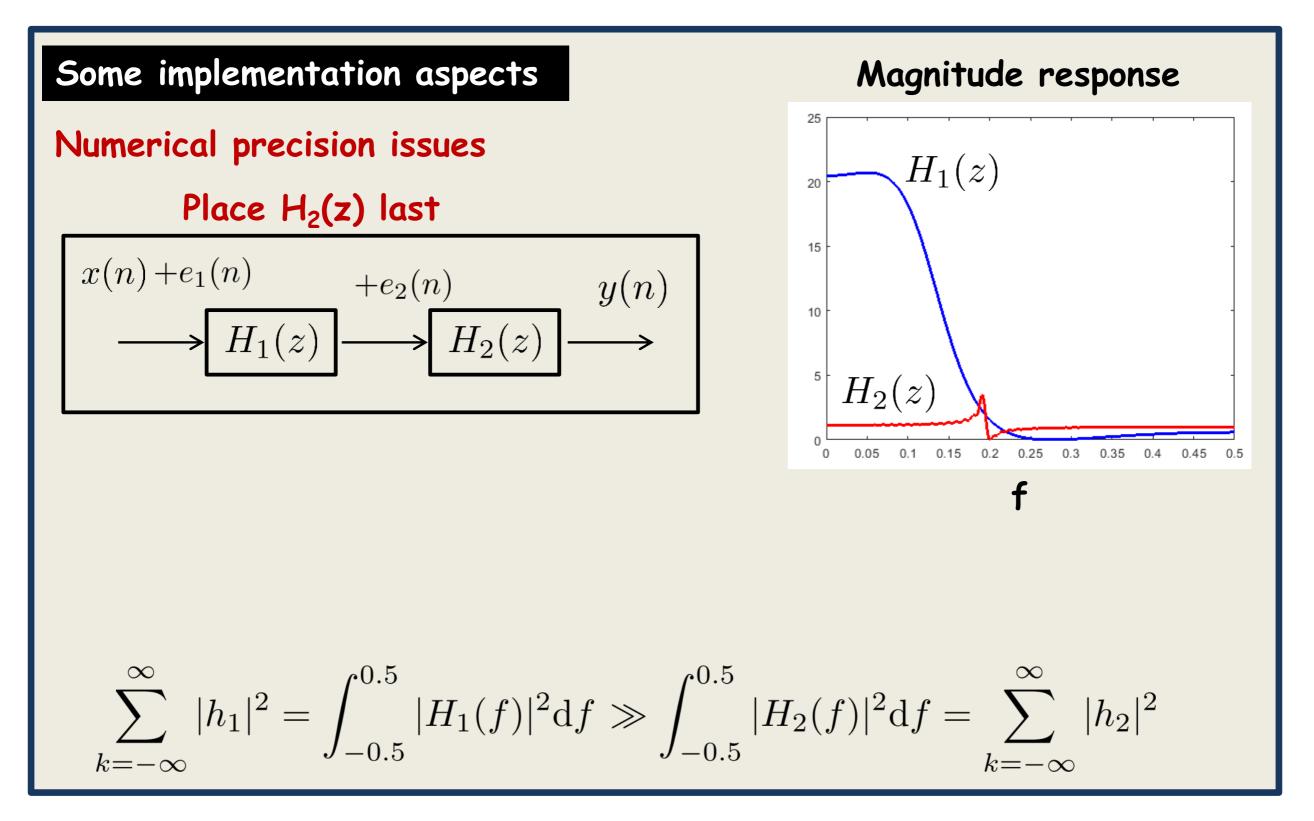

### Some implementation aspects

#### Numerical precision issues

Consider a desired transfer function

$$H(z) = \frac{(z-z_1)(z-z_2)(z-z_3)\cdots(z-z_M)}{(z-p_1)(z-p_2)(z-p_3)\cdots(z-p_M)}$$

General rule: Not wise to implement this as a one-stage filter, i.e., using direct form II (or its transposed version)

Better solution. Typical case: each filter is second order ("biquad"). M' = M/2

$$x(n) + \underbrace{e(n)}_{H_1(z)} \xrightarrow{e_v(n)}_{H_2(z)} \underbrace{e_3(n)}_{H_3(z)} \xrightarrow{e_3(n)}_{H_3(z)} \xrightarrow{u_1(n)}_{H_{M'}(z)} \underbrace{y(n)}_{H_{M'}(z)} \xrightarrow{y(n)}_{H_{M'}(z)}$$

Model: Each filter produces noise that is being added to the input of itself

This noise will get amplified by later stages

$$H(2) = \frac{(Z - 2i)(Z - 2i)}{(Z - P_{1})(Z - P_{2})} \cdot \frac{(Z - 2i)(Z - 2i)}{(Z - P_{1})(Z - P_{2})} \cdot \frac{(Z - 2i)(Z - 2i)}{(Z - P_{1})(Z - P_{2})}$$

$$= H_{1}(1+) \cdot H_{2}(2) \cdot \cdots$$

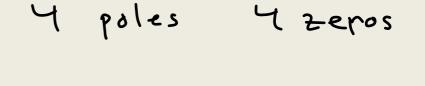

### Some implementation aspects

#### Numerical precision issues

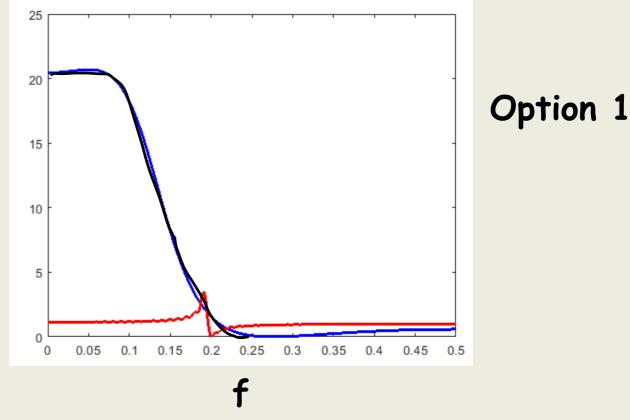

Consider the following filter

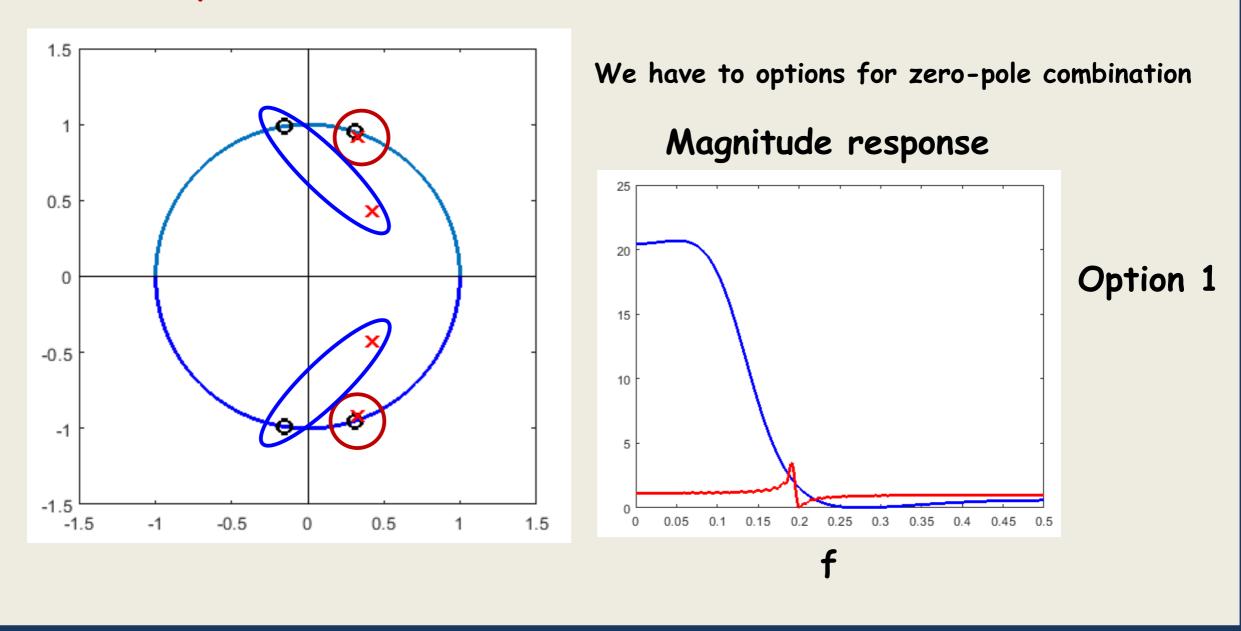

Hwo We have to options for zero-pole combination

### Some implementation aspects

### Numerical precision issues

We have to options for zero-pole combination

**Option 1**

Consider the following filter

### Some implementation aspects

### Numerical precision issues

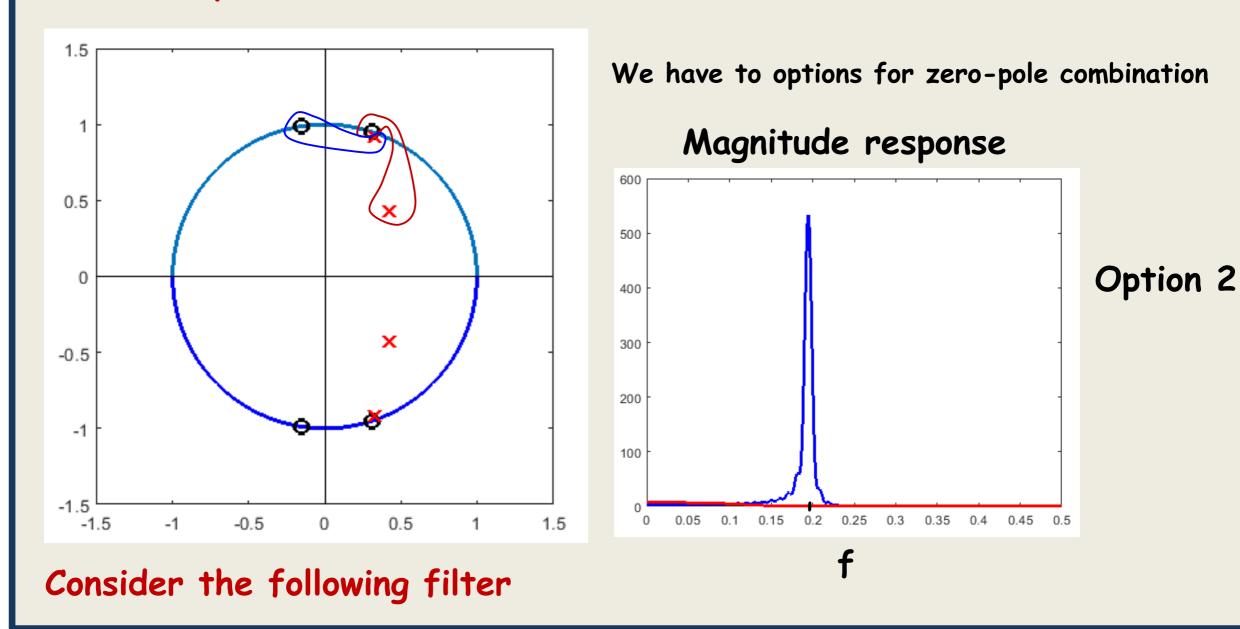

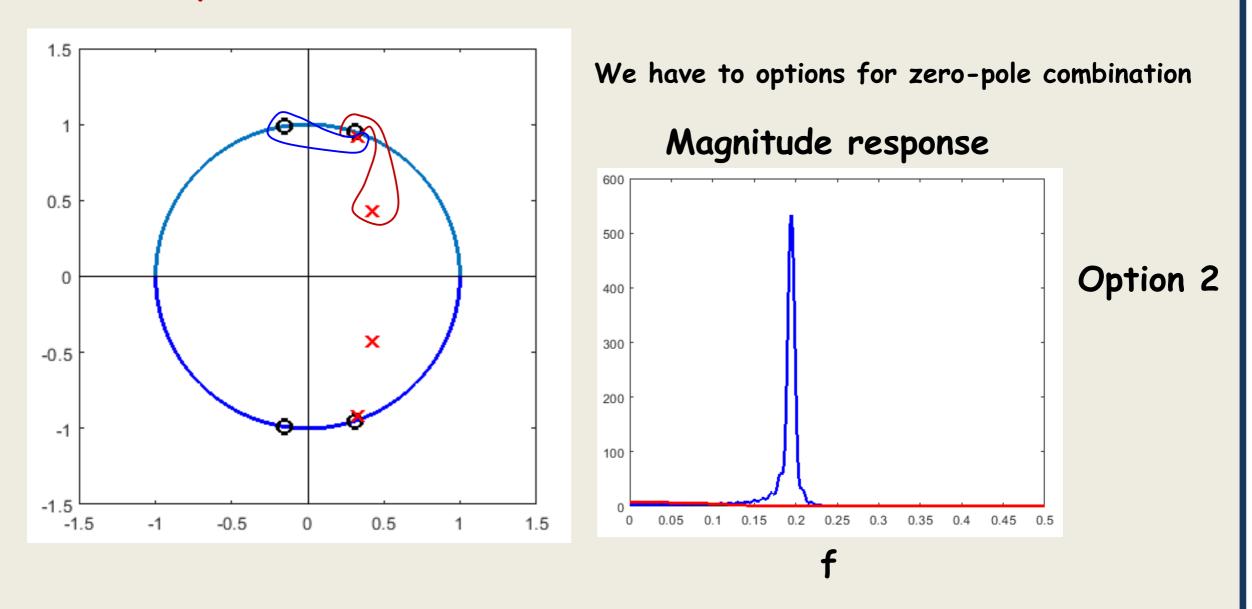

We have to options for zero-pole combination

**Option 2**

Consider the following filter

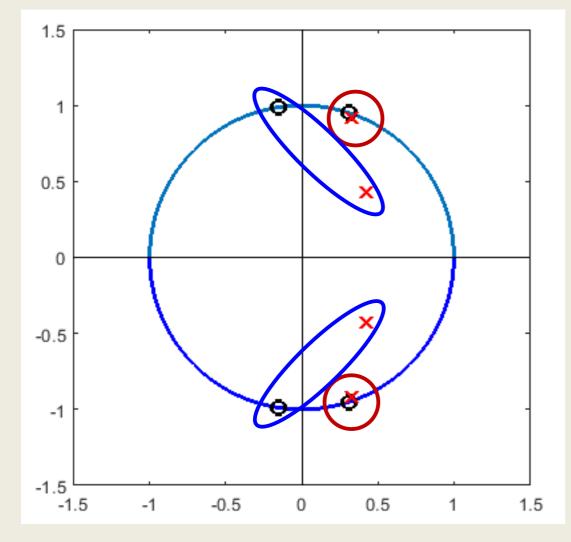

### Some implementation aspects

#### Numerical precision issues

Consider the following filter

We have to options for zero-pole combination

#### Magnitude response

### Some implementation aspects

#### Numerical precision issues

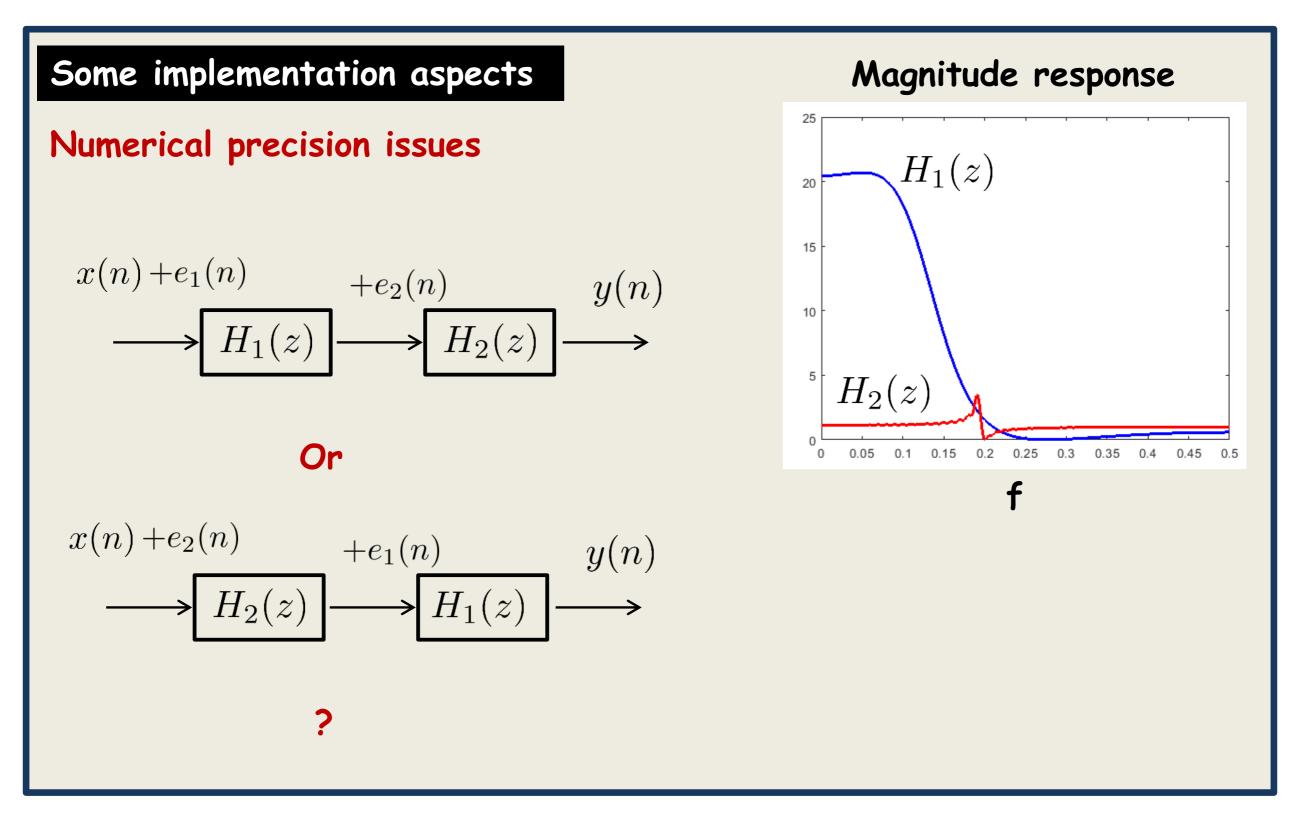

#### Some implementation aspects

#### Numerical precision issues

This option would greatly amplify any source of noise we have. Not suitable.

### Some implementation aspects

#### Numerical precision issues

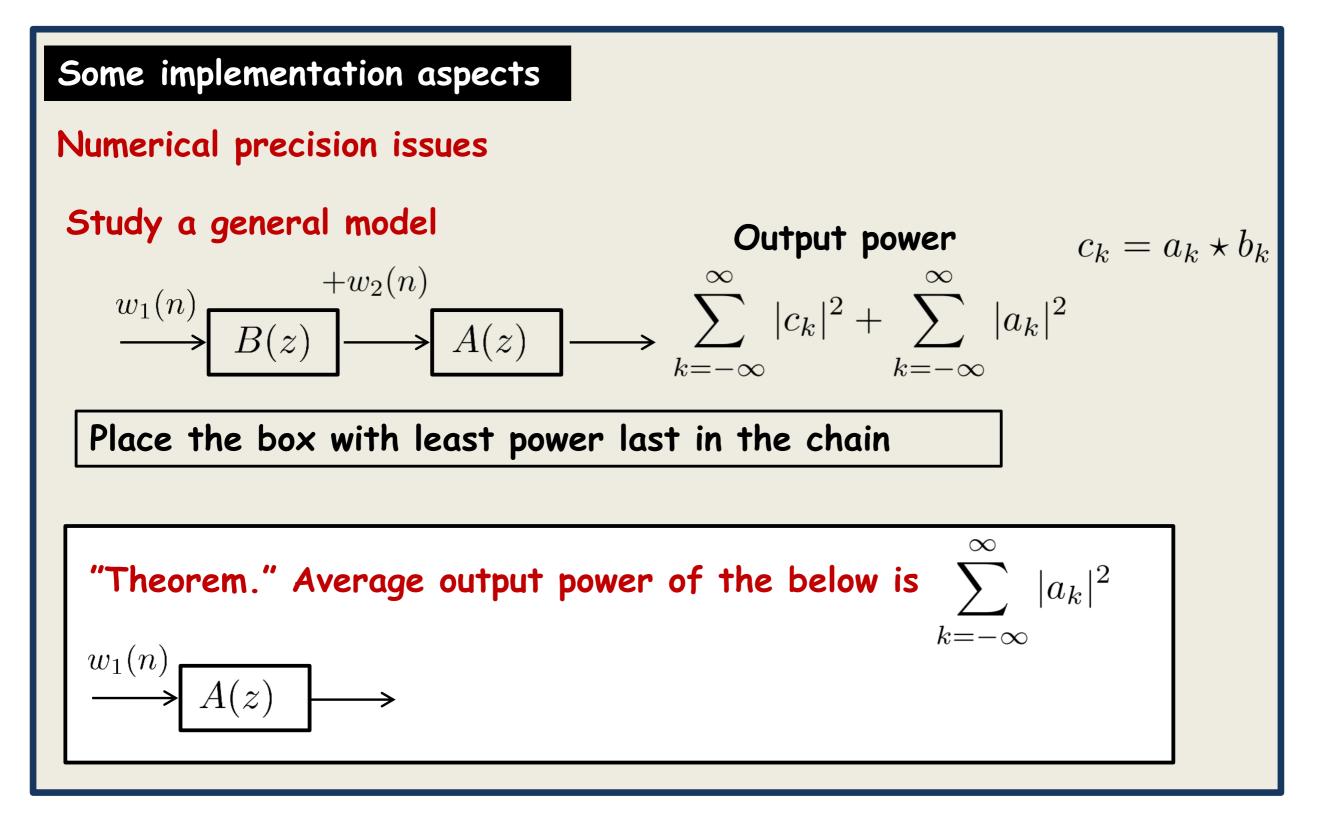

We choose option 1. Remains to discuss their order.

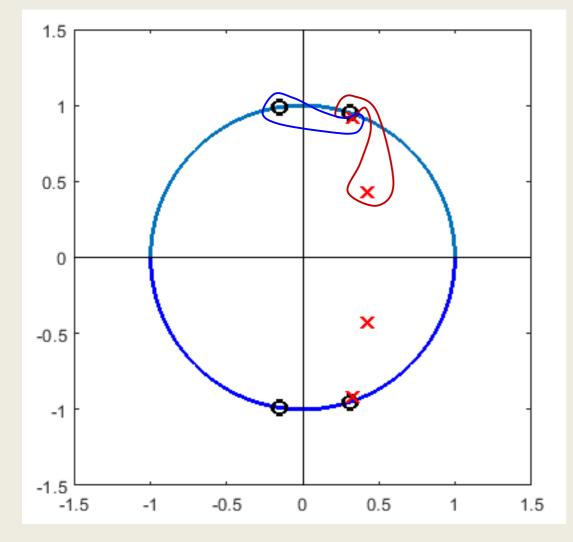

Some implementation aspects

Numerical precision issues

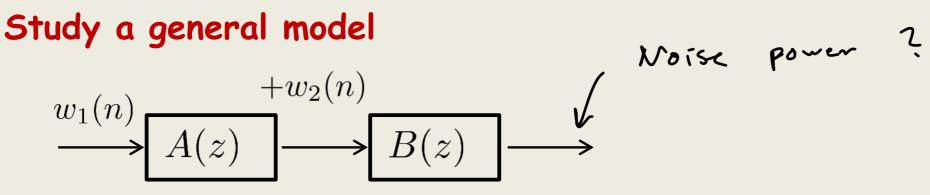

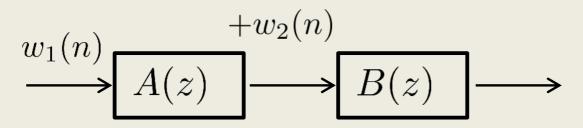

Compute the average output power if the noise sources are unit power random signals

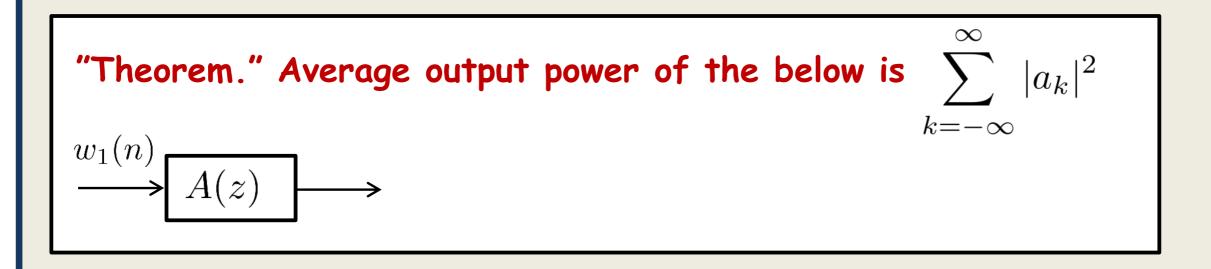

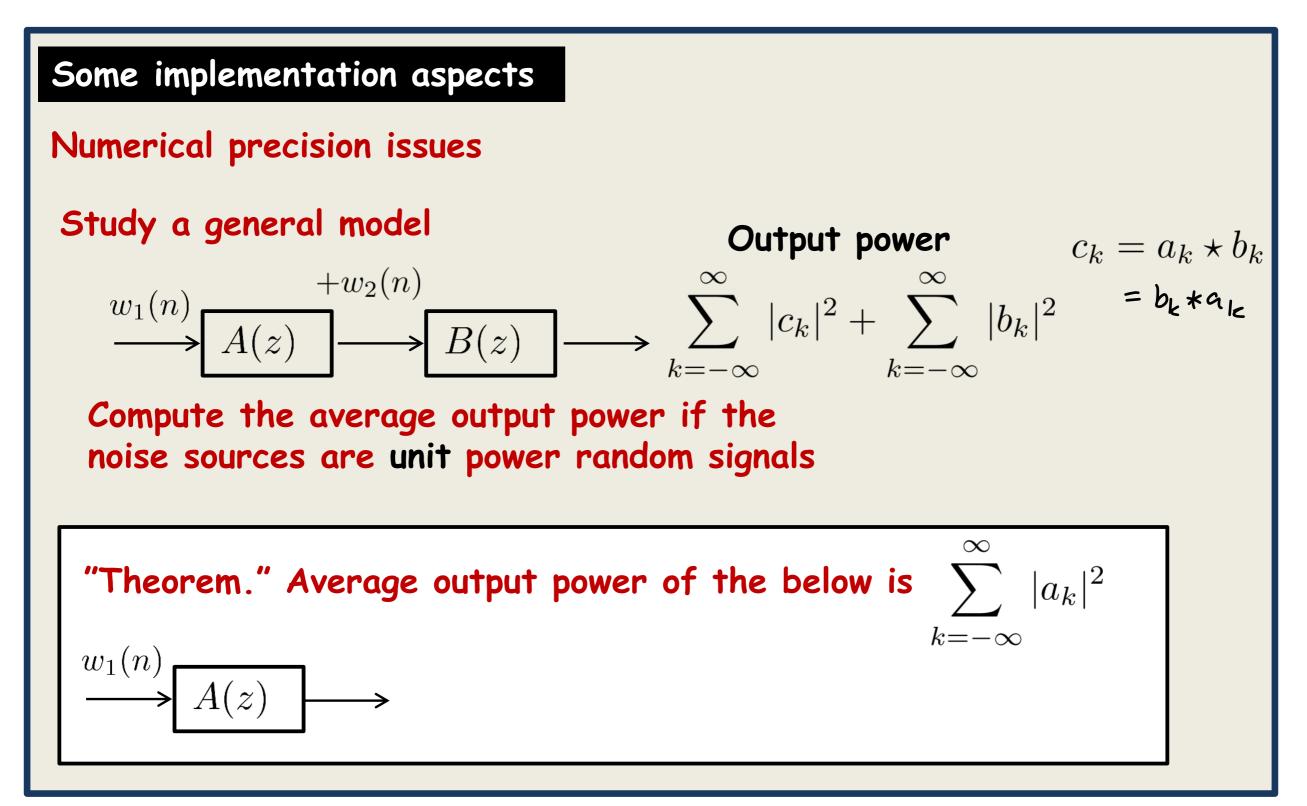

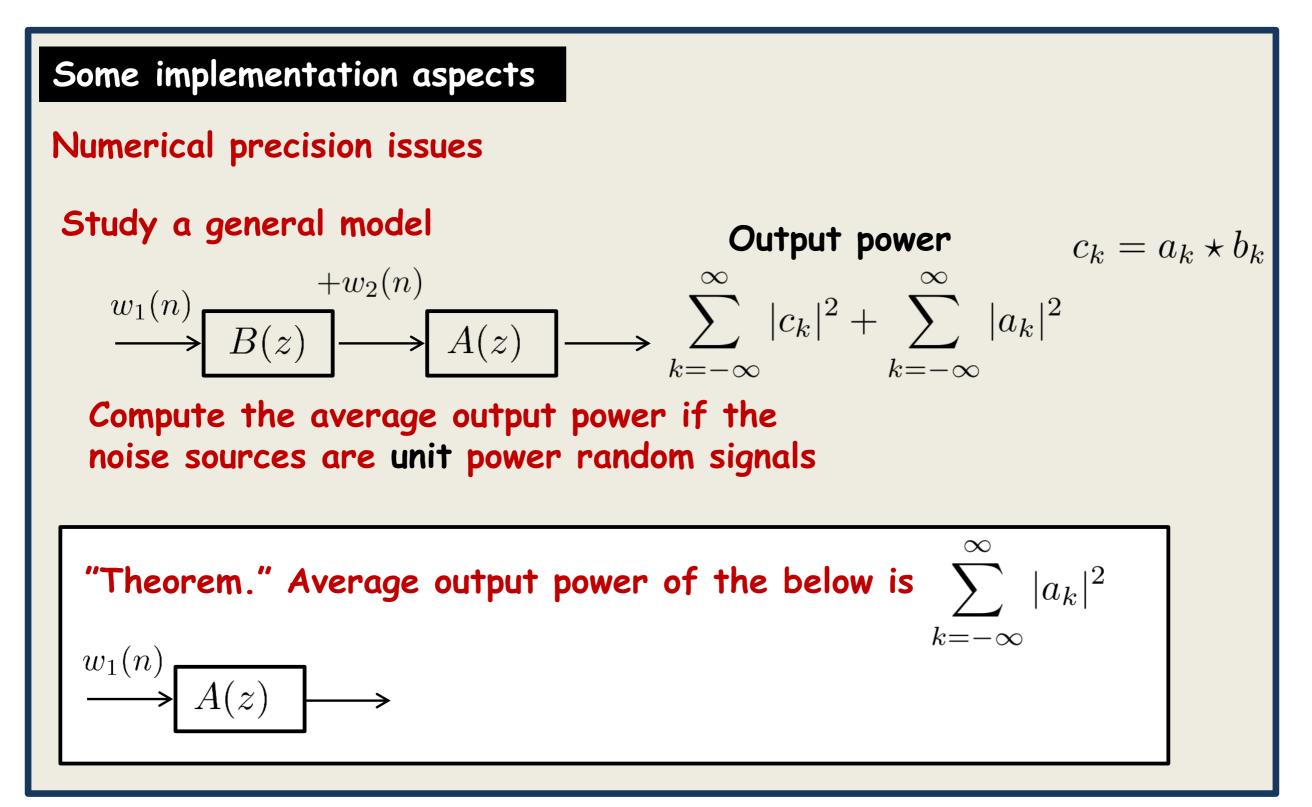

- Numerical precision issues

- Study a general model

Compute the average output power if the noise sources are unit power random signals