# Digitalteknik EITF65

Lecture 11: Asynchronous Sequential Circuits

August 27, 2020

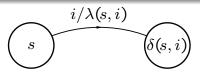

## Mealy

### Definition

A Mealy graph is defined by the five-tuple  $\mathcal{M}=\{\mathcal{I},\mathcal{S},\mathcal{Z},\delta,\lambda\}$  where

•  $\delta$  is the state transition function,

$$\delta: \mathcal{S} \times \mathcal{I} \to \mathcal{S}$$

•  $\lambda$  is the output function,

$$\lambda: \mathcal{S} \times \mathcal{I} \to \mathcal{Z}$$

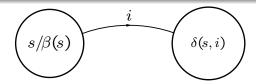

### Moore

### Definition (6.6)

A Moore graph is defined by the five-tuple  $\mathcal{M}=\{\mathcal{I},\mathcal{S},\mathcal{Z},\delta,\beta\}$  where

•  $\delta$  is the state transition function,

$$\delta: \mathcal{S} \times \mathcal{I} \to \mathcal{S}$$

•  $\beta$  is the output function,

$$\beta: \mathcal{S} \to \mathcal{Z}$$

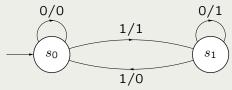

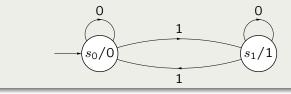

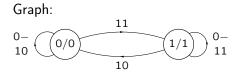

## Parity check

### Example 6.7

The (even/odd) parity check graph can be written as a

Mealy graph:

► Moore graph:

## Conversion

#### $\mathsf{Mealy} \to \mathsf{Moore}$

All Mealy graphs can be rewritten as Moore graphs if we allow that

- the output is delayed one step.

- we might need more states.

#### Conversion:

- Split the states such that all entering edges into a state have the same output.

- Move the output into the state pointed out by the edge (next state).

## Conversion

### $\mathsf{Moore} \to \mathsf{Mealy}$

All Moore graphs can be rewritten as Mealy graphs if we allow that the output is affected directly (asynchronously) by the input. Conversion:

- Move the output to the entering edges.

- Use the RF-algorithm.

# Asynchronous sequential circuits

Martin Hell, Digitalteknik L11:7, Ch 6.3, 6.4

## Asynchronously realizable

### Definition (6.7)

A state s is stable for the input i if

$$\delta(s,i)=s$$

i.e., if *i* gives an edge back to *s*.

If there is a path for input *i* from state  $s_0$  to the stable state *s* then *s* is a successor state of  $s_0$  for input *i*.

### Definition (6.8)

A graph is asynchronously realizable if all states have successor states for all inputs.

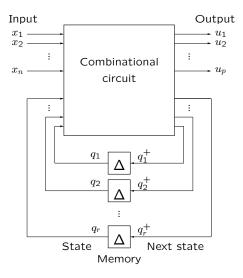

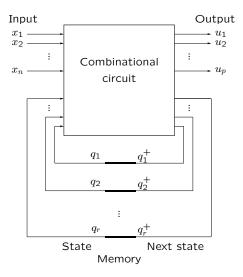

## Sequential circuit (canonical form)

#### Definition

In a race free state assignment only one state variable changes when a state changes.

It is always possible to rewrite an asynchronously realizable graph such that it can be encoded race free. One way is to think of the states as corners in an (n-dimensional) cube. The allowed transitions are the edges of the cube.

Due to different delays in the components, there might appear transients in the output. This is called hazard.

To avoid hazard the realization must be hazard free. That is, *all* prime implicants must be in the function. An asynchronous sequential circuit is not clock controlled, and the states are updated continuously. That gives an event controlled circuit.

Therefore, we need that

- the graph is asynchronously realizable.

- the state assignment is race free.

- the functions are hazard free.

## Sequential circuit (canonical form)

### Latch

#### Example 6.13

A latch is a simple memory element. Use the signal  $\phi$  to control the output such that

$$z = \begin{cases} x, & \text{if } \phi = 1 \\ x_0, & \text{if } \phi = 0 \end{cases}$$

where  $x_0$  is the input the latest occasion  $\phi = 1$ .

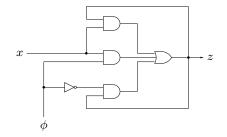

## Latch (realisation)

Functions:

$$q^{+} = q\phi' \lor qx \lor \phi x$$

$$z = q$$

Karnaugh map:

Realisation:

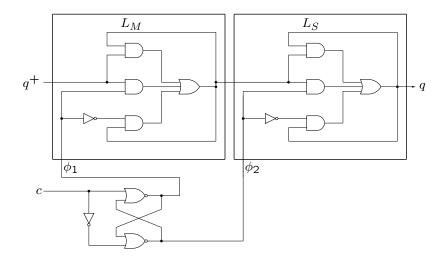

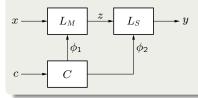

### D-element

### Example 6.14

To avoid direct connection between the input and the output we cascade two latches.

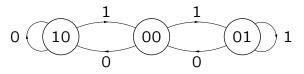

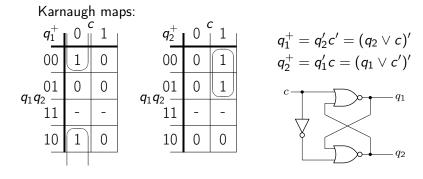

The control circuit C:

$$(\phi_1,\phi_2)=egin{cases} (0,1), & c=1\ (1,0), & c=0 \end{cases}$$

At the transition  $(\phi_1, \phi_2) = (0, 0)$ .

Moore graph for the *C* circuit:

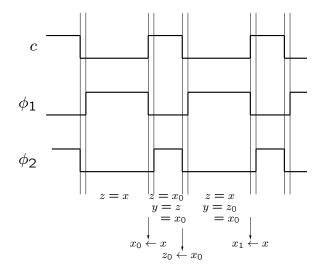

## *D*-element (time schedule)

Time schedule for c,  $\phi_1$ , and  $\phi_2$ :

# *D*-element (circuit)