#### Introduction to Structured VLSI Design Lab1 – State Machine Modeling

MOHAMMAD ATTARI SEPTEMBER 4, 2019

# Learning Outcomes

- VHDL modelling for synthesis

- Registers (state)

- Combinational logic

- Latches

- State machines

- Mealy

- Moore

- Testbench

- Xilinx Vivado

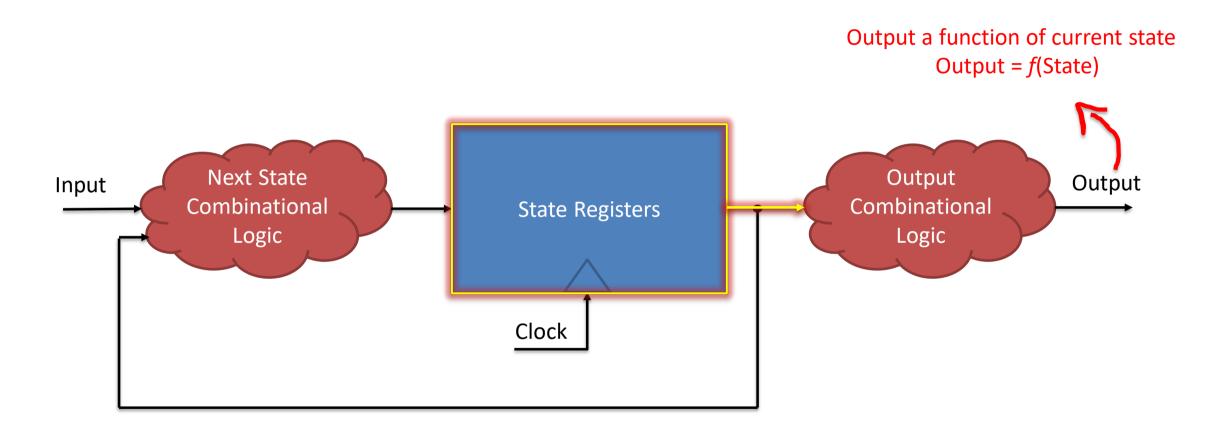

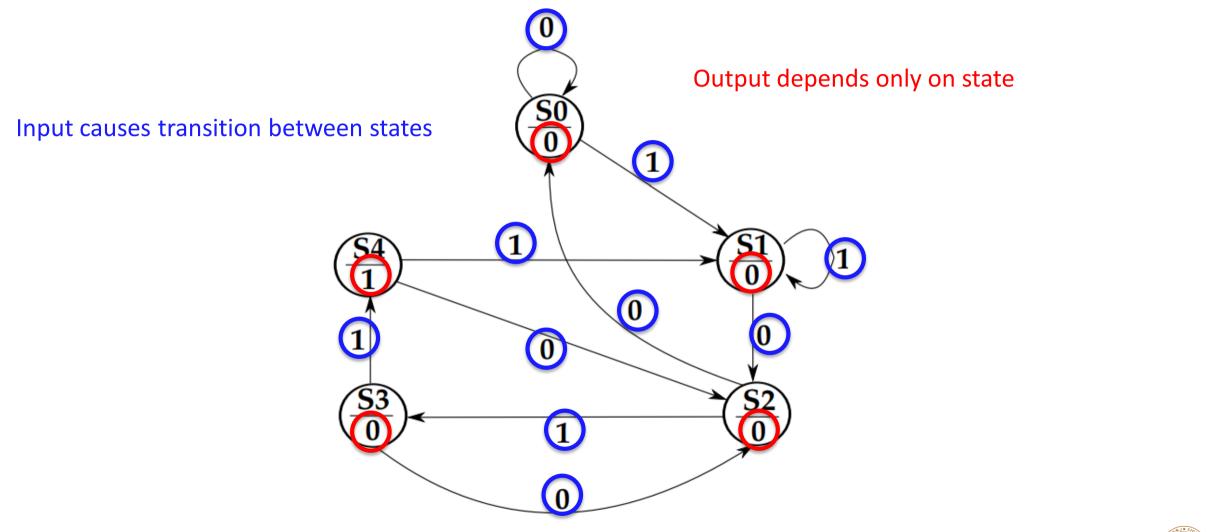

#### Moore Machine

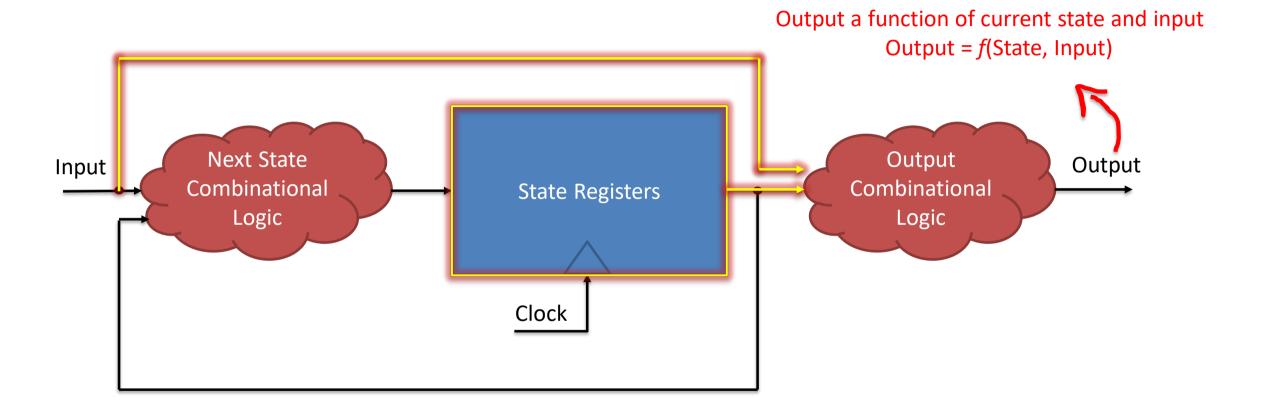

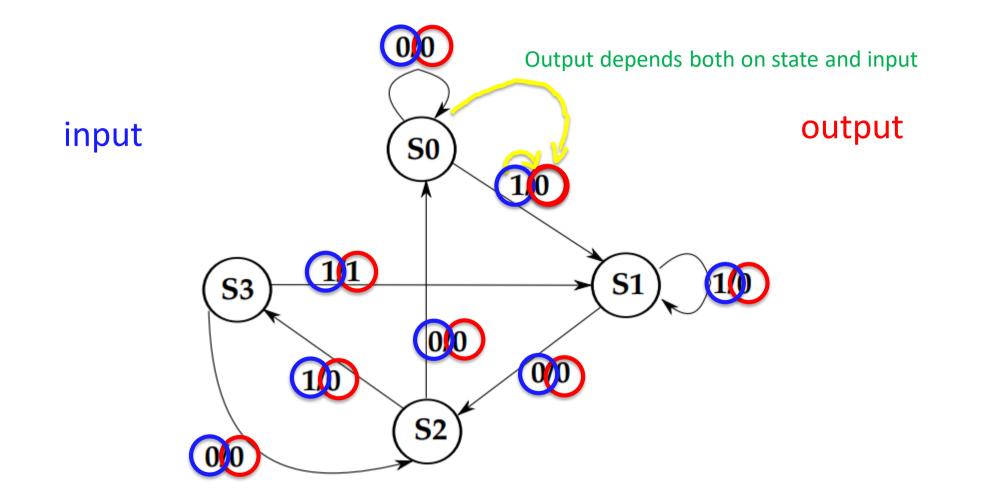

## Mealy Machine

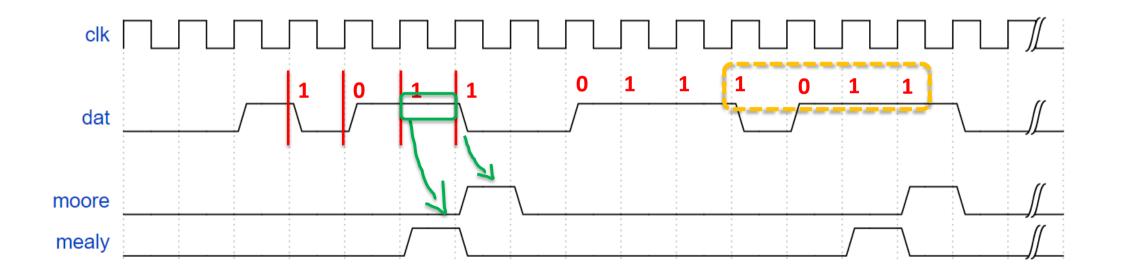

# Moore vs. Mealy

- Mealy

- Fewer states

- React faster

- Moore

- Safer

- Synchronous

## Sequence Detector

• Detect the sequence **1011**

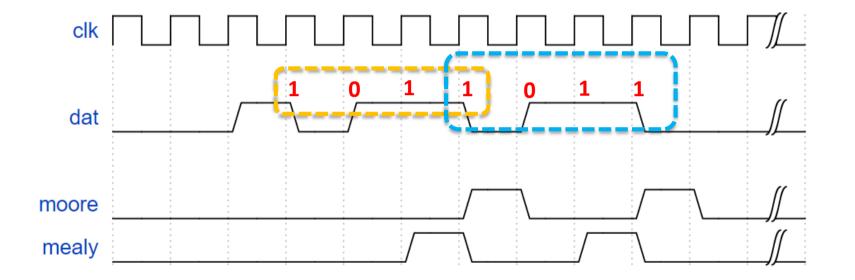

# Sequence in Sequence

## Mealy State Machine

#### Moore State Machine

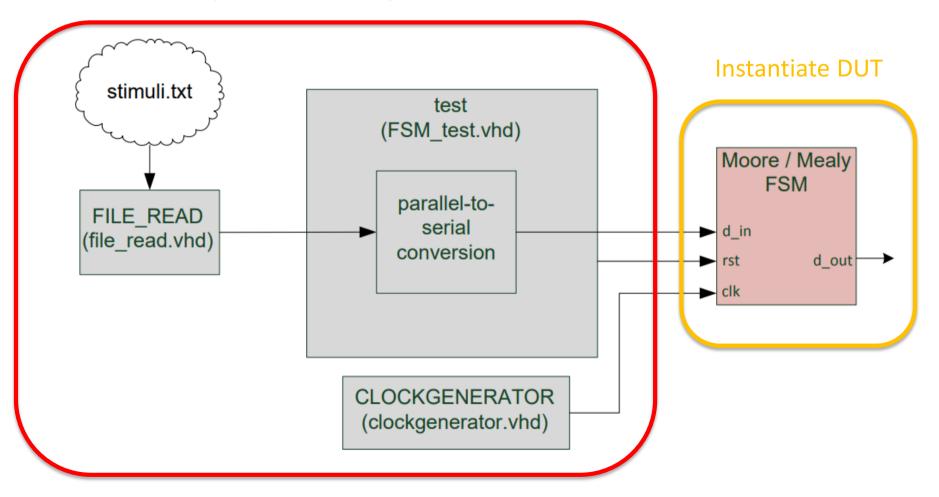

## Testbench

#### All provided as templates

# Vivado Design Suite

| À vlsi_lab1 - [D:/Work_Space/Vivado/vlsi_lab |                                                                                                                                       |                             | Quist Lange |                       |               |                                   |                                         |                                             |          |        |           |              |            |          |          |           |           |          |                       | ×    |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------------|-----------------------|---------------|-----------------------------------|-----------------------------------------|---------------------------------------------|----------|--------|-----------|--------------|------------|----------|----------|-----------|-----------|----------|-----------------------|------|

|                                              | Synthesis Complet                                                                                                                     |                             |             |                       |               |                                   |                                         |                                             |          |        |           |              |            |          |          |           |           |          |                       |      |

|                                              |                                                                                                                                       |                             |             | ✓ ±                   | II C          |                                   |                                         |                                             |          |        |           |              |            |          |          |           |           | -        |                       | ~    |

| Flow Navigator 😤 🗘 ? 🔔                       | SIMULATION - Behavioral Sim                                                                                                           | ulation - Functional - sim_ | 1 - test    |                       |               |                                   |                                         |                                             |          |        |           |              |            |          |          |           |           |          | ?                     | • ×  |

| ✓ PROJECT MANAGER                            | Scope × Sources                                                                                                                       | _                           | O C Ob      | jects                 | ? _ 0 6       | < detector.vhd × F                | SM_test.vhd × Untitled 7*               | ×                                           |          |        |           |              |            |          |          |           |           |          | ? 🗆                   | Ci i |

| Settings                                     | Q                                                                                                                                     |                             | • Q         |                       |               |                                   |                                         | eleri+Firal                                 | - 1 H I  |        |           |              |            |          |          |           |           |          |                       | ø    |

| Add Sources                                  | Name Design Unit                                                                                                                      | Block Type                  |             | me                    | Value Dat     |                                   | • • • • • • • • • • • • • • • • • • • • |                                             |          |        |           | 152.227400 u | IS I       |          |          |           |           |          |                       | ^    |

| Language Templates                           | test test(behavior)                                                                                                                   |                             |             | las_in                | 0 Log         |                                   | Value                                   | _                                           |          |        |           |              |            |          |          |           |           |          |                       |      |

| ₽ IP Catalog                                 | E sequence_de                                                                                                                         | coder( VHDL En              |             | <mark>la</mark> dk    | 1 Lo <u>c</u> | 16 s_in                           | value                                   | 130 us                                      | 135 us   | 140 us | 145 us 15 | 0 us 155     | us 16      | 60 us 16 | 5 us 11  | 70 us 175 | us 180 us | 185 u    | s 190 us              |      |

|                                              | I FILE_READ(B                                                                                                                         |                             |             | 🕼 rst                 | 1 Log         | 14 dk                             | 1                                       |                                             |          |        |           | _            | _          |          | _        |           | _         |          | _                     |      |

| ✓ IP INTEGRATOR                              | CLOCKGENE                                                                                                                             | RATOR VHDL En               |             | lå d_out1             | 0 Log         | 14 rst                            | 1                                       |                                             |          |        |           |              |            |          |          |           |           |          |                       |      |

| Create Block Design                          |                                                                                                                                       |                             |             | ሬ d_out2<br>ሬ flag    | 0 Log         |                                   | 0                                       |                                             |          |        |           |              |            |          |          |           |           |          |                       |      |

| Open Block Design                            |                                                                                                                                       |                             |             | e nag<br>e count[3:0] | 3 Arra        | le d_out2                         | U                                       |                                             |          |        |           |              |            |          |          |           |           |          |                       |      |

| Generate Block Design                        |                                                                                                                                       |                             |             | Inputbus[11:0]        | 56c Arra      | lø flag                           | 0                                       |                                             | <u> </u> | _      |           |              |            |          |          |           |           |          |                       |      |

| ✓ SIMULATION                                 |                                                                                                                                       |                             | >           | 🕸 inputbus_temp[.     | 5b0 Arra      | > V count[3:0] > V inputbus[11:0] | 5<br>5e5                                | <u>1                                   </u> | 2 1      | 3 1    | 4 7 5     | X 6<br>5e5   | _ <u> </u> | X8       | <u> </u> | <b>^</b>  | b         | <b>↓</b> | <u>, 1 , 2</u><br>e45 |      |

| SIMULATION     Run Simulation                |                                                                                                                                       |                             | >           | W M1[11:0]            | b60 Arra      | > W inputbus_temp                 |                                         | 5e5 X                                       | beb X    | 797 X  | f2f X e5f |              |            | X 2ff    | X 5ff    | ) bff     | X 7ff     | × ###    | χ e45 χα              |      |

| Run Simulation                               |                                                                                                                                       |                             |             |                       |               | > 😼 M1[11:0]                      | cbf                                     | beb                                         | 797      |        | e5f cbf   |              | X 2ff      |          |          |           | X ttt     | X e45    | X c8b XD              |      |

| ✓ RTL ANALYSIS                               |                                                                                                                                       |                             |             |                       |               |                                   |                                         |                                             |          |        |           |              |            |          |          |           |           |          |                       |      |

| > Open Elaborated Design                     |                                                                                                                                       |                             |             |                       |               |                                   |                                         |                                             |          |        |           |              |            |          |          |           |           |          |                       |      |

|                                              |                                                                                                                                       |                             |             |                       |               |                                   |                                         |                                             |          |        |           |              |            |          |          |           |           |          |                       |      |

| ✓ SYNTHESIS                                  |                                                                                                                                       |                             |             |                       |               |                                   |                                         |                                             |          |        |           |              |            |          |          |           |           |          |                       |      |

| Run Synthesis                                |                                                                                                                                       |                             |             |                       |               |                                   |                                         |                                             |          |        |           |              |            |          |          |           |           |          |                       |      |

| > Open Synthesized Design                    |                                                                                                                                       |                             |             |                       |               |                                   |                                         |                                             |          |        |           |              |            |          |          |           |           |          |                       |      |

| ✓ IMPLEMENTATION                             |                                                                                                                                       |                             |             |                       |               |                                   |                                         |                                             |          |        |           |              |            |          |          |           |           |          |                       |      |

| Run Implementation                           |                                                                                                                                       |                             |             |                       |               |                                   |                                         |                                             |          |        |           |              |            |          |          |           |           |          |                       |      |

| > Open Implemented Design                    |                                                                                                                                       |                             |             |                       |               |                                   |                                         |                                             |          |        |           |              |            |          |          |           |           |          |                       |      |

| > Open implemented Design                    |                                                                                                                                       |                             |             |                       |               |                                   |                                         |                                             |          |        |           |              |            |          |          |           |           |          |                       |      |

| Y PROGRAM AND DEBUG                          |                                                                                                                                       |                             |             |                       |               |                                   |                                         |                                             |          |        |           |              |            |          |          |           |           |          |                       |      |

| Senerate Bitstream                           |                                                                                                                                       |                             |             |                       |               |                                   |                                         |                                             |          |        |           |              |            |          |          |           |           |          |                       |      |

| > Open Hardware Manager                      |                                                                                                                                       |                             |             |                       |               |                                   |                                         |                                             |          |        |           |              |            |          |          |           |           |          |                       |      |

|                                              |                                                                                                                                       |                             |             |                       |               |                                   |                                         |                                             |          |        |           |              |            |          |          |           |           |          |                       |      |

|                                              |                                                                                                                                       |                             |             |                       |               |                                   |                                         |                                             |          |        |           |              |            |          |          |           |           |          |                       |      |

|                                              |                                                                                                                                       |                             |             |                       |               |                                   |                                         |                                             |          |        |           |              |            |          |          |           |           |          |                       |      |

|                                              |                                                                                                                                       |                             |             |                       |               |                                   |                                         |                                             |          |        |           |              |            |          |          |           |           |          |                       |      |

|                                              |                                                                                                                                       |                             |             |                       |               |                                   |                                         |                                             |          |        |           |              |            |          |          |           |           |          |                       |      |

|                                              |                                                                                                                                       |                             |             |                       |               |                                   |                                         |                                             |          |        |           |              |            |          |          |           |           |          |                       |      |

|                                              |                                                                                                                                       |                             |             |                       |               |                                   |                                         |                                             |          |        |           |              |            |          |          |           |           |          |                       |      |

|                                              |                                                                                                                                       |                             |             |                       |               |                                   |                                         |                                             |          |        |           |              |            |          |          |           |           |          |                       |      |

|                                              |                                                                                                                                       |                             |             |                       |               |                                   |                                         |                                             |          |        |           |              |            |          |          |           |           |          |                       |      |

|                                              |                                                                                                                                       |                             |             |                       |               |                                   |                                         |                                             |          |        |           |              |            |          |          |           |           |          |                       |      |

|                                              |                                                                                                                                       |                             |             |                       |               |                                   |                                         |                                             |          |        |           |              |            |          |          |           |           |          |                       |      |

|                                              |                                                                                                                                       |                             | < 0         |                       | >             | ~                                 | <                                       | > <                                         |          |        |           |              | -          |          |          |           |           |          |                       | >    |

|                                              | Tel Constelle - M. Hennessen - Lon                                                                                                    |                             |             |                       |               |                                   |                                         |                                             |          |        |           |              | ? _ 🗆      | 14       |          |           |           |          |                       |      |

|                                              | TclConsole       ×       Messages       Log         Q       ₹       ↓↓       ↓↓       ↓↓         D       ₹       ↓↓       ↓↓       ↓↓ |                             |             |                       |               |                                   |                                         |                                             |          |        |           |              |            | r = U    | -        |           |           |          |                       |      |

|                                              | Q <b>x ₹ 1 u</b><br>run 20000 ns                                                                                                      | a   enel   MA               |             |                       |               |                                   |                                         |                                             |          |        |           |              |            |          |          |           |           |          |                       | ~    |

|                                              | run 20000 ns                                                                                                                          |                             |             |                       |               |                                   |                                         |                                             |          |        |           |              |            |          |          |           |           |          |                       |      |

|                                              | run 20000 ns<br>run 20000 ns                                                                                                          |                             |             |                       |               |                                   |                                         |                                             |          |        |           |              |            |          |          |           |           |          |                       |      |

|                                              | <                                                                                                                                     |                             |             |                       |               |                                   |                                         |                                             |          |        |           |              |            |          |          |           |           |          |                       | ~    |

|                                              | Type a Tcl command he                                                                                                                 | ce                          |             |                       |               |                                   |                                         |                                             |          |        |           |              |            |          |          |           |           |          |                       |      |

|                                              |                                                                                                                                       |                             |             |                       |               |                                   |                                         |                                             |          |        |           |              |            |          |          |           |           |          |                       |      |

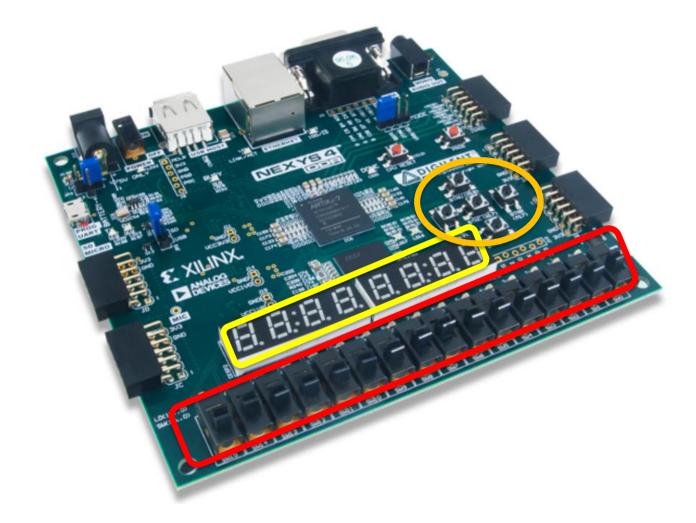

## Nexys 4 FPGA (Labs 2-5)

# Lab1 Assignment

- Draw the state diagrams

- Cross check

- Implement FSM in VHDL

- Show simulation

- Demonstrate understanding