Processor MC68008

Microprocessorn vi valde finns i två versioner, 48 respektive 52 pins. Då emulatorn endast kan hantera

48 pins versionen valdes denna. 48 pins versionen saknar bl a några adressledningar och begränsar därmed

det adresserbara minnet till 1 Mb.

MC68008 är en bantad version av storebror MC68000. Den möjliggör design av kostnadseffektiva

system med 8 bitars databuss men med 32 bitars processorarkitektur. All kommunikation med periferienheter

är normalt asynkron, dock finns stöd även för synkrona enheter.

En asynkron busscykel (write):

- Processorn lägger ut en adress på adressbussen.

- Processorn aktiverar adress-strobenĀ(AS) - indikerar att giltig adress finns på adressbussen.

- Processorn lägger ut data på databussen.

- Processorn aktiverar data-stroben (DS) - indikerar att giltig data finns på databussen.

- Periferienheten läser data från databussen.

- Periferienheten aktiverar data-acknowledge (DTACK).

Vi gör en förenklad lösning av ovanstående busscykel - vi antar att DTACK kan genereras efter en bestämd

tid och förusätter därmed att periferienheten hinner med att läsa in data från databussen under en viss

förutbestämd tid. DTACK genereras i en PAL krets och dess grindfördröjning får tjäna som konstant

tidsfördröjning.

En asynkron busscykel (read):

- Processorn lägger ut en adress på adressbussen.

- Processorn aktiverar adress-stroben (AS).

- Processorn aktiverar data-stroben (DS).

- Periferienheten lägger ut data på databussen.

- Periferienheten aktiverar data-acknowledge (DTACK).

- Processorn läser in data från databussen.

Vi förenklar ovanstående busscykel på samma sätt som tidigare - en PAL krets genererar DTACK istället för

periferienheten.

En synkron busscykel (read):

- Processorn lägger ut en adress på adressbussen.

- Processorn aktiverar adress-stroben (AS).

- Processorn aktiverar data-stroben (DS).

- JK vippan aktiverar 'valid peripheral address' (VPA), vilket får processorn att gå in i synkront läge.

- JK vippan genererar 'valid memory address' (VMA), vilket aktiverar periferienheten för läsning.

- Busscykeln avslutas när 'enable' (E) genomlöpt en cykel.

Under en synkron busscykel får inte DTACK genereras då VPA är aktiv. Om både DTACK och VPA aktiveras

går MC68008 in i ett obestämt tillstånd.

Datablad

Emulator

Utvecklingsmiljö

EPROM - 27C256 32K

Standard EPROM som raderas med UV-ljus och programmeras elektriskt.

Datablad

Hex-kod

SRAM - 43256 32K

Statiskt RAM.

Datablad

PAL - CE22V10

Vi har valt att generera alla 'chip select' samt övrig logik med hjälp av PAL kretsar. Fördelen med att

programmera logik istället för att koppla med standard TTL logik är att realiseringen blir kompakt samt

enkel att ändra.

Vid programmering av en PAL krets används en konfigurationsfil som beskriver logiken. Filen används

som indata till ett program som via en extern enhet programmerar PAL kretsen elektriskt.

Datablad

Minnesmappning

Konfigurationsfil för 'chip select'

Konfigurationsfil för avbrott

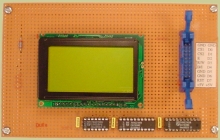

LCD - Batron 128x64 LCD

Displayen består av två segment om vardera 64x64 pixel. Segmenten aktiveras och matas med data oberoende

av varandra. Varje segment har 8 kolumner, vilka i sin tur är uppdelade i 40 rader. De olika segmenten

pekas ut med 'chip select' (CS1 och CS2).

De operationer som kan utföras på displayen är:

- On/off

- Sätta offset för scrollning

- Peka ut rad (0-39)

- Peka ut kolumn (0-7)

- Skriva data till minne.

- Läsa data från minne.

Då en viss kolumn och rad har lästs eller skrivits (8 bitar), inkrementeras aktuellt radindex automatiskt.

En fullständig omritning av ett segment är sålunda relativt enkelt att utföra.

för alla 8 kolumner

{

aktivera kolumn

aktivera rad 0 i aktiv kolumn

mata display med 40 byte data (40 rader)

}

Datablad för Batron LCD

Datablad för styrkrets (1)

Datablad för styrkrets (2)

Systemklocka

Systemklockan är uppbyggd av en inverterare som är kopplad enligt figur 2 i nedanstående ritning. Klockan

är konstruerad för att generera en frekvens på 10 MHz.

Ritning

JK-vippa

Används för att synkronisera processorn mot de periferienheter som kräver synkron kommunikation. I vårt fall

är det endast LCD displayen som kommunicerar synkront.

D-latch

Används för att separera spelknapparna från databussen.

Avbrottstimer - 74LS292

Kretsen delar ner systemklockan med ett värde som laddas in i 292-kretsen. Den genererade utfrekvensen

triggar sedan interruptnivå 5.

Vi använder för närvarande inte något interrupt i programmet, men har

byggt in funktionen för framtida behov.

Datablad

Spelknapp

En switch matad med 5 volt via ett motstånd. Signalen är ansluten till en D-latch och används som input

till spelet.

Kopplingen medför att nedtryckt spelknapp genererar en nolla och ej nedtryckt spelknapp

genererar en etta på respektive knapps bitposition:

- 0 - Vänster

- 1 - Höger

- 2 - Avfyrning

Reset - DS 1233

Resetkretsen är byggd kring en DS 1233 och har två funktioner. Vid påslag av spänning samt vid

användarinitierad reset håller kretsen resetsignalen viss tid.

Datablad

Spänningsmatning

Extern källa - 5 volt.

|