### **HARDWARE**

## **Interface Signals**

Table 2. Interface Signals

| SIGNAL NAME                       | INPUT/OUTPUT   | EXTERNAL CONNECTION | FUNCTION                                                                                                                                                                                |

|-----------------------------------|----------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RS                                | Input          | MPU                 | Register select signal "0": Instruction register (when writing) Busy flag and address counter (when reading) "1": Data register (when writing and reading)                              |

| R/W                               | Input          | MPU                 | Read/write select signal: "0": Writing; "1": Reading                                                                                                                                    |

| E                                 | Input          | MPU                 | Operation (data read/write) enable signal                                                                                                                                               |

| DB4 - DB7                         | In put/Output  | MPU                 | High-order lines of data bus with three-state, bidirctional function for use in data transactions with the MPU. DB <sub>7</sub> may also be used to check the busy flag.                |

| DB <sub>0</sub> - DB <sub>3</sub> | In pu t/Output | MPU                 | Low-order lines of data bus with three-state, bidirectional function for use in data transactions with the MPU.  These lines are not used when interfacing with a 4-bit microprocessor. |

| $V_{DD}, V_{SS}$                  |                | Power Supply        | V <sub>DD</sub> : +5 V, V <sub>SS</sub> : GND                                                                                                                                           |

| V <sub>0</sub>                    | <u> </u>       | Power Supply        | Contrast adjustment voltage                                                                                                                                                             |

### **Functional Blocks**

# Registers

The LCD unit has two 8-bit registers - an instruction register (IR) and a data register (DR). The instruction register stores instruction codes such as "clear display" or "shift cur sor", and als o stores address information for the display data RAM and character generator RAM. The IR can be accessed by the microprocessor only for writing.

The data register is used for temporarily storing data during data transactions with the microprocessor. When writing data to the LCD unit, the data is initially stored in the data register, and is then automatically written into either the display data RAM or character gener ator RAM, as deter mined by the

current operation. The data register is also used as a temporary storage area when reading data from the display data RAM or character generator RAM. When address information is written into the instruction register, the corresponding data from the display data RAM or character generator RAM is moved to the data register. Data transfer is completed when the microprocessor reads the contents of the data register by the next instruction. After the transfer is completed, data from the next address position of the appropriate RAM is moved to the data register, in preparation for subsequent reading operations by the microprocessor. One of the two registers is selected by the register select (RS) signal.

Table 3. Register Selection

| RS | R/W | OPERATION                                                                                                 |

|----|-----|-----------------------------------------------------------------------------------------------------------|

| 0  | 0   | Write to instruction register, and execute internal operation (clear display, etc.)                       |

| 0  | 1   | Read busy flag (DB <sub>7</sub> ) and address counter (DB <sub>0</sub> - DB <sub>6</sub> )                |

| 1  | 0   | Write to data register, and execute internal operation (DR $ ightarrow$ DD RAM or DR $ ightarrow$ CG RAM) |

| 1  | 1   | Read data register and execute internal operation (DD RAM $ ightarrow$ DR or CG RAM $ ightarrow$ DR)      |

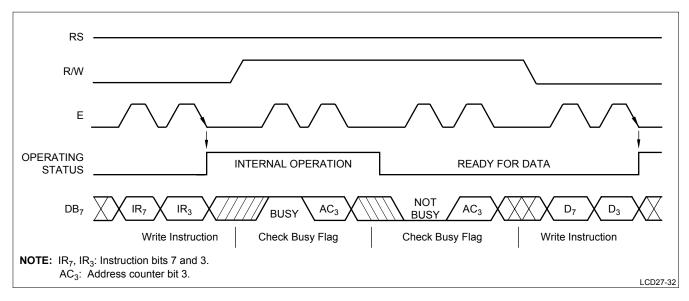

### Busy Flag (BF)

When the busy flag is set at a logical "1", the LCD unit is executing an internal operation, and no instruction will be accepted. The state of the busy flag is output ondata line DB<sub>7</sub> in response to the register selection signals RS = 0, R/W= 1 as shown in Table 3. The next ins truction may be enter ed after the busy flag is reset to logical "0".

### Address Counter (AC)

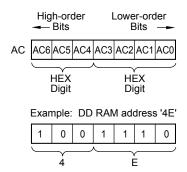

The address counter generates the address for the di splay d ata R AM and c haracter generator RAM. When the address set instruction is written into the instruction register, the address information is sent to the address counter. The same instruction also determines which of the two RAM's is to be selected.

After data has been written to or read from the display data RAM or character generator RAM, the address counter is autom atically incr emented or decremented by one. The contents of the address counter ar e output on data lines DB  $_0$  - DB $_6$  in response to the register selection signals RS = 0, R/W = 1 as shown in Table 3.

### Display Data RAM (DD RAM)

This 80 x8 bitRAM stores up to 80 8-bit character codes as display data. The unused area of the RAM may be us ed by the m icroprocessor as a gener al purpose RAM area.

The display data RAMaddress, set in the addess counter, is expressed in hexadecimal (HEX) numbers as follows:

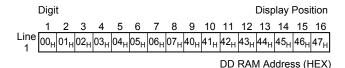

The address of the dis play data RAM c orresponds to the display position on the LCD panel as follows:

a. Address type a . . . . For dual-line display

|        |                 |                 |                 |                 |                 |                 |                 |                 |                 | Display Position |                 |                 |  |  |  |

|--------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|------------------|-----------------|-----------------|--|--|--|

| Digit  | _1_             | 2               | 3               | 4               | 5               | 6               | 7               | 8               | 9               |                  | 39              | 40              |  |  |  |

| Line 1 | 00 <sub>H</sub> | 01 <sub>H</sub> | 02 <sub>H</sub> | 03 <sub>H</sub> | 04 <sub>H</sub> | 05 <sub>H</sub> | 06 <sub>H</sub> | 07 <sub>H</sub> | 08 <sub>H</sub> |                  | 26 <sub>H</sub> | 27 <sub>H</sub> |  |  |  |

| Line 2 | 40 <sub>H</sub> | 41 <sub>H</sub> | 42 <sub>H</sub> | 43 <sub>H</sub> | 44 <sub>H</sub> | 45 <sub>H</sub> | 46 <sub>H</sub> | 47 <sub>H</sub> | 48 <sub>H</sub> |                  | 66 <sub>H</sub> | 67 <sub>H</sub> |  |  |  |

DD RAM Address (HEX)

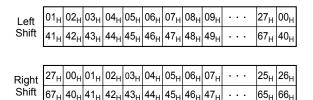

When a display shift takes place, the addresses shift is as follows:

The addresses for the second line are not continuous to the addresses for the first line. A40-character RAM area is assigned to each of the two line as follows:

line 1:

$$00_H$$

-  $27_H$

line 2:  $40_H$  -  $67_H$

For an LCD unit with a dis play capacity of less than 40 char acters per line, c haracters equal in number to the display capacity, as counted from display position 1, are displayed.

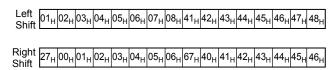

b. Address type b . . . . For single-line display with logically dual-line addressing

When a display shift takes place, the addresses shift as follows:

The right-hand eight characters, for the purposes of addressing and shifting, m ay be considered to constitute a second display line. For the address type of each model, see Table 12.

.......

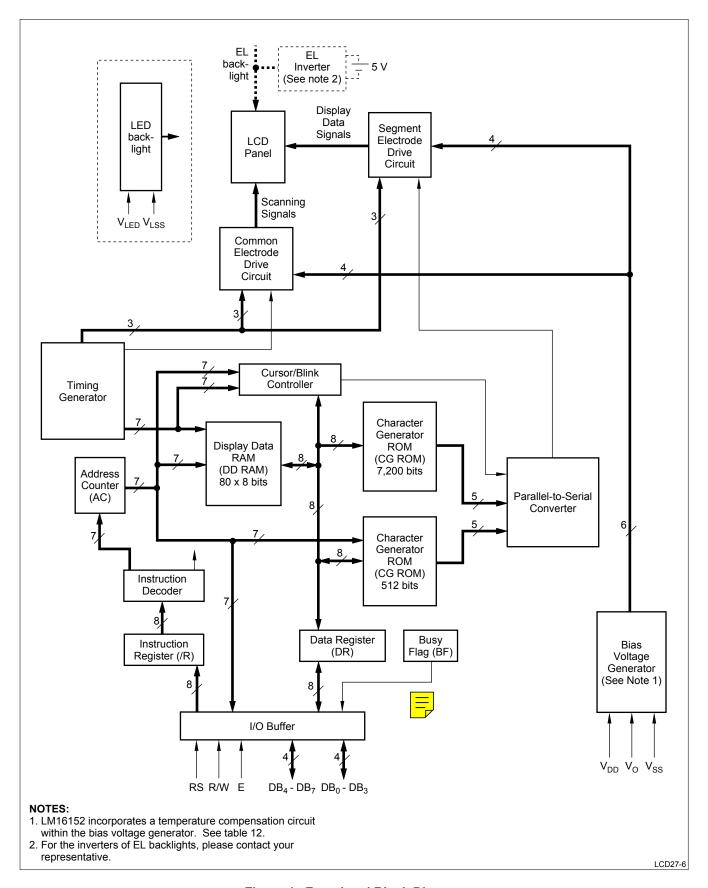

Figure 1. Functional Block Diagram

**Table 4. Character Codes**

| HIGH-ORDER<br>4 BIT<br>LOW-<br>ORDER 4 BIT |                  | 0010     | 0011     | 0100    | 0101  | 0110         | 0111     | 1010     | 1011       | 1100     | 1101         | 1110       | 1111 |

|--------------------------------------------|------------------|----------|----------|---------|-------|--------------|----------|----------|------------|----------|--------------|------------|------|

| xxxx0000                                   | CG<br>RAM<br>(1) |          |          |         |       | *•           | ====     |          |            |          | <u>-</u>     | ÷:         |      |

| xxxx0001                                   | (2)              |          |          |         |       |              |          |          |            |          |              | -:::       |      |

| xxxx0010                                   | (3)              |          |          |         |       |              | <b>!</b> |          |            |          | <u>,::</u> : |            |      |

| xxxx0011                                   | (4)              |          |          | · · · · | ===== | i <u></u> .  |          |          |            |          |              | ==-        | 4-3  |

| xxxx0100                                   | (5)              |          |          |         |       |              | <b>‡</b> | •.       |            | <b>!</b> |              |            |      |

| xxx0101                                    | (6)              |          |          |         |       |              | 1        | #        |            |          |              | ===        |      |

| xxx0110                                    | (7)              |          | ===      |         | 1,,1  |              | 1.,1     |          |            |          |              |            |      |

| xxxx0111                                   | (8)              | :        | :        |         |       |              |          |          |            |          |              |            | .II. |

| xxxx1000                                   | (1)              | •        |          |         | :::   | <b>!</b> :   | ×        |          |            |          | ij           | .J"        | ×    |

| xxxx1001                                   | (2)              | <b>;</b> |          | i       | 1,1   |              |          |          |            |          | 11.          | 1          |      |

| xxxx1010                                   | (3)              | -#-:     | ##       |         |       | :            |          |          |            | : 1      | 1            |            |      |

| xxxx1011                                   | (4)              |          | #<br>;   |         |       |              | -        | <b>:</b> |            |          |              | ×          |      |

| xxxx1100                                   | (5)              | :        | •        |         |       | <b>!</b>     |          |          | =:         |          |              | 4          |      |

| xxxx1101                                   | (6)              |          |          |         |       |              |          |          |            | -*       | <u>.</u> .:  | <b></b>    | -    |

| xxxx1110                                   | (7)              |          | <b>:</b> |         | "•.   | <b>!-"</b> ! |          |          |            |          | •.••         | <b>!</b> " |      |

| xxxx1111                                   | (8)              |          | •        |         |       | ::::         |          | :::      | <b>.</b> ! | -:       | ===          | ::::       |      |

#### NOTES:

- 1. The CG RAM generates character patterns in accordance with the user's program.

- 2. Shaded areas indicate 5 x 10 dot character patterns.

Dot-Matrix LCD Units SHARP

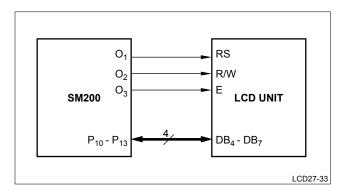

### 4-Bit Interface

Figure 4. 4-Bit Interface

Table 7. Instruction Set

| INSTRUCTION                          |                                                                                                                |     |                 |                 | CC              | DE              |                 |                 |                 |                                                                                                                                                 | FUNCTION                                                                                                             | EXECUTION TIME (max)    |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------|-----|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-------------------------|

| MOTROCTION                           | RS                                                                                                             | R/W | DB <sub>7</sub> | DB <sub>6</sub> | DB <sub>5</sub> | DB <sub>4</sub> | DB <sub>3</sub> | DB <sub>2</sub> | DB <sub>1</sub> | DB <sub>0</sub>                                                                                                                                 | TONCTION                                                                                                             | (fcp or fosc = 250 kHz) |

| Display Clear                        | 0                                                                                                              | 0   | 0               | 0               | 0               | 0               | 0               | 0               | 0               | 1                                                                                                                                               | Clear enter display area, restore display from shift, and load address counter with DD RAM address 00 <sub>H</sub> . | 1.64 ms                 |

| Display/Cursor<br>Home               | 0                                                                                                              | 0   | 0               | 0               | 0               | 0               | 0               | 0               | 1               | *                                                                                                                                               | Restore display from shift and load address counter with DD RAM address 00 <sub>H</sub> .                            | 1.64 ms                 |

| Entry Mode<br>Set                    | 0                                                                                                              | 0   | 0               | 0               | 0               | 0               | 0               | 1               | I/D             | S                                                                                                                                               | Specify cursor advance direction and display<br>shift mode. This operation takes place after<br>each data transfer.  | 40 μs                   |

| Display ON/OFF                       | 0                                                                                                              | 0   | 0               | 0               | 0               | 0               | 1               | D               | С               | В                                                                                                                                               | Specify activation of display (D), cursor (C), and blinking of character at cursor position (B).                     | 40 μs                   |

| Display/Cursor<br>Shift              | 0                                                                                                              | 0   | 0               | 0               | 0               | 1               | S/C             | R/L             | *               | *                                                                                                                                               | Shift display or move cursor.                                                                                        | 40 μs                   |

| Function Set                         | 0                                                                                                              | 0   | 0               | 0               | 1               | DL              | N               | 0               | *               | *                                                                                                                                               | Set interface data length (DL) and number of display lines (N).                                                      | 40 μs                   |

| CG RAM<br>Address Set                | 0                                                                                                              | 0   | 0               | 1               |                 |                 | А               | CG              |                 |                                                                                                                                                 | Load the address counter with a CG RAM address. Subsequent data is CG RAM data.                                      | 40 μs                   |

| DD RAM<br>Address Set                | 0                                                                                                              | 0   | 1               |                 |                 |                 | $A_{DD}$        |                 |                 |                                                                                                                                                 | Load the address counter with a DD RAM address. Subsequent data is DD RAM data.                                      | 40 μs                   |

| Busy<br>Flag/Address<br>Counter Read | 0                                                                                                              | 1   | BF              |                 |                 |                 | AC              |                 |                 |                                                                                                                                                 | Read busy flag (BF) and contents of address counter (AC).                                                            | 0 μs                    |

| CG RAM/DD<br>RAM Data Write          | 1                                                                                                              | 0   |                 |                 |                 | Write           | data            |                 |                 |                                                                                                                                                 | Write data to CG RAM or DD RAM.                                                                                      | 40 μs                   |

| CG RAM/DD<br>RAM Data Read           | 1                                                                                                              | 1   |                 |                 |                 | Read            | data            |                 |                 |                                                                                                                                                 | Read data from CG RAM or DD RAM.                                                                                     | 40 μs                   |

|                                      | S = 1: Display Shift On S/C = 1: Shift Display, S/C = 0: Move Cursor R/L = 1: Shift Right, R/L = 0: Shift Left |     |                 |                 |                 |                 |                 | tion            |                 | DD RAM: Display Data RAM CG RAM: Character Generator RAM Acg: Character Generator RAM Address ADD: Display Data RAM Address AC: Address Counter |                                                                                                                      |                         |

#### NOTES:

- 1. Symbol "\*" signifies a "don't care" bit.

- 2. Correct input value for "N" is predetermined for each model (see Table 12).

#### **ELECTRICAL CHARACTERISTICS**

### **Absolue Maximum Ratings**

See the device specifications for each LCD unit model.

#### **Electrical Characteristics**

See the device specificiations for each LCD unit model. Some of the cur rently available specifications do not describe the test conditions for the high-level and low-level output v oltages. These conditions are as follows:

Table 8.

| PARAMI  | ETER | SYMBOL | TEST CONDITIONS             | MIN. | MAX. | UNIT |

|---------|------|--------|-----------------------------|------|------|------|

| Output  | Н    | Vон    | -l <sub>OH</sub> = 0.205 mA | 2.4  | _    | ٧    |

| Voltage | L    | Vol    | I <sub>OL</sub> = 1.2 mA    |      | 0.4  | V    |

## **Timing Characteristics**

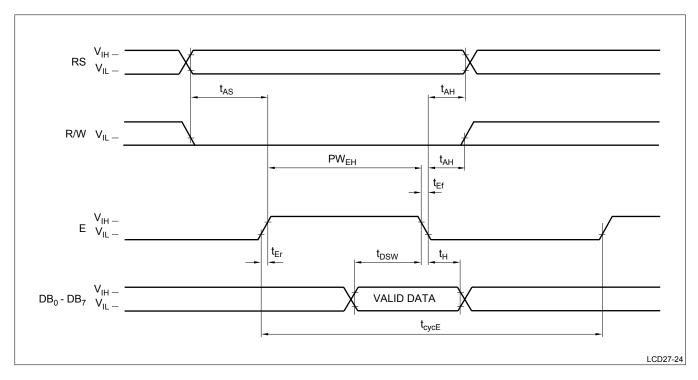

Figure 5. Write Operation Timing Diagram

(For data sent from the external microprocessor to the LCD unit)

**Table 9. Write Operation Timing Characteristics**

$(V_{DD} = 5.0 \pm 5\%, V_{SS} = 0 \text{ V}, T_{A} = 0 \sim 50^{\circ}\text{C})$

| PARAMET               | FR                                            | SYMBOL           | VAL  | UNIT |      |

|-----------------------|-----------------------------------------------|------------------|------|------|------|

| TAIVAMET              | <u>- 11                                  </u> | OT MID OL        | MIN. | MAX. | ONII |

| Enable Cycle Time     |                                               | tcycE            | 1000 | _    | ns   |

| Enable Pulse Width    | "High" Level                                  | PW <sub>EH</sub> | 450  | _    | ns   |

| Enable Rise/Fall Time |                                               | ter, ter         | _    | 25   | ns   |

| Setup Time            | RS, R/W-E                                     | t <sub>AS</sub>  | 140  | _    | ns   |

| Address Hold Time     | •                                             | t <sub>AH</sub>  | 10   | _    | ns   |

| Data Setup Time       |                                               | tosw             | 195  | _    | ns   |

| Data Hold Time        |                                               | t <sub>H</sub>   | 10   | _    | ns   |

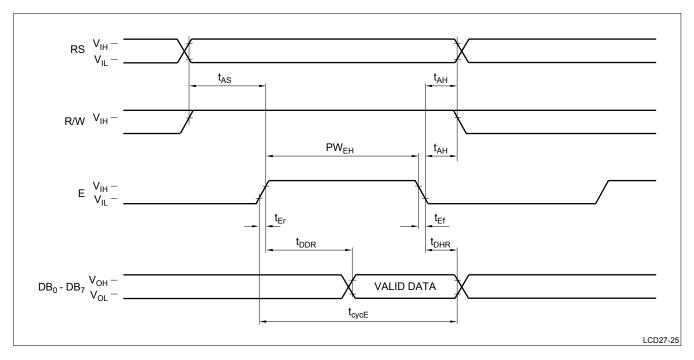

Figure 6. Read Operation Timing Diagram

(For data sent from the LCD unit to the external microprocessor)

Table 10. Read Operation Timing Characteristics ( $V_{DD}$  = 5.0 ± 5%,  $V_{SS}$  = 0 V, Ta = 0 ~ 50°C)

|                       |                  |                    | VAL  | HE   |    |

|-----------------------|------------------|--------------------|------|------|----|

| PARAMETE              | ĒR               | SYMBOL             | VAL  | UNIT |    |

|                       |                  |                    | MIN. |      |    |

| Enable Cycle Time     |                  | t <sub>cyc</sub> E | 1000 | _    | ns |

| Enable Pulse Width    | "High" Level     | PWEH               | 450  | _    | ns |

| Enable Rise/Fall Time | •                | ter, ter           | _    | 25   | ns |

| Setup Time            | RS, R/W-E        | tas                | 140  | _    | ns |

| Address Hold Time     |                  | t <sub>AH</sub>    | 10   | _    | ns |

| Data Delay Time       | t <sub>DDR</sub> | _                  | 320  | ns   |    |

| Data Hold Time        |                  | t∩µp               | 20   |      | ns |

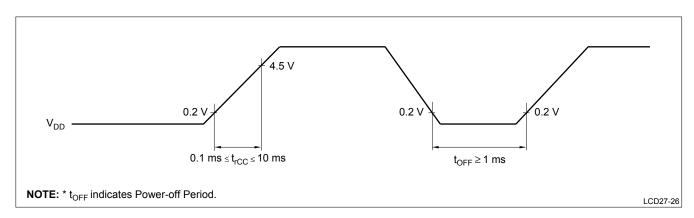

**Table 11. Power Conditions for Internal Reset**

| PARAMETER             | SYMBOL           |      | UNIT |      |    |

|-----------------------|------------------|------|------|------|----|

|                       | 01111202         | MIN. | TYP. | MAX. | •  |

| Voltage Build-Up Time | t <sub>rcc</sub> | 0.1  | _    | 10   | ms |

| Power-Off Period      | toff             | 1    | _    |      | ms |

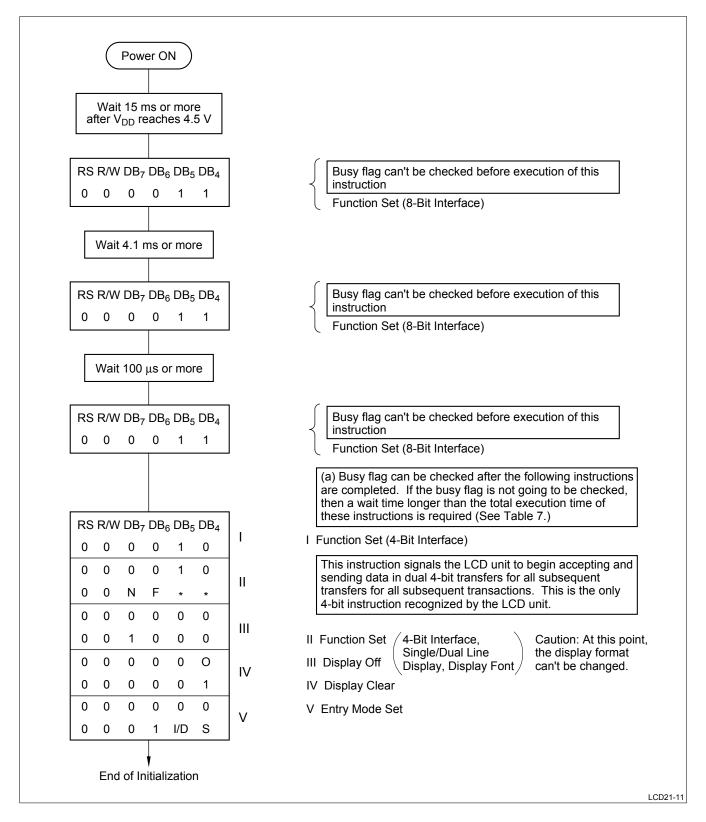

If the above conditions are not satisfied, the internal reset circuit will not operate normally. In such a case, the LCD unit must be initialized by executing a series of instructions (see the Ex ecution by Instructions section).

Figure 7.

2. 4-Bit Data Transfer with a Single-Line, 16-Character Display (Using Internal Reset). Table 14 shows a sample operating procedure for an LCD unit in this mode. After power has been turned on, the 8-bit data transfer mode is in effect, and the first write operation is assumed to be an 8-bit data transfer.

Since the data lines DB  $_{0}$  - DB $_{3}$  are not connected, this data is not accepted and must be written again (i.e. the function s et instruction must be written twice). Subsequent data transfers are completed in two 4-bit transfer operations (see Table 14).

Figure 9. 4-Bit Interface Timing (Example)

Figure 10. Connection to SM200