# IDT79RC36100 Highly Integrated RISController Hardware User's Manual

Version 2.1 August 1998

2975 Stender Way, Santa Clara, California 95054 Telephone: (800) 345-7015 • TWX: 910-338-2070 • FAX: (408) 492-8674 Printed in U.S.A. © 1998 Integrated Device Technology, Inc. Integrated Device Technology, Inc. reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance and to supply the best possible product. IDT does not assume any responsibility for use of any circuitry described other than the circuitry embodied in an IDT product. The Company makes no representations that circuitry described herein is free from patent infringement or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent, patent rights or other rights, of Integrated Device Technology, Inc.

#### LIFE SUPPORT POLICY

Integrated Device Technology's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is executed between the manufacturer and an officer of IDT.

1. Life support devices or systems are devices or systems which (a) are intended for surgical implant into the body or (b) support or sustain life and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

2. A critical component is any components of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

The IDT logo is a registered trademark, and BiCameral, BurstRAM, BUSMUX, CacheRAM, DECnet, Double-Density, FASTX, Four-Port, FLEXI-CACHE, Flexi-PAK, Flow-thruEDC, IDT/ c, IDTenvY, IDT/sae, IDT

MIPS is a registered trademark, and RISCompiler, RISComponent, RISComputer, RISCware, RISC/os, R3000, and R3010 are trademarks of MIPS Computer Systems, Inc. Postscript is a registered trademark of Adobe Systems, Inc. AppleTalk, LocalTalk, and Macintosh are registered trademarks of Apple Computer, Inc. Centronics is a registered trademark of Genicom, Inc. Ethernet is a registered trademark of Digital Equipment Corp. PS2 is a registered trademark of IBM Corp.

## **About This Manual**

### Notes

This hardware user's manual provides updated functional overviews and operational details on the IDT79RC36100 Integrated RISController<sup>™</sup>. As noted below, a MIPS-I architectural overview is included. However, for more detailed software information or descriptions on individual CPU/FPU instructions, refer to the *IDT MIPS Microprocessor Family Software Reference Manual*.

#### **Summary of Contents**

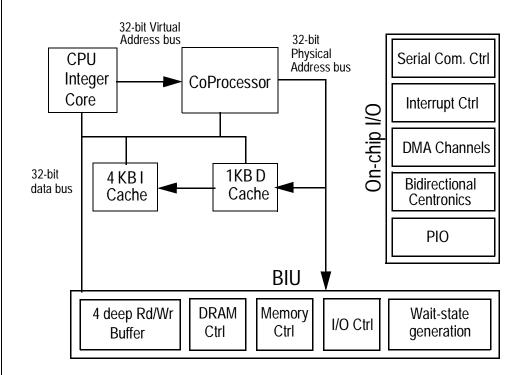

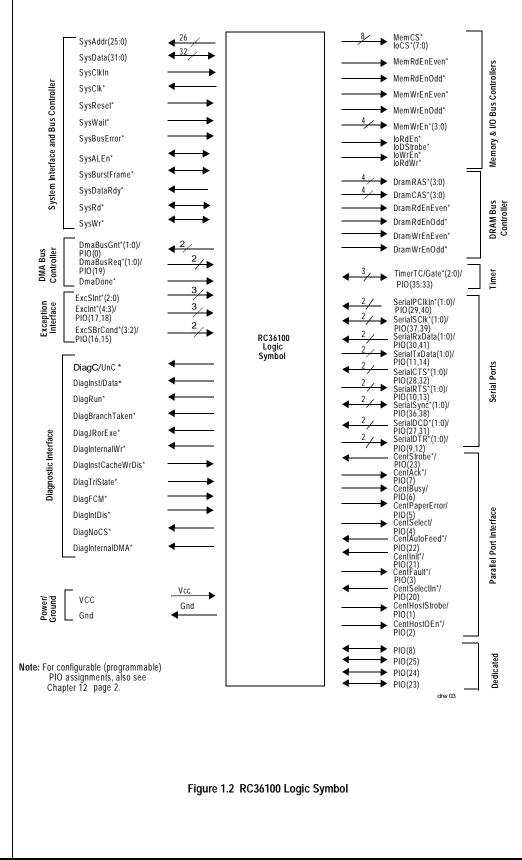

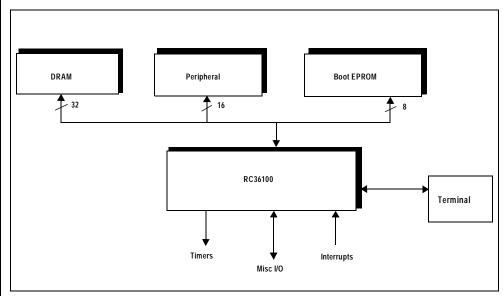

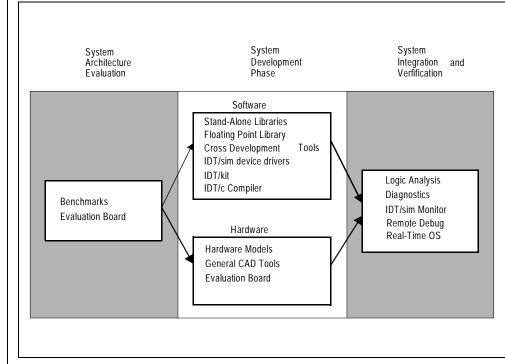

Chapter 1, "RC36100 Device Overview," presents an introduction to the operation of the RC36100 device and provides a revised block diagram that illustrates system components. This chapter includes an updated features list, pin description table, logic diagram and performance overview.

**Chapter 2**, **"Instruction Set Architecture**," contains an overview of the MIPS-1 architecture set and discusses the programmers' model for this device. This chapter also provides a summary of the CPU registers.

**Chapter 3**, **"Cache Architecture**," reviews the fundamentals of general cache operation and provides a discussion on the organization of the RC36100's on-chip caches.

Chapter 4, "Virtual-to-Physical Address Translation and Address Map," explains the devices two operating states (kernal and user) as well as the virtual-to-physical address translation mechanisms provided in the RC36100.

Chapter 5, "Coprocessor 0 Register Set," describes the implementation of the RC36100's system control coprocessor (CPO). This chapter provides complete descriptions of registers and includes field actions and values.

**Chapter 6**, **"Interruption and Exception Handling**," discusses the pipeline stages implemented in the RC36100 and provides a structure for understanding the device's exception handling processes. This chapter also contains a section on "Basic Software Techniques For Handling Interrupts."

Chapter 7, "System Bus Interface Unit Overview," provides an operational overview on the RC36100's execution core, as well as operation of the various memory controllers during both internal and external peripheral transactions.

**Chapter 8**, "**Memory Controller**," addresses the RC36100's on-chip memory controller interface and includes pin descriptions and timing diagrams. This chapter includes an explanation on how this interface relates to typical external hardware ROMs and RAMs.

**Chapter 9**, **"I/O Controller**," provides an overview of the I/O controller interface, pin descriptions and timing diagrams. A discussion on the relationship between this interface and typical external hardware I/O devices is also included.

Chapter 10, "DRAM Controller," presents an overview on the DRAM controller interface of the RC36100 and includes pin descriptions, timing diagrams and a discussion on the relationship between the interface and typical external hardware DRAM systems.

Chapter 11, "Direct Memory Access (DMA) Controller," explains the DMA Controller interface and its relationship to typical internal and external hardware DMA systems. Complete pin definitions, signal information, timing diagrams, and register drawings are also provided.

Chapter 12, "Parallel Input/Output (PIO)," provides an operational overview on the PIO programming interface and includes register descriptions and a table indicating the alternate functions that are mapped to the PIO pins.

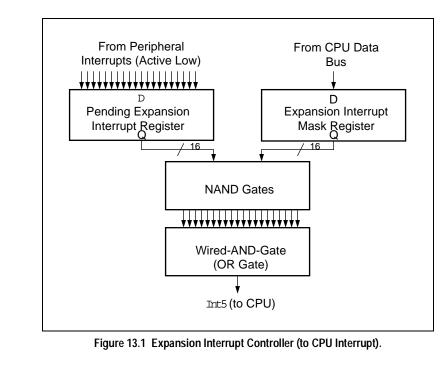

Chapter 13, "Peripheral Expansion Interrupt Controller," overviews the features and operation of this controller. A block diagram as well as pin and register descriptions are also provided.

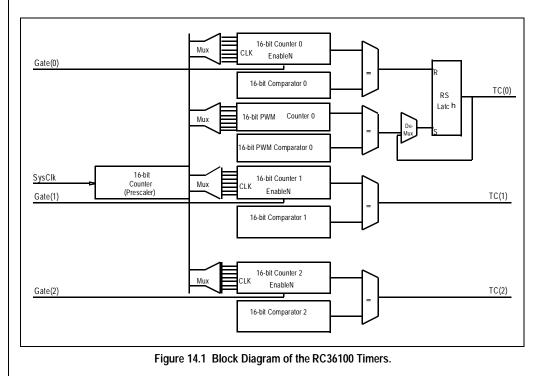

**Chapter 14**, **"Timers**," overviews the features and operation of the RC36100's timer programming interface. This chapter also provides pin descriptions and a discussion on how these timers relate to typical internal and external systems.

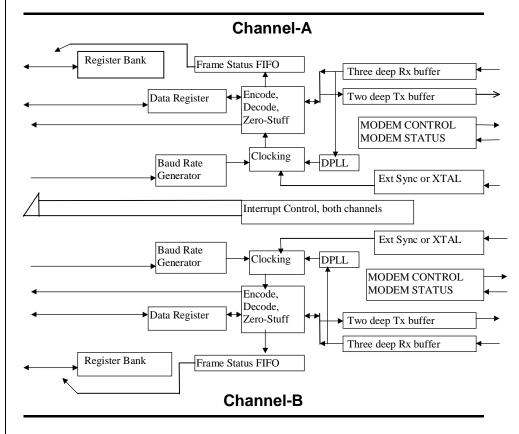

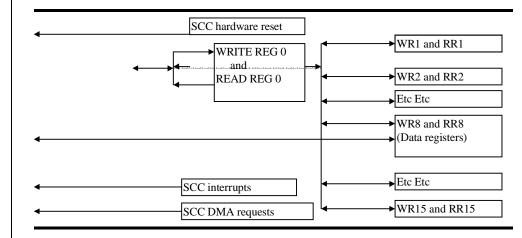

**Chapter 15**, **"Serial Ports**," provides an operational overview on the RC36100's two independent serial port channels and includes a block diagram, register descriptions and pin definitions.

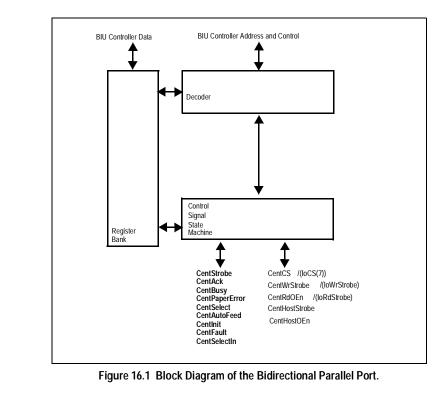

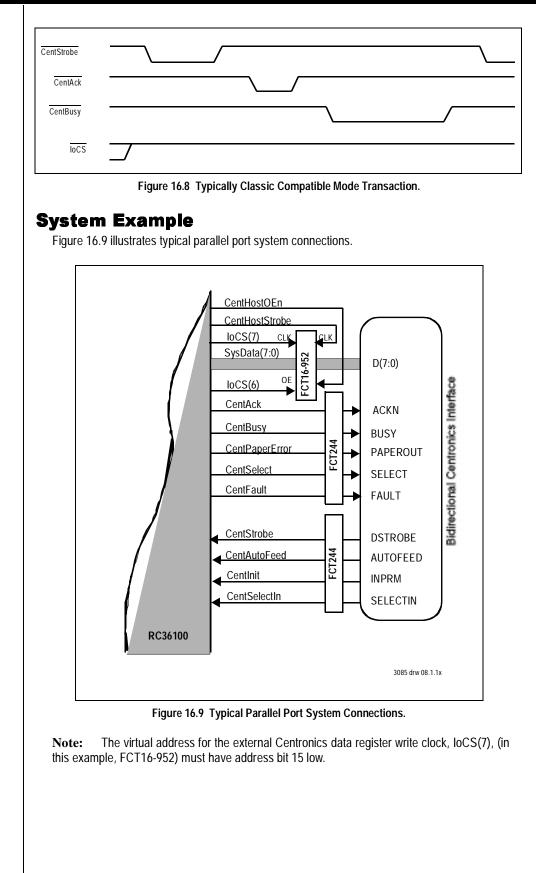

**Chapter 16**, **"Bidirectional Parallel Port**," explains the interfacing functions of the bidirectional parallel port and provides information on the various modes and options available. Register definitions and a system connection example are also included.

**Chapter 17**, **"Reset Initialization and Input Clocking**," details the RC36100's initialization selectable features and discusses the processor's required reset sequence.

**Chapter 18**, "**Debug Mode Features**," describes features that have been included to facilitate the debugging of RC36100-based systems.

## **Where To Find More Product Information**

Details on this device's electrical interface can be found in the product's data sheet, which also includes packaging, pin-out, and ordering information.

For information on development tools and how to use this product in various applications, refer to IDT's on-line library of data sheets, application notes, evaluation board manuals, software reference manuals, and the IDT Advantage Program Guides.

Your local IDT sales representative can help you identify and use any of these resources.

## **Table of Contents**

| RC36100 Device Overview                                            | Chapter 1  |

|--------------------------------------------------------------------|------------|

| RC36100 Features List                                              |            |

| Device Overview                                                    | 1-3        |

| CPU Core                                                           | 1-3        |

| System Control Co-Processor                                        | 1-3        |

| Clock Generator Unit                                               | 1-3        |

| Instruction Cache                                                  | 1-3        |

| Data Cache                                                         | 1-4        |

| Bus Interface Unit                                                 | 1-4        |

| Memory Controller                                                  |            |

| DRAM Controller                                                    |            |

| I/O Controller                                                     |            |

| DMA Control and Interface                                          | 1-5        |

| Counter/Timers                                                     |            |

| PIO Interface                                                      |            |

| Serial Communications Controller                                   |            |

| Interrupt Controller                                               |            |

| IEEE 1284 Bidirectional Centronics                                 |            |

| Pin Information                                                    |            |

| Logic Symbol                                                       |            |

| Pin Descriptions                                                   |            |

| System Usage                                                       |            |

| Development Support                                                |            |

| Performance Overview                                               |            |

| Instruction Set Architecture                                       |            |

| Introduction                                                       |            |

| Processor Features Overview                                        |            |

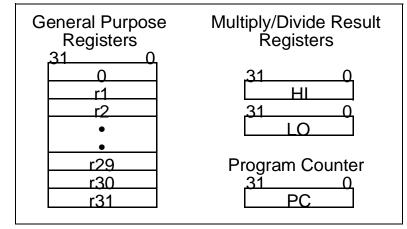

| CPU Registers Overview                                             |            |

| Instruction Set Overview                                           |            |

| Programming Model                                                  |            |

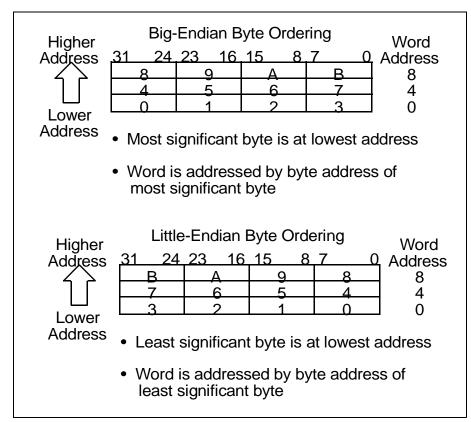

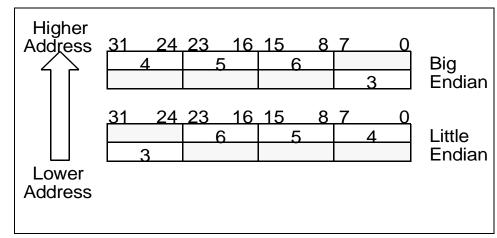

| Data Formats and Addressing                                        |            |

| CPU General Registers                                              |            |

| CP0 Special Registers                                              |            |

| Operating Modes                                                    |            |

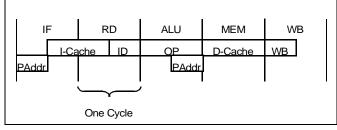

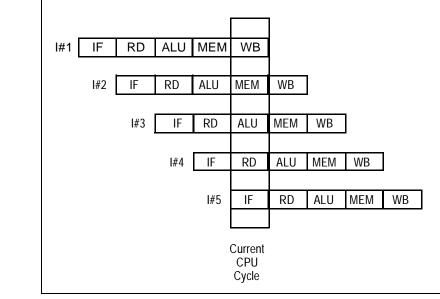

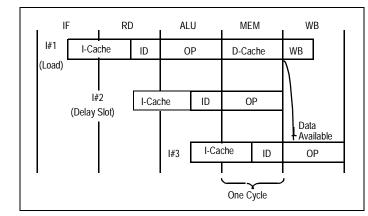

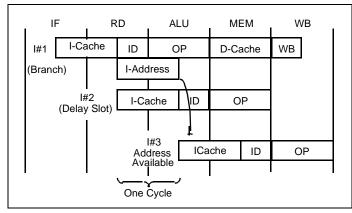

| Pipeline Architecture                                              |            |

| Pipeline Hazards                                                   |            |

| Instruction Set Summary                                            |            |

| Instruction Formats                                                |            |

| Instruction Notational Conventions                                 |            |

| Load and Store Instructions                                        |            |

| Big-Endian (32-bit memory system)                                  |            |

| Little-Endian (32-bit memory system)                               |            |

| Big-Endian (16-bit memory system)                                  |            |

| Little-Endian (16-bit memory system)<br>Computational Instructions |            |

| Jump and Branch instructions                                       |            |

| Special Instructions                                               |            |

| Co-processor Instructions                                          |            |

| System Control Co-processor (CP0) Instructions                     |            |

| RC36100 Opcode Encoding                                            |            |

|                                                                    | ····· ∠-∠1 |

| Cache Architecture                                                                                                               | •     |

|----------------------------------------------------------------------------------------------------------------------------------|-------|

| Fundamentals of Cache Operation                                                                                                  |       |

| RC36100 Cache Organization                                                                                                       |       |

| Basic Cache Operation                                                                                                            |       |

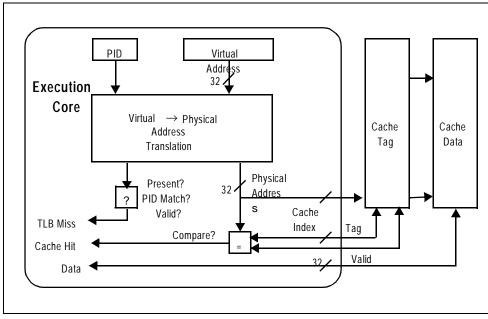

| Memory Address to Cache Location Mapping                                                                                         |       |

| Cache Addressing                                                                                                                 |       |

| Write Policy                                                                                                                     |       |

| Partial Word Writes                                                                                                              |       |

| Instruction Cache Line Size                                                                                                      |       |

| Data Cache Line Size                                                                                                             |       |

| Summary                                                                                                                          |       |

| Cache Operation                                                                                                                  |       |

| Basic Cache Fetch Operation                                                                                                      |       |

| Cache Miss Processing                                                                                                            |       |

| Instruction Streaming                                                                                                            |       |

| Cacheable References                                                                                                             |       |

| Software Directed Cache Operations                                                                                               |       |

| Cache Sizing                                                                                                                     |       |

| Cache Flushing                                                                                                                   |       |

| Forcing Data into the Caches                                                                                                     |       |

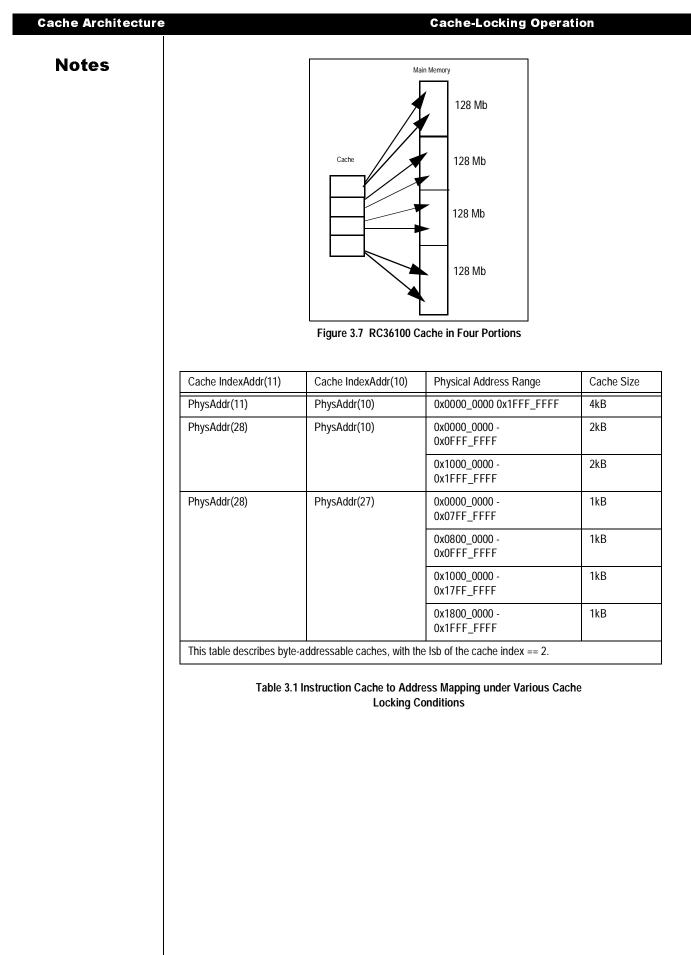

| Cache-Locking Operation                                                                                                          |       |

| Summary                                                                                                                          |       |

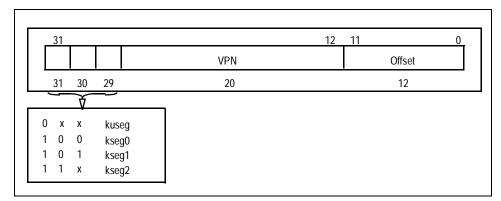

| Virtual-to-Physical Address Translation and Address Map                                                                          |       |

| Virtual Memory in the RISCore32 series Architecture                                                                              |       |

| Privilege States                                                                                                                 |       |

| User Mode Virtual Addressing                                                                                                     |       |

| Kernel Mode Virtual Addressing                                                                                                   |       |

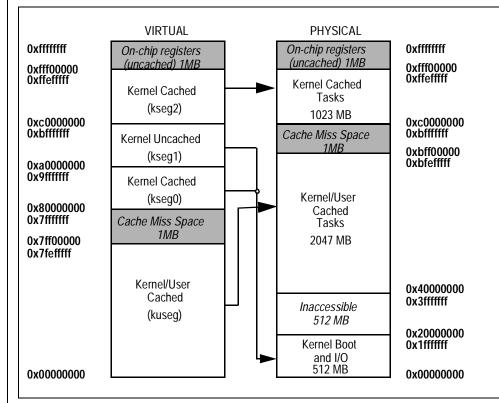

| RC36100 address translation                                                                                                      |       |

| On-Chip Registers                                                                                                                |       |

| Cache Miss Area                                                                                                                  |       |

| Summary                                                                                                                          |       |

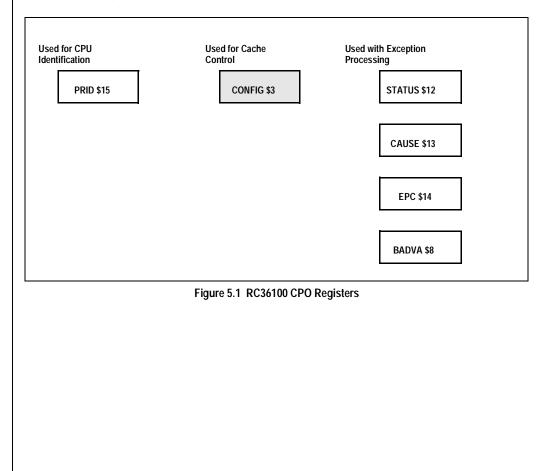

| Coprocessor 0 Register Set                                                                                                       |       |

| Introduction                                                                                                                     |       |

| Coprocessor 0 Bus Interface Control                                                                                              |       |

| Cache Configuration Register                                                                                                     |       |

| Lock ('Lock')                                                                                                                    |       |

| Reserved-High ('1')                                                                                                              |       |

| Reserved-Low ('0')                                                                                                               |       |

| DBlockRefill ('DBR')                                                                                                             |       |

| D-CacheIndexControl ('DCI')                                                                                                      |       |

| Halt Mode ('Halt')                                                                                                               |       |

| I-CacheIndexControl ('ICI')                                                                                                      |       |

| ReduceFrequency ('RF')                                                                                                           |       |

| ForceDCacheMiss ('FDCM')                                                                                                         |       |

| ForcelCacheMiss ('FICM')                                                                                                         |       |

| DCacheWriteDisable('DWrD')                                                                                                       |       |

| I-CacheWriteDisable ('IWrD')                                                                                                     |       |

| I-Gaulewhiedisable (TWID)                                                                                                        |       |

|                                                                                                                                  |       |

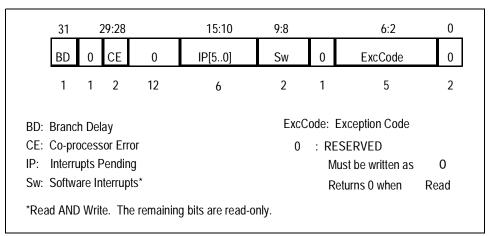

| The Cause Register                                                                                                               |       |

| The Cause Register<br>The EPC (Exception Program Counter) Register                                                               |       |

| The Cause Register<br>The EPC (Exception Program Counter) Register<br>Bad VAddr Register                                         |       |

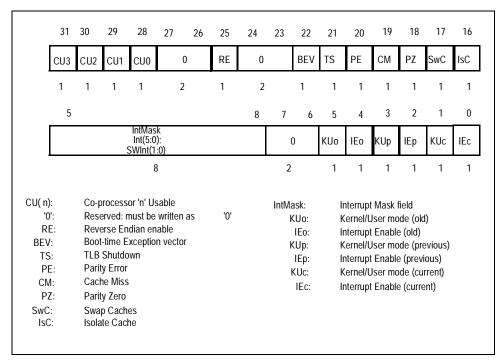

| The Cause Register<br>The EPC (Exception Program Counter) Register<br>Bad VAddr Register<br>The Status Register                  |       |

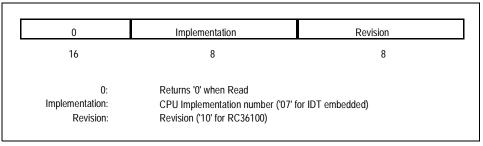

| The Cause Register<br>The EPC (Exception Program Counter) Register<br>Bad VAddr Register<br>The Status Register<br>PRId Register |       |

| The Cause Register<br>The EPC (Exception Program Counter) Register<br>Bad VAddr Register<br>The Status Register                  | 5<br> |

|  | Tab | e of | Con | tents |

|--|-----|------|-----|-------|

|--|-----|------|-----|-------|

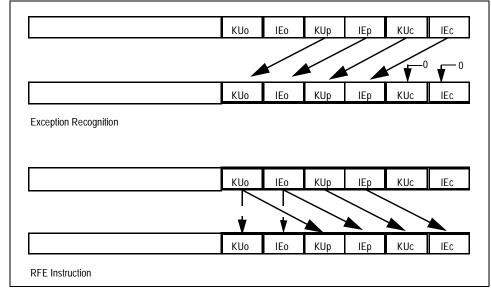

|       | Precise vs. Imprecise Exceptions                  | 6-2  |

|-------|---------------------------------------------------|------|

| Notes | Exception Processing                              |      |

|       | Exception Handling Registers                      |      |

|       | The Cause Register                                | 6-3  |

|       | The EPC (Exception Program Counter) Register      |      |

|       | Bad VAddr Register                                |      |

|       | The Status Register                               |      |

|       | Exception Vector Locations                        |      |

|       | Exception Prioritization                          | 6-6  |

|       | Exception Latency                                 |      |

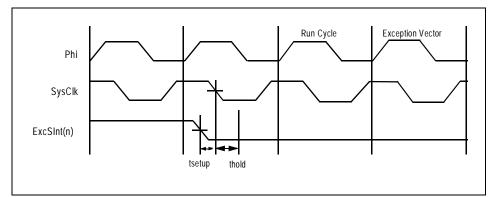

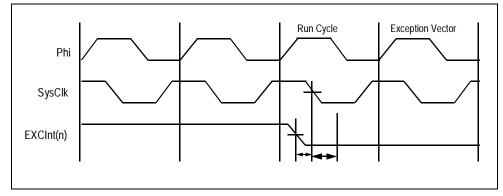

|       | Interrupts Inputs in the RC36100                  | 6-8  |

|       | Interrupt Operation in the RC36100                | 6-8  |

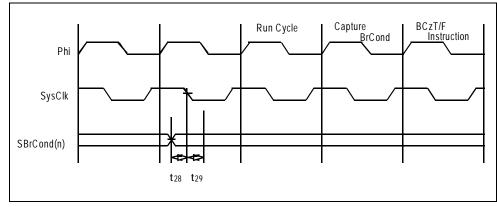

|       | Using the BrCond Inputs                           | 6-9  |

|       | Interrupt Handling                                | 6-10 |

|       | Interrupt Servicing                               | 6-11 |

|       | Basic Software Techniques For Handling Interrupts | 6-11 |

|       | Preserving Context                                | 6-12 |

|       | Examining Exception                               | 6-13 |

|       | Returning From Exceptions                         | 6-14 |

|       | Special Techniques                                | 6-15 |

|       | Interrupt Masking                                 | 6-15 |

|       | Using BrCond For Fast Response                    | 6-15 |

|       | Cache Locking                                     | 6-17 |

|       | Nested Interrupts                                 |      |

|       | Catastrophic Exceptions                           |      |

|       | Handling Specific Exceptions                      |      |

|       | Address Error Exception                           |      |

|       | Cause                                             |      |

|       | Handling                                          |      |

|       | Servicing                                         |      |

|       | Breakpoint Exception                              |      |

|       | Cause                                             |      |

|       | Handling                                          |      |

|       | Service                                           |      |

|       | Bus Error Exception                               |      |

|       | Cause<br>Handling                                 |      |

|       | Servicing                                         |      |

|       | Co-processor Unusable Exception                   |      |

|       | Cause                                             |      |

|       | Handling                                          |      |

|       | Servicing                                         |      |

|       | Interrupt Exception                               |      |

|       | Cause                                             |      |

|       | Handling                                          |      |

|       | Servicing                                         |      |

|       | Overflow Exception                                |      |

|       | Cause                                             |      |

|       | Handling                                          |      |

|       | Servicing                                         |      |

|       | Reserved Instruction Exception                    |      |

|       | Cause                                             |      |

|       | Handling                                          | 6-21 |

|       | Servicing                                         | 6-21 |

|       | Reset Exception                                   |      |

|       | Cause                                             | 6-22 |

|       |                                                   |      |

| Handling                                |  |

|-----------------------------------------|--|

| Servicing                               |  |

| System Call Exception                   |  |

| Cause                                   |  |

| Handling                                |  |

| Servicing                               |  |

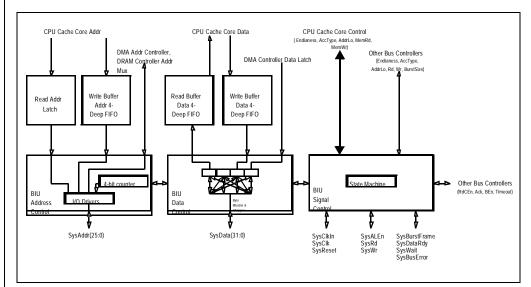

| System Bus Interface Unit Overview      |  |

| Introduction                            |  |

| Bus Interface Overview                  |  |

| Pin Description                         |  |

| System Bus Interface Signals            |  |

| Clock and Reset Signals                 |  |

| Bus Interface Control Signals           |  |

| CPU Core Transaction Types              |  |

| Read Operation                          |  |

| Write Operations                        |  |

| Multiple Operations                     |  |

| Execution Engine Fundamentals           |  |

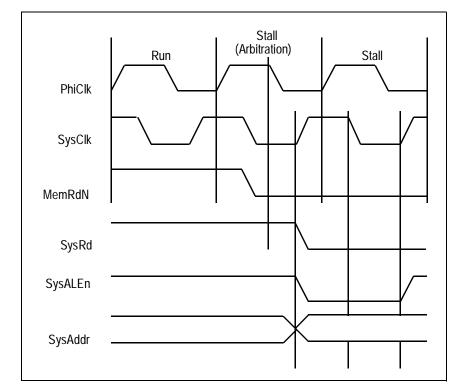

| Execution Core Cycles                   |  |

| Cycles                                  |  |

| Run Cycles                              |  |

| Stall Cycles                            |  |

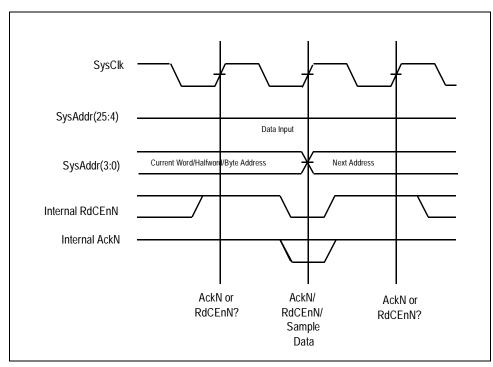

| Internal Acknowledgment                 |  |

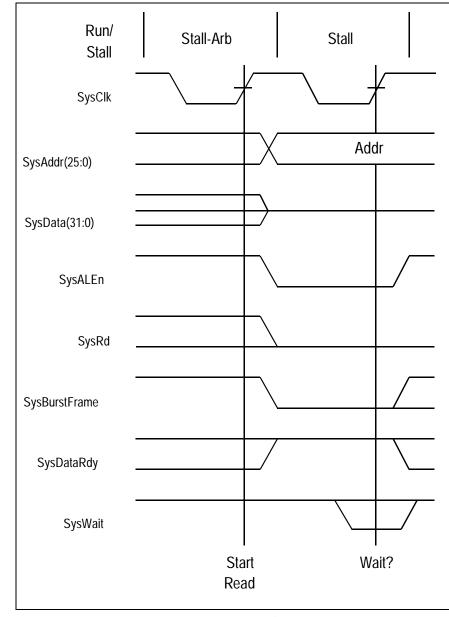

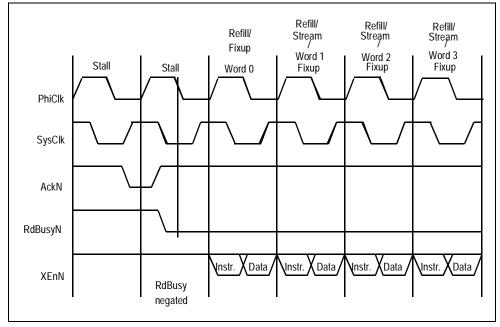

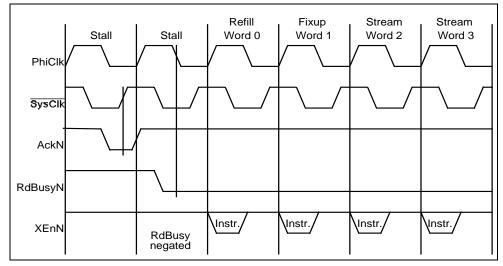

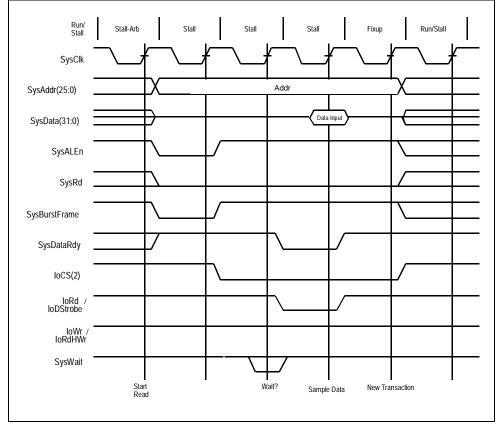

| Read Interface Timing Overview          |  |

| Initiation of a Read Request            |  |

| Memory Addressing                       |  |

| Initiation of the Data Phase            |  |

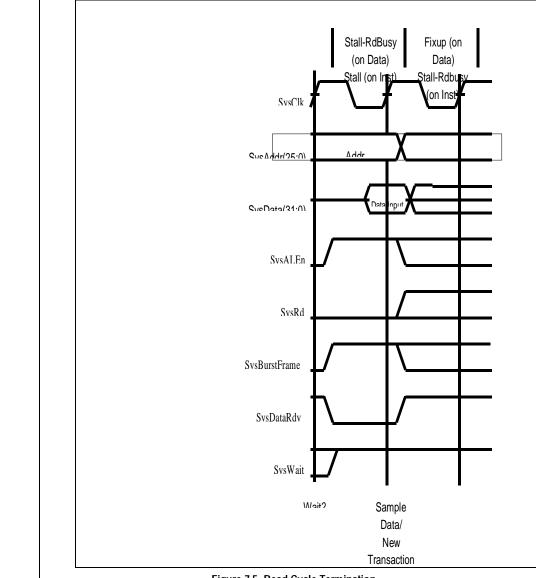

| Bringing Data into the Processor        |  |

| Terminating the Read                    |  |

| Latency Between Processor Operations    |  |

| Processor Internal Activity             |  |

| The Write Interface                     |  |

| Importance of Writes in RC36100 Systems |  |

| Types of Write Transactions             |  |

| 32-Bit Write Transactions               |  |

| 16-Bit Transactions                     |  |

| 8-Bit Transactions                      |  |

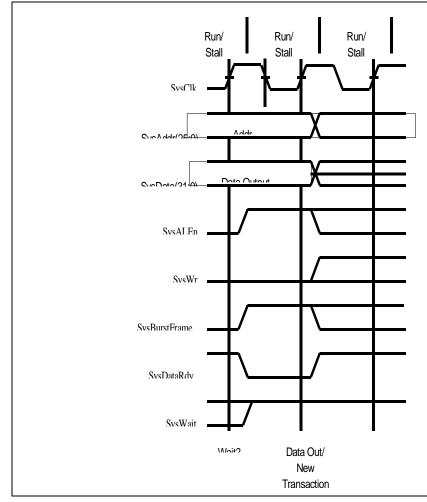

| Write Interface Timing Overview 7-16    |  |

| Initiating the Write                    |  |

| Memory Addressing                       |  |

| The Data Phase                          |  |

| Terminating the Write                   |  |

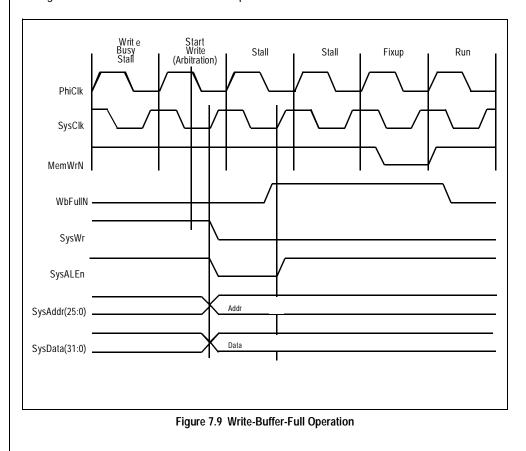

| Write Buffer Full Operation             |  |

| Memory Controller                       |  |

| Introduction                            |  |

| Features                                |  |

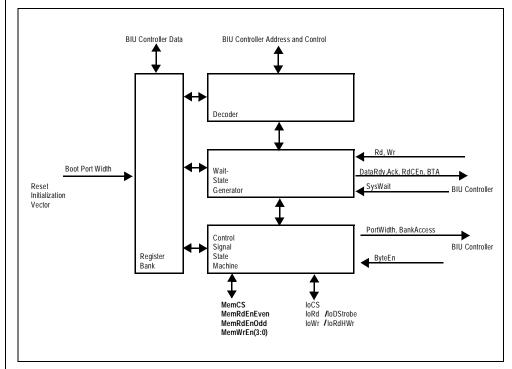

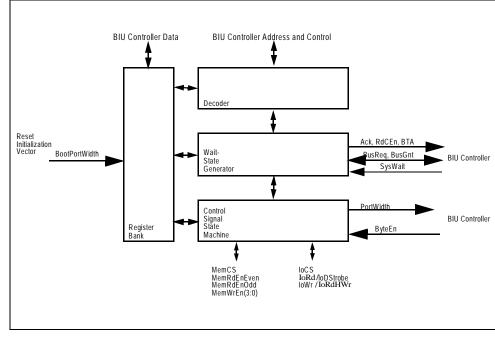

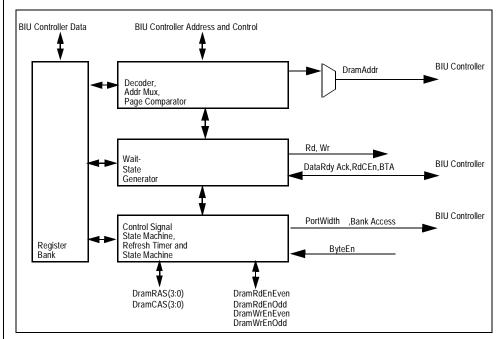

| Block Diagram                           |  |

| Memory Controller Signals               |  |

| BIU Controller Signals                  |  |

| Memory Controller Overview              |  |

| Chip Selects                            |  |

| Transceiver Control Interface           |  |

| Wait-State Generator                    |  |

| Register Option Programmability         |  |

| Register Descriptions                   |  |

|                                         |  |

| Table of Contents | Table                                                                              | e of Contents |

|-------------------|------------------------------------------------------------------------------------|---------------|

|                   | Memory MSB Base Address Register for Bank 70                                       |               |

| Notes             | ('MemMSBBaseAddrReg(70)') and Memory LSB Base Address Register for Ban             | uk 7 0        |

| NULES             | ('MemLSBBaseAddrReg(7.0)')                                                         |               |

|                   | Memory MSB Bank Mask Register for Bank 70 ('MemMSBBankMaskReg(70)'),               |               |

|                   | and Memory LSB Bank Mask Register for Bank 70                                      | 1             |

|                   | ('MemLSBBankMaskReg(7.0)')                                                         | 0 0           |

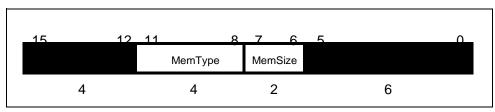

|                   | Memory and I/O Control Register for Bank 70.                                       | 0-0           |

|                   | ('MemControlReg(70)')                                                              | Q 10          |

|                   | Port Size Width ('MemSize') Field                                                  | 0-10          |

|                   | Memory LSB Wait-State Register for Bank 70                                         |               |

|                   | ('MemLSBWaitStateReg(7.0)')                                                        | 0 11          |

|                   | Read Start Cycle to the First Datum ('RdStart2Datum') Field:                       |               |

|                   | Write Start Cycle to the First Datum ('WrStart2Datum') Field:                      |               |

|                   | Read Datum to Datum ('RdDatum2Datum') Field:                                       |               |

|                   | Write Datum to Datum ('WrDatum2Datum') Field:                                      |               |

|                   | Memory MSB Wait-State Register for Bank 70                                         | 0-12          |

|                   |                                                                                    | 0 1 2         |

|                   | ('MemMSBWaitStateReg(70)')<br>Repeat Start Bus Cycle State 0 ('StartRepeat') Field |               |

|                   | Start of Read to AckN on Burst Reads ('Start2BurstAck') Field                      |               |

|                   | Byte Enables on Reads ('BEn') Field                                                |               |

|                   | Read Cycle Bus Turn-Around ('RdBTA') Field                                         |               |

|                   | Formulas for Calculating Memory Controller Start2BurstAck Field Value              |               |

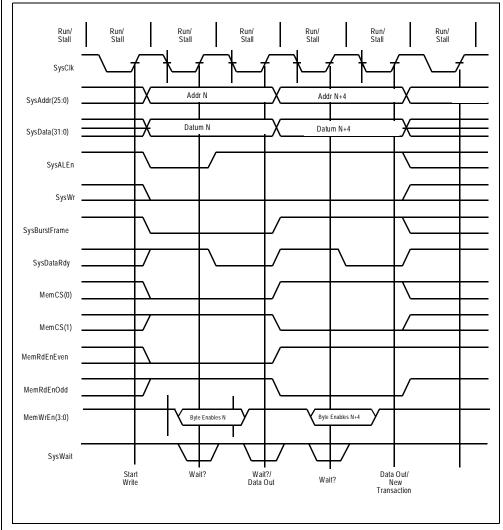

|                   | Memory Controller Timing Diagrams                                                  |               |

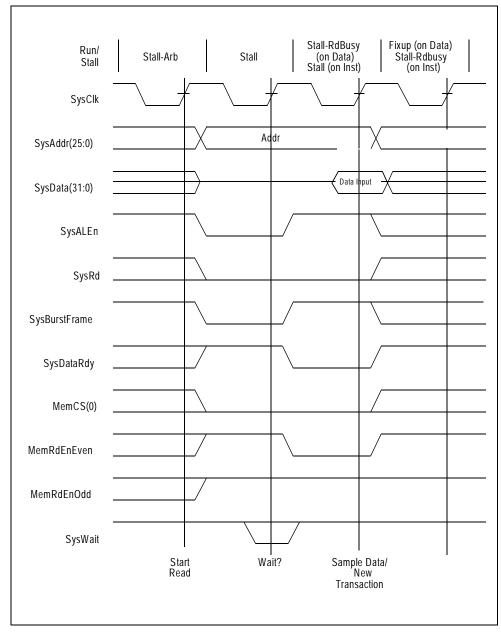

|                   | Read Transactions                                                                  |               |

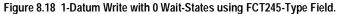

|                   | Basic 1-Datum Read with 0 Wait-States                                              |               |

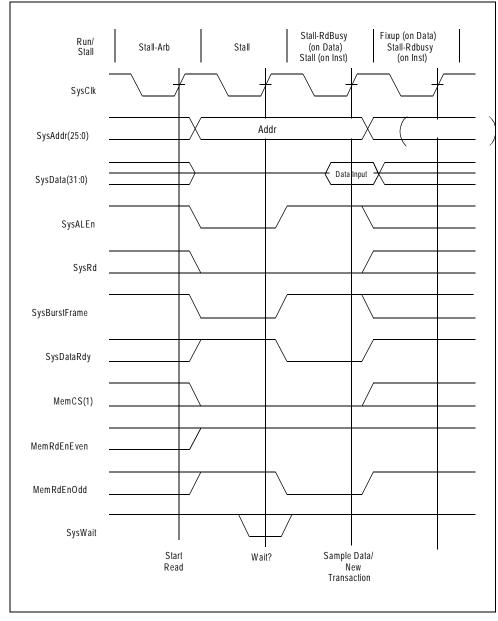

|                   | 1-Datum Read with 0 Wait-States using Odd Chip Select                              |               |

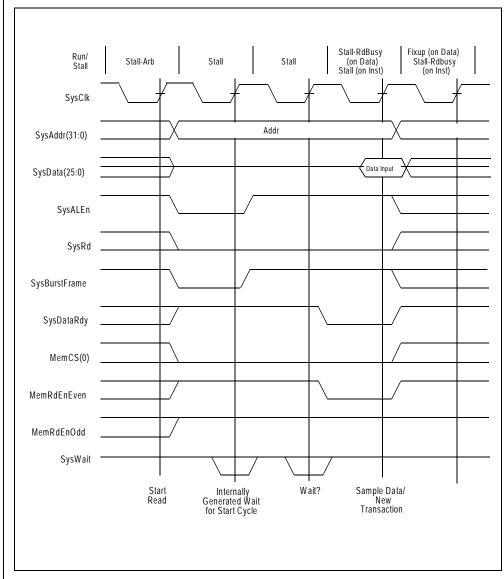

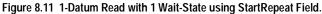

|                   | Read with Wait-State using Start Repeat Field                                      |               |

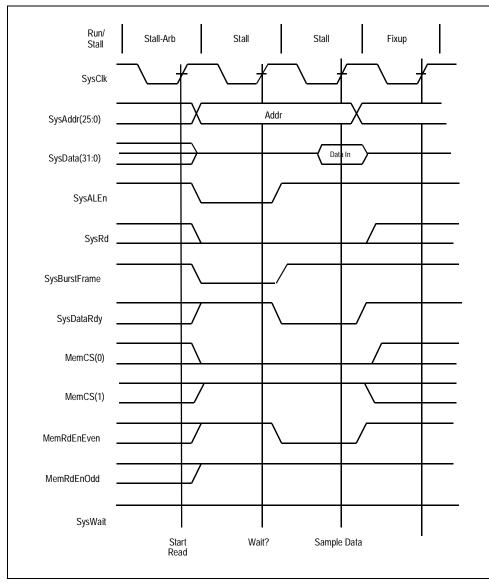

|                   | Read with Wait-State using RdStart2Datum Field                                     |               |

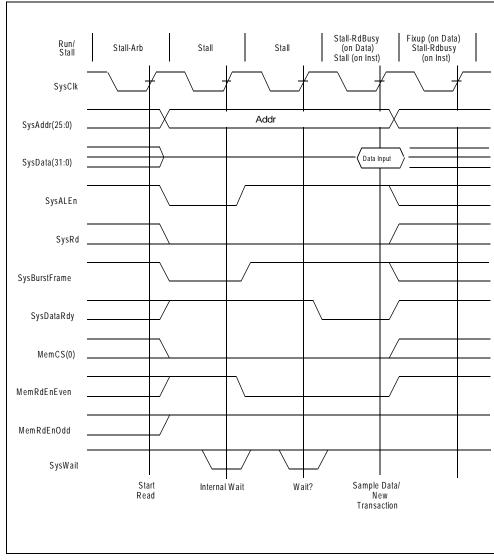

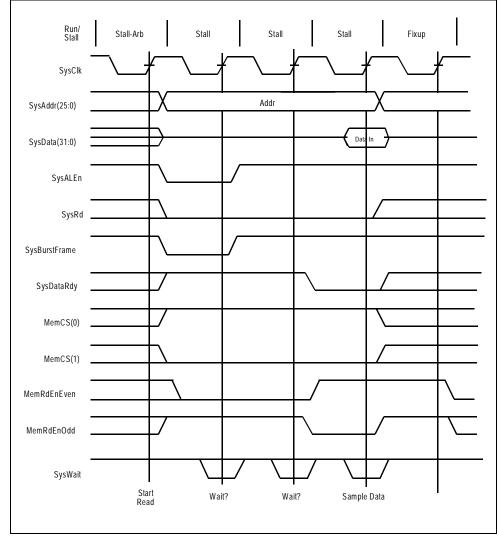

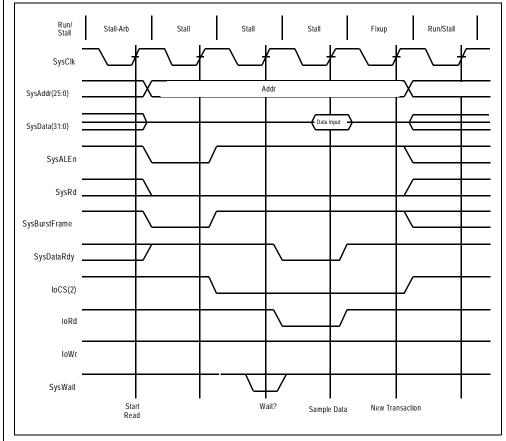

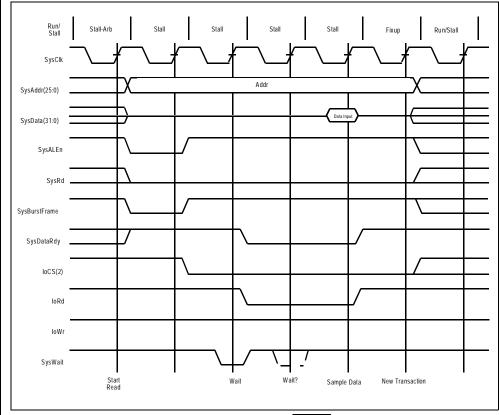

|                   | Read with Wait-State using SysWait                                                 |               |

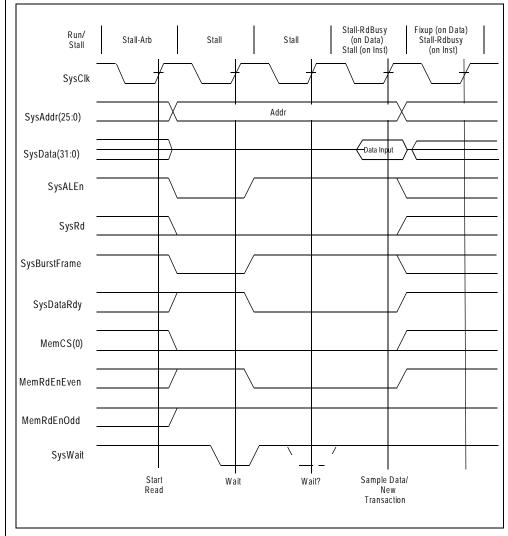

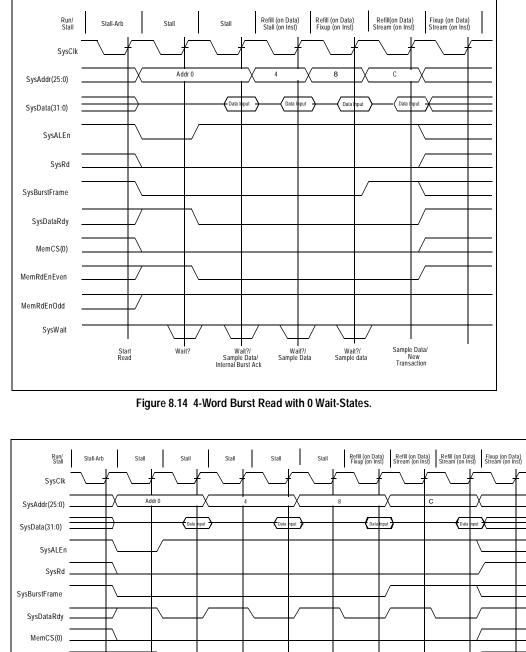

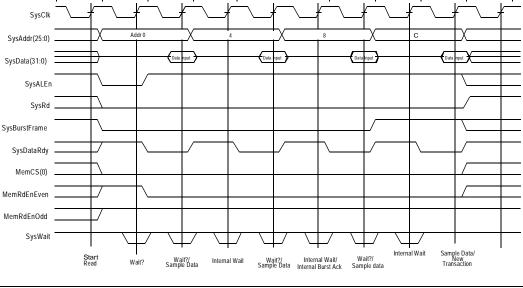

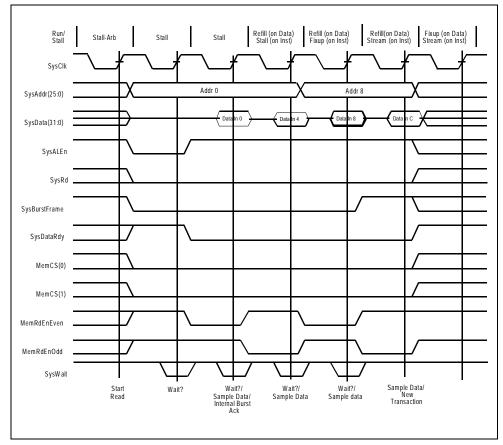

|                   | 4-Word Burst Read with 0 Wait-States                                               |               |

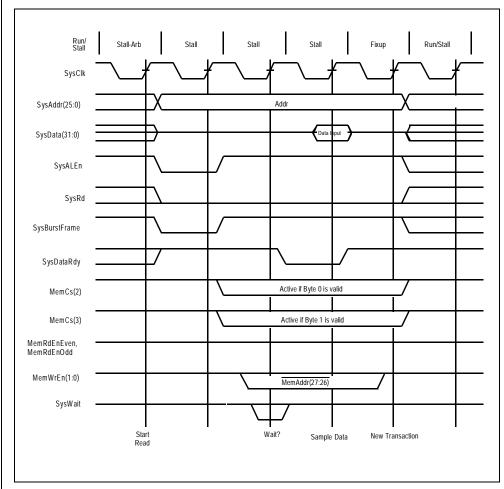

|                   | Basic 16-bit PCMCIA-style Memory Read with Zero Wait-States                        |               |

|                   | Write Transactions                                                                 |               |

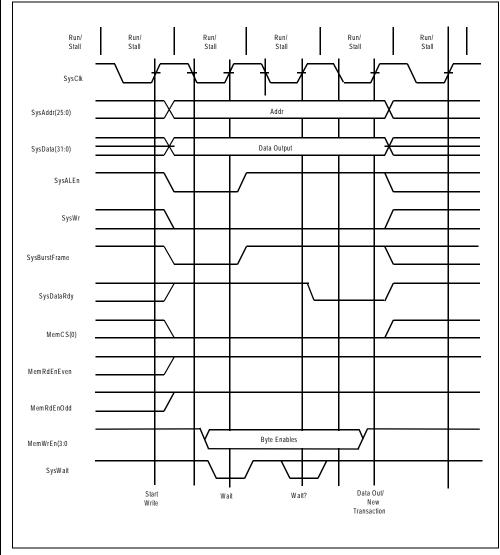

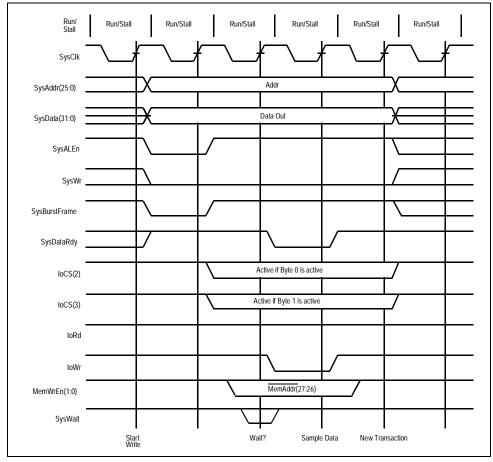

|                   | Single Datum Write                                                                 |               |

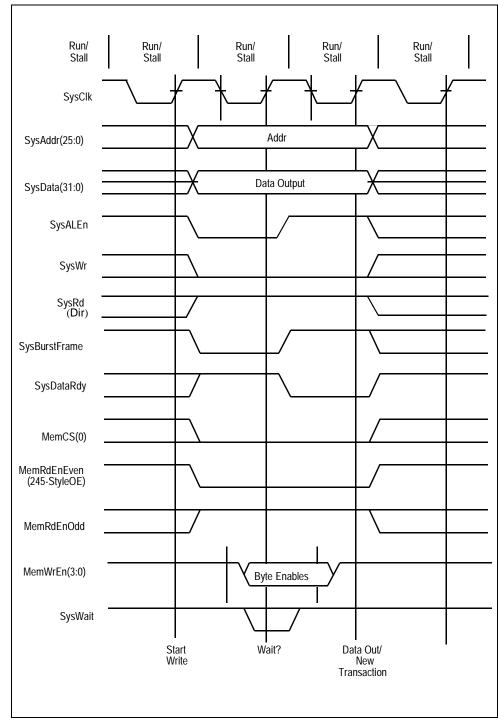

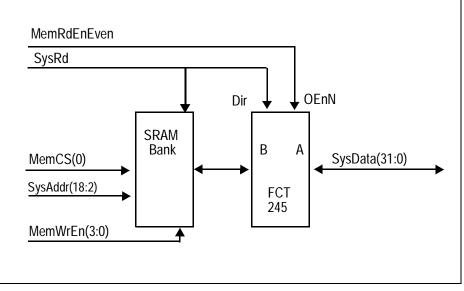

|                   | 1-Datum Write with 0 Wait-States using FCT245-Type Field                           |               |

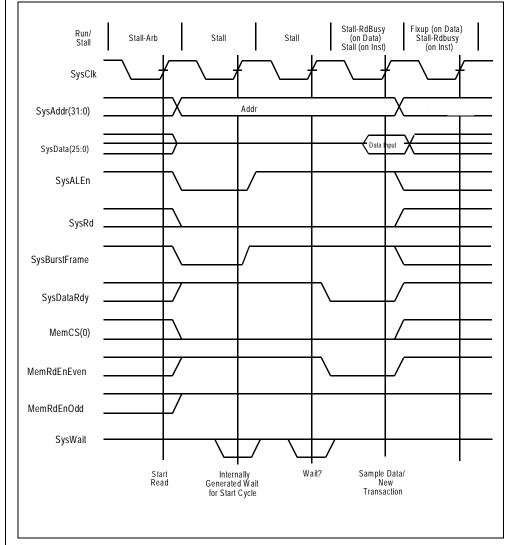

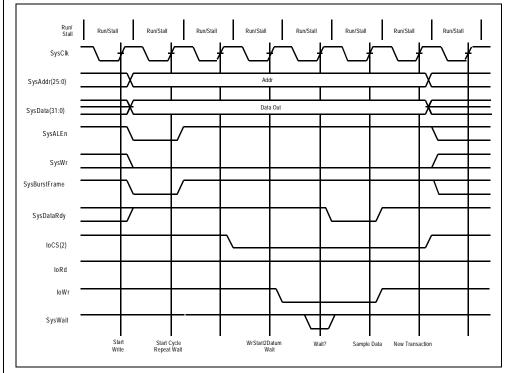

|                   | 1-Datum Write with Wait-State using StartRepeat Field                              |               |

|                   | 1-Datum Write with Wait-State using WrStart2Datum Field                            |               |

|                   | 1-Datum Write with Wait-State using SysWait                                        |               |

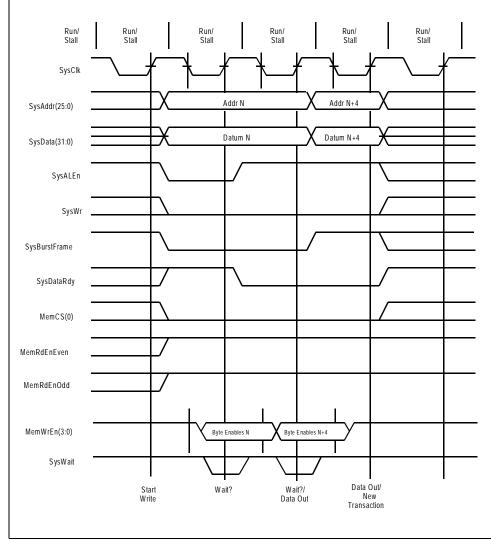

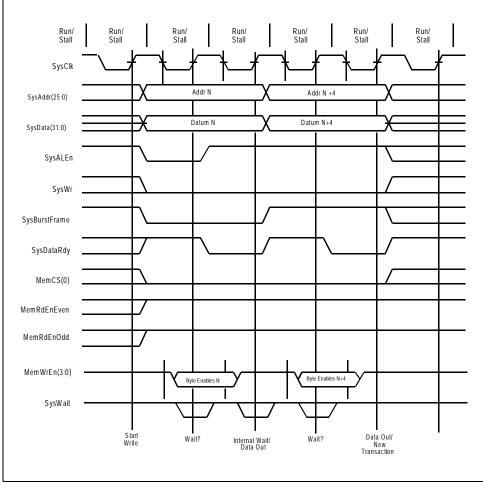

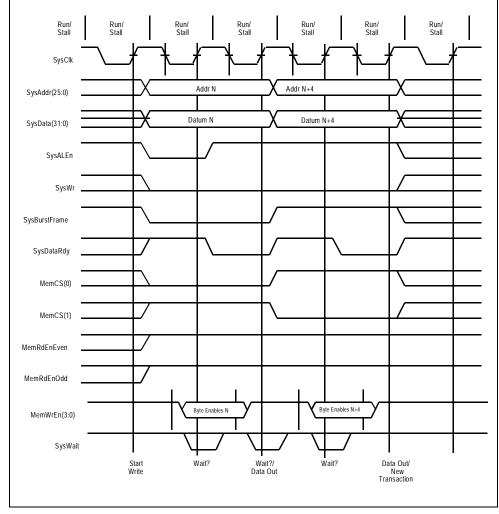

|                   | Multi-Datum Burst Write                                                            |               |

|                   | Multi-Datum Burst Write using Wait-State with WrDatum2Datum                        |               |

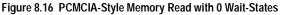

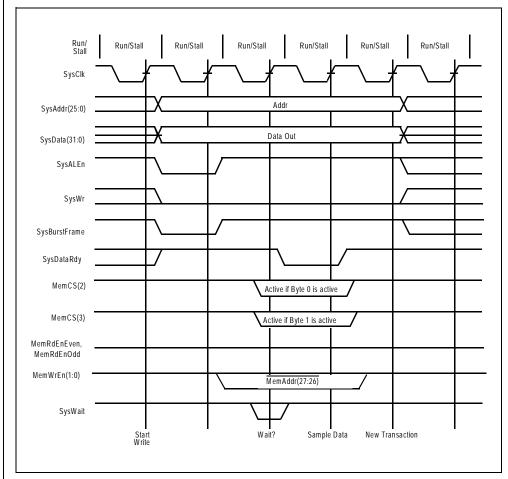

|                   | Basic PCMCIA-Type Memory Write with 0 Wait-States                                  |               |

|                   | Interleaved-Type Transactions                                                      |               |

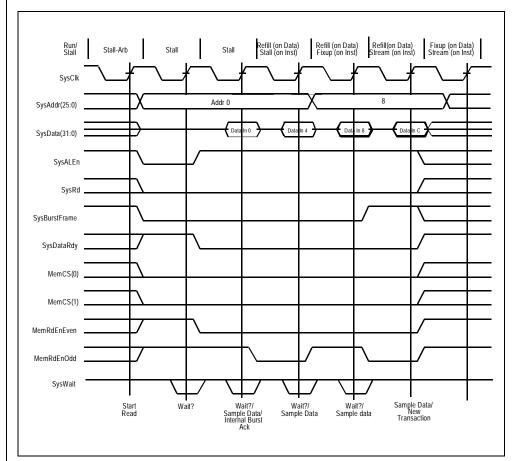

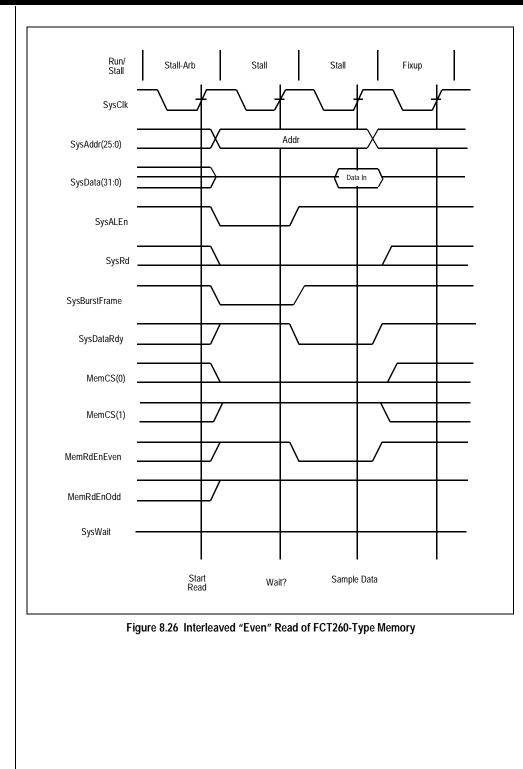

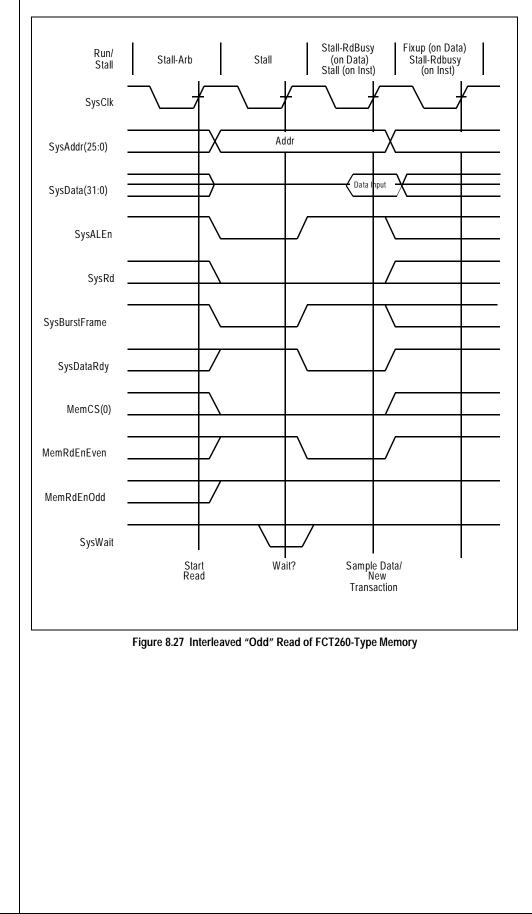

|                   | Interleaved Read using FCT260-Type Field                                           |               |

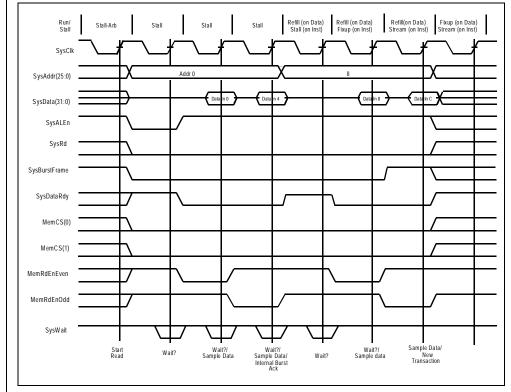

|                   | Interleaved Read using FCT543-Type Field                                           |               |

|                   | Interleaved Writes                                                                 |               |

|                   | System Examples.                                                                   |               |

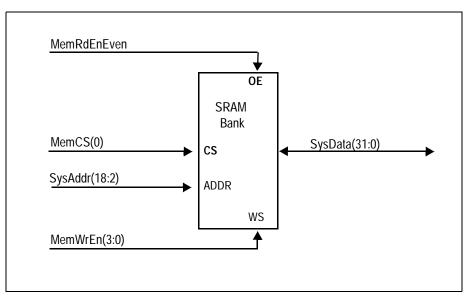

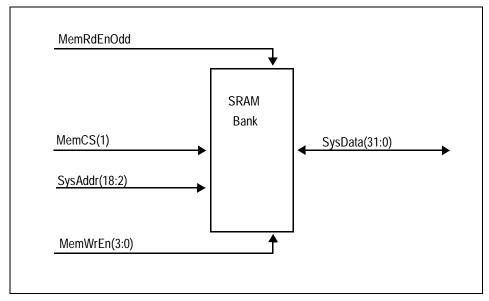

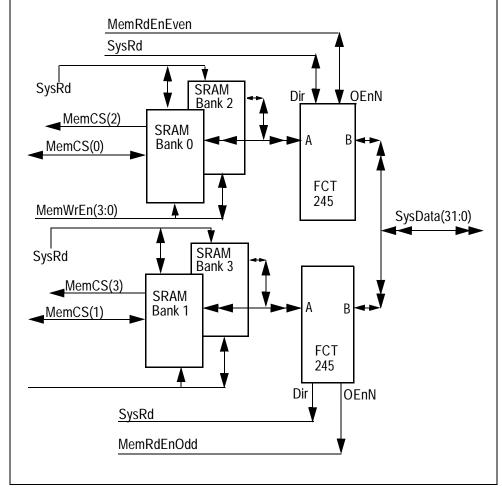

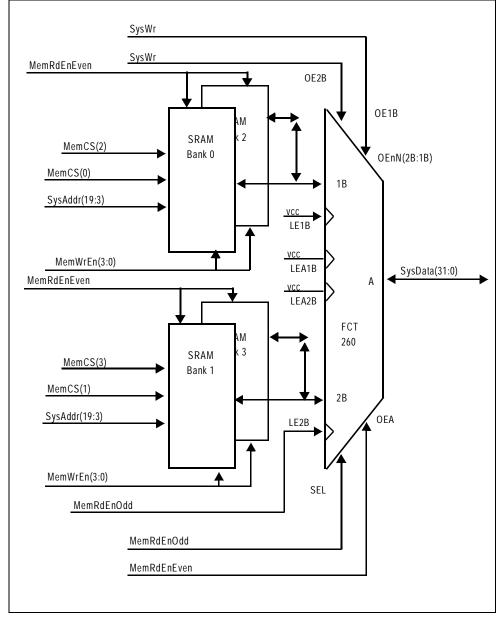

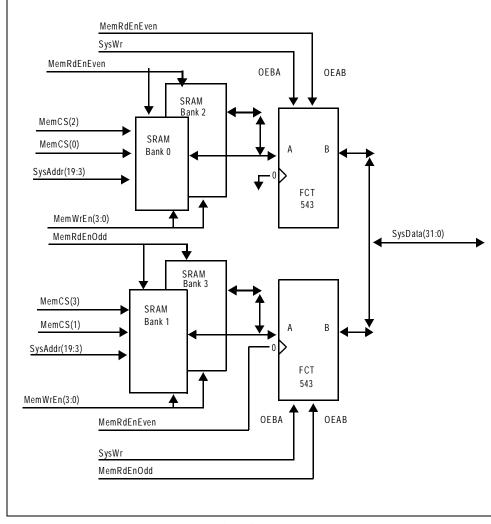

|                   | 32-bit SRAM using 245 Transceivers                                                 |               |

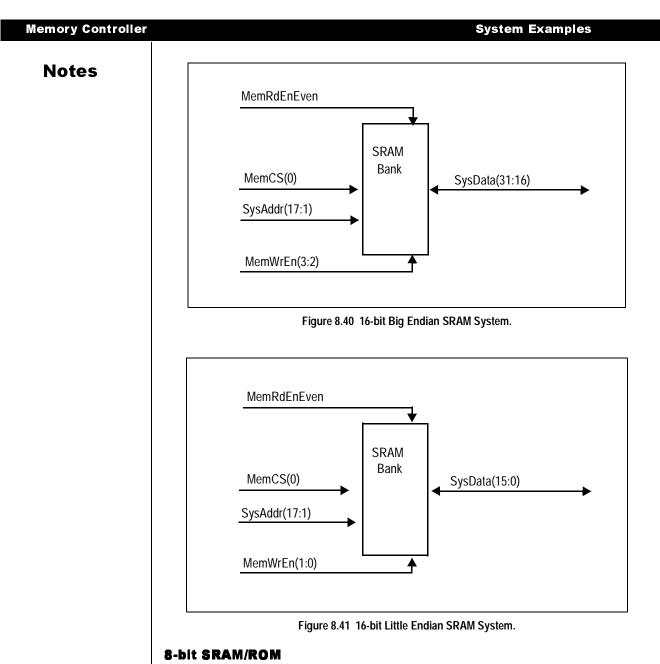

|                   | 16-bit SRAM/ROM                                                                    |               |

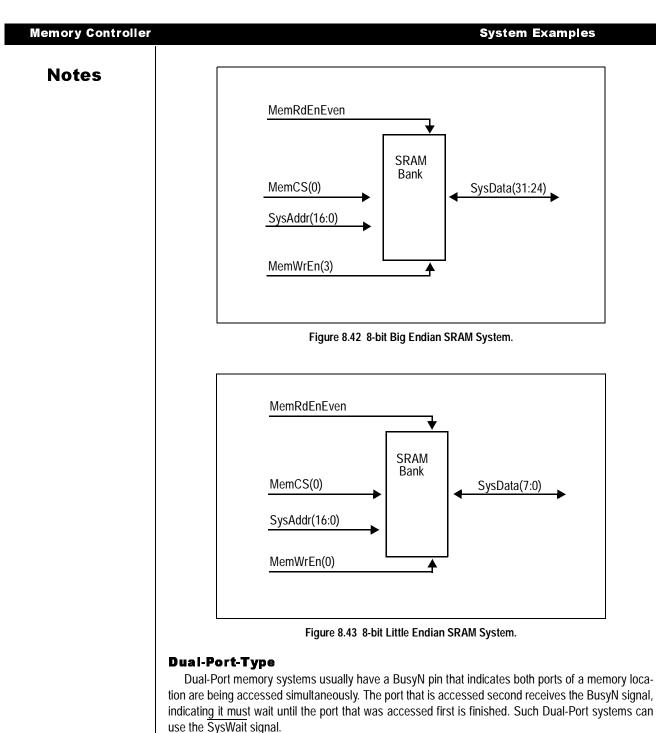

|                   | 8-bit SRAM/ROM                                                                     |               |

|                   | Dual-Port-Type                                                                     |               |

|                   | PCMCIA-Style Application                                                           |               |

|                   | I/O Controller                                                                     |               |

|                   | Introduction                                                                       |               |

|                   | Features                                                                           |               |

|                   |                                                                                    |               |

|                   | Block Diagram<br>I/O Bus Controller Interface Signals                              |               |

|                   | BIU Controller Signals                                                             |               |

|                   | טוט                                            |               |

|       | Overview of the I/O Controller                                                                  | . 9-4 |

|-------|-------------------------------------------------------------------------------------------------|-------|

| Notes | Chip Selects                                                                                    | . 9-4 |

|       | Signal Control Interface                                                                        | . 9-4 |

|       | Wait-State Generator                                                                            | . 9-5 |

|       | Register Option Programmability                                                                 | . 9-5 |

|       | Register Descriptions                                                                           | . 9-5 |

|       | Memory and I/O Control Register70                                                               |       |

|       | ('MemloCntrlReg(7.0)')                                                                          | . 9-7 |

|       | Memory Type ('MemType') Field                                                                   |       |

|       | Portsize Width ('MemSize') Field                                                                | . 9-7 |

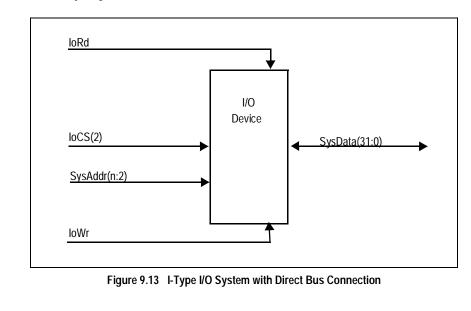

|       | I-Туре I/O Туре:                                                                                | . 9-8 |

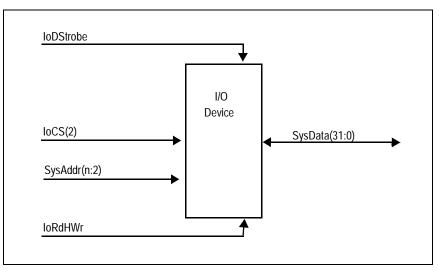

|       | М-Туре І/О Туре:                                                                                |       |

|       | PCMCIA-I/O Style:                                                                               |       |

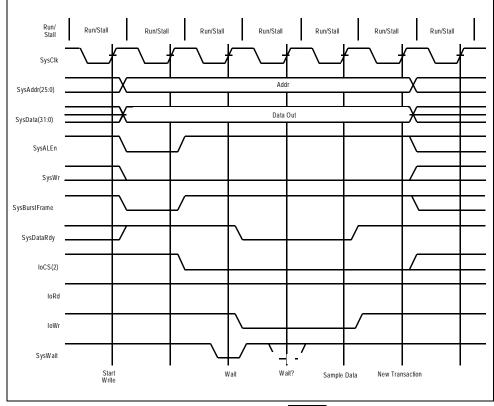

|       | I/O Controller Timing Diagrams                                                                  |       |

|       | I/O Datum Size                                                                                  |       |

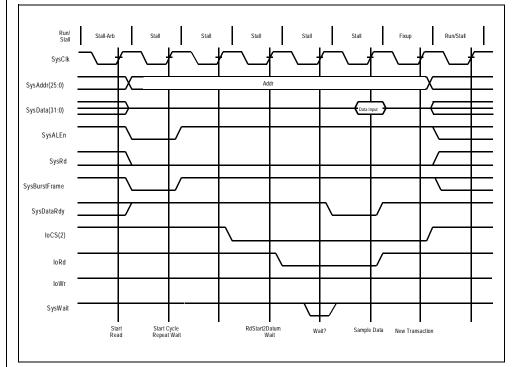

|       | Read Transactions                                                                               |       |

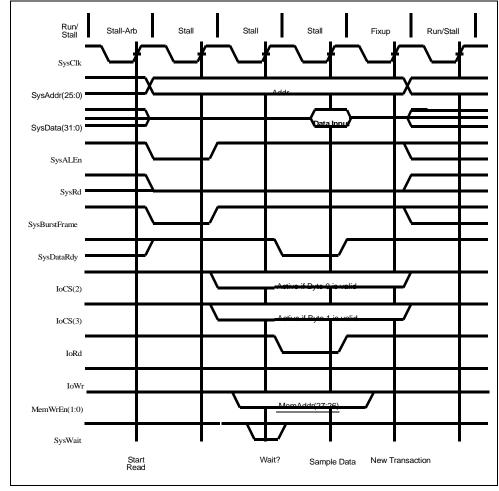

|       | Basic I-Type I/O Read with 0 Wait-States                                                        |       |

|       | Basic M-Type I/O Read with 0 Wait-States                                                        |       |

|       | Basic 16-bit PCMCIA-style I/O Read with 0 Wait-States                                           |       |

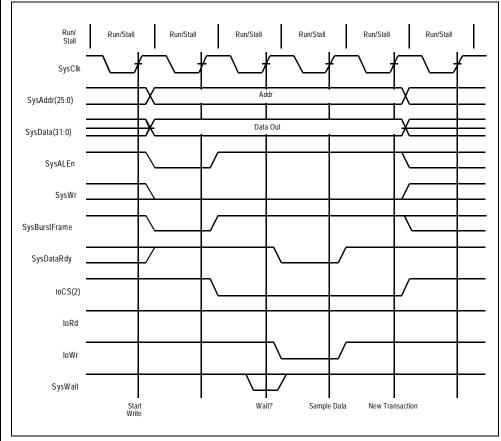

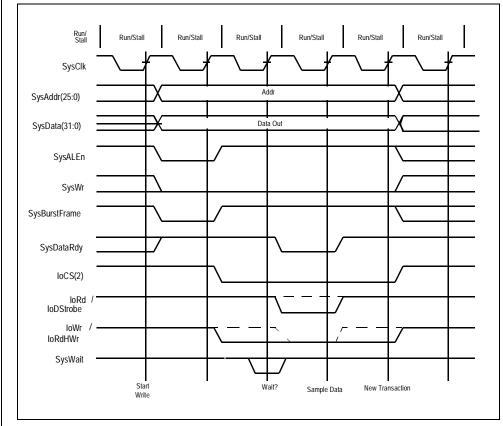

|       | Basic I-Type I/O Write with 0 Wait-States                                                       |       |

|       | Basic M-Type I/O Write with 0 Wait-States                                                       |       |

|       | Read with Wait-State using Start Repeat Field<br>Read with Wait-State using RdStart2Datum Field |       |

|       | Read with Wait-State using RustanzDatum Field                                                   |       |

|       | 1-Datum Write with Wait-State using Syswalt                                                     |       |

|       | 1-Datum Write with Wait-State using WrStart2Datum Field                                         |       |

|       | 1-Datum Write with Wait-State using SysWait                                                     |       |

|       | System Examples                                                                                 |       |

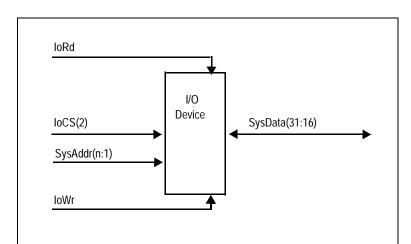

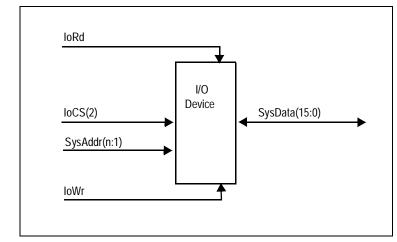

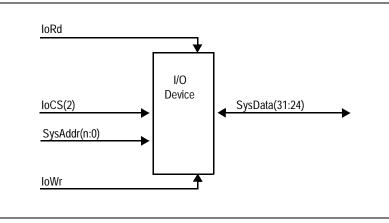

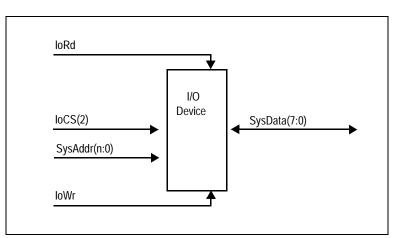

|       | 32-bit I/O Device Directly Connected to Bus                                                     |       |

|       | I/O Reset Application                                                                           |       |

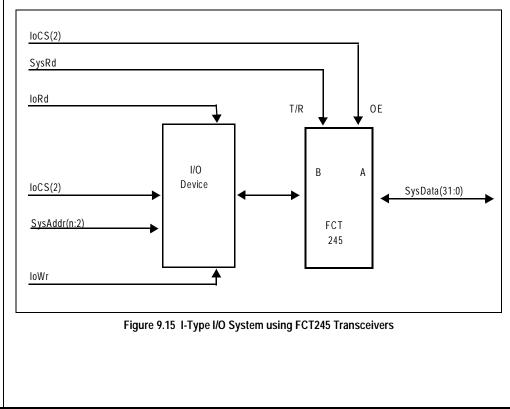

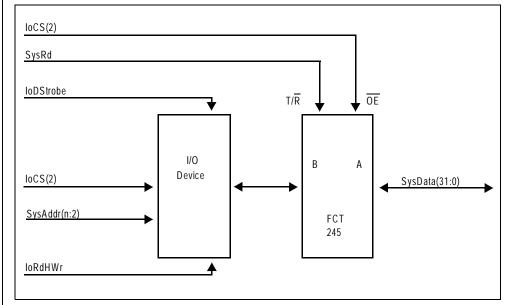

|       | 32-bit I/O Device using 245 Transceivers                                                        |       |

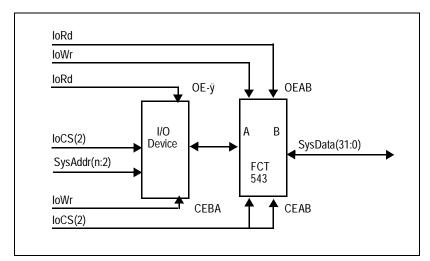

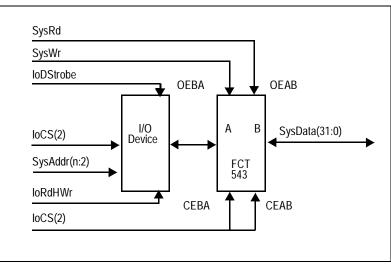

|       | 32-bit I/O Device using 543 Transceivers                                                        |       |

|       | Using more than one device behind each transceiver                                              |       |

|       | 16-bit I/O Devices                                                                              | 9-21  |

|       | 8-bit I/O Devices                                                                               | 9-22  |

|       | DRAM Controller Chapt                                                                           | er 10 |

|       | Introduction                                                                                    |       |

|       | Features                                                                                        | 10-1  |

|       | Block Diagram                                                                                   |       |

|       | DRAM Bus Controller Interface Signals                                                           |       |

|       | BIU Controller Signals                                                                          |       |

|       | Overview of the DRAM Controller                                                                 |       |

|       | Address mapping                                                                                 |       |

|       | 32-bit and 16-bit mode support                                                                  |       |

|       | Types of memory supported                                                                       |       |

|       | Programmable wait state generation<br>Page Comparator Algorithm                                 |       |

|       | Unaligned page accesses                                                                         |       |

|       | Refresh Timing                                                                                  |       |

|       | Initialization                                                                                  |       |

|       | Programmable features                                                                           |       |

|       | Signal Control Interface                                                                        |       |

|       | Wait State Generator                                                                            |       |

|       | Register Option Field Programmability                                                           |       |

|       | Register Descriptions                                                                           |       |

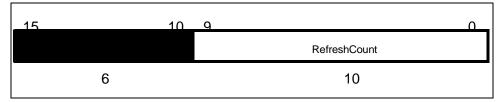

|       | DRAM Refresh Count Register ('DramRefreshCountReg')                                             |       |

|       |                                                                                                 |       |

|       | Staggered Refresh                                                                    | 10-8    |

|-------|--------------------------------------------------------------------------------------|---------|

| Notes | Refresh Arbitration                                                                  | 10-8    |

|       | Panic Mode Refresh Application                                                       | 10-8    |

|       | Reduced Frequency Mode Application                                                   | 10-8    |

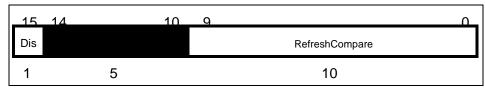

|       | DRAM Refresh Compare Register                                                        | 10-8    |

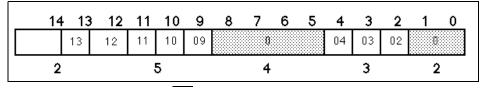

|       | DRAM RAS Multiplexer Select Register for Pair(1:0, 3:2)                              |         |

|       | ('DramRasMuxSelReg'1_0, 3_2)                                                         | . 10-10 |

|       | DRAM CAS Multiplexer Select Register for Pair (1:0, 3:2)                             |         |

|       | ('DramCasMuxSelReg'1_0, 3_2)                                                         | . 10-10 |

|       | DRAM MSB Bank Mask Register for Bank 03                                              |         |

|       | ('DramMSBBankMaskReg(0.3)')                                                          | . 10-14 |

|       | DRAM LSB Control Register for Bank 03                                                | 10.45   |

|       | ('DramLSBControlReg(03)')                                                            |         |

|       | RASPageMask ('RASPageMask') Field (bits 15:8)                                        |         |

|       | DRAM Type ('DramType') Field (bits 7:5)                                              |         |

|       | FCT543-Type (Latched Non-Multiplexer Type)                                           |         |

|       | FCT245 Type (Non-latched Transceiver Type)<br>FCT260-Type (Latched Multiplexer Type) |         |

|       | Port Size ('Size') Field (bits 4:3)                                                  |         |

|       | DRAM MSB Control Register for Bank 03                                                | . 10-17 |

|       | ('DramMSBControlReg'03)                                                              | 10-18   |

|       | RAS Precharge Period ('RASP') Field (bit 15:14)                                      |         |

|       | RAS Address Hold Time ('RASAddrHold') Field (bit 13)                                 |         |

|       | Address Setup Time to RAS and to CAS ('AddrSetup') Field (bit 12)                    |         |

|       | CAS Active Pulse Width ('CASW') Field (bit 11:10)                                    |         |

|       | DRAM Read Cycle Bus Turn-Around ('DramRdBTA') Field (bit 9:8)                        |         |

|       | DRAM Write Cycle Bus Turn Around ('DramWrBTA') Field (bit 6)                         |         |

|       | Burst Acknowledge Placement ('DramBurstAck') Field (bit 4:0)                         |         |

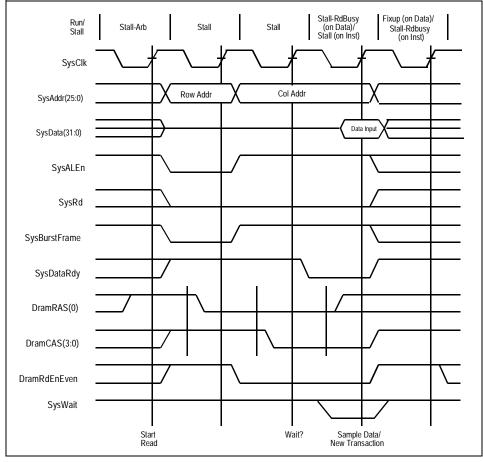

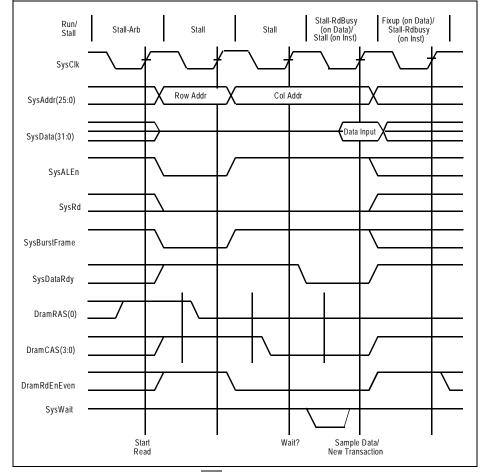

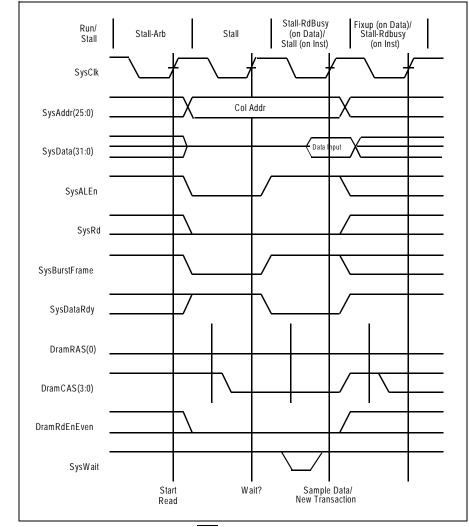

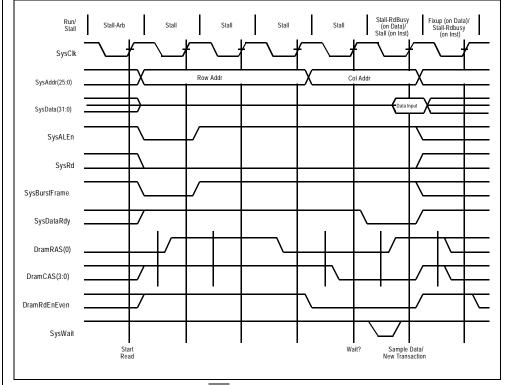

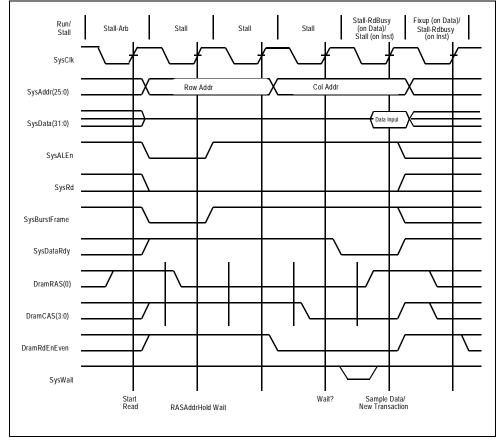

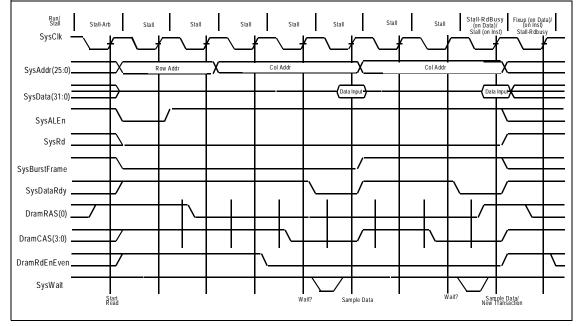

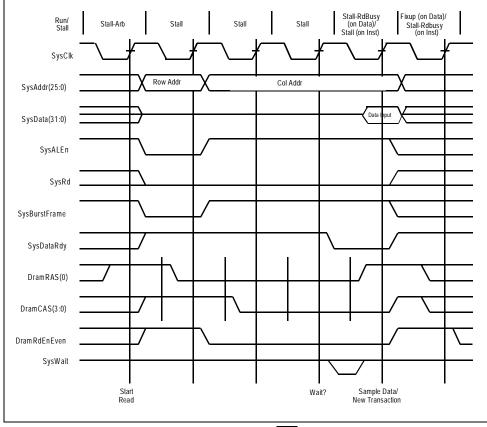

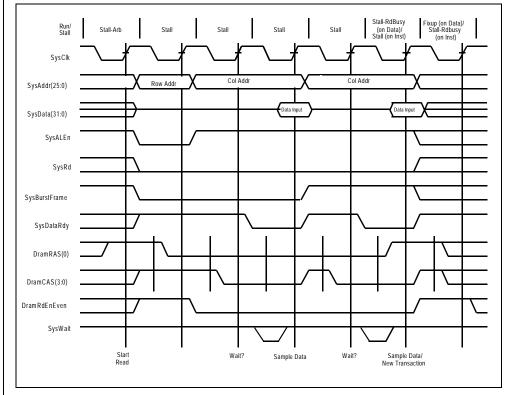

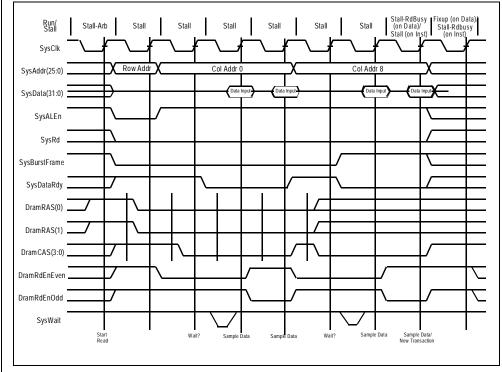

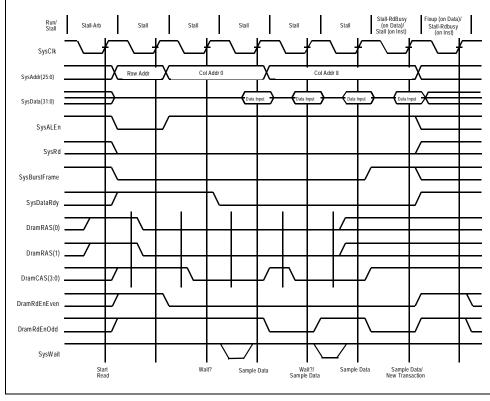

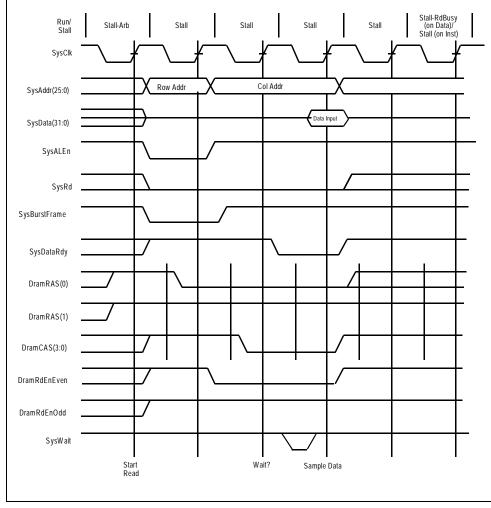

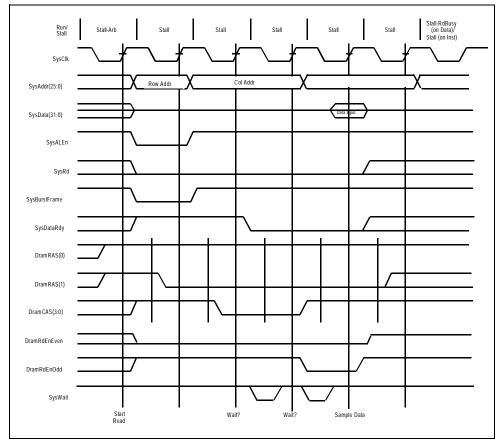

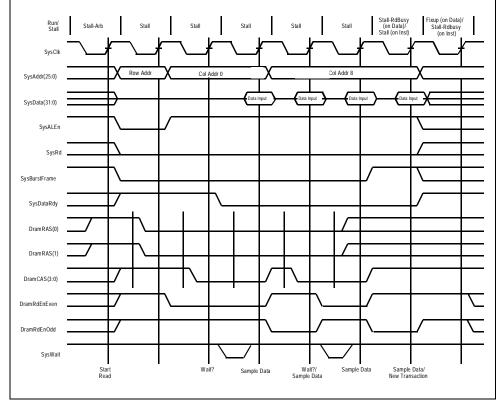

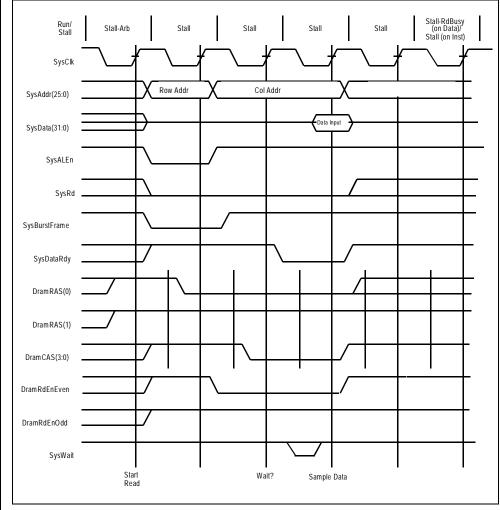

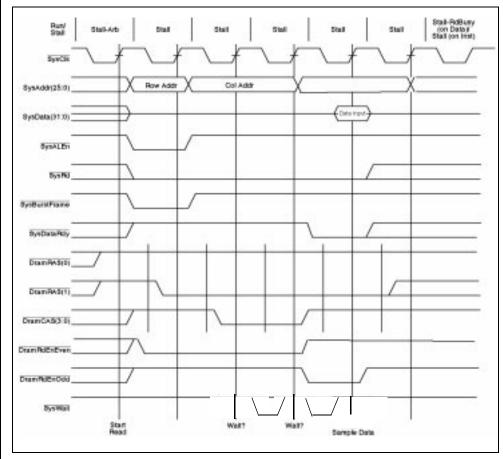

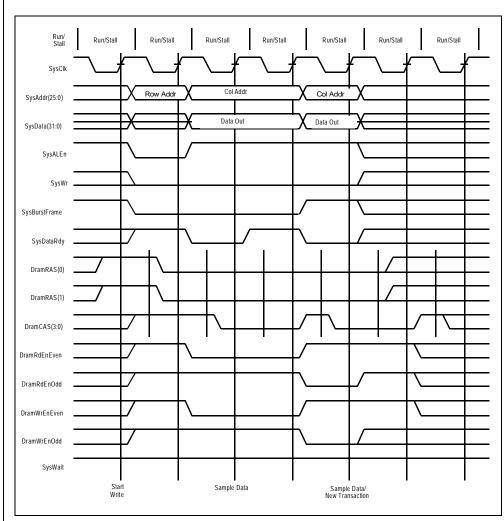

|       | Timing Diagrams                                                                      | . 10-21 |

|       | Standard DRAM Chip Summary                                                           |         |

|       | Basic New Page DRAM Read                                                             |         |

|       | RAS Asserted at End of Transfer                                                      |         |

|       | RAS Asserted at Start of Transfer                                                    |         |

|       | RAS Asserted Throughout Transfer                                                     |         |

|       | RAS Precharge Field                                                                  |         |

|       | RAS Address Hold Field                                                               |         |

|       | Address Setup Field                                                                  |         |

|       | CAS Width Field                                                                      |         |

|       | Multiple Data Reads<br>Basic DRAM Write                                              |         |

|       | RAS Asserted at Start of Write                                                       |         |

|       | RAS Asserted at End of Write                                                         |         |

|       | RAS Asserted Throughout Write                                                        |         |

|       | Other DRAM timing Controls                                                           |         |

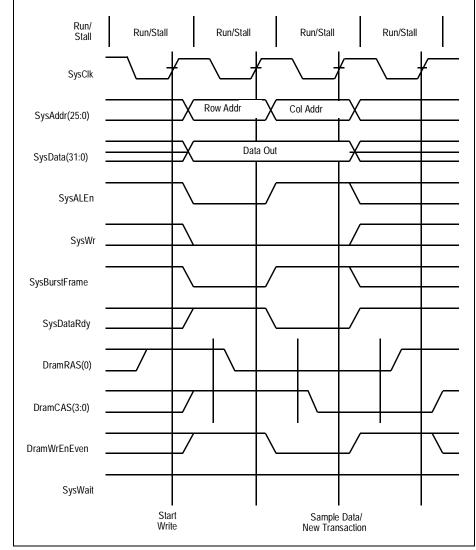

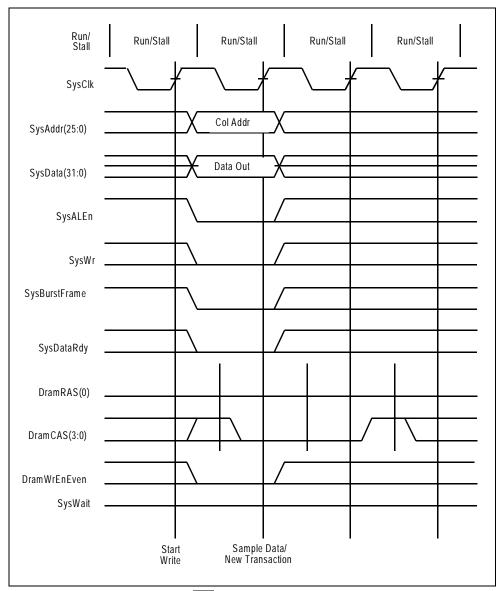

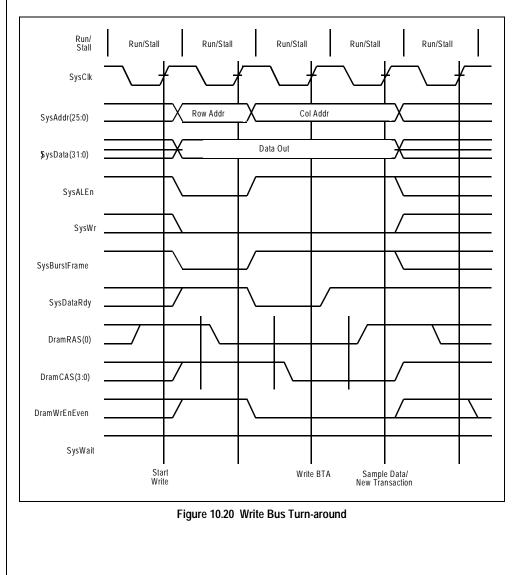

|       | Write Bus Turn-Around                                                                |         |

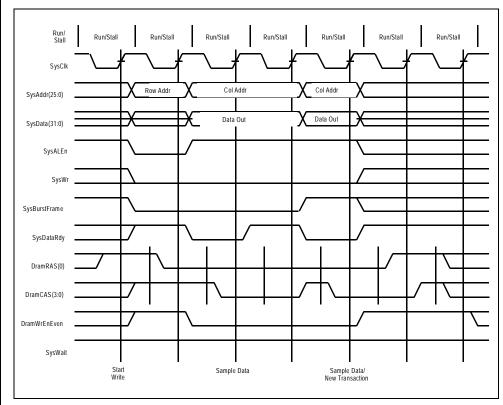

|       | Two Datum Write Transaction                                                          |         |

|       | Interleaved Read Timing Diagrams                                                     |         |

|       | Interleaved FCT245 Reads                                                             |         |

|       | Interleaved FCT260 Reads                                                             |         |

|       | Interleaved FCT543 Reads                                                             | . 10-38 |

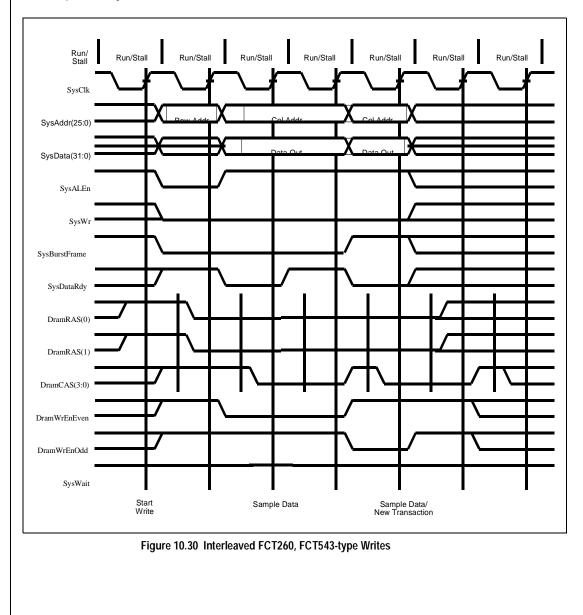

|       | Interleaved Writes                                                                   | . 10-41 |

|       | Single Word Interleaved FCT245 Write                                                 | . 10-41 |

|       | Interleaved FCT245 Writes                                                            |         |

|       | Single Word Interleaved FCT260 Write                                                 |         |

|       | Interleaved FCT260 Writes                                                            |         |

|       | Interleaved FCT543 Writes                                                            | . 10-43 |

|       |                                                                                      |         |

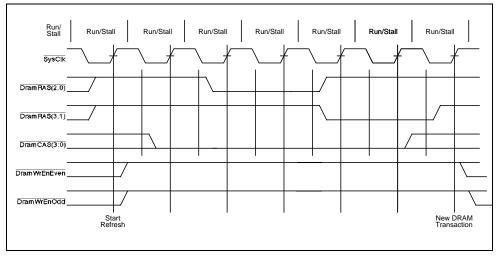

|       | Refresh                                                                                                     | 10-44 |

|-------|-------------------------------------------------------------------------------------------------------------|-------|

| Notes | System Examples                                                                                             | 10-44 |

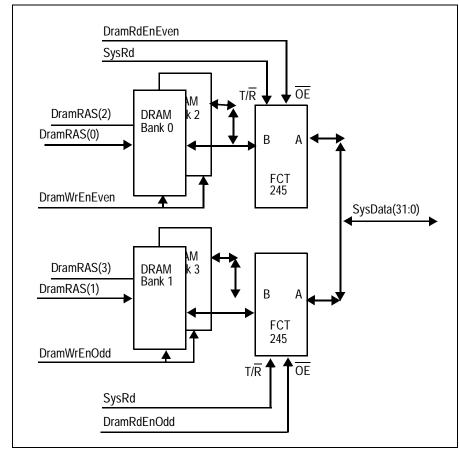

|       | DRAM System using FCT245 Transceivers                                                                       |       |

|       | Low Cost DRAM System using FCT245 Transceivers                                                              | 10-45 |

|       | Very Low Cost DRAM System without Transceivers                                                              | 10-46 |

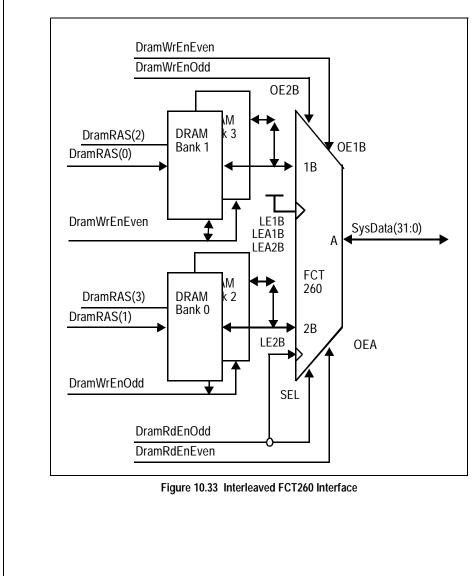

|       | DRAM System using FCT260 Multiplexers                                                                       |       |

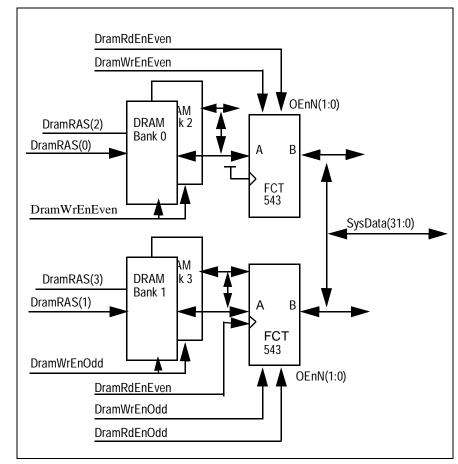

|       | DRAM System using FCT543 Registered Transceivers                                                            |       |

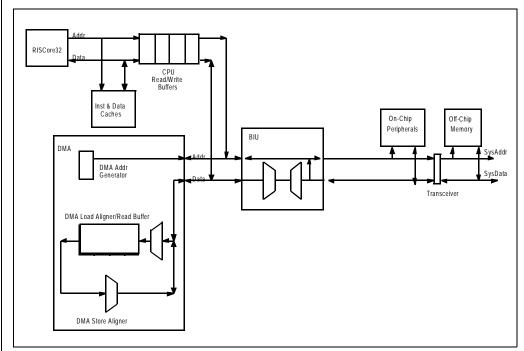

|       | Direct Memory Access (DMA) Controller                                                                       | •     |

|       | Introduction                                                                                                |       |

|       | Features                                                                                                    |       |

|       | Block Diagram Overview                                                                                      |       |

|       | Functional Overview                                                                                         |       |

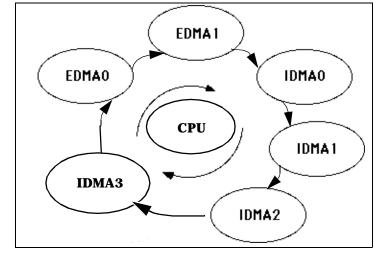

|       | Internal DMA Channels                                                                                       |       |

|       | Internal DMA Algorithm                                                                                      |       |

|       | External DMA Channels                                                                                       |       |

|       | Pin Descriptions                                                                                            |       |

|       | Direct Memory Access (DMA) Controller Signals<br>System Control Signals used during DMA Controller Accesses |       |

|       | Register Descriptions                                                                                       |       |

|       | Internal DMA Controller Register Descriptions                                                               |       |

|       | DMA LSB Source Address Register for Channel 03                                                              |       |

|       | ('DmaLSBSourceAddrReg(03)')                                                                                 | 11-8  |

|       | DMA LSB Source Address Register for Link AD                                                                 |       |

|       | ('DmaLSBSourceAddrReg(AD)')                                                                                 | 11-8  |

|       | DMA MSB Source Address Register for Channel 03                                                              |       |

|       | ('DmaMSBSourceAddrReg(03)')                                                                                 | 11-8  |

|       | DMA MSB Source Address Register for Link AD                                                                 |       |

|       | ('DmaMSBSourceAddrReg(AD)')                                                                                 | 11-8  |

|       | DMA LSB Target Address Register for Channel 03                                                              |       |

|       | ('DmaLSBTargetAddrReg(03)')                                                                                 | 11-9  |

|       | DMA LSB Target Address Register for Link AD                                                                 |       |

|       | ('DmaLSBTargetAddrReg(AD)')                                                                                 | 11-9  |

|       | DMA MSB Target Address Register for Channel 03                                                              | 11.0  |

|       | ('DmaMSBTargetAddrReg(03)')                                                                                 | 11-9  |

|       | DMA MSB Target Address Register for Link AD                                                                 | 11.0  |

|       | ('DmaMSBTargetAddrReg(AD)')                                                                                 |       |

|       | DMA LSB Count Register for Channel 03<br>DMA LSB Count Register for Link AD                                 |       |

|       | DMA LSD count Register for Channel 03                                                                       |       |

|       | ('DmaMSBCountReg(0.3)')                                                                                     | 11-10 |

|       | DMA MSB Count Register for Link AD                                                                          |       |

|       | ('DmaMSBCountReg(AD)')                                                                                      | 11-10 |

|       | DMA LSB Control Register for Channel 03                                                                     |       |

|       | ('DmaLSBControlReg(03)')                                                                                    | 11-10 |

|       | DMA LSB Control Register for Link AD                                                                        |       |

|       | ('DmaLSBControlReg(AD)')                                                                                    |       |

|       | Arbitration Type ('Arb') Field (Bit 15):                                                                    |       |

|       | Keep Bus ('Bus') Field (Bit 14):                                                                            |       |

|       | Allow DMADone ('Done') Field Bit (13):                                                                      |       |

|       | Wait for Interrupt ('WInt') Field (Bit 12):                                                                 |       |

|       | Burst Type ('Burst') Field (Bit 9)                                                                          |       |

|       | Source Byte Enable Type ('SBE') Field (Bit7:6):                                                             |       |

|       | Target Byte Enable Type ('TBE') Field (Bit 5:4):                                                            |       |

|       | Source Endianness Type ('SEndian') Field (Bit 3):                                                           |       |

|       | Target Endianness Type ('TEndian') Field (Bit 2):<br>Increment Source Address ('SInc') Field (Bit 1):       |       |

|       |                                                                                                             | 11-13 |

|       | Increment Target Address ('TInc') Field (Bit 0):                                  | 11-13 |

|-------|-----------------------------------------------------------------------------------|-------|

| Notes | DMA MSB Control Register for Channel 03                                           |       |

|       | ('DmaMSBControlReg(03)')                                                          | 11-13 |

|       | DMA MSB Control Register for Link AD                                              |       |

|       | ('DmaMSBControlReg(AD)')                                                          | 11-13 |

|       | Stop ('Stop') Field (Bit 15):                                                     |       |

|       | Break ('Break') Field (Bit 14):                                                   |       |

|       | ReservedLink Field ('RsvdLink') (Bit 13:10):                                      |       |

|       | Link ('Link') Field (Bit9:8):                                                     |       |

|       | Burst Size ('BurstSize') Field (Bit 3:0)                                          |       |

|       | External DMA Controller Registers                                                 |       |

|       | External DMA Control Register 01                                                  |       |

|       | ('ExtDmaControlReg(01)')                                                          | 11-15 |

|       | Stop Channel ('EC') Field (Bit 15):                                               | 11-16 |

|       | Bus Request Protocol High ('ReqH') Field (Bit 14):                                | 11-16 |

|       | Sample MemWrEn and SysBurstFrame 1 Clock Later                                    |       |

|       | ('SampleLate') Field (Bit 11):                                                    | 11-16 |

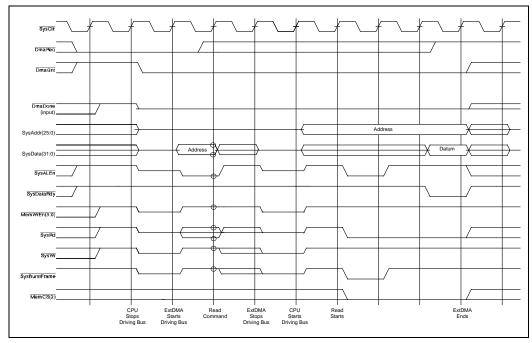

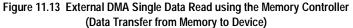

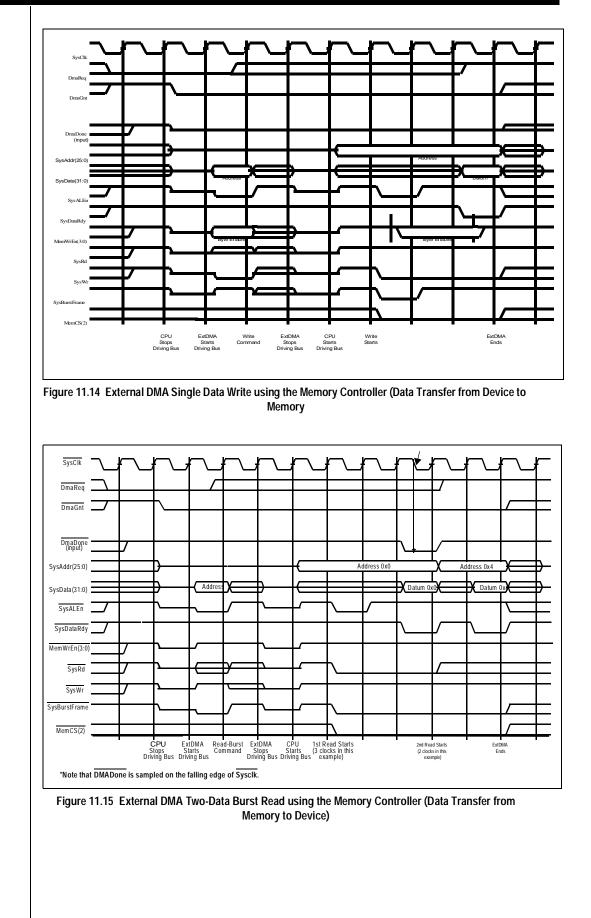

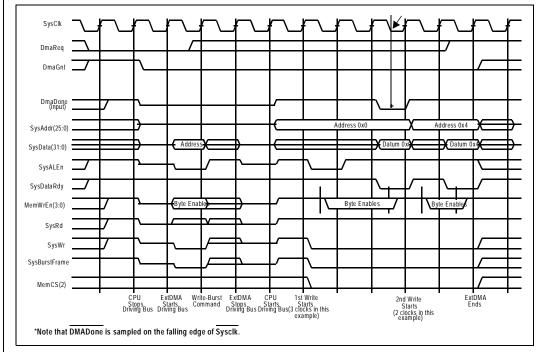

|       | External DMA Transactions                                                         | 11-16 |

|       | External DMA Operation Timing Diagrams                                            |       |

|       | System Examples                                                                   | 11-19 |

|       | Memory-to-Memory Copying                                                          | 11-19 |

|       | Transfers between I/O and Memory                                                  |       |

|       | Distinguishing Between CPU and Internal DMA Accesses                              |       |

|       | Internal DMA Channel Chaining                                                     |       |

|       | Parallel Input/Output (PIO)                                                       | -     |

|       | Introduction                                                                      |       |

|       | Features                                                                          |       |

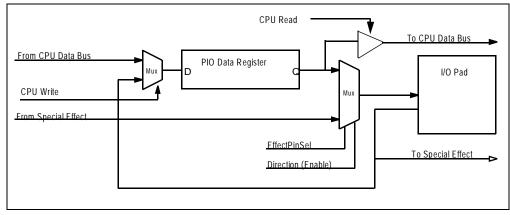

|       | Block Diagram                                                                     |       |

|       | Overview                                                                          |       |

|       | Pin Descriptions                                                                  |       |

|       | Register Definitions                                                              |       |

|       | PIO Data Register 02 ('PioDataReg'02)                                             |       |

|       | PIO Data ('PIOData') Field:                                                       |       |

|       | PIO Direction Register 02 ('PioDirReg'02)                                         |       |

|       | Lock ('Lock') Field:                                                              |       |

|       | Direction ('Dir') Field:                                                          |       |

|       | PIO Effect Select Register 02 ('PioEffectSelReg'02)                               |       |

|       | Lock ('Lock') Field:                                                              |       |

|       | Effect Select ('EffectSel') Field:                                                |       |

|       | Peripheral Expansion Interrupt Controller                                         |       |

|       | Introduction<br>Features                                                          |       |

|       |                                                                                   |       |

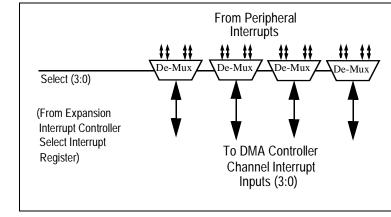

|       | Block Diagrams<br>Overview                                                        |       |

|       | Pin Descriptions                                                                  |       |

|       | Exception Signals                                                                 |       |

|       | ExcSlnt(2:0),                                                                     |       |

|       | Exclint(4:3) Input                                                                |       |

|       | ExcSBrCond(3:2) Input                                                             |       |

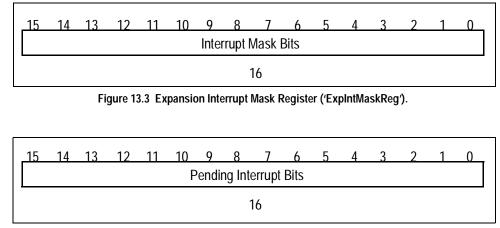

|       | Exception (3.2) mput<br>Expansion Interrupt Mask Register 01 ('ExplntMaskReg01)') |       |

|       | Expansion Interrupt Pending Register 01 ('Explicit PendReg01)')                   |       |

|       | Reserved Low ('0') Field:                                                         |       |

|       | Mask Bits ('Mask') Field:                                                         |       |

|       | Pending Bits ('Pend') Field:                                                      |       |

|       | Expansion Interrupt DMA Select Register ('ExpIntDMASelReg')                       |       |

|       | Select Interrupt 'SelInt()' Field:                                                |       |

|       |                                                                                   |       |

|       |                                                                                   |       |

| Timers Introduction                                       | •     |

|-----------------------------------------------------------|-------|

| Features                                                  |       |

| Block Diagram                                             |       |

| Overview                                                  |       |

| Pin Descriptions                                          |       |

| Timer Peripheral Signals                                  |       |

|                                                           |       |

| TC(2:0), Input/Output                                     |       |

| TimerGate(2:0)                                            |       |

| Register Descriptions                                     |       |

| Timer Prescaler Count Register ('TimerPrescalerCountReg') |       |

| Timer Count Register 02, Timer PWM Count Register         |       |

| ('TimerCountReg'02, TimerPWMCount Reg'0)                  |       |

| Timer Compare Register 02                                 |       |

| ('TimerCompareReg'02)                                     |       |

| Timer Pulse Width Modulation Register 0                   |       |

| ('TimerPWMReg0')                                          |       |

| Timer Control Register 02 ('TimerControlReg'02)           | 14-   |

| Lock ('Lock') Field (Bit 15):                             | 14-0  |

| Lock Count and Compare ('LockCC') Field (Bit 14):         | 14-0  |

| Write Compare Ack ('Ack') Field (Bit13):                  | 14-0  |

| PIO is Input Gate ('Gate') Field (Bit 11):                | 14-6  |

| BusTimeout ('BTO') Field (Bit 10):                        |       |

| Timer Disable ('TimerDis') Field (Bit 9):                 |       |

| Prescaler Select ('PSel') Field (Bit 3:0):                |       |

| Serial Ports                                              |       |

| Introduction                                              |       |

| Features                                                  |       |

| Overview                                                  |       |

| Registers                                                 |       |

| Interrupts                                                |       |

| DMA                                                       |       |

| External connections of the SCC                           |       |

|                                                           |       |

| SCC Operations                                            |       |

| Polled Operation                                          |       |

| Interrupt operation                                       |       |

| The SCC's Interrupt Structure                             |       |

| DMA operation                                             |       |

| Data Encoding                                             |       |

| Digital Phase Locked Loop (DPLL)                          |       |

| External Connections                                      | 15-9  |

| SDLC Loop Mode                                            | 15-   |

| Clocking Options                                          | 15-9  |

| SCC Operating Sequence                                    | 15-10 |

| I/O                                                       |       |

| SCC Registers                                             |       |

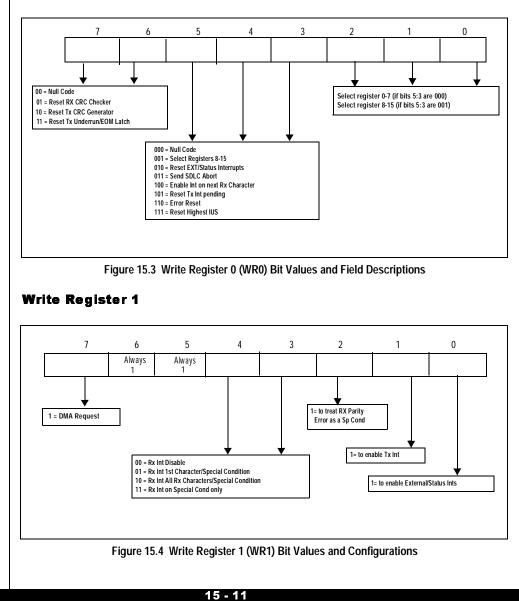

| Write Register 0                                          |       |

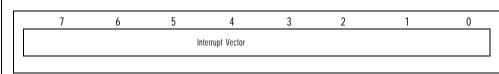

| Write Register 1                                          |       |

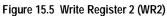

| Write Register 2                                          |       |

| 5                                                         |       |

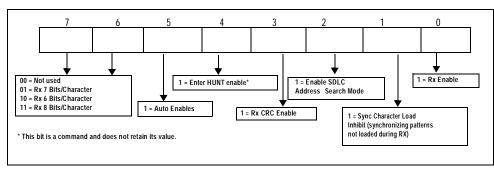

| Write Register 3                                          |       |

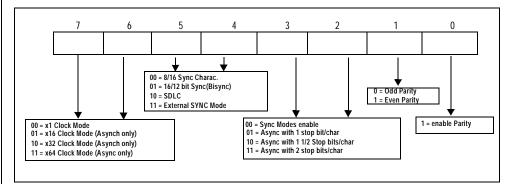

| Write Register 4                                          |       |

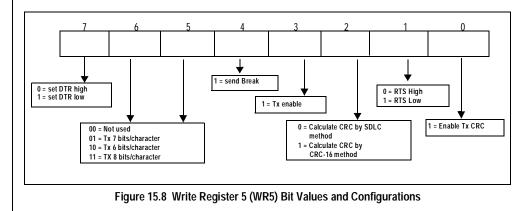

| Write Register 5                                          |       |

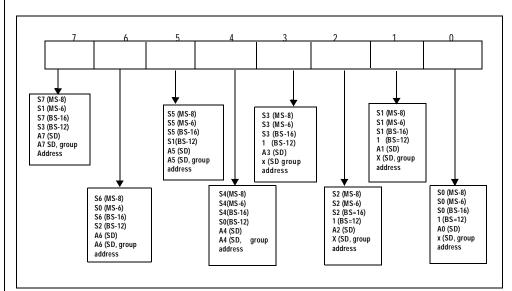

| Write Register 6                                          |       |

| Write Register 7                                          |       |

| Write Register 7'                                         |       |

| Write Register 8 is the Data Register.                    | 15-14 |

| Tab | e of | Con | ten | 9 |

|-----|------|-----|-----|---|

|     |      |     |     |   |

|       | Write Register 9                                                         |       |

|-------|--------------------------------------------------------------------------|-------|

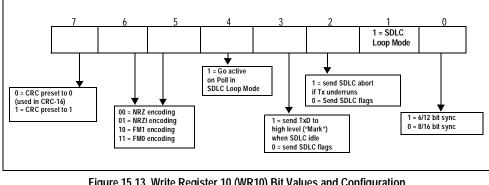

| Notes | Write Register 10                                                        |       |

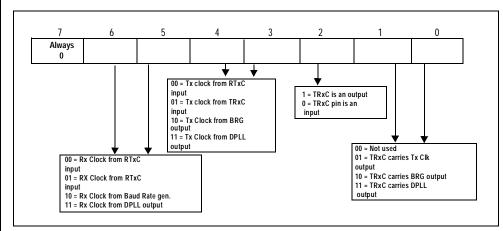

|       | Write Register 11                                                        |       |

|       | Write Register 12 carries the low byte of the                            |       |

|       | Baud Rate Generator Time Constant.                                       | 15-15 |

|       | Write Register 13 carries the high byte of the                           |       |

|       | Baud Rate Generator Time Constant                                        | 15-15 |

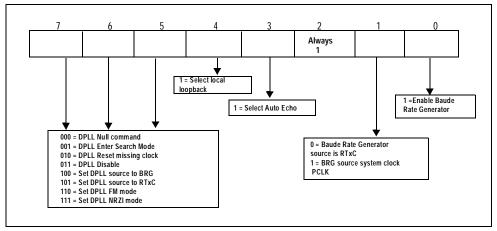

|       | Write Register 14                                                        | 15-15 |

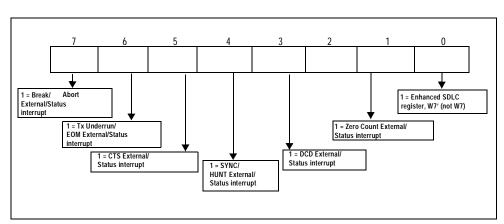

|       | Write Register 15                                                        |       |

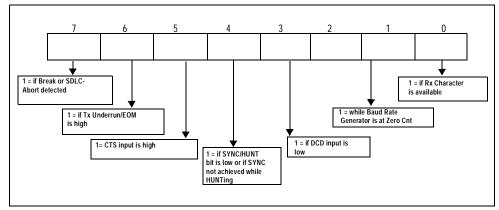

|       | Read Register 0                                                          |       |

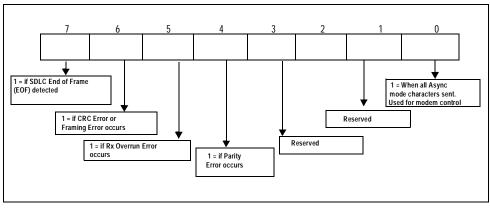

|       | Read Register 1                                                          | 15-16 |

|       | Read Register 2: Reads back WR2 in channel A, includes interrupt status  |       |

|       | (in bits 3:1) in Channel B.                                              |       |

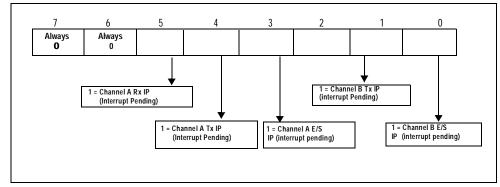

|       | Read Register 3 (Channel A only)                                         | 15-17 |

|       | Read Register 4 is the readback register for WR4                         | 15 17 |

|       | if WR7′ bit 6 is set<br>Read Register 5 is the readback register for WR5 | 13-17 |

|       | if WR7' bit 6 is set                                                     | 15 17 |

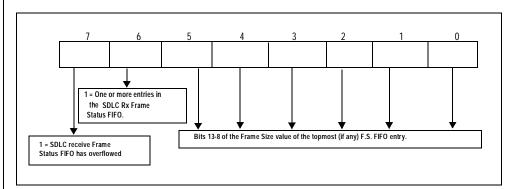

|       | Read Register 6 carries the lowest byte of the Frame Size value within   |       |

|       | the topmost entry (if any) of the SDLC receive Frame Status FIFO.        | 15-17 |

|       | Read Register 7                                                          |       |

|       | Bidirectional Parallel Port                                              |       |

|       | Introduction                                                             |       |

|       | Features                                                                 |       |

|       | Block Diagram                                                            | 16-1  |

|       | Overview                                                                 | 16-2  |

|       | Negotiation Phase                                                        |       |

|       | Nibble Mode Phase                                                        |       |

|       | Byte Mode Phase                                                          |       |

|       | Extended Capabilities Port (ECP) Mode Phase                              |       |

|       | Enhanced Parallel Port (EPP) Mode Phases                                 |       |

|       | CPU Control Mode Phases                                                  |       |

|       | Programmable Timing<br>Centronics, Interrupts & DMA Requests             |       |

|       | Centrolics, interrupts & DWA Requests                                    |       |

|       | CentRdInt                                                                |       |

|       | CentrWrInt                                                               |       |

|       | DMARdReg                                                                 |       |

|       | DMAWrReg                                                                 |       |

|       | Pin Descriptions                                                         |       |

|       | Bidirectional Parallel Port Centronics Interface Signals                 |       |

|       | CentStrobe Input                                                         | 16-6  |

|       | CentAck Output                                                           | 16-6  |

|       | CentBusy Output                                                          |       |

|       | CentPaperError Output                                                    | 16-6  |

|       | CentSelect Output                                                        |       |

|       | Centronics Select                                                        |       |

|       | CentAutoFeed Input                                                       |       |

|       | Centronics Auto Feed                                                     |       |

|       | Centinit Input                                                           |       |

|       | Centronics Initialize                                                    |       |

|       | CentFault Output<br>Centronics Fault:                                    |       |

|       | Centonics Fault                                                          |       |

|       | Centronics Select Input                                                  |       |

|       | Bidirectional Parallel Port Centronics Peripheral                        |       |

|       | · · · · · · · · · · · · · · · · · · ·                                    |       |

| and Host Interface Signals                                   |      |

|--------------------------------------------------------------|------|

| CentCS(7:6) Output                                           |      |

| CentWrStrobe Output                                          |      |

| CentRdOEn Output                                             |      |

| CentHostStrobe Output                                        |      |

| CentHostOEn Output                                           |      |

| Register Definitions                                         |      |

| Centronics Sub Mode Register ('CentSubModeReg')              |      |

| Centronics Compatible Sub Modes ('SubMode') Field            |      |

| Centronics Status Register ('CentStatusReg')                 |      |

| Extended Capabilities Port Buffer Full (BufFul)              |      |

| Extended Capabilities Peripheral Acknowledge Field (nPerAck) |      |

| Extended Capabilities Peripheral Request Field (nPerReq)     |      |

|                                                              |      |

| Printer Error ('PError') Field                               |      |

| Printer On Line Select ('Select') Field:                     |      |

| Printer Fault ('Fault') Field:                               |      |

| Printer Acknowledge Negated ('AckN') Field                   |      |

| Printer Busy ('Busy') Field                                  |      |

| Centronics Control Register ('CentControlReg')               |      |

| Iprime Interrupt Pending Field                               |      |

| loCS(7), loCS(6) Mask Enable                                 |      |

| Centronics Negotiation Interrupt Pending                     |      |

| Centronics Negotiation Interrupt Enable                      |      |

| Centronics Reset Interrupt Pending                           | 16-1 |

| Centronics Reset Interrupt Enable                            | 16-1 |

| DMA or Interrupt Field in ECP/EPP Mode                       | 16-1 |

| Nibble ID Mode Field                                         | 16-1 |

| Host Busy Data Available Enable Field (HBDA)                 |      |

| Negotiation XFlag Reply ('NegRep') Field                     |      |

| Negotiation Mode ('NegMode') Field                           |      |

| Centronics Nibble Data Register ('CentNibbleDataReg')        |      |

| Centronics Host Status Register ('CentHostStatusReg')        |      |

| AutoFeed Negated ('nAutoFeed') Field                         |      |

| Initialize Negated ('nInit') Field                           |      |

| Select In Negated ('nSelectIn') Field                        |      |

| Host Strobe Negated ('nStrobe') Field                        |      |

| Centronics Minimum Delay Register ('CentDelayReg')           |      |

| 2500ns Delay Type Field ('D2500ns') Field                    |      |

| 500ns Delay Type Field ('D500ns') Field                      |      |

|                                                              |      |

| LSB/MSB Host Time-Out Register                               |      |

| LSB/MSB Host Time-Out Counter Register                       |      |

| Timing Diagram                                               |      |

| System Example                                               |      |

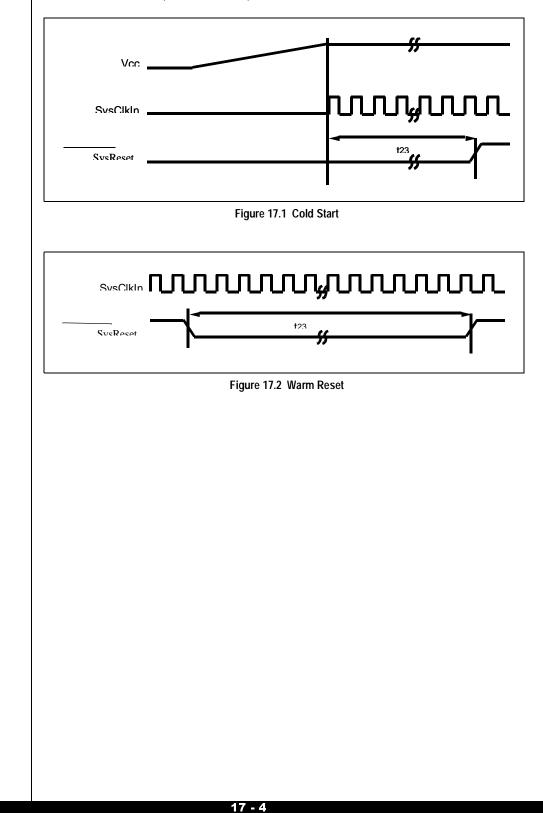

| Reset Initialization and Input Clocking                      | -    |

| Introduction                                                 |      |

| Reset Timing                                                 |      |

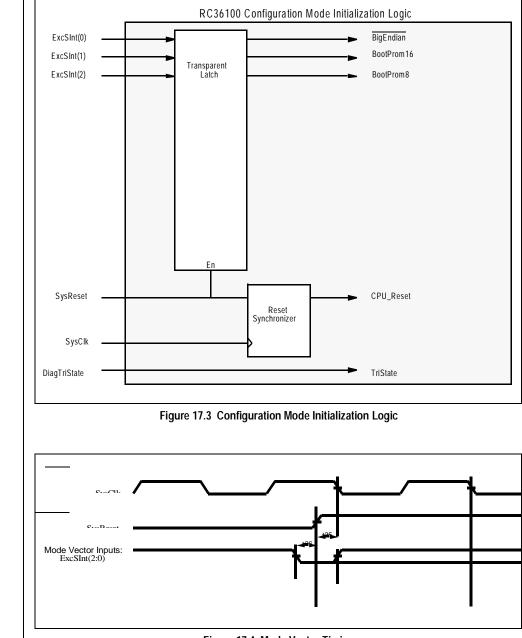

| Reset Configuration Mode Features                            |      |

| Reset Configuration Mode Pin Descriptions                    |      |

| Exception Signals                                            | 17-  |

| SysReset Input                                               | 17-  |

| ExcSInt(2:0) Input                                           | 17-  |

| LittleEndian                                                 |      |

| BootProm8                                                    |      |

| BootProm16                                                   |      |

| RISCore32 series Equivalent Modes                            |      |

|                                                              |      |

| Reset Behavior                                               | 17   |

| Notes         Boot Software Requirements           Detailed Reset Timing Diagrams         Detailed Reset Timing Diagrams           Reset Pulse Width         Reset Timing Diagrams | 17-3<br>17-3<br>17-4 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

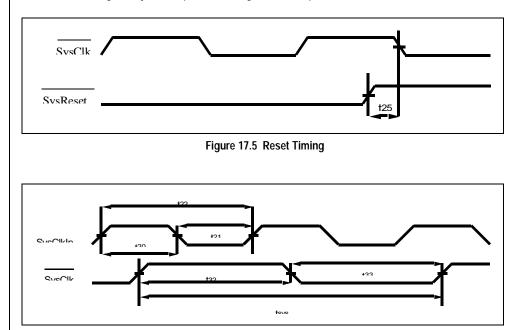

| Reset Pulse Width                                                                                                                                                                  | 17-3<br>17-4         |

|                                                                                                                                                                                    | 17-4                 |

| Mode Initialization Timing Requirements                                                                                                                                            |                      |

| Reset Setup Time Requirements                                                                                                                                                      |                      |

| ClkIn Requirements                                                                                                                                                                 | 17-6                 |

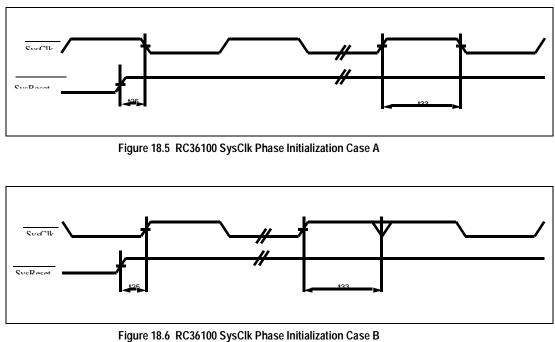

| Debug Mode Features Chapt                                                                                                                                                          |                      |

| Introduction                                                                                                                                                                       |                      |

| Features                                                                                                                                                                           |                      |

| Tri-Stateable Outputs                                                                                                                                                              |                      |

| Tracepoint Registers                                                                                                                                                               |                      |

| Extended CP0 Cache Configuration Register                                                                                                                                          |                      |

| Cause and EPC Register Writes                                                                                                                                                      |                      |