Data sheet acquired from Harris Semiconductor SCHS047C

August 1998 - Revised August 1999

# CMOS Analog Multiplexers/Demultiplexers with Logic Level Conversion

The CD4051B, CD4052B, and CD4053B analog multiplexers are digitally-controlled analog switches having low ON impedance and very low OFF leakage current. Control of analog signals up to  $20V_{P-P}$  can be achieved by digital signal amplitudes of 4.5V to 20V (if  $V_{DD}$ - $V_{SS}$  = 3V, a  $V_{DD}$ - $V_{EE}$  of up to 13V can be controlled; for  $V_{DD}$ - $V_{EE}$  level differences above 13V, a  $V_{DD}$ - $V_{SS}$  of at least 4.5V is required). For example, if  $V_{DD}$  = +4.5V,  $V_{SS}$  = 0V, and  $V_{EE}$  = -13.5V, analog signals from -13.5V to +4.5V can be controlled by digital inputs of 0V to 5V. These multiplexer circuits dissipate extremely low quiescent power over the full  $V_{DD}$ - $V_{SS}$  and  $V_{DD}$ - $V_{EE}$  supply-voltage ranges, independent of the logic state of the control signals. When a logic "1" is present at the inhibit input terminal, all channels are off.

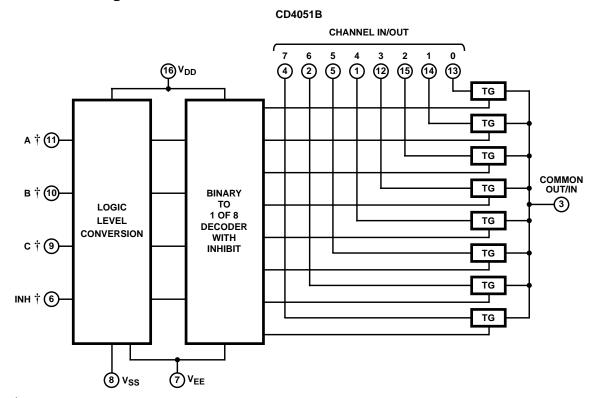

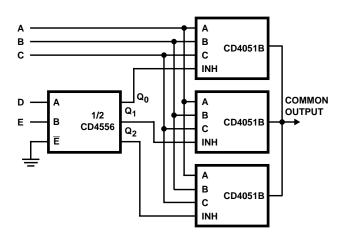

The CD4051B is a single 8-Channel multiplexer having three binary control inputs, A, B, and C, and an inhibit input. The three binary signals select 1 of 8 channels to be turned on, and connect one of the 8 inputs to the output.

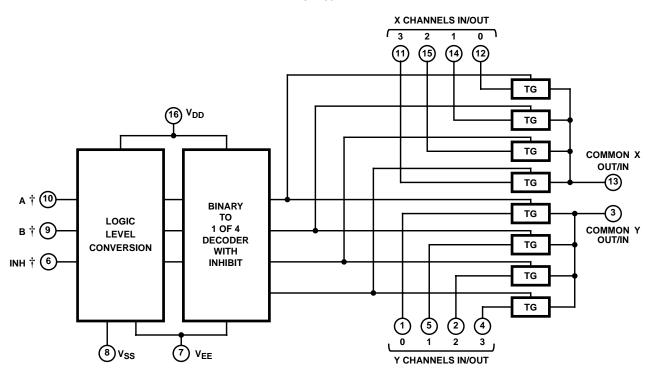

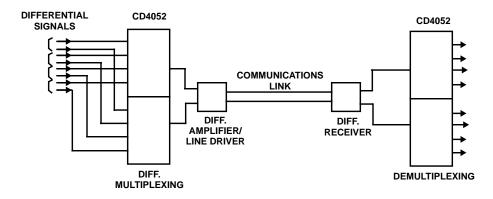

The CD4052B is a differential 4-Channel multiplexer having two binary control inputs, A and B, and an inhibit input. The two binary input signals select 1 of 4 pairs of channels to be turned on and connect the analog inputs to the outputs.

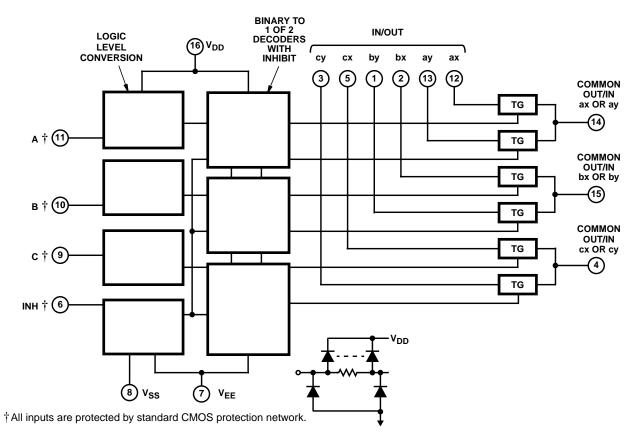

The CD4053B is a triple 2-Channel multiplexer having three separate digital control inputs, A, B, and C, and an inhibit input. Each control input selects one of a pair of channels which are connected in a single-pole, double-throw configuration.

When these devices are used as demultiplexers, the "CHANNEL IN/OUT" terminals are the outputs and the "COMMON OUT/IN" terminals are the inputs.

## Ordering Information

| PART NUMBER                     | TEMP.<br>RANGE (°C) | PACKAGE      | PKG.<br>NO. |

|---------------------------------|---------------------|--------------|-------------|

| CD4051BF, CD4052BF,<br>CD4053BF | -55 to 125          | 16 Ld CERDIP | F16.3       |

| CD4051BE, CD4052BE,<br>CD4053BE | -55 to 125          | 16 Ld PDIP   | E16.3       |

| CD4051BM                        | -55 to 125          | 16 Ld SOIC   | M16.15      |

### Features

- · Wide Range of Digital and Analog Signal Levels

- Low ON Posistance 1250 (Typ) Over 15\/ Signal laput

- Low ON Resistance, 125 $\Omega$  (Typ) Over 15V<sub>P-P</sub> Signal Input Range for V<sub>DD</sub>-V<sub>EE</sub> = 18V

- High OFF Resistance, Channel Leakage of  $\pm 100 pA$  (Typ) at  $V_{DD}-V_{EE}=18V$

- Logic-Level Conversion for Digital Addressing Signals of 3V to 20V (V<sub>DD</sub>-V<sub>SS</sub> = 3V to 20V) to Switch Analog Signals to 20V<sub>P-P</sub> (V<sub>DD</sub>-V<sub>EE</sub> = 20V)

- Matched Switch Characteristics,  $r_{ON} = 5\Omega$  (Typ) for  $V_{DD}$ - $V_{EE} = 15V$

- Very Low Quiescent Power Dissipation Under All Digital-Control Input and Supply Conditions, 0.2μW (Typ) at V<sub>DD</sub>-V<sub>SS</sub> = V<sub>DD</sub>-V<sub>EE</sub> = 10V

- · Binary Address Decoding on Chip

- 5V, 10V and 15V Parametric Ratings

- 10% Tested for Quiescent Current at 20V

- Maximum Input Current of 1μA at 18V Over Full Package Temperature Range, 100nA at 18V and 25°C

- Break-Before-Make Switching Eliminates Channel Overlap

# **Applications**

- Analog and Digital Multiplexing and Demultiplexing

- A/D and D/A Conversion

- · Signal Gating

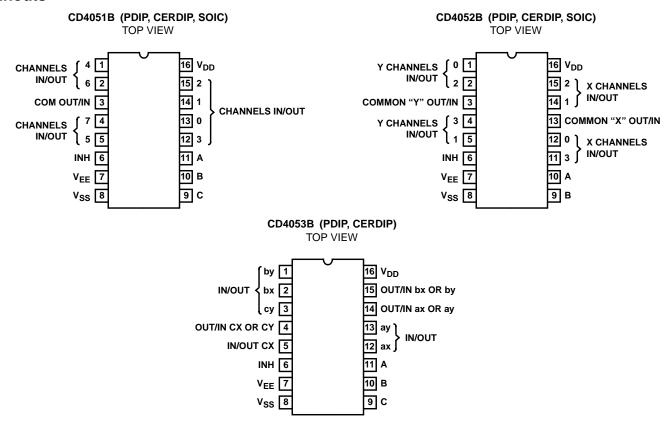

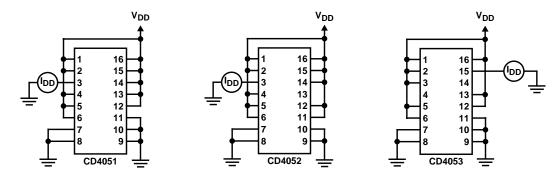

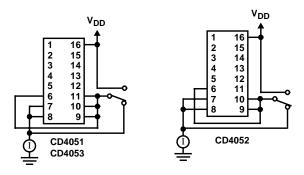

### **Pinouts**

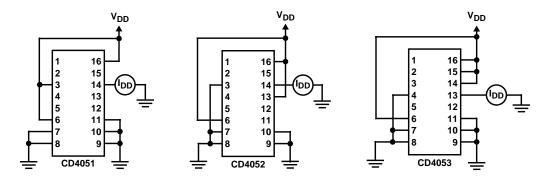

# Functional Block Diagrams

$\dagger$  All inputs are protected by standard CMOS protection network.

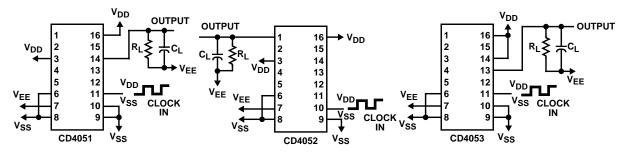

# Functional Block Diagrams (Continued)

### CD4052B

### CD4053B

# CD4051B, CD4052B, CD4053B

# TRUTH TABLES

| I       | NPUT ST |   |   |                 |  |  |  |  |

|---------|---------|---|---|-----------------|--|--|--|--|

| INHIBIT | С       | В | Α | "ON" CHANNEL(S) |  |  |  |  |

| CD4051B |         |   |   |                 |  |  |  |  |

| 0       | 0       | 0 | 0 | 0               |  |  |  |  |

| 0       | 0       | 0 | 1 | 1               |  |  |  |  |

| 0       | 0       | 1 | 0 | 2               |  |  |  |  |

| 0       | 0       | 1 | 1 | 3               |  |  |  |  |

| 0       | 1       | 0 | 0 | 4               |  |  |  |  |

| 0       | 1       | 0 | 1 | 5               |  |  |  |  |

| 0       | 1 1     |   | 0 | 6               |  |  |  |  |

| 0       | 1 1     |   | 1 | 7               |  |  |  |  |

| 1       | Х       | Х | Х | None            |  |  |  |  |

| CD4052B |         |   |   |                 |  |  |  |  |

| INHIBIT | ı       | 3 | Α |                 |  |  |  |  |

| 0       | (       | ) | 0 | 0x, 0y          |  |  |  |  |

| 0       |         | ) | 1 | 1x, 1y          |  |  |  |  |

| 0       |         | 1 | 0 | 2x, 2y          |  |  |  |  |

| 0       |         | 1 | 1 | 3x, 3y          |  |  |  |  |

| 1       | )       | < | Х | None            |  |  |  |  |

| CD4053B |         |   |   |                 |  |  |  |  |

| INHIBIT | А       |   |   |                 |  |  |  |  |

| 0       |         | 0 |   | ax or bx or cx  |  |  |  |  |

| 0       |         | 1 |   | ay or by or cy  |  |  |  |  |

| 1       |         | Х |   | None            |  |  |  |  |

X = Don't Care

### CD4051B, CD4052B, CD4053B

# Absolute Maximum Ratings Supply Voltage (V+ to V-) Voltages Referenced to V<sub>SS</sub> Terminal .....-0.5V to 20V DC Input Voltage Range .....-0.5V to V<sub>DD</sub> +0.5V DC Input Current, Any One Input ......±10mA

### **Operating Conditions**

Temperature Range . . . . . . . -55°C to 125°C

### **Thermal Information**

| Thermal Resistance (Typical, Note 1)    | $\theta_{JA}$ (oC/W) | $\theta_{JC}$ (oC/W) |

|-----------------------------------------|----------------------|----------------------|

| PDIP Package                            | 78                   | N/A                  |

| CERDIP Package                          | 115                  | 45                   |

| SOIC Package                            | 113                  | N/A                  |

| Maximum Junction Temperature (Ceramic F |                      | 175 <sup>0</sup> C   |

| Maximum Junction Temperature (Plastic F | Package)             | 150 <sup>0</sup> C   |

| Maximum Storage Temperature Range       | 6                    | 5°C to 150°C         |

| Maximum Lead Temperature (Soldering 1   | 0s)                  | 265 <sup>0</sup> C   |

| (SOIC - Lead Tips Only)                 |                      |                      |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

### NOTE:

1.  $\theta_{\text{JA}}$  is measured with the component mounted on an evaluation PC board in free air.

**Electrical Specifications** Common Conditions Here: If Whole Table is For the Full Temp. Range,  $V_{SUPPLY} = \pm 5V$ ,  $A_V = +1$ ,  $R_L = 100\Omega$ , Unless Otherwise Specified (Note 3)

|                                                                                                          | CONDITIONS LIMITS AT INDICATED TEMPERATURES (°C) |                                      |                     |                     |        |         |       |          | °C) |       |                  |       |

|----------------------------------------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------|---------------------|---------------------|--------|---------|-------|----------|-----|-------|------------------|-------|

|                                                                                                          |                                                  |                                      |                     |                     |        |         |       |          |     | 25    |                  | -     |

| PARAMETER                                                                                                | V <sub>IS</sub> (V)                              | V <sub>EE</sub> (V)                  | V <sub>SS</sub> (V) | V <sub>DD</sub> (V) | -55    | -40     | 85    | 125      | MIN | TYP   | MAX              | UNITS |

| SIGNAL INPUTS (V <sub>IS</sub> ) A                                                                       | ND OUTPUT                                        | S (V <sub>OS</sub> )                 |                     |                     |        |         | ,     |          |     |       |                  |       |

| Quiescent Device                                                                                         | -                                                | -                                    | -                   | 5                   | 5      | 5       | 150   | 150      | -   | 0.04  | 5                | μΑ    |

| Current, I <sub>DD</sub> Max                                                                             | -                                                | -                                    | -                   | 10                  | 10     | 10      | 300   | 300      | -   | 0.04  | 10               | μΑ    |

|                                                                                                          | -                                                | -                                    | -                   | 15                  | 20     | 20      | 600   | 600      | -   | 0.04  | 20               | μА    |

|                                                                                                          | -                                                | -                                    | -                   | 20                  | 100    | 100     | 3000  | 3000     | -   | 0.08  | 100              | μА    |

| Drain to Source ON                                                                                       | -                                                | 0                                    | 0                   | 5                   | 800    | 850     | 1200  | 1300     | -   | 470   | 1050             | Ω     |

| Resistance $r_{ON}$ Max $0 \le V_{IS} \le V_{DD}$                                                        | -                                                | 0                                    | 0                   | 10                  | 310    | 330     | 520   | 550      | -   | 180   | 400              | Ω     |

| 10 00                                                                                                    | -                                                | 0                                    | 0                   | 15                  | 200    | 210     | 300   | 320      | -   | 125   | 240              | Ω     |

| Change in ON                                                                                             | -                                                | 0                                    | 0                   | 5                   | -      | -       | -     | -        | -   | 15    | -                | Ω     |

| Resistance (Between Any Two Channels),                                                                   | -                                                | 0                                    | 0                   | 10                  | -      | -       | -     | -        | -   | 10    | -                | Ω     |

| $\Delta r_{ON}$                                                                                          | -                                                | 0                                    | 0                   | 15                  | -      | -       | -     | -        | -   | 5     | -                | Ω     |

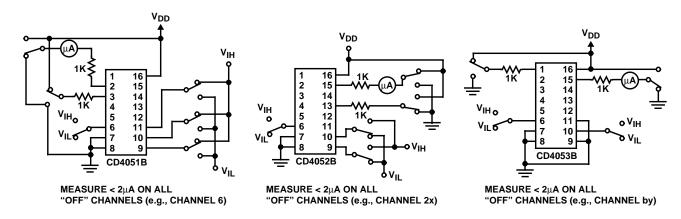

| OFF Channel Leakage<br>Current: Any Channel<br>OFF (Max) or ALL<br>Channels OFF (Common<br>OUT/IN) (Max) | -                                                | 0                                    | 0                   | 18                  | ±100 ( | Note 2) | ±1000 | (Note 2) | -   | ±0.01 | ±100<br>(Note 2) | μА    |

| Capacitance:                                                                                             | -                                                | -5                                   | 5-                  | 5                   |        |         |       |          |     |       |                  |       |

| Input, C <sub>IS</sub>                                                                                   |                                                  |                                      |                     |                     | -      | -       | -     | -        | -   | 5     | -                | pF    |

| Output, C <sub>OS</sub><br>CD4051                                                                        |                                                  |                                      |                     |                     | -      | -       | -     | -        | -   | 30    | -                | pF    |

| CD4052                                                                                                   |                                                  |                                      |                     |                     | -      | -       | -     | -        | -   | 18    | -                | pF    |

| CD4053                                                                                                   |                                                  |                                      |                     |                     | -      | -       | -     | -        | -   | 9     | -                | pF    |

| Feedthrough C <sub>IOS</sub>                                                                             |                                                  |                                      |                     |                     | -      | -       | -     | -        | -   | 0.2   | -                | pF    |

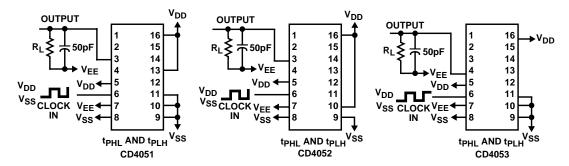

| Propagation Delay Time                                                                                   | V <sub>DD</sub>                                  | R <sub>L</sub> = 200                 | kΩ,                 | 5                   | -      | -       | -     | -        | -   | 30    | 60               | ns    |

| (Signal Input to Output                                                                                  | 丕                                                | $C_{L} = 50p$<br>$t_{r}, t_{f} = 20$ | F,<br>ns            | 10                  | -      | -       | -     | -        | -   | 15    | 30               | ns    |

|                                                                                                          |                                                  | 1, 1 =0                              | -                   | 15                  | -      | -       | -     | -        | -   | 10    | 20               | ns    |

# CD4051B, CD4052B, CD4053B

# **Electrical Specifications**

Common Conditions Here: If Whole Table is For the Full Temp. Range,  $V_{SUPPLY}=\pm5V$ ,  $A_V=+1$ ,  $R_L=100\Omega$ , Unless Otherwise Specified **(Continued)** (Note 3)

|                                                                   |                                                                                 | LIMITS AT INDICATED TEMPERATURES (°C)                                             |                     |                     |      |      |     |     |     |                   |      |       |

|-------------------------------------------------------------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|---------------------|---------------------|------|------|-----|-----|-----|-------------------|------|-------|

|                                                                   |                                                                                 |                                                                                   |                     |                     |      | -40  | 85  |     | 25  |                   |      |       |

| PARAMETER                                                         | V <sub>IS</sub> (V)                                                             | V <sub>EE</sub> (V)                                                               | V <sub>SS</sub> (V) | V <sub>DD</sub> (V) | -55  |      |     | 125 | MIN | TYP               | MAX  | UNITS |

| CONTROL (ADDRESS                                                  | OR INHIBIT),                                                                    | V <sub>C</sub>                                                                    | •                   | •                   |      |      |     | •   | •   | '                 |      |       |

| Input Low Voltage, V <sub>IL</sub> ,                              | $V_{IL} = V_{DD}$                                                               | $V_{EE} = V_{SS}$ ,<br>$R_L = 1k\Omega$ to $V_{SS}$ ,<br>$I_{IS} < 2\mu A$ on All |                     | 5                   | 1.5  | 1.5  | 1.5 | 1.5 | -   | -                 | 1.5  | V     |

| Max                                                               | through<br>1kΩ;                                                                 |                                                                                   |                     | 10                  | 3    | 3    | 3   | 3   | -   | -                 | 3    | V     |

|                                                                   | $V_{IH} = V_{DD}$                                                               | OFF Cha                                                                           |                     | 15                  | 4    | 4    | 4   | 4   | -   | -                 | 4    | V     |

| Input High Voltage, V <sub>IH</sub> ,                             | through<br>1kΩ                                                                  |                                                                                   |                     | 5                   | 3.5  | 3.5  | 3.5 | 3.5 | 3.5 | -                 | -    | V     |

| Min                                                               |                                                                                 |                                                                                   |                     | 10                  | 7    | 7    | 7   | 7   | 7   | -                 | -    | V     |

|                                                                   |                                                                                 | 1                                                                                 |                     | 15                  | 11   | 11   | 11  | 11  | 11  | -                 | -    | V     |

| Input Current, I <sub>IN</sub> (Max)                              | V <sub>IN</sub> = 0, 18                                                         |                                                                                   |                     | 18                  | ±0.1 | ±0.1 | ±1  | ±1  | -   | ±10 <sup>-5</sup> | ±0.1 | μΑ    |

| Propagation Delay Time:                                           |                                                                                 |                                                                                   |                     |                     |      |      |     |     |     |                   |      |       |

| Address-to-Signal                                                 | $t_{r}, t_{f} = 20\text{ns},$ $C_{L} = 50\text{pF},$ $R_{L} = 10\text{k}\Omega$ | 0                                                                                 | 0                   | 5                   | -    | -    | -   | -   | -   | 450               | 720  | ns    |

| OUT (Channels ON or OFF) See Figures 10,                          |                                                                                 | 0                                                                                 | 0                   | 10                  | -    | -    | -   | -   | -   | 160               | 320  | ns    |

| 11, 14                                                            |                                                                                 | 0                                                                                 | 0                   | 15                  | -    | -    | -   | -   | -   | 120               | 240  | ns    |

|                                                                   |                                                                                 | -5                                                                                | 0                   | 5                   | -    | -    | -   | -   | -   | 225               | 450  | ns    |

| Propagation Delay Time:                                           |                                                                                 |                                                                                   |                     |                     |      |      |     |     |     |                   |      |       |

| Inhibit-to-Signal OUT                                             | $t_{\rm r}, t_{\rm f} = 20 {\rm ns},$                                           | 0                                                                                 | 0                   | 5                   | -    | -    | -   | -   | -   | 400               | 720  | ns    |

| (Channel Turning ON)<br>See Figure 11                             | $C_L = 50pF,$<br>$R_L = 1k\Omega$                                               | 0                                                                                 | 0                   | 10                  | -    | -    | -   | -   | -   | 160               | 320  | ns    |

| -                                                                 |                                                                                 | 0                                                                                 | 0                   | 15                  | -    | -    | -   | -   | -   | 120               | 240  | ns    |

|                                                                   |                                                                                 | -10                                                                               | 0                   | 5                   | -    | -    | -   | -   | -   | 200               | 400  | ns    |

| Propagation Delay Time:                                           |                                                                                 |                                                                                   |                     |                     |      |      |     |     |     |                   |      |       |

| Inhibit-to-Signal OUT                                             | $t_{r}, t_{f} = 20 \text{ns},$                                                  | 0                                                                                 | 0                   | 5                   | -    | -    | -   | -   | -   | 200               | 450  | ns    |

| (Channel Turning<br>OFF) See Figure 15                            | $C_L = 50pF,$<br>$R_L = 10k\Omega$                                              | 0                                                                                 | 0                   | 10                  | -    | -    | -   | -   | -   | 90                | 210  | ns    |

|                                                                   |                                                                                 | 0                                                                                 | 0                   | 15                  | -    | -    | -   | -   | -   | 70                | 160  | ns    |

|                                                                   |                                                                                 | -10                                                                               | 0                   | 5                   | -    | -    | -   | -   | -   | 130               | 300  | ns    |

| Input Capacitance, C <sub>IN</sub> (Any Address or Inhibit Input) |                                                                                 |                                                                                   |                     |                     | -    | -    | -   | -   | -   | 5                 | 7.5  | pF    |

### NOTE:

# **Electrical Specifications**

|                               |                                      | LIMITS              |                     |                                  |        |     |       |

|-------------------------------|--------------------------------------|---------------------|---------------------|----------------------------------|--------|-----|-------|

| PARAMETER                     | V <sub>IS</sub> (V)                  | V <sub>DD</sub> (V) | $R_L$ (k $\Omega$ ) |                                  |        | TYP | UNITS |

| Cutoff (-3dB) Frequency Chan- | 5 (Note 3)                           | 10                  | 1                   | V <sub>OS</sub> at Common OUT/IN | CD4053 | 30  | MHz   |

| nel ON (Sine Wave Input)      | V <sub>EE</sub> = V <sub>SS</sub> ,  |                     |                     |                                  | CD4052 | 25  | MHz   |

|                               | 201.6                                | V <sub>OS</sub> 3   | dB                  |                                  | CD4051 | 20  | MHz   |

|                               | $20Log \frac{V_{OS}}{V_{IS}} = -3dB$ |                     |                     | V <sub>OS</sub> at Any Channel   |        | 60  | MHz   |

<sup>2.</sup> Determined by minimum feasible leakage measurement for automatic testing.

### **Electrical Specifications**

|                                        |                                                                               | TEST CONDITIONS          |                     |                                |                       |                              |      |                    |  |  |  |

|----------------------------------------|-------------------------------------------------------------------------------|--------------------------|---------------------|--------------------------------|-----------------------|------------------------------|------|--------------------|--|--|--|

| PARAMETER                              | V <sub>IS</sub> (V)                                                           | V <sub>DD</sub> (V)      | $R_L$ (k $\Omega$ ) |                                |                       |                              | TYP  | UNITS              |  |  |  |

| Total Harmonic Distortion, THD         | 2 (Note 3)                                                                    | 5                        | 10                  |                                |                       |                              | 0.3  | %                  |  |  |  |

|                                        | 3 (Note 3)                                                                    | 10                       |                     |                                |                       |                              | 0.2  | %                  |  |  |  |

|                                        | 5 (Note 3)                                                                    | 15                       |                     |                                |                       |                              | 0.12 | %                  |  |  |  |

|                                        | V <sub>EE</sub> = V <sub>SS</sub> ,                                           | f <sub>IS</sub> = 1kHz S | Sine Wave           |                                |                       |                              |      | %                  |  |  |  |

| -40dB Feedthrough Frequency            | 5 (Note 3)                                                                    | 10                       | 1                   | V <sub>OS</sub> at Common OUT  | 8                     | MHz                          |      |                    |  |  |  |

| (All Channels OFF)                     | V <sub>EE</sub> = V <sub>SS</sub> ,                                           |                          |                     |                                | 10                    | MHz                          |      |                    |  |  |  |

|                                        | $20 Log \frac{V_{OS}}{V_{IS}} = -40 dB$                                       |                          |                     |                                |                       | CD4051                       | 12   | MHz                |  |  |  |

|                                        |                                                                               |                          |                     | V <sub>OS</sub> at Any Channel | 8                     | MHz                          |      |                    |  |  |  |

| -40dB Signal Crosstalk                 | 5 (Note 3)                                                                    | 10                       | 1                   | Between Any 2 Chani            | 3                     | MHz                          |      |                    |  |  |  |

| Frequency                              | $V_{EE} = V_{SS},$ $20 Log \frac{V_{OS}}{V_{IS}} = -40 dB$                    |                          |                     | Between Sections,              | Measured or           | n Common                     | 6    | MHz                |  |  |  |

|                                        |                                                                               |                          |                     | CD4052 Only                    | Measured or nel       | Measured on Any Chan-<br>nel |      | MHz                |  |  |  |

|                                        |                                                                               |                          |                     | Between Any Two                | In Pin 2, Out Pin 14  |                              | 2.5  | MHz                |  |  |  |

|                                        |                                                                               |                          |                     | Sections, CD4053<br>Only       | In Pin 15, Out Pin 14 |                              | 6    | MHz                |  |  |  |

| Address-or-Inhibit-to-Signal Crosstalk | -                                                                             | 10                       | 10<br>(Note 4)      |                                | '                     |                              | 65   | mV <sub>PEAK</sub> |  |  |  |

|                                        | V <sub>EE</sub> = 0, V <sub>S</sub> ;<br>= V <sub>DD</sub> - V <sub>S</sub> ; |                          |                     | 1                              |                       |                              | 65   | mV <sub>PEAK</sub> |  |  |  |

NOTES:

3. Peak-to-Peak voltage symmetrical about  $\frac{V_{DD} - V_{EE}}{2}$

4. Both ends of channel.

# **Typical Performance Curves**

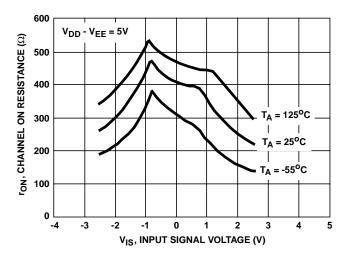

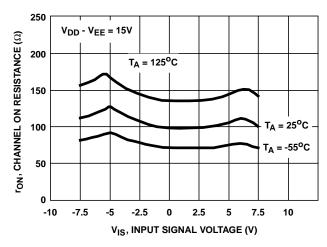

FIGURE 1. CHANNEL ON RESISTANCE vs INPUT SIGNAL VOLTAGE (ALL TYPES)

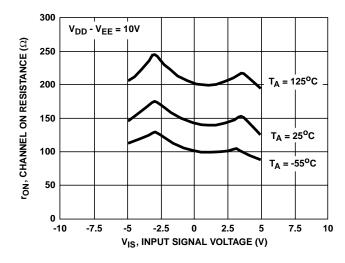

FIGURE 2. CHANNEL ON RESISTANCE vs INPUT SIGNAL VOLTAGE (ALL TYPES)

# Typical Performance Curves (Continued)

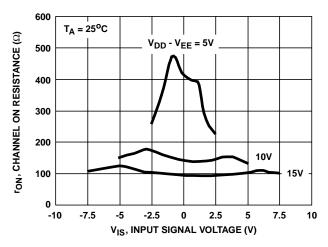

FIGURE 3. CHANNEL ON RESISTANCE vs INPUT SIGNAL VOLTAGE (ALL TYPES)

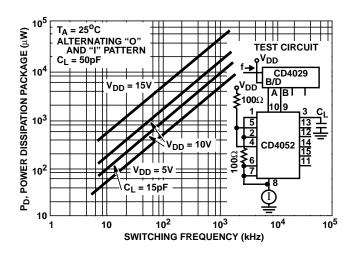

FIGURE 5. ON CHARACTERISTICS FOR 1 OF 8 CHANNELS (CD4051B)

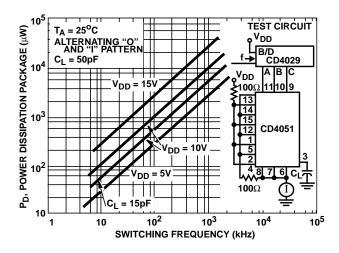

FIGURE 7. DYNAMIC POWER DISSIPATION vs SWITCHING FREQUENCY (CD4052B)

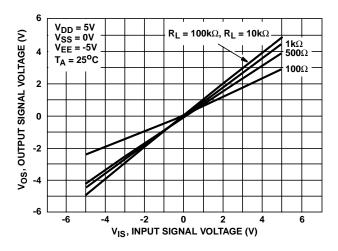

FIGURE 4. CHANNEL ON RESISTANCE VS INPUT SIGNAL VOLTAGE (ALL TYPES)

FIGURE 6. DYNAMIC POWER DISSIPATION vs SWITCHING FREQUENCY (CD4051B)

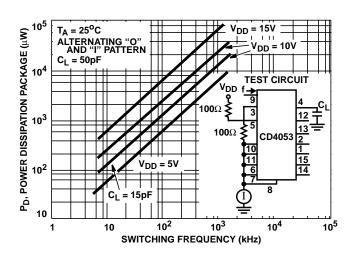

FIGURE 8. DYNAMIC POWER DISSIPATION vs SWITCHING FREQUENCY (CD4053B)

### Test Circuits and Waveforms

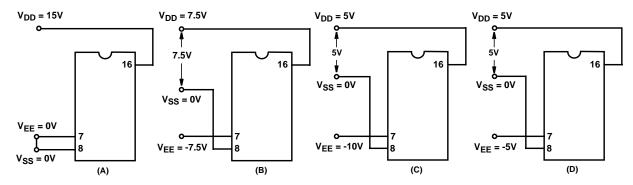

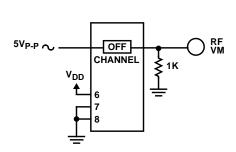

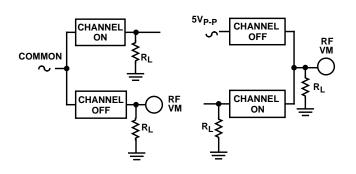

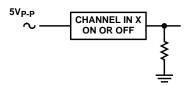

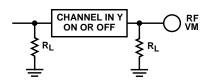

NOTE: The ADDRESS (digital-control inputs) and INHIBIT logic levels are: "0" =  $V_{SS}$  and "1" =  $V_{DD}$ . The analog signal (through the TG) may swing from  $V_{EE}$  to  $V_{DD}$ .

FIGURE 9. TYPICAL BIAS VOLTAGES

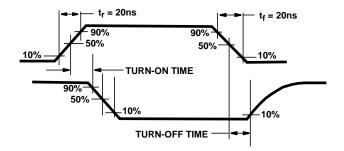

FIGURE 10. WAVEFORMS, CHANNEL BEING TURNED ON (RL = 1k $\Omega$ )

FIGURE 11. WAVEFORMS, CHANNEL BEING TURNED OFF ( $R_L = 1 \text{k}\Omega$ )

FIGURE 12. OFF CHANNEL LEAKAGE CURRENT - ANY CHANNEL OFF

# Test Circuits and Waveforms (Continued)

FIGURE 13. OFF CHANNEL LEAKAGE CURRENT - ALL CHANNELS OFF

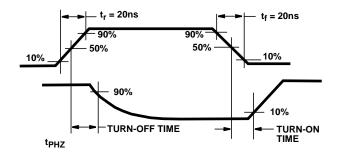

FIGURE 14. PROPAGATION DELAY - ADDRESS INPUT TO SIGNAL OUTPUT

FIGURE 15. PROPAGATION DELAY - INHIBIT INPUT TO SIGNAL OUTPUT

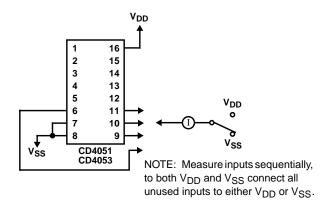

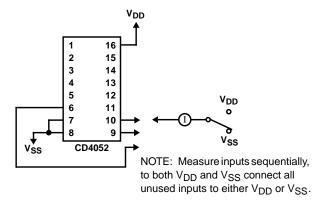

FIGURE 16. INPUT VOLTAGE TEST CIRCUITS (NOISE IMMUNITY)

# Test Circuits and Waveforms (Continued)

FIGURE 17. QUIESCENT DEVICE CURRENT

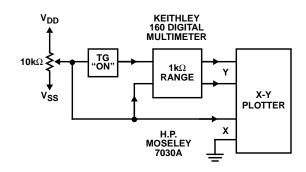

FIGURE 18. CHANNEL ON RESISTANCE MEASUREMENT CIRCUIT

FIGURE 19. INPUT CURRENT

FIGURE 20. FEEDTHROUGH (ALL TYPES)

FIGURE 21. CROSSTALK BETWEEN ANY TWO CHANNELS (ALL TYPES)

FIGURE 22. CROSSTALK BETWEEN DUALS OR TRIPLETS (CD4052B, CD4053B)

# Test Circuits and Waveforms (Continued)

FIGURE 23. TYPICAL TIME-DIVISION APPLICATION OF THE CD4052B

### Special Considerations

In applications where separate power sources are used to drive  $V_{DD}$  and the signal inputs, the  $V_{DD}$  current capability should exceed  $V_{DD}/R_L$  ( $R_L$  = effective external load). This provision avoids permanent current flow or clamp action on the  $V_{DD}$  supply when power is applied or removed from the CD4051B, CD4052B or CD4053B.

FIGURE 24. 24-TO-1 MUX ADDRESSING

### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated