# Power and Performance Tradeoff in LTE Receiver Chains

# **Master Thesis**

Muris Sarajlić

Lund University

A thesis submitted for the degree of

Master of Science

September 2013

# Acknowledgements

First and foremost, I would like to express my sincere appreciation to Professor Ove Edfors for giving me the opportunity to do this master thesis work under his supervision.

A special word of thanks goes also to professors and PhD students at the Analog RF, Data Converters and Frequency Synthesis and Digital ASIC groups at the department of EIT: Professor Pietro Andreani, PhD students Anders Nejdel, Mohammed Abdulaziz, Xiaodong Liu and others for providing me with valuable insights and helpful advice.

I would also like to thank my friends and study colleagues for all the priceless moments we had together, both in school and outside of it. Thanks for all the trips, parties, fikas and long lunches. I hope we will meet again somewhere!

Last but not least, for my parents and my girlfriend Erna: thank you for your love and support. Although you are far away, at every moment I feel like you are right next to me. I love you.

# Abstract

The continuous development and expansion of mobile systems puts increased demand on the mobile receiver designers to deliver circuits that will provide high bitrates, while at the same time the power consumption and battery life should be kept at reasonable levels, and ideally should not increase. Classical radio receiver design techniques are proving hard to meet these conflicting requirements, opening doors for introducing new and different means of designing high performance, high powerefficient receiver circuits.

Following this, newer radio receiver circuits are utilizing today's cheap, fast and power-efficient digital circuits for *digital assistance* and *digital control* of receiver blocks. This thesis focuses on the techniques of digital control and presents a basic investigation of radio receiver block properties that leads to a digital control strategy. The basic idea of digitally controlled radio receivers is to adapt the overall analog and digital processing quality to the current channel properties, with the final goal of saving power. If the receiver is operating in a channel with good quality, then it might be possible to reduce the processing quality of the receiver (introduce more thermal noise, allow increased distortion due to nonlinearity, etc.) by tuning certain parameters of receiver blocks; the output performance should not deteriorate in the process. Power savings then come as the result of decreasing the processing effort of the receiver.

In order to determine the right combination of tunable parameters of receiver blocks that will keep the overall performance above a certain threshold while at the same time consuming least power, two things need to be determined: how does the change of the parameter affect the overall performance, and how does it reflect on the power consumption.

This thesis first investigates appropriate ways of modeling the effects of RF impairments and then finds a way to connect the tunable block parameters through RF impairments with the overall performance; this is accomplished by determining the Error Vector Magnitude (EVM) of each RF impairment source, calculating the total receiver EVM and using the information about thermal noise and EVM to determine the Signal-to-Noise-and-Distortion ratio (SNDR) which serves as the overall channel quality indicator. After this, the behaviour of individual blocks of the direct-conversion receiver is analyzed in terms of a functional dependence between the value of tunable block parameters and power consumption; the analysis is performed through analyzing the tradeoffs between power consumption and performance for each block, as well as for the entire receiver. Finally, using the knowledge about the power and performance behaviour of blocks due to the tuning of block parameters, a simple strategy of digital control is proposed and supported by initial calculations, which show that power consumption savings are possible when using a channel-adaptive, digitally tunable receiver.

# **Table of Contents**

| 1 | Introduction1                                                        |             |  |  |  |

|---|----------------------------------------------------------------------|-------------|--|--|--|

|   | 1.1 Background                                                       | 1           |  |  |  |

|   | 1.2 Thesis goals                                                     | 2           |  |  |  |

|   | 1.3 Thesis outline                                                   | 3           |  |  |  |

| 2 | Overview of RF Impairment Modeling                                   | 4           |  |  |  |

|   | 2.1 RF impairments                                                   | 4           |  |  |  |

|   | 2.1.1 Thermal noise                                                  | 4           |  |  |  |

|   | 2.1.2 Nonlinearity                                                   | 4           |  |  |  |

|   | 2.1.3 Carrier frequency offset (CFO)                                 | 8           |  |  |  |

|   | 2.1.4 Sampling clock offset                                          |             |  |  |  |

|   | 2.1.5 Local oscillator leakage - DC offset                           | 8           |  |  |  |

|   | 2.1.6 I/Q imbalance                                                  | 9           |  |  |  |

|   | 2.1.7 Phase noise                                                    | 9           |  |  |  |

|   | 2.1.8 Quantization noise and clipping                                | 13          |  |  |  |

|   | 2.2 Error vector magnitude                                           |             |  |  |  |

|   | 2.2.1 EVM of phase noise                                             |             |  |  |  |

|   | 2.2.2 EVM of nonlinearities                                          | 17          |  |  |  |

|   | 2.2.3 EVM of quantization and clipping                               | 19          |  |  |  |

|   | 2.2.4 Calculation of EVM for a cascade of impairments                |             |  |  |  |

|   | 2.2.5 EVM as means of calculating SNR degradation and signal-to      |             |  |  |  |

|   | distortion ratio (SNDR)                                              |             |  |  |  |

| 3 | Direct Conversion Receiver - Analog Front End                        | 29          |  |  |  |

|   | 3.1 Introduction                                                     | 29          |  |  |  |

|   | 3.2 Low noise amplifier                                              |             |  |  |  |

|   | 3.2.1 Tunability and its impact on the overall system performance    | e31         |  |  |  |

|   | 3.3 Frequency synthesizers.                                          |             |  |  |  |

|   | 3.3.1 Voltage-controlled oscillator (VCO)                            |             |  |  |  |

|   | 3.3.2 The phase locked loop (PLL) concept                            |             |  |  |  |

|   | 3.3.3 The all-digital phase-locked loop (ADPLL)                      | 41          |  |  |  |

|   | 3.3.4 Tunability and its impact on the overall system performance    |             |  |  |  |

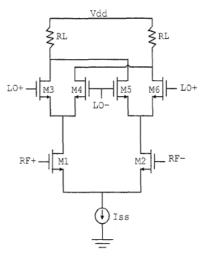

|   | 3.4 Downconversion mixer                                             | 44          |  |  |  |

|   | 3.4.1 Tunability and its impact on the overall system performance    | e45         |  |  |  |

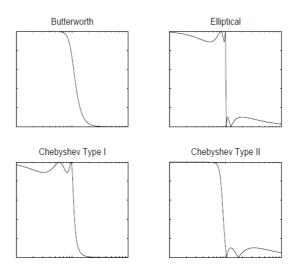

|   | 3.5 Channel select filters                                           | 46          |  |  |  |

|   | 3.5.1 Filter types                                                   | 46          |  |  |  |

|   | 3.5.2 Filter implementations                                         | 47          |  |  |  |

|   | 3.5.3 Tunability and its impact on the overall system performance    | 48          |  |  |  |

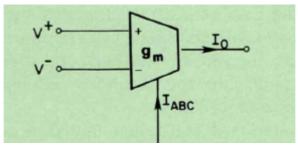

|   | 3.6 Variable gain amplifier (VGA)                                    |             |  |  |  |

|   | 3.6.1 Tunability and its impact on the overall system performance    | e53         |  |  |  |

| 4 | Direct Conversion Receiver - Analog to Digital Conversion and Digita | al Baseband |  |  |  |

|   |                                                                      |             |  |  |  |

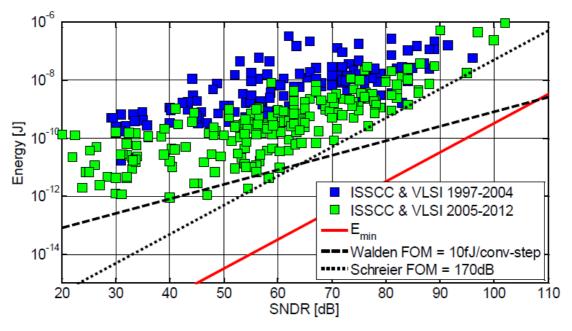

|   | 4.1 Analog to Digital Conversion                                     |             |  |  |  |

|   | 4.1.1 Introduction                                                   |             |  |  |  |

|   | 4.1.2 A brief general overview of different types of ADCs            |             |  |  |  |

|   | 4.1.3 Sigma-delta modulator ADC                                      |             |  |  |  |

|   | 4.1.3.1 Oversampling and noise shaping                               |             |  |  |  |

|   | 4.1.         | 3.2 SD ADC Types                                                      | 57 |  |

|---|--------------|-----------------------------------------------------------------------|----|--|

|   | 4.1.4        | Tunability and its impact on the overall system performance           | 57 |  |

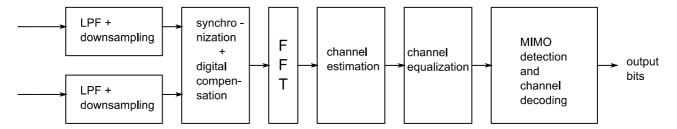

|   |              | ital baseband                                                         |    |  |

|   | 4.2.1        | Introduction                                                          | 60 |  |

|   | 4.2.2        | Structure of the baseband part of a MIMO/OFDM receiver                | 60 |  |

|   | 4.2.3        | Tunability and its impact on the overall system performance           |    |  |

| 5 | 5 1          |                                                                       |    |  |

|   |              |                                                                       |    |  |

|   |              | al tradeoffs                                                          |    |  |

|   | 5.1.1        | LNA.                                                                  |    |  |

|   | 5.1.2        | Frequency synthesizer                                                 |    |  |

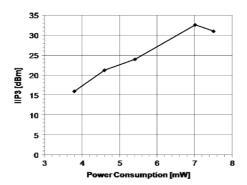

|   | 5.1.3        | Downconversion mixer                                                  |    |  |

|   | 5.1.4        | Channel select filter.                                                |    |  |

|   | 5.1.5        | Variable gain amplifier                                               |    |  |

|   | 5.1.6        | ADC.                                                                  |    |  |

|   | 5.1.7        | Digital baseband                                                      |    |  |

| ( |              | bal tradeoffs                                                         |    |  |

| 6 | -            | son of fixed and channel-adaptive approaches in radio receiver design |    |  |

|   |              | oduction                                                              |    |  |

|   |              | ed design                                                             |    |  |

|   | 6.2.1        |                                                                       |    |  |

|   | •            | 1.1 LNA.                                                              |    |  |

|   | 6.2.         |                                                                       |    |  |

|   | 6.2.<br>6.2. |                                                                       |    |  |

|   | 6.2.<br>6.2. |                                                                       |    |  |

|   |              | 1.6 ADC                                                               |    |  |

|   |              | Receiver gain and noise/distortion budgets                            |    |  |

|   |              | Innel-adaptive design                                                 |    |  |

|   | 6.3.1        | Receiver block designs                                                |    |  |

|   | 6.3          | e e                                                                   |    |  |

|   | 6.3          |                                                                       |    |  |

|   |              | Calculation and analysis of optimal block parameters                  |    |  |

| 7 |              | ions and future work                                                  |    |  |

| ' |              | nce list                                                              |    |  |

|   | 101010       |                                                                       |    |  |

# **1** Introduction

# 1.1 Background

In recent years, the world has witnessed an incredibly fast development of mobile phone systems and devices; by observing only the communication part, a multifold increase in transmission bitrates enabled support for an increased number of services and finally enabled a multifold increase in overall quality of user experience. Current 4G - LTE (Long Term Evolution) systems are designed to provide maximum downlink and uplink bitrates of 100 Mbps and 50 Mbps, respectively, whereas the LTE-Advanced (LTE-A) systems, which are currently in development, should provide transmission bitrates of 1 Gbps in the downlink and 500 Mbps in the uplink ("downlink" and "uplink" are referred to the user equipment - mobile device). Increased bitrates inevitably cause an increase in power consumption in receiver circuits, which reduces the battery life of the mobile device. Therefore, there is a big challenge imposed on transceiver designers to deliver power-efficient analog and digital circuits that will still have processing power needed to support the nominal bitrates.

Luckily, the development of mobile systems ran in parallel to the development of digital circuit technology, which has seen a continuous reduction of the size of fundamental components - integrated transistors, as well as an increase of processing speed. This development not only serves to support the increased demand on processing power in the digital domain, but can also be cleverly used to improve the performance of integrated analog blocks of the receiver. This can be implemented in two ways:

- By using digital signal processing techniques to correct errors induced in the analog part of the receiver: this can be done either in the analog part at the place of the error generation ("clean RF" approach) or in a special block for digital correction of impairments situated at the front of the digital baseband part of the receiver (the "dirty RF" approach);

- By designing analog receiver blocks to be reconfigurable and digitally tunable. Values of one or several parameters of an analog block are allowed to change during operation, thus affecting the peformance and power consumption of the block. The idea is to adjust the performance of the block to current overall performance requirements, *e.g.* reduce its performance quality if a high quality is not needed; due to inherent tradeoffs between power consumption and performance quality for the blocks, a reduction of performance quality would directly result in savings in power consumption. Analog blocks would be controlled by an external digital global controller which uses the information about current performance requirements to set the tunable parameters of analog blocks to proper values.

Receiver design employing digital control can go one step further, so the controller not only controls analog, but also *digital* blocks, because there is room for benefitting from power/performance tradeoffs in the digital domain also.

Determining the proper values for tunable parameters of analog and digital blocks is not a trivial task. Reconfiguring one block might influence the performance of other blocks, so we always have to have the insight in how the *overall* receiver chain performance is influenced by tuning one

parameter. Furthermore, it might be possible to save more power by reconfiguring one block than by reconfiguring some other block. It is obvious that the values of tunable parameters are obtained by solving an *optimization* problem.

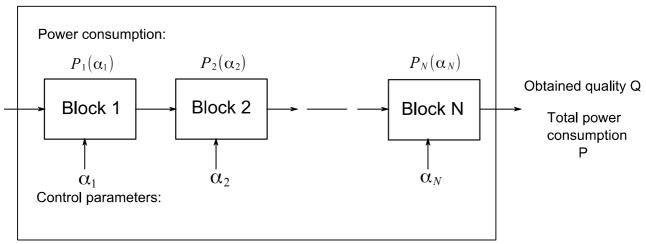

This optimization problem can be formulated with the help of a generic model of the radio receiver chain given in Figure 1.

*Figure 1: Generic receiver chain model*

The parameter  $\alpha_k$  is used to tune the performance and power consumption of each block. It can be assumed that the overall power consumption is the sum of power consumptions of individual blocks

$$P(\alpha_{1,}\alpha_{2,}...\alpha_{N}) = \sum_{k=1}^{N} P_{k}(\alpha_{k})$$

(1.1)

The overall performance quality (measured as BER, BLER, or in terms of equivalent SNR, or other performance indicators) is a function of tunable parameters  $\alpha_k$  that is generally more complex than a simple linear combination of performance quality for each individual block. This is due to the heavy influence that certain block parameters exert on the performance of other blocks. The overall performance is also a function of external variables, like interference and fading that can be subsumed in an environment variable  $\Theta$ , so  $Q = Q(\alpha_1, \alpha_2, \dots, \alpha_N, \Theta)$ . The task of finding the optimal vector of parameters  $[\alpha_1, \alpha_2, \dots, \alpha_N]_{opt}$  is then the task of solving the optimization problem

minimize

$$P(\alpha_{1,}\alpha_{2,}...\alpha_{N})$$

subject to  $Q(\alpha_{1,}\alpha_{2,}...\alpha_{N},\Theta) \ge Q_{bound}$ , (1.2)

where  $Q_{bound}$  is a bounding value for the overall performance.

## 1.2 Thesis goals

The objectives of this master thesis work are:

- 1. Finding the appropriate tunable parameters for each block of the receiver chain;

- 2. Analyzing the influence tunable parameters have on power consumption and performance quality of the chosen block;

- 3. Establishing the connections between individual parameters that will determine the overall

performance quality Q;

- 4. Using the information obtained under steps 1 3, setting up a framework for solving the optimization problem (1.2). Power consumption and performance quality models found under 2. and 3. should be tractable have reasonable complexity that will enable relatively simple solving of the optimization problem, while at the same time the precision of the model should not be reduced;

- 5. Solving the optimization problem (1.2) by using the developed framework and proving that power consumption can be reduced by adapting the receiver blocks to the demands for performance quality.

# 1.3 Thesis outline

This thesis work has the following outline:

- **Chapter 2** presents an analysis of RF impairments and their models. Also, the Error Vector Magnitude (EVM) is introduced as a unifying model of RF impairments' impact on the overall performance quality of the receiver system; this provides a tractable (and at the same time reasonably accurate) model of the quality function Q from (1.2);

- **Chapter 3** describes the functionality and design of the analog blocks of the receiver chain, lists the possible tunable parameters of these blocks and analyzes their impact on power consumption and performance;

- **Chapter 4** provides the same type of analysis given in Chapter 3, but applied to the mixed-signal and digital parts of the receiver;

- **Chapter 5** gives a concise overview of information gathered about tunable parameters and local and global power/performance tradeoffs;

- In **Chapter 6**, the EVM based framework is applied to calculate the tunable parameters of a channel-adaptive receiver; this receiver is compared in terms of power consumption with a non-adaptive design.

- Finally, **Chapter 7** gives a conclusion of the work, as well as possible improvements and guidelines for future work.

# **2** Overview of RF Impairment Modeling

Real-life radio receivers suffer from performance degradation caused by thermal noise, as well as various signal degradations caused by component and system imperfections. This chapter will give a brief overview of these degradations, analyze their impact on multicarrier systems and introduce a unifying approach of measuring their effect.

## 2.1 **RF** impairments

#### 2.1.1 Thermal noise

Thermal noise is generated by resistive components inside receiver blocks and is caused by the chaotic movement of electrons. The power of thermal noise is given by

$$P_n = kTB \quad , \tag{2.1}$$

where k is Boltzmann's constant, T is the temperature in Kelvins and B the bandwidth of the device.

A measure of the influence of thermal noise on the SNR degradation is the *noise figure* F, defined as

$$F = \frac{SNR_{\rm in}}{SNR_{out}} \quad . \tag{2.2}$$

For a cascade of noisy blocks with gains  $G_i$  and noise figures  $F_i$ , the equivalent noise figure for the cascade is given by the *Friis' formula*

$$F_{total} = F_1 + \frac{F_2 - 1}{G_1} + \frac{F_3 - 1}{G_1 G_2} + \dots + \frac{F_N - 1}{G_1 G_2 \cdots G_{N-1}} \quad .$$

(2.3)

The total noise figure enables us to represent the noise generated in the whole receiver by a single noise source with power equal to

$$P_{n,total} = kTBF_{total} \quad . \tag{2.4}$$

#### 2.1.2 Nonlinearity

Although modeled as linear when dealing with input signals of small amplitude, most receiver blocks actually exhibit nonlinear behaviour with arbitrary levels of input signals. Significant causes of nonlinearity are saturation of active electronic elements and component mismatch.

One of the commonly used ways to represent nonlinearities is by using the polynomial

input-output model [1]:

$$y(t) \approx \alpha_1 x(t) + \alpha_2 x^2(t) + \alpha_3 x^3(t)$$

(2.5)

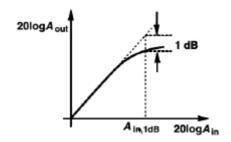

Figure 2: 1 dB compression point ([1])

A majority of RF devices of interest has a so-called "compressive" characteristic with  $\alpha_3 < 0$ . This means that the amplitude gain *decreases* with the increase of the input signal amplitude *A*, or as it is popularly put, the device "goes into compression" for sufficiently high input signal levels (or powers). The compression is characterized by the *1 dB compression point*

$(CP_{1dB})$  - the input signal power for which the actual output deviates from the linear one for 1 dB. It can be shown that (for a single sinusoidal tone at the output) the input signal amplitude at the 1 dB compression point is

$$A_{CPIdB} = \sqrt{0.145 \left| \frac{\alpha_1}{\alpha_3} \right|} \tag{2.6}$$

A phenomenon analogous to compression occurs when the wanted signal is joined by a strong interferer. In the case of a compressive nonlinear device, the interferer will reduce the gain, effectively "drowning" the wanted signal. This phenomenon is called "desensitization" or "blocking", and therefore a more common term for a single interferer in RF parlance is "blocker".

If the single-tone interferer is substituted by an amplitude-modulated signal, the wanted signal modulates this signal (and additionally broadens its spectrum), so in the end the interferer and wanted signal spectra overlap. This phenomenon is called "cross-modulation".

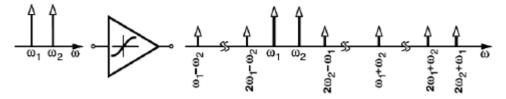

Next we analyze the situation when the signal is accompanied not by one, but by two interferers (a very common situation in real-life radio systems). The interferer tone pair can be modeled as  $x(t)=A_1\cos(\omega_{int,1}t)+A_2\cos(\omega_{int,2}t)$ . The ouput of the nonlinear device (2.5) contains, other than the components at frequencies  $\omega_{int,1}$  and  $\omega_{int,1}$ , a DC component and 10 additional components at various frequencies., given in Figure 3.

Figure 3: Various intermodulation products of the two interferers [1]

Of all the intermodulation products created by the linearity, the ones sitting at frequencies  $(\omega_{int,2}-2\omega_{int,1})$  and  $(\omega_{int,1}-2\omega_{int,2})$  (the so-called "third-order intermodulation products", or IM3) present the highest danger to the wanted signal: if the wanted signal has, *e.g.* frequency  $\omega_0 = 2\omega_{int,1} - \omega_{int,2}$ , one of these newly created frequency components will directly interfere with

it. This scenario is not at all uncommon in real-life radio systems.

A measure of the level of influence the third-order nonlinearities have in the system is the *third-order intercept point* (IP3). The input IP3 is defined as the input signal level for which the system output (clear of any influence of nonlinearities) is equal to the IM3, and is calculated as

$$A_{IIP3} = \sqrt{\frac{4}{3} \left| \frac{\alpha_1}{\alpha_3} \right|} \tag{2.7}$$

The device goes into saturation long before the  $A_{IIP3}$ , so it is not a directly measurable value. It can be shown that  $A_{CP1dB}$  is about 10 dB lower than  $A_{IIP3}$ .

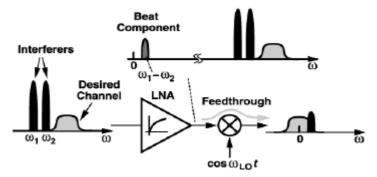

*Figure 4: Impact of IM2 on the direct-conversion receiver* [1]

In addition to IM3, direct-conversion receivers are vulnerable to IM2. The description of this influence is somewhat more involved than the simple mixing effect of IM3. As it is described in [1], the imbalance between the mixers in the I and Q branches of the receiver can cause a DC component to accompany the carrier frequency tone, thus allowing any baseband frequency content to pass "through" the mixer without altering its carrier frequency. On the other hand, if the two interferers are close in frequency, their order - two intermodulation product (IM2) at  $(\omega_{int,1}-\omega_{int,2})$  falls into the baseband, and combined with mixer mismatch can interfere with the downconverted wanted signal. This scenario is described in Figure 4.

The measure of impact of the IM2 is the *second-order intercept point* (IP2), defined as the input level for which the IM2 is equal to the distortion-free input, and calculated simply as

$$A_{IIP2} = \frac{\alpha_1}{\alpha_2} \tag{2.8}$$

A phenomenon observed when analysing the effects of nonlinearities in frequency domain is *spectral regrowth*. To describe it, it is best to consider the polynomial nonlinearity model and an arbitrary lowpass input signal  $x_L(t)$ . Assuming just the third-order nonlinearity, the output of a nonlinear system in the time domain can be written in the form [2]

$$y_L(t) = x_L(t) + \alpha_3 x_L^2(t) x_L^*(t)$$

, (2.9)

where subscript L denotes that the signal is lowpass (baseband), and \* in the superscript denotes the complex conjugate. If we assume x(t) is deterministic, the frequency-domain version of (2.9) is

$$Y_{L}(f) = X_{L}(f) + \alpha_{3} X_{L}(f) * X_{L}(f) * X_{L}^{*}(-f) \quad , \qquad (2.10)$$

where the operator \* denotes convolution. As the spectrum of the signal is convoluted with itself, the signal experiences a broadening of the spectrum (signal power leaks into adjacent bands).

The coefficients of the polynomial nonlinearity model are usually hard to obtain from measurement. Based on the observation that the nonlinearity depends only on the input signal amplitude (not the phase) [2], two metrics are introduced that describe the mapping from input

amplitude to output amplitude and to output phase. These metrics are called AM-to-AM and AM-to-PM characteristics, respectively. For a complex baseband signal,  $x_L(t) = a_L(t)e^{j\phi(t)}$ , the AM-AM characteristic can be denoted as  $f(a_L(t))$  and the AM-PM as  $g(a_L(t))$ . The total output signal can then be expressed as

$$y_{I}(t) = f(a_{I}(t))e^{j(\phi(t) + g(a_{L}(t)))}$$

(2.11)

Some parameters of these functions can be determined by measurements, and then the complete characteristics are derived empirically from the measurement results.

It has been observed ([3], [4], [5]) that the effects nonlinearities have on the OFDM signal exhibit themselves as a rotation and attenuation of the signal constellation, plus an addition of a noise term. If we observe this influence through the AM-AM/AM-PM model of the nonlinearity, we can conclude that:

- The rotation of the constellation comes from the AM-PM characteristic. If  $g(a_L(t))=0$ , there is no rotation. This is the case for some very common nonlinear models, like the baseband polynomial model for a nonlinear device without memory [6], as well as hard and soft limiter models.

- The attenuation and noise factor are due to the AM-AM characteristic. The subcarriers produce intermodulation products that interfere with other subcarriers, causing intercarrier interference (ICI), which appears in the constellation diagram in the form of noise "clouds" around constellation points.

In [5], these effects have been expressed in a form of a mathematical model, and the validity of this model has been proven. The model can be formulated as

$$Y_{k} = \mu_{NL} X_{k} + D_{k,NL}$$

, (2.12)

where  $Y_k$  and  $X_k$  are the received and sent OFDM symbols for the *k*th subcarrier respectively,  $\mu_{NL}$  is a complex gain factor not depending on the subcarrier index (describing the attenuation and rotation of the whole constellation) and  $D_{k,NL}$  is a nonlinear distortion (NLD) noise term; the NLD noise is not correlated with the signal at the nonlinear device input. For a large number of subcarriers *N*, this noise can be assumed to be complex Gaussian. Analytical expressions for  $\mu_{NL}$ and the variance of  $D_{k,NL}$ ,  $\sigma_{NL}^2$  expressed via AM-AM and AM-PM characteristics are given in [5].

Using the MATLAB code from [2], the influence of a third-order nonlinearity on an OFDM system using QPSK is demonstrated and shown in Figure 5. The IIP3, expressed as a power measure on a 50 ohm load, is equal to -5 dBm.

Figure 5: Influence of a third-order nonlinearity on the OFDM system

As said before, the third-order memoryless polynomial nonlinarity model does not introduce any phase shift and therefore there is no observed rotation of the constellation. There is, however, an attenuation (the constellation gets "compressed" - its points come closer together.

#### 2.1.3 Carrier frequency offset (CFO)

In direct conversion receivers, CFO is defined as the offset between the local oscillator frequency and the carrier frequency. For an OFDM signal, the CFO exhibits itself as a phase shift common to all subcarriers (rotation of the constellation), plus a noise-like additive component coming from intercarrier interference (FCO causes a loss of orthogonality between subcarriers).

#### 2.1.4 Sampling clock offset

All clocks and local oscillators in a receiver usually use a single reference oscillator (crystal oscillator). Therefore, any drift of the crystal oscillator that causes the CFO will also cause a sampling clock offset in the ADC. The impact of the sampling clock offset on an OFDM signal is similar to the one CFO has, with additional amplitude distortion.

#### 2.1.5 Local oscillator leakage - DC offset

Due to imperfections of integrated electronic components and on-chip manufacturing process, a certain amount of local oscillator signal "leaks" to other parts of the analog front-end. One part of the leaked signal goes through the antenna, causing desensitization of the nearby receivers operating in the same band. It can also bounce off neighboring objects, get received and downconverted to baseband; because of relative movement of the receiver, this can result in a *slowly time-varying DC offset*. Another part of the leaked signal returns towards the mixer and mixes with itself, creating a *static DC offset* component that interferes with the downconverted

wanted signal. This offsets the signal at the input of the ADC, reducing its dynamic range [2].

#### 2.1.6 I/Q imbalance

If the I and Q branches of the direct conversion receiver don't have same gains and/or phases, we say that I/Q imbalance occurs. There are three main causes of the I/Q imbalance [1]:

- errors in the 90° phase shift circuit

- mismatch of the mixers

- mismatch of baseband components (baseband filters and ADCs)

It can be shown that, due to I/Q imbalance, the baseband signal gets scaled and interferes with a scaled complex conjugate version of itself. If observed in frequency domain

$$X_{LP}(f) = \alpha_R X_L(f) + \beta_R X_L^*(-f)$$

(2.13)

we see this implies that the positive part of the spectrum overlaps with the scaled negative ("mirrored") part of itself. This effect is observed equally in single- and multicarrier systems; in multicarrier systems this implies overlapping of a subcarrier with a "mirrored" subcarrier.

#### 2.1.7 Phase noise

Local oscillator frequency in real-life receivers is not a pure sine wave. The local oscillator exhibits random changes of the instantaneous frequency, which is equivalent to a random phase shift. The local oscillator signal can therefore be modeled as

$$x_{osc}(t) = e^{j2\pi f_{c}t} e^{j\phi(t)}$$

(2.14)

where  $\phi(t)$  is the phase noise process. Phase noise can be also described as a *random phase modulation* of the signal of the local oscillator, which transfers directly to a random phase modulation of the wanted signal. The received baseband signal is thus

$$y_L(t) = x_L(t)e^{j\phi(t)}$$

(2.15)

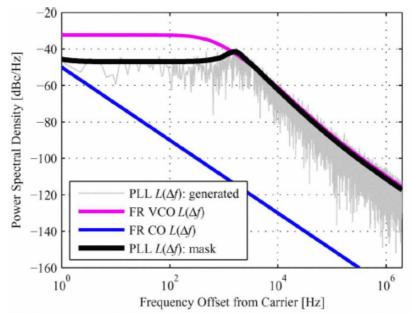

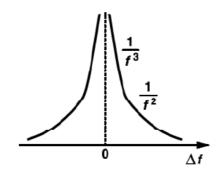

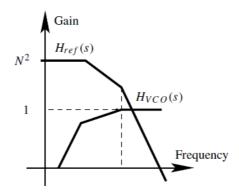

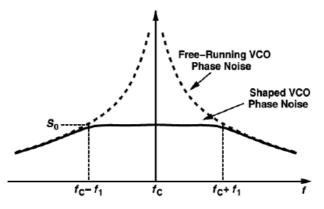

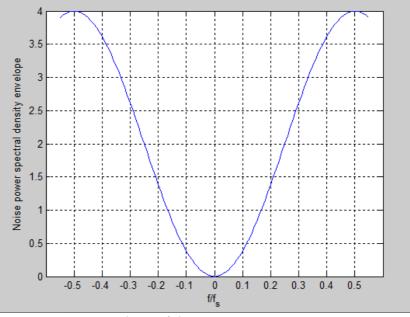

Phase noise is usually characterized by its one-sided power spectral density (PSD)  $L_{\phi}(f)$ . For free-running oscillators, the phase noise is modeled as a Wiener process with a Lorentzian PSD ([1], [7], [8]). However, most receivers use phase locked loop (PLL)-based frequency synthesizers for downconversion, and the PSD in PLL is a rather intricate function of various white and colored noise sources in the voltage-controlled oscillator (VCO) and the reference cristal oscillator (CO), as well as the transfer function of the PLL ([1], [7], [8]). An example of a resulting phase noise "mask" is shown in Figure 6.

Figure 6: An example of a PLL phase noise mask, together with freerunning VCO and CO PSDs shown for comparison [7]

The measured phase noise PSD is expressed relative to the carrier power.

The total power of the phase noise is

$$\sigma_{\phi}^2 = 2 \int_{0}^{f_B} L_{\phi}(f) df$$

, (2.16)

where  $f_B$  is the receiver bandwidth (determined by the baseband channel select filter).

The effect of phase noise in OFDM systems has been analyzed in [9] and [10]. Following the analysis presented in these papers, we can first start by recognizing the time - domain symbols at the OFDM modulator output as

$$x_n = \sum_{k=0}^{N-1} X_k e^{j2\pi \frac{k}{N}n} , \qquad (2.17)$$

where  $X_k$  are frequency-domain data symbols. To simplify things, the channel is considered flat and with unity gain. Only the influence of phase noise is considered, and the received samples affected by the PN are then given as

$$r_n = x_n e^{j\phi(n)} \tag{2.18}$$

where  $\phi(n)$  is the sampled phase noise process  $\phi(t)$ . The OFDM demodulator performs the DFT, generating

$$Y_{k} = \frac{1}{N} \sum_{m=0}^{N-1} r_{m} e^{-j2\pi \frac{m}{N}k} \quad .$$

(2.19)

Assuming that  $\phi(n)$  is small (a valid assumption for most state-of-the-art frequency synthesizers), we have

$$e^{j\phi(n)} \approx 1 + j \cdot \phi(n)$$

. (2.20)

Using this assumption, we obtain

$$Y_{k} = X_{k} + \frac{j}{N} \sum_{r=0}^{N-1} X_{r} \sum_{m=0}^{N-1} \phi(m) e^{j 2\pi \frac{(r-k)}{N}m} = X_{k} + E_{k} \quad , \qquad (2.21)$$

which implies that the received symbol is equal to the sent symbol, plus an error term  $E_k$ . This error term is analyzed for two cases:

• when r = k:

$$E_k = j X_k \Phi \tag{2.22}$$

with  $\Phi$  being the average of the phase noise across all the samples:

$$\Phi = \frac{1}{N} \sum_{n=0}^{N-1} \phi(n)$$

(2.23)

We can conclude that all subcarriers experience the same amount of phase shift (from (2.20), (2.21) and (2.22),  $Y_k = X_k + jX_k \Phi = X_k (1+j\Phi) \approx X_k e^{j\Phi}$ ) equal to  $\Phi$ . This phase shift is referred to as the *common phase error* (CPE). As OFDM-based systems like LTE employ pilot-based channel estimation and equalization schemes, CPE is removed - to a certain extent - in the process of channel equalization.

• when  $r \neq k$  :

$$E_{k} = ICI_{k} = \frac{j}{N} \sum_{\substack{r=0,\\r\neq k}}^{N-1} X_{r} \sum_{n=0}^{N-1} \phi(n) e^{j2\pi \frac{(r-k)}{N}n}$$

(2.24)

As it can be read from this expression, symbols from every subcarrier (multiplied by a complex gain factor) interfere with each of the remaining subcarriers. Phase noise therefore introduces a loss of orthogonality between subcarriers, or ICI.

If the phase noise is narrowband compared to the subcarrier bandwidth (its samples are very correlated, if we observe them in time domain) then it doesn't change much across one set of N samples and  $\Phi \neq 0$ . This means that CPE is the dominant error mechanism for narrowband phase noise. CPE can be removed in the process of pilot-assisted channel estimation and equalization (same as in the case of carrier frequency offset).

On the other hand, if the phase noise is broadband, it is fairly uncorrelated across the set of N samples and it averages out to 0,  $\Phi \approx 0$ . This means that for broadband phase noise CPE is negligible and ICI is the dominant error mechanism.

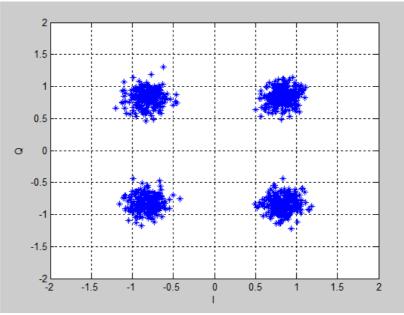

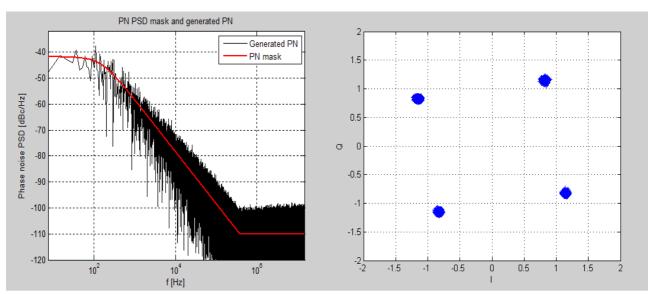

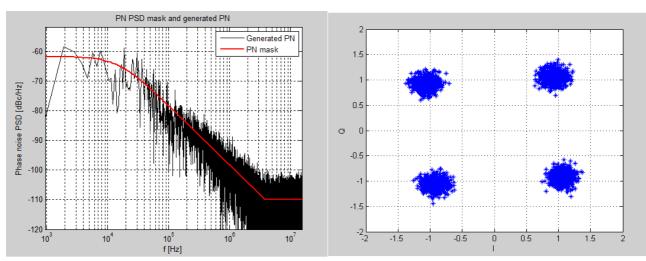

Figure 7: Phase noise spectrum (left) and a QPSK constellation diagram (right): PN 3 dB bandwidth = 150 Hz

*Figure 8: Phase noise spectrum (left) and a QPSK constellation diagram (right): PN 3 dB bandwidth = 15 kHz*

The presented conclusions are illustrated in the Figures 7 and 8. The simulation of the phase noise effect in multicarrier system was done in MATLAB, using the code provided in [2]. The number of subcarriers was N = 2048 and the sampling frequency  $F_s = 30.72 MHz$ , corresponding to the highest channel bandwidth of LTE. The total integrated phase noise is the same for both scenarios, equal to -15 dBc. The chosen spectral mask has a Lorentzian shape for low and medium frequencies and a noise floor for higher frequencies. The 3 dB bandwidth of the PN in the first case is 150 Hz, and in the second case 15 kHz.

When a receiver has a noisy local oscilator and a strong out-of-band interferer, the oscillator mixes with the wanted signal as well as the interferer. Aside from a randomly phase modulated wanted signal, this also results in spreading the noisy "skirt" of the modulated interferer across the bandwidth of the wanted signal, reducing the total SNR. This phenomenon is known as *reciprocal mixing*.

#### 2.1.8 Quantization noise and clipping

Errors due to quantization and clipping are introduced in the analog-to-digital converter (ADC), the device that serves as a bridge between analog and digital domains of the receiver. This device takes an analog signal and discretizes it both in time (by sampling at discrete time instants) and in amplitude (by mapping a continuous value of the amplitude to the nearest discrete quantization level). The number of quantization levels depends on the number of quantization bits *n* and is finite, implying that all signal levels outside of the range  $(-A_{max}, A_{max})$  are assigned to the outermost quantization levels, introducing distortion due to the clipping of the signal. Errors due to quantization can be modeled as additive, white noise uniformly distributed over [-q/2, q/2], where *q* is the quantization step size:

$$q = \frac{2A_{max}}{2^n - 1}$$

(2.25)

The mean value of quantization noise is 0, and the quantization noise variance is

$$\sigma_e^2 = \frac{q^2}{12} \quad . \tag{2.26}$$

Combining with the expression for q, we get

$$\sigma_e^2 = \frac{A_{max}^2}{3(2^n - 1)^2} \approx \frac{A_{max}^2}{3 \cdot 2^{2n}} , \qquad (2.27)$$

with the approximation being valid for n > 3.

An important performance metric of ADCs is the *dynamic range* DR, measured with a sinusoidal input signal and defined as

$$DR = \frac{A_{max}^2}{2P_N} \quad , \tag{2.28}$$

where  $P_N$  is the general quantization noise power (can be different from the pure quantization noise variance because quantization noise can be shaped and filtered). DR for an ideal Nyquist - rate ADC is given as [44]

$$DR \approx 6.02n + 1.76[dB] \tag{2.29}$$

We can now define another ADC performance metric, namely the *ideal effective number of bits* (ENOB) as the bit precision of an ideal Nyquist-rate ADC having the dynamic range DR:

$$ENOB_{id} = \frac{DR(dB) - 1.76}{6.02}$$

(2.30)

In a real-world ADC, thermal noise and distortion will also affect the performance and have to be taken into account. The ENOB for a real-world ADC is therefore defined by taking the SNDR (signal-to-noise-and-distortion ratio) into account:

$$ENOB = \frac{SNDR(dB) - 1.76}{6.02} \tag{2.31}$$

and this definition of ENOB is the one most commonly used in characterizing ADCs.

Quantization and clipping in OFDM systems can be assumed to have the effect of additive noises with non-Gaussian distributions. The received OFDM symbol is therefore

$$Y_{k} = X_{k} + N_{k}^{q} + N_{k}^{c}$$

(2.32)

where  $N_k^q$  and  $N_k^c$  are quantization and clipping noise terms with variances  $\sigma_q^2$  and  $\sigma_c^2$ .

## 2.2 Error vector magnitude

Error vector magnitude (EVM) emerged as a standard performance measure in the analysis and synthesis of RF receiver systems. Using EVM, it is possible to quantify the level of degradation that a certain RF impairment introduces in the signal, to compare these levels of degradation and, using certain assumptions, to combine them in a "degradation budget" calculation for the whole receiver chain - properties not readily obtainable from using BER simulation curves. Although the EVM was traditionally used as a performance measure for the transmitted signals, its attractive properties (and especially the one offering the possibility of creating an EVM budget) point out to EVM as a performance indicator of choice used in the power-optimized RF receiver design.

For a set of N measured symbols with a single modulation scheme being used during the measurement period, the EVM is defined as [11]

$$EVM = \sqrt{\frac{\frac{1}{N}\sum_{k=1}^{N} |Y_{k} - X_{k}|^{2}}{\frac{1}{N}\sum_{k=1}^{N} |X_{k}|^{2}}}$$

(2.33)

where  $Y_k$  are the received symbols (constellation points) and  $X_k$  are the ideal received symbols (without the influence of signal degradation or noise). The quantity  $1/N \sum_{k=1}^{N} |Y_k - X_k|^2$ can be recognized as the mean error vector power ( $|Y_k - X_k|$  is the distance between the distorted and ideal constellation points, or an error vector) and the quantity  $1/N \sum_{k=1}^{N} |X_k|^2$  is the mean reference signal power  $P_s$ .

If the distortion can be modeled as an uncorrelated additive noise term  $D_k$  with variance  $\sigma_{dist}^2$

$$Y_k = X_k + D_k \tag{2.34}$$

the EVM can be simply expressed as [12]

$$EVM \approx \sqrt{\frac{\sigma_{dist}^2}{Ps}} = \frac{1}{\sqrt{SNR}}$$

(2.35)

The uncorrelated additive noise model of the distortion allows for a very simple and elegant way of combining the EVMs related to different distortion sources into a total EVM. If we assume that there are K distortion sources in the receiver chain, that the distortions can be modeled as AWGN and that there is no correlation between individual distortion sources, we have [13]:

$$EVM_{total}^{2} = \frac{\sigma_{dist,total}^{2}}{P_{s}} = \frac{\sum_{k=1}^{K} \sigma_{dist,k}^{2}}{P_{s}} = \sum_{k=1}^{K} EVM_{k}^{2} , \qquad (2.36)$$

or simply

$$EVM_{total} = \sqrt{\sum_{k=1}^{K} EVM_{k}^{2}} = \sqrt{\sum_{k=1}^{K} \frac{1}{SNR_{k}}} \quad .$$

(2.37)

The effects of a large number of RF impairments can be cancelled or compensated in the receiver. This is achieved by using two possible approaches:

- Using DSP algorithms for estimation and correction of the errors induced in the RF. The processing takes place in digital baseband, right before the baseband MIMO-OFDM detection block. This approach is referred to as "dirty RF" (the analog signal is left "dirty" and "cleaned" only in the digital baseband)

- Using DSP algorithms and digital tuning of the parameters of analog blocks to correct/cancel/reduce the RF impairment effects *at the spot*, in the very analog block where they are generated. This is the so-called "clean RF" approach (the RF signal is "cleaned" already in the analog domain and arrives "clean" to the digital baseband).

A number of "dirty RF" algorithms have been developed for use in OFDM systems. They mostly target the deterministic or time-invariant RF impairments (carrier frequency offset, DC offset, I/Q imbalance and sampling clock offset). Some of these algorithms are presented in [14], [15], [16] to list only a few. Some "dirty RF" algorithms are also described in [2].

With the final goal of reducing the complex and intricate set of RF impairment effects in the receiver to a tractable one that can be used in a simple power-performance tradeoff analysis, we introduce a series of assumptions. These assumptions will be used later in the derivation of the EVM for the entire receiver chain.

- It is assumed that the effects of the four deterministic RF impairments are corrected by "dirty RF"; thus, the remaining distortion comes from phase noise, nonlinearities and quantization/clipping.

- In OFDM systems using pilot symbols for channel estimation and synchronization (LTE being one of these systems), the compensation of the common phase rotation and/or attenuation due to PN and nonlinear compression comes as a by-product of frequency-domain channel estimation and equalization (baseband channel estimator sees and corrects the overall constellation rotation and attenuation due to the transmission channel, PN and compression). Additional compensation of the attenuation caused by nonlinearities can be performed by the automatic gain control (AGC) in the analog RF part of the receiver. The AGC senses the instantaneous power level and acts on it with a final goal of delivering a constant power level at the input of the ADC. This way the power variations due to compression get compensated together with other channel power variations.

This then leaves us just with the additive noise due to PN, quantization/clipping and compression. (We can additionally assume for now that out-of-band blockers are not present; this leaves the connected effects, like desensitization, reciprocal mixing and noise folding in the ADC out of the analysis. However, a more thorough analysis will have to deal with blocker-induced effects because blockers are an omni-present and serious problem). The overall RF impairment influence of the performance can then be simply calculated using (2.37).

We now turn to analyzing the EVMs for the most critical RF impairments.

#### 2.2.1 EVM of phase noise

For the derivation of EVM for the phase noise, we first assume perfect channel estimation and ZF equalization in the receiver; this will perfectly derotate the signal constellation, rendering CPE = 0. Using (2.21), (2.22) and (2.24), the received symbol  $Y_k$  can be written as

$$Y_k \approx X_k e^{j\Phi} + ICI_k \tag{2.38}$$

and the equalized received symbol is then

$$Y_k^{(e)} \approx X_k + ICI_k e^{-j\Phi} \quad . \tag{2.39}$$

This leaves us just with ICI, which can be modeled as complex, circularly symmetric Gaussian noise (if the number of subcarriers N is large enough). Following the derivation in [17], the power of the "ICI noise" is

$$P_{ICI} = var\left\{e^{-j\Phi}e^{j\pi/2}\frac{1}{N}\sum_{\substack{r=0,\\r\neq k}}^{N-1}X_{r}\sum_{n=0}^{N-1}\phi(n)e^{j2\pi\frac{(r-k)}{N}n}\right\} = var\left\{\sum_{\substack{r=0,\\r\neq k}}^{N-1}X_{r}\sum_{n=0}^{N-1}\phi(n)e^{j2\pi\frac{(r-k)}{N}n}\right\}$$

(2.40)

because  $var(cX) = |c|^2 var(X)$ .  $P_{ICI}$  is then found to be

$$P_{ICI} = P_s \frac{N-1}{N} \sigma_{\phi}^2 \tag{2.41}$$

where  $P_s$  is the OFDM signal power.

Although papers [9], [10] and [17] do not derive the EVM of the phase noise explicitly, it can be derived easily. By assuming a large number of subcarriers and combining (2.16), (2.35) and (2.41) we get an approximate expression for the EVM of phase noise as

$$EVM_{PN} \approx \sqrt{\sigma_{\phi}^2} = \sqrt{2 \int_{0}^{f_s} L_{\phi}(f) df}$$

(2.42)

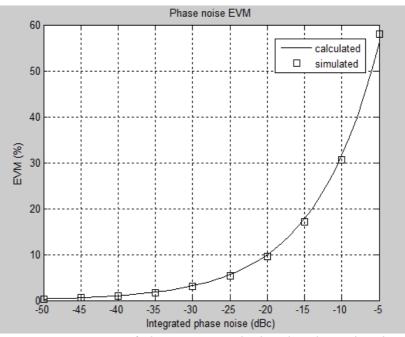

The influence of phase noise was simulated with the phase noise model provided in [2], for a 100 kHz PLL loop bandwidth and a system bandwidth of 3.84 MHz. The results are given in Figure 9.

Figure 9: EVM of phase noise, calculated and simulated

#### 2.2.2 EVM of nonlinearities

The derivation of the EVM due to nonlinearity given here is the original contribution of this thesis work, based on the results derived in [18].

In the analysis of the EVM in nonlinear systems, we focus on the polynomial baseband model of nonlinearities, given in discrete time. The input-output K-order characteristic of such a system is [18], [19]

$$y_{n} = \sum_{k=1}^{K} \alpha_{k} x_{n} |x_{n}|^{k-1}$$

(2.43)

As it was pointed out before, the overall effect of nonlinearities on an OFDM signal can be described by joint compression of the signal constellation and addition of (approximately Gaussian) noise, the latter coming from subcarrier ICI. The signal at the FFT output can then be modeled by (2.38).

In order to determine the overall influence of nonlinearity in a real-life system, we must recall that in real-life systems there is an AGC device (usually sitting at the end of the analog part of the chain) that ideally delivers a constant power level to the ADC; if it senses any perturbation of the signal power, it fights to cancel it. If any power loss is left uncompensated, it will be compensated in the digital domain by channel equalization (we can think of the AGC as an analog-domain equalization, if we consider a flat fading channel). In this respect, the compensation of the compression has to be regarded as a phenomenon that is inherent to the nonlinearity and needs to be taken into concern when analyzing the effects of nonlinearity.

The nonlinearity model can be rewritten as

$$Y_{k} = \mu_{NL} X_{k} + D_{k,NL} = \alpha_{1} \cdot \gamma X_{k} + D_{k,NL} , \qquad (2.44)$$

where  $\alpha_1$  is the small-signal gain (uncompressed) and  $\gamma$  models the compression

effect.

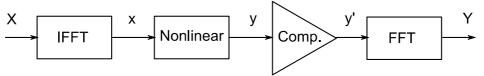

The block diagram of the system with compression compensation is given in Figure 10.

Figure 10: Nonlinearity with compensation

The mathematical model of the system is (only taking into account only the third order nonlinearity):

$$x = IFFT(X)$$

$$y = \alpha_{1}x + \alpha_{3}x|x|^{2}$$

$$y' = G \cdot y$$

$$Y = FFT(y') = G \cdot IFFT(y) = G \cdot \mu \cdot X + G \cdot D_{NL}$$

(2.45)

Since  $G=1/\gamma$ , finally we have

$$Y = \alpha_1 \cdot X + G \cdot D_{NL} \quad . \tag{2.46}$$

In [18], it was found that

$$\gamma = 1 + \frac{\alpha_3}{\alpha_1} \frac{P}{N} \quad , \tag{2.47}$$

$$\sigma_{NL}^2 = 3|\alpha_3|^2 \frac{P^3}{N^2} , \qquad (2.48)$$

where P is the power of the pre-IFFT signal X and  $P_{in} = P/N$  is the power of the signal x, coming after IFFT. For determining the EVM, we must determine the power of the distortion  $P_{dist}$  and the reference power P

$$P_{dist} = G^2 \cdot \sigma_{NL}^2 = \frac{1}{\gamma^2} 3|\alpha_3|^2 \frac{P^3}{N^2}$$

(2.49)

and since we are expecting the signal X with small-signal amplification, the reference output constellation should have the power

$$P_{ref} = \alpha_1^2 \cdot P \tag{2.50}$$

It should be observed that the compensation is not taken into concern when calculating  $P_{ref}$  since it is inherent to the nonlinearity, as explained before. The EVM is now found to be

$$EVM = \sqrt{\frac{P_{dist}}{P_{ref}}} = \sqrt{3\left(\frac{\alpha_3}{\alpha_1}\right)^2 \frac{P_{in}^2}{\gamma^2}}$$

(2.51)

which after little manipulation becomes

$$EVM = \frac{4 \cdot P_{\text{in}}}{\sqrt{3} A_{IIP3}^2 - \frac{4\sqrt{3}}{3} P_{\text{in}}}$$

(2.52)

This model was put to the test in MATLAB, where a nonlinear device with IIP3 = 10 dBm

was simulated with an input OFDM signal of varying power. The results are given in Figure 11.

Figure 11: Nonlinearity EVM, simulated and calculated

## 2.2.3 EVM of quantization and clipping

The joint EVM of quantization and clipping is derived based on the expressions for the power of quantization and clipping distortions that are well-known in literature (for the purposes of this derivation, the expression for the power of clipping distortion is found in [20]).

The effects of quantization and clipping in OFDM systems are defined in terms of the *input* backoff (IBO), defined as

$$\rho_{ADC} = \frac{A_{max}^2}{P_{\rm in}} \tag{2.53}$$

where  $P_{in}$  is the power of the post-IFFT (time-domain) OFDM signal. The power of the clipping distortion is shown to be [20]

$$\sigma_c^2 = 2 \left( P_{\text{in}} + A_{max}^2 \right) Q \left( \frac{A_{max}}{\sqrt{P_{\text{in}}}} \right) - 2 A_{max} \sqrt{\frac{P_{\text{in}}}{2\pi}} e^{-\frac{A_{max}^2}{2P_{\text{in}}}} .$$

(2.54)

If the quantization noise power  $\sigma_q^2 = \sigma_e^2$  is found from (2.27), the total EVM is

$$EVM_{c,q} = \sqrt{\frac{\sigma_c^2 + \sigma_q^2}{P_{in}}} = \sqrt{2(1 + \rho_{ADC})Q(\sqrt{\rho_{ADC}})} - \sqrt{\frac{2\rho_{ADC}}{\pi}}e^{-\frac{\rho_{ADC}}{2}} + \frac{\rho_{ADC}}{3\cdot(2^n - 1)^2}$$

(2.55)

where Q(x) is the Q-function.

The EVM of a regular Nyquist ADC with bit resolutions 6, 8, 10, 12 and 14 and as a function of input backoff is plotted in Figure 12.

Figure 12: EVM as a function of input backoff (IBO) for ADCs with different bit resolutions

As it can be seen from Figure 12, for a very large input signal power  $P_s$  (small *IBO*) the clipping is very intense and EVM is large. As  $P_s$  decreases, the EVM reaches its minimum. For a very small  $P_s$ , the effective number of bits used in the quantization of the signal is small and so EVM increases again. Thus, the errors due to clipping dominate the area left of the minimum, and quantization noise dominates to the right of the minimum.

If we assume that an ideal AGC precedes the ADC, then the working point of the AGC is always at the minimum value of the EVM curve for a particular bit resolution. In ADC design, for a given EVM specification (like EVM = 1.5%, given as a dashed black line in Figure 12), we then choose the bit resolution that has its minimum below the target EVM. As it can be seen from the plot, we are usually allowed to have a *range* of IBO values, allowing for a non-ideal (simpler) AGC.

#### **2.2.4** Calculation of EVM for a cascade of impairments

As another original contribution of this thesis, the expressions relating to the power of phase noise, nonlinearity and quantization/clipping distortions, found in [17], [18] and [20], are going to be applied on a specific receiver topology, resulting in the overall RF impairment EVM for that topology. The theory is compared with simulation results.

So far, we have analyzed the influence individual RF impairments have on the OFDM signal. In the analysis and design of real systems, however, there is a need to determine the total EVM for a cascade of blocks, where each block contains one or more sources of RF signal distortion coming from impairments. Due to the interaction between different impairment effects in the cascade, the complexity of an accurate theoretical expression for the EVM blows up with the number of blocks taken into account. This work, on the other hand, aims at finding useful system performance models that will give reasonable precision with reduced description complexity.

In order for the analysis to yield usable theoretical description, two important assumptions need to be made:

1. The phase rotation of the constellation due to CPE and the compression of the constellation due to nonlinearities are compensated with AGC, with equalization or jointly by both. Therefore, the final joint effect of RF impairments is a sum of noise-like components;

2. With 1. satisfied, we assume these noise-like components to be Gaussian and independent. The overall distortion power  $P_{dist, total}$  is then calculated as the sum of powers of K individual distortions:

$$P_{dist,total} = P_{dist,1} + P_{dist,2} + \dots + P_{dist,K}$$

(2.56)

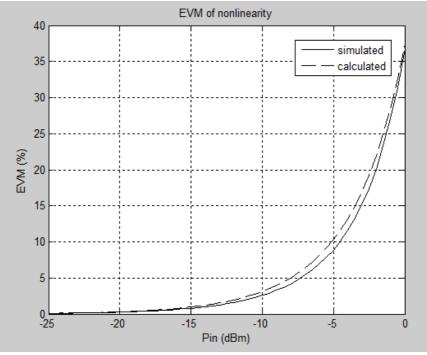

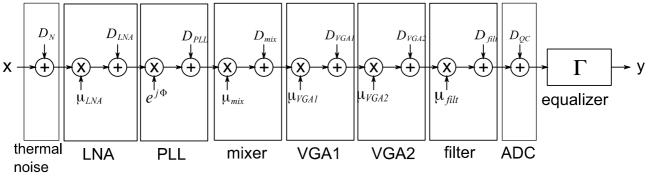

The validity of these assumptions is going to be put on test in a receiver chain model. The block diagram of the model is shown in Figure 13.

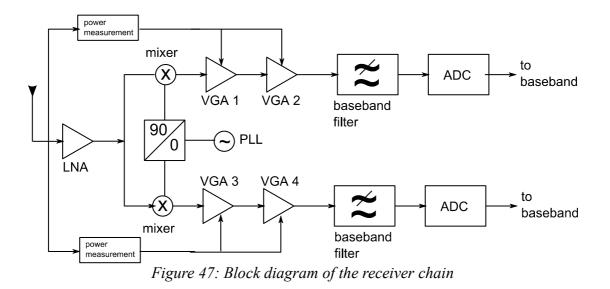

Figure 13: Block diagram of the receiver chain

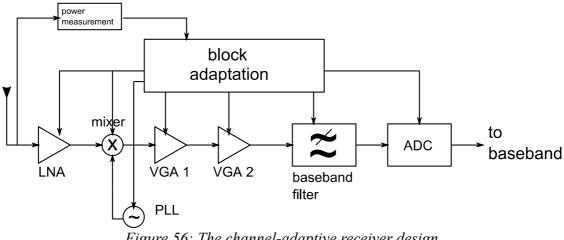

LNA, VGAs, mixer and the baseband filter can quickly be recognized as sources of nonlinearity, PLL as the source of the phase noise and ADC of the quantization and clipping distortion. All of the elements also generate thermal noise; the equivalent thermal noise for the chain can be calculated using formulas (2.3) and (2.4) and then be referenced at the input of the chain, right after the antenna. This noise can also be assumed independent from other distortions. The block diagram of the RF impairment model of the chain (needed for calculating the input - output characteristic) is given in Figure 14.

Figure 14: RF impairment model of the receiver chain

Compressed signal gains  $\mu_{LNA}$ ,  $\mu_{mix}$ ,  $\mu_{VGA1}$ ,  $\mu_{VGA2}$ ,  $\mu_{filt}$  of their respective elements are given by  $\alpha_1 + \alpha_3 \cdot P_{block}$ , where  $P_{block}$  is the input power to the block:

$$\mu_{LNA} = \sqrt{G_{LNA}} + \alpha_{3LNA} \cdot \frac{P}{N} ,$$

$$\mu_{mix} = \sqrt{G_{mix}} + \alpha_{3mix} \cdot \frac{\mu_{LNA}^2 P}{N} ,$$

$$\mu_{VGAI} = \sqrt{G_{VGAI}} + \alpha_{3VGAI} \cdot \frac{\mu_{LNA}^2 \mu_{mix}^2 P}{N} ,$$

$$\mu_{VGA2} = \sqrt{G_{VGA2}} + \alpha_{3VGA2} \cdot \frac{\mu_{LNA}^2 \mu_{mix}^2 \mu_{VGAI}^2 P}{N}$$

$$\mu_{filt} = \sqrt{G_{filt}} + \alpha_{3filt} \cdot \frac{\mu_{LNA}^2 \mu_{mix}^2 \mu_{VGAI}^2 \mu_{VGA2}^2 P}{N} \quad . \tag{2.57}$$

A few further observations about the model: the small - signal gains  $\alpha_1$  can be substituted by  $\sqrt{G}$ , where G is the corresponding power gain of the block. Furthermore, P models the constellation power before the IFFT and it is assumed that there is no loss in the channel, *i.e.* channel gain is 1. Any channel losses would have to be incorporated in the pre-IFFT constellation power.

The terms  $D_{LNA}$ ,  $D_{mix}$ ,  $D_{VGA1}$ ,  $D_{VGA2}$ ,  $D_{filt}$  are the "noise" components of the nonlinear distortion, whose power is given by the expressions

$$\sigma_{LNA}^{2} = 3 |\alpha_{3LNA}|^{2} \frac{P^{3}}{N^{2}} = 3 |\alpha_{3LNA}|^{2} P_{in}^{3} \cdot N ,$$

$$\sigma_{mix}^{2} = 3 |\alpha_{3mix}|^{2} \mu_{LNA}^{6} P_{in}^{3} \cdot N ,$$

$$\sigma_{VGAI}^{2} = 3 |\alpha_{3VGA1}|^{2} \mu_{LNA}^{6} \mu_{mix}^{6} P_{in}^{3} \cdot N ,$$

$$\sigma_{VGA2}^{2} = 3 |\alpha_{3VGA2}|^{2} \mu_{LNA}^{6} \mu_{mix}^{6} \mu_{VGA1}^{6} P_{in}^{3} \cdot N ,$$

$$\sigma_{fill}^{2} = 3 |\alpha_{3fill}|^{2} \mu_{LNA}^{6} \mu_{mix}^{6} \mu_{VGA1}^{6} P_{in}^{3} \cdot N ,$$

$$\sigma_{fill}^{2} = 3 |\alpha_{3fill}|^{2} \mu_{LNA}^{6} \mu_{mix}^{6} \mu_{VGA1}^{6} P_{in}^{3} \cdot N ,$$

(2.58)

where  $P_{in} = P/N$  is the post-IFFT power, or the power at the receiving antenna.

Additionally,  $e^{j\Phi}$  is the phase rotation due to the CPE caused by phase noise.

An important note about VGAs and equalization: by examining Figure 13, it can be observed that VGA gains are adjusted using the input signal information from the input of the antenna. The analog part of the receiver in this setup is not aware of possible signal compression by nonlinear elements, and hence the compensation of compression is not done by VGAs. This compensation, together with the derotation of the constellation, is done by the equalizer. Assuming flat fading and perfect channel estimation, the voltage gain  $\Gamma$  of the zero forcing equalizer is

$$\Gamma = \frac{e^{-j\Phi}}{\gamma_{LNA}\gamma_{mix}\gamma_{VGA1}\gamma_{VGA2}\gamma_{filt}} \qquad (2.59)$$

The input-output characteristic of the system shown in Figure 13 is then given by

$$y = (\mu_{LNA} e^{j\Phi} \mu_{mix} \mu_{VGA1} \mu_{VGA2} \mu_{filt} x$$

$$+ \mu_{LNA} e^{j\Phi} \mu_{mix} \mu_{VGA1} \mu_{VGA2} \mu_{filt} D_N$$

$$+ e^{j\Phi} \mu_{mix} \mu_{VGA1} \mu_{VGA2} \mu_{filt} D_{LNA}$$

$$+ \mu_{mix} \mu_{VGA1} \mu_{VGA2} \mu_{filt} D_{PLL}$$

$$+ \mu_{VGA1} \mu_{VGA2} \mu_{filt} D_{mix}$$

$$+ \mu_{VGA2} \mu_{filt} D_{VGA1}$$

$$+ \mu_{Gh1} D_{VGA2} + D_{filt} + D_{OC}) \cdot \Gamma$$

$$(2.60)$$

which can then be expressed as

$$y = \alpha_{LNA} \alpha_{mix} \alpha_{VGAI} \alpha_{VGA2} \alpha_{filt} X$$

$$+ \alpha_{LNA} \alpha_{mix} \alpha_{VGAI} \alpha_{VGA2} \alpha_{filt} D_N$$

$$+ \alpha_{mix} \alpha_{VGAI} \alpha_{VGA2} \alpha_{filt} \frac{D_{LNA}}{Y_{LNA}}$$

$$+ \alpha_{mix} \alpha_{VGAI} \alpha_{VGA2} \alpha_{filt} e^{-j\Phi} \frac{D_{PLL}}{Y_{LNA}}$$

$$+ \alpha_{VGAI} \alpha_{VGA2} \alpha_{filt} e^{-j\Phi} \frac{D_{mix}}{Y_{LNA} Y_{mix}}$$

$$+ \alpha_{VGA2} \alpha_{filt} e^{-j\Phi} \frac{D_{VGAI}}{Y_{LNA} Y_{mix} Y_{VGAI}}$$

$$+ \alpha_{filt} e^{-j\Phi} \frac{D_{VGA2}}{Y_{LNA} Y_{mix} Y_{VGAI} Y_{VGA2} Y_{filt}}$$

$$+ e^{-j\Phi} \frac{D_{QC}}{Y_{LNA} Y_{mix} Y_{VGAI} Y_{VGA2} Y_{filt}}$$

The distortion power for the nonlinearities is given by:

$$P_{dist, LNA} = \frac{\alpha_{mix}^{2} \alpha_{VGA1}^{2} \alpha_{VGA2}^{2} \alpha_{filt}^{2} \sigma_{LNA}^{2}}{\gamma_{LNA}^{2}} = \frac{\alpha_{mix}^{2} \alpha_{VGA1}^{2} \alpha_{VGA2}^{2} \alpha_{filt}^{2} 3 |\alpha_{3LNA}|^{2} P_{in}^{3} \cdot N}{\gamma_{LNA}^{2}} ,$$

$$P_{dist, mix} = \frac{\alpha_{VGA1}^{2} \alpha_{VGA2}^{2} \alpha_{filt}^{2} \sigma_{mix}^{2}}{\gamma_{LNA}^{2} \gamma_{mix}^{2}} = \frac{\alpha_{VGA1}^{2} \alpha_{VGA2}^{2} \alpha_{filt}^{2} 3 |\alpha_{3mix}|^{2} \mu_{LNA}^{6} P_{in}^{3} \cdot N}{\gamma_{LNA}^{2} \gamma_{mix}^{2}} ,$$

$$P_{dist, VGA1} = \frac{\alpha_{VGA2}^{2} \alpha_{filt}^{2} \sigma_{VGA1}^{2}}{\gamma_{LNA}^{2} \gamma_{mix}^{2}} = \frac{\alpha_{VGA2}^{2} \alpha_{filt}^{2} 3 |\alpha_{3VGA1}|^{2} \mu_{LNA}^{6} \mu_{mix}^{6} P_{in}^{3} \cdot N}{\gamma_{LNA}^{2} \gamma_{mix}^{2}} ,$$

$$P_{dist, VGA1} = \frac{\alpha_{VGA2}^{2} \alpha_{filt}^{2} \sigma_{VGA1}^{2}}{\gamma_{LNA}^{2} \gamma_{mix}^{2} \gamma_{VGA1}^{2}} = \frac{\alpha_{VGA2}^{2} \alpha_{filt}^{2} 3 |\alpha_{3VGA1}|^{2} \mu_{LNA}^{6} \mu_{mix}^{6} P_{in}^{3} \cdot N}{\gamma_{LNA}^{2} \gamma_{mix}^{2} \gamma_{VGA1}^{2}} ,$$

$$P_{dist, VGA2} = \frac{\alpha_{filt}^{2} \sigma_{VGA2}^{2} \alpha_{filt}^{2} \sigma_{VGA1}^{2}}{\gamma_{LNA}^{2} \gamma_{mix}^{2} \gamma_{VGA1}^{2} \gamma_{VGA1}^{2}} = \frac{\alpha_{filt}^{2} 3 |\alpha_{3VGA1}|^{2} \mu_{LNA}^{6} \mu_{mix}^{6} \mu_{Mix}^{6} P_{in}^{3} \cdot N}{\gamma_{LNA}^{2} \gamma_{mix}^{2} \gamma_{VGA1}^{2}} ,$$

$$P_{dist, filt} = \frac{\sigma_{filt}^{2} \gamma_{LNA}^{2} \gamma_{mix}^{2} \gamma_{VGA1}^{2} \gamma_{VGA2}^{2}}{\gamma_{LAA}^{2} \gamma_{Mix}^{2} \gamma_{VGA1}^{2} \gamma_{VGA1}^{2} \gamma_{VGA2}^{2} \gamma_{filt}^{2}} .$$

$$(2.62)$$

The analysis of distortion power for the PLL and for ADC needs to be undertaken carefully.

Following the analysis in [17] and according to (2.41), the power of the ICI distortion due to phase noise is

$$P_{ICI, single} = P_S \sigma_{\phi}^2 \quad , \tag{2.63}$$

where  $P_s$  is the power of the pre-IFFT (frequency-domain) OFDM signal. If a certain (compressed) gain  $\mu_{LNA}$  precedes the entry point of the PLL signal in the chain, this needs to be incorporated in  $P_s$ . Therefore, ICI distortion power in the chain is equal to

$$P_{dist, PLL} = P_{ICI, chain} = \mu_{LNA}^2 P_S \sigma_{\phi}^2 \quad . \tag{2.64}$$

Clipping noise power is expressed in terms of an input backoff (IBO) denoted by  $\rho$ . In an ideal receiver chain, without compression and with ideal AGC settings, this IBO is set to the optimum value for the particular bit resolution (corresponding to bottom points of the curves in Figure 12). It we are to track the joint effect of quantization, clipping and nonlinearities, it is then convenient to define an optimum clipping noise for the optimal backoff:

$$\sigma_{c,opt}^{2} = 2(P_{opt} + A_{max}^{2})Q\left(\frac{A_{max}}{\sqrt{P_{opt}}}\right) - 2A_{max}\sqrt{\frac{P_{opt}}{2\pi}}e^{-\frac{A_{max}^{2}}{2P_{opt}}} , \quad (2.65)$$

with  $P_{opt} = \alpha_{LNA}^2 \alpha_{mix}^2 \alpha_{VGA1}^2 \alpha_{VGA2}^2 \alpha_{filt}^2 P_{in}$ . If we now consider the effects of compression, it is obvious that the power of the signal at ADC input is not longer going to give the optimal backoff: it is reduced so the backoff is increased.

Let's define, for convenience, a power compression coefficient K:

$$K = \gamma_{LNA}^{2} \gamma_{mix}^{2} \gamma_{VGA1}^{2} \gamma_{VGA2}^{2} \gamma_{filt}^{2} . \qquad (2.66)$$

Then the input power to the ADC is equal to  $K \cdot P_{opt}$  and the clipping noise power for this case is calculated as

$$\sigma_{c,comp}^{2} = 2\left(K \cdot P_{opt} + A_{max}^{2}\right) Q\left(\frac{A_{max}}{\sqrt{K \cdot P_{opt}}}\right) - 2A_{max}\sqrt{\frac{K \cdot P_{opt}}{2\pi}} e^{-\frac{A_{max}^{2}}{2K \cdot P_{opt}}} \quad .$$

(2.67)

The expressions for the nonlinearity and PLL distortions have been derived for the entire OFDM system, *i.e.* they consider that the power of the signal is increased *N* times in the FFT block. Quantization and clipping noise expressions, however, do not consider this, and as a result, the proper expression for the power of the joint quantization and clipping noise would be

$$\sigma_{QC}^2 = N \left( \sigma_{c, comp}^2 + \sigma_q^2 \right)$$

(2.68)

and the power of the distortion

$$P_{dist,QC} = \frac{\sigma_{QC}^2}{K} = \frac{1}{K} N \left( \sigma_{c,comp}^2 + \sigma_q^2 \right) \quad . \tag{2.69}$$

A proper definition of the reference power is essential for finding the correct EVM. The reference power for the chain is defined as the signal power that is expected at the FFT output when there are no RF impairments present, *i.e.* with just the small-signal gains. This power is equal to

$$P_{ref} = \alpha_{LNA}^2 \alpha_{mix}^2 \alpha_{VGA1}^2 \alpha_{VGA2}^2 \alpha_{filt}^2 P = \alpha_{LNA}^2 \alpha_{mix}^2 \alpha_{VGA1}^2 \alpha_{VGA2}^2 \alpha_{filt}^2 P_{in} \cdot N \quad .$$

(2.70)

Individual EVMs for different impairment sources are then calculated as follows:

$$EVM_{LNA} = \sqrt{\frac{P_{dist, LNA}}{P_{ref}}} = \sqrt{3\left(\frac{\alpha_{3LNA}}{\alpha_{LNA}}\right)^{2} \frac{P_{in}^{2}}{\gamma_{LNA}^{2}}} ,$$

$$EVM_{PLL} = \sqrt{\frac{P_{dist, PLL}}{P_{ref}}} = \sqrt{\sigma_{\phi}^{2}} ,$$

$$EVM_{mix} = \sqrt{\frac{P_{dist, mix}}{P_{ref}}} = \sqrt{3\left(\frac{\alpha_{3mix}}{\alpha_{mix}}\right)^{2} \frac{\left(\mu_{LNA}^{2} P_{in}\right)^{2}}{\gamma_{mix}^{2}}} ,$$

$$EVM_{VGAI} = \sqrt{\frac{P_{dist, VGAI}}{P_{ref}}} = \sqrt{3\left(\frac{\alpha_{3VGA1}}{\alpha_{VGAI}}\right)^{2} \frac{\left(\mu_{LNA}^{2} \mu_{mix}^{2} P_{in}\right)^{2}}{\gamma_{VGAI}^{2}}} ,$$

$$EVM_{VGA2} = \sqrt{\frac{P_{dist, VGA2}}{P_{ref}}} = \sqrt{3\left(\frac{\alpha_{3VGA2}}{\alpha_{VGA2}}\right)^{2} \frac{\left(\mu_{LNA}^{2} \mu_{mix}^{2} \mu_{in}^{2}\right)^{2}}{\gamma_{VGAI}^{2}}} ,$$

$$EVM_{filt} = \sqrt{\frac{P_{dist.filt}}{P_{ref}}} = \sqrt{3\left(\frac{\alpha_{3filt}}{\alpha_{filt}}\right)^2 \frac{\left(\mu_{LNA}^2 \mu_{mix}^2 \mu_{VGAI}^2 \mu_{VGAI}^2 P_{in}\right)^2}{\gamma_{filt}^2} , \qquad (2.72)$$

For the ADC, the  $P_{ref}$  is more conveniently expressed as

$$P_{ref} = K \cdot P_{opt} \cdot N \cdot \frac{1}{K} = N \cdot P_{opt} \quad .$$

(2.73)

The EVM for the ADC is then

$$EVM_{ADC} = \sqrt{\frac{P_{dist, QC}}{P_{ref}}} = \sqrt{\frac{\frac{1}{K}N(\sigma_{c,comp}^{2} + \sigma_{q}^{2})}{N \cdot P_{opt}}}$$

$$EVM_{ADC} = \sqrt{2\left(1 + \frac{\rho_{opt}}{K}\right)Q\left(\sqrt{\frac{\rho_{opt}}{K}}\right) - \sqrt{\frac{2\rho_{opt}}{K\pi}}e^{-\frac{\rho_{opt}}{2K}} + \frac{\rho_{opt}}{3K \cdot (2^{n} - 1)^{2}}$$

$$(2.74)$$

Finally, the EVM of the thermal noise is calculated simply as  $EVM_n = \sqrt{P_n/P_{in}}$ .

The total EVM for the entire chain is then calculated as

$$EVM_{total} = \sqrt{EVM_{LNA}^{2} + EVM_{PLL}^{2} + EVM_{mix}^{2} + EVM_{VGAI}^{2} + EVM_{VGA}^{2} + EVM_{fill}^{2} + EVM_{ADC}^{2} + EVM_{n}^{2}}$$

(2.75)

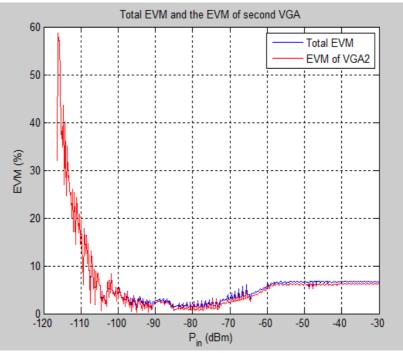

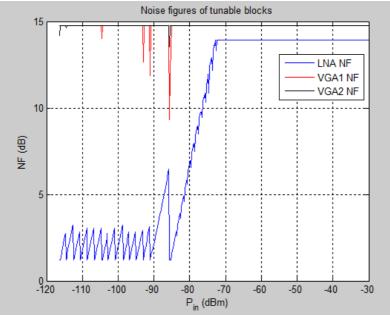

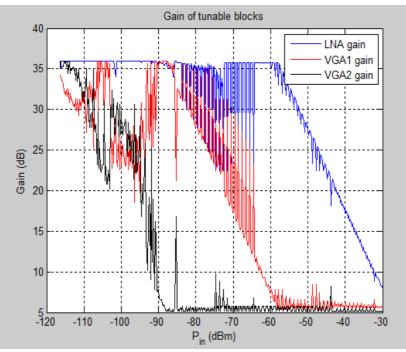

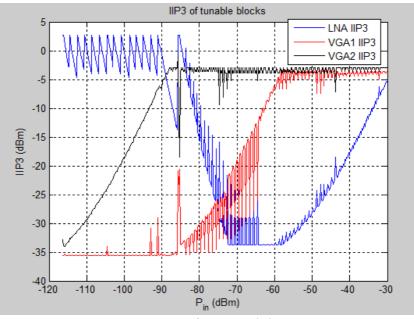

The described model has been put to test in MATLAB, with a couple of characteristic use cases:

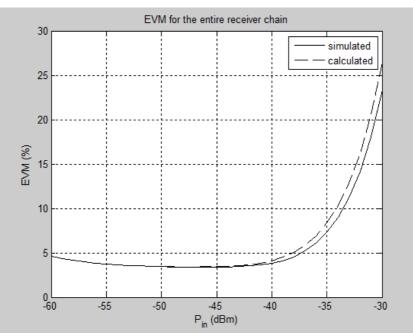

• Use case 1: Parameters of the blocks (gains, linearity) are fixed and input power changes. The parameters are given in Table 1:

| Block           | Parameter values                                                                    |

|-----------------|-------------------------------------------------------------------------------------|

| LNA             | G = 10  dB, IIP3 = 10  dBm                                                          |

| PLL             | Integrated phase noise = $-43.86$ dBc; the rest is same as in the simulation of 2.1 |

| Mixer           | G = 5 dB, IIP3 = 5 dBm                                                              |

| VGA1            | G = 10  dB, IIP3 = 15  dBm                                                          |

| VGA2            | G = 15  dB, IIP3 = 20  dBm                                                          |

| Baseband filter | G = 5 dB, IIP $3 = 20 dBm$                                                          |

| ADC             | ENOB = 6, optimal IBO = 10.5 dB                                                     |

| Thermal noise   | $P_n = -90 \text{ dBm}$                                                             |

Table 1: Parameter values for the simulation of use case 1 of the receiver chain

The input power is swept from -60 to -30 dBm. Simulated and calculated EVM are given in Figure 15.

*Figure 15: Simulated and calculated EVM for the entire receiver chain, use case 1*

It can be observed that the theory gives an accurate estimate of the actual EVM.

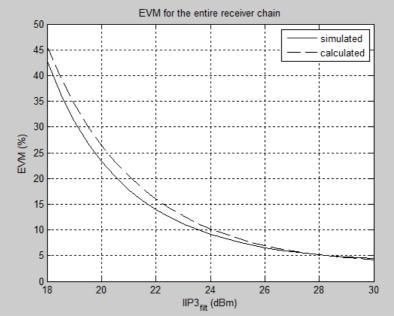

• Use case 2: Input power is fixed at -30 dBm and filter IIP3 is swept. The remaining parameters are same as in use case 1.

Figure 16: Simulated and calculated EVM for the entire receiver chain, use case 2

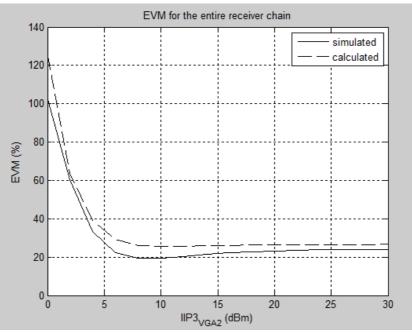

• Use case 3: Input power is fixed at -30 dBm and VGA2 IIP3 is swept. The remaining parameters are same as in use case 1.

Figure 17: Simulated and calculated EVM for the entire receiver chain, use case 3

Plots for use cases 2 and 3 also confirm that the model gives a reasonably good approximation of the EVM (and it's always an overestimate).

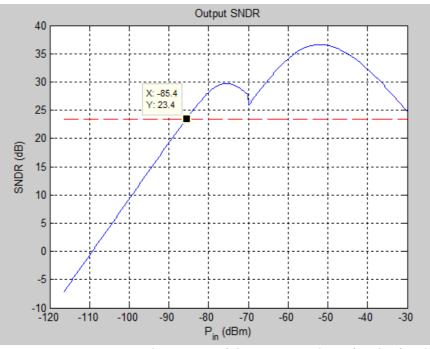

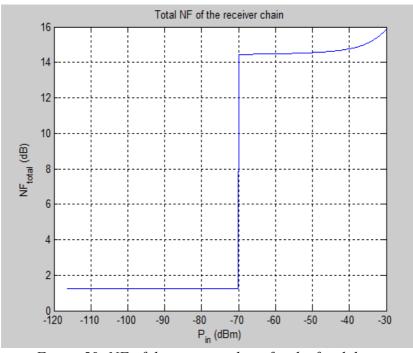

## 2.2.5 EVM as means of calculating SNR degradation and signal-to-noise-anddistortion ratio (SNDR)

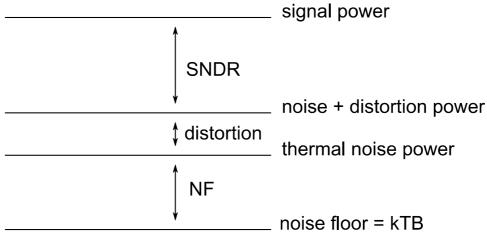

When analyzing the overall effects that the receiver chain has on the received signal, it is useful to separate the influence of thermal noise from the influence of other RF impairments (nonlinearity, phase noise...):

- The ratio of signal power to thermal noise power is the signal-to-noise ratio (SNR)

- The ratio of signal power to the sum of the power of thermal noise and other distortions is the signal-to-noise-and-distortion ratio (SNDR)

In the end, it's the effect of the SNDR that determines the quality of detection at the baseband and thus the overall performance of the system. Therefore, the SNDR has to be quantified. Figure 18 shows the noise and distortion budget diagram.

Figure 18: Noise and distortion budget diagram

One possible way of determining the SNDR is with the help of the EVM. First, it is assumed that the effect of all RF impairments can be modeled as white noise; this can hold for multicarrier systems that use equalization, as described in section 2.2.4. If we denote signal power with S, the total thermal noise power by N and total distortion power as M, SNDR is determined simply as

$$SNDR = \frac{S}{N+M}$$

(2.76)

If we recognize that  $EVM_{total}^2 = M/S$  and SNR = S/N, then we can write

$$\frac{1}{SNDR} = \frac{1}{SNR} + EVM_{total}^2 , \qquad (2.77)$$

or finally

$$SNDR = \frac{SNR}{1 + EVM_{total}^2 \cdot SNR} \quad . \tag{2.78}$$

With an SNR determined from (2.4) and  $EVM_{total}$  defined as

$$EVM_{total} = \sqrt{EVM_{LNA}^{2} + EVM_{PLL}^{2} + EVM_{mix}^{2} + EVM_{VGAl}^{2} + EVM_{VGA}^{2} + EVM_{filt}^{2} + EVM_{ADC}^{2}}$$

(2.79)

(not counting the effects of thermal noise, because it is separately accounted for by SNR), it is then possible to determine the SNDR.

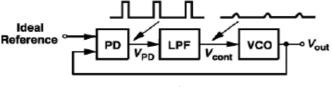

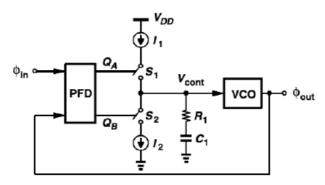

# **3** Direct Conversion Receiver - Analog Front End

## **3.1** Introduction

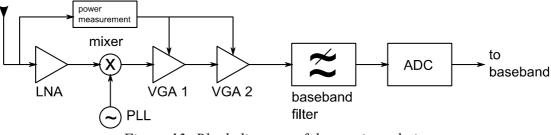

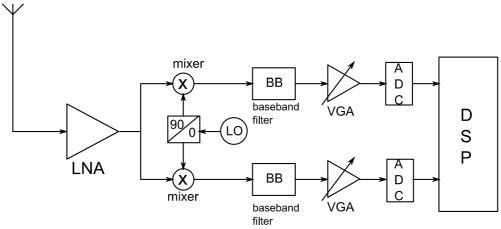

In recent years, RF receivers based on the direct-conversion principle have began to dominate in the realm of cellular chipset design. Figure 19 shows a direct conversion receiver (DCR) without the initial band-pass filter.

*Figure 19: Direct conversion receiver (without the surface-acoustic-wave filter)*

DCRs convert the signal from passband to baseband in a single step, by mixing the signal with a tone which has the frequency equal to the center frequency of the signal. Since the transmitted information is encoded in the two sidebands of the signal, these two sidebands have to be preserved and separated for successful detection; this explains the I and Q branches of the DCR.

Some benefits of DCRs are [21]:

- No need for bulky off-chip components like image-reject or IF filters;

- The entire receiver fits onto one chip;

- Only one local oscillator is needed;

- Image frequency issue, present in heterodyne receivers, is not encountered in DCRs;

- Channel-select filter is a simple baseband filter.

However, there are also some issues related specifically to DCRs:

- DC offset due to LO leakage;

- I/Q imbalance problem;

- Problems with even-order distortion;

- Pronounced flicker (low-frequency) noise.

All of the named issues that impair the performance of DCRs can be treated by clever analog designs, employing analog impairment cancellation schemes right at the point of the impairment

(the so-called "clean RF" approach). In recent years, the advances in digital design have also made possible that the listed issues be resolved in the digital domain by employing digital signal processing algorithms ("dirty-RF" approach).

This chapter deals with the analog part of the DCR. The analog-to-digital conversion (mixed-signal part) and digital baseband are overviewed in subsequent chapters.

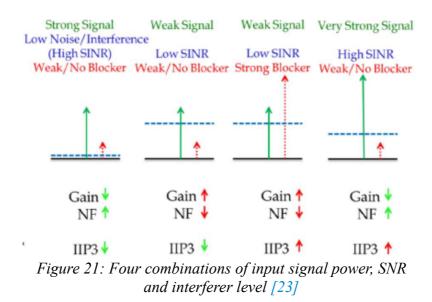

## 3.2 Low noise amplifier

The LNA represents the first stage of a radio receiver, and owing to this sensitive position it exerts a significant impact on the overall system performance. Therefore, much care needs to be invested in the design of the LNA. Important parameters in the LNA design are:

- Noise figure (NF). From the Friis' formula, the noise figure of the LNA directly adds to the overall noise figure of the receiver. The input stage of the LNA is the main contributor to its NF.

- Gain. Again from the Friis' formula, the gain of the LNA has to be sufficiently high so it supresses thermal noise coming from subsequent stages (especially the one coming from the downconversion mixer). However, if the gain is chosen too large, it raises the input signal level too high too early in the receiver chain; this emphasizes the nonlinearity of the subsequent stages.

- **Input return loss (matching).** For maximum effectiveness, the antenna is designed for a real terminating impedance (usually 50 ohm). Therefore, the input impedance of the LNA should be equal to this impedance, otherwise, a certain amount of input power is reflected at the LNA input back to the antenna.

- Linearity. Except for occasional peaks, the power of the wanted signal at the input of the LNA is rather small so, with regards to just the wanted signal, LNA will rarely go into compression. The issues with the LNA linearity arise when there is a strong blocking signal at its input (typically a leaked transmit signal; for a typical Tx power level of 30 dBm and duplexer isolation of 50 dB, the blocker is at -20 dBm). This imposes an increased demand for LNA linearity, and for the linearity of subsequent stages as well.

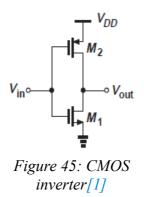

LNA topologies can be divided into two major groups: LNAs with a common-source (CS) input stage, and LNAs with a common-gate (CG) input stage.

CG designs are shown [1] to be broadband, *i.e.* their gain and matching are relatively constant over a wider range of frequencies. Compared with CS topologies, the matching is better (input return loss is lower). CG also provide a higher NF than CS topologies, but their NF is independent of frequency.

CS designs offer a smaller gain and matching bandwidth, with the input return loss being higher compared to CG. CS, on the other hand, offer an overall smaller NF which is, however, frequency dependent.

We therefore see that the choice of the topology-CG or CS-entails a tradeoff between noise, input matching and supported bandwidth: if a higher noise floor can be allowed in the design, the CG should be used (giving a larger badwidth and better matching), but if the demand on the noise floor is strict, it's better to choose the CS (with a lower bandwidth and poorer matching).

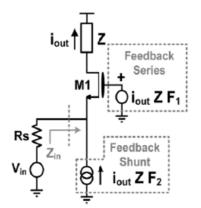

#### **3.2.1** Tunability and its impact on the overall system performance

LNAs in modern multistandard radio receivers have to be designed to support multiple bands (inside one standard, or for different standards), *i.e.* their central frequency of operation needs to be tunable. Also, the LNA should support some kind of power tunability that would trade performance for power. Classical radio receivers use an LNA in CS topology with inductively degenerated input. The operating frequency of this LNA design proves to be very difficult to tune (tuning it also tunes the NF), and the power tuning is difficult as well (due to interdependence between the noise, linearity and input matching of the amplifier).

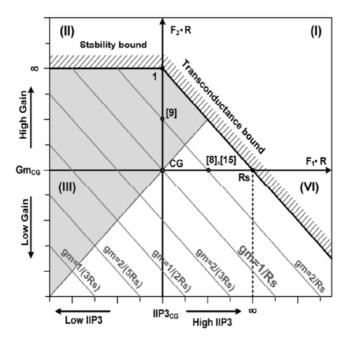

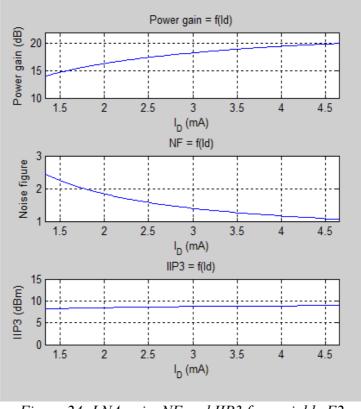

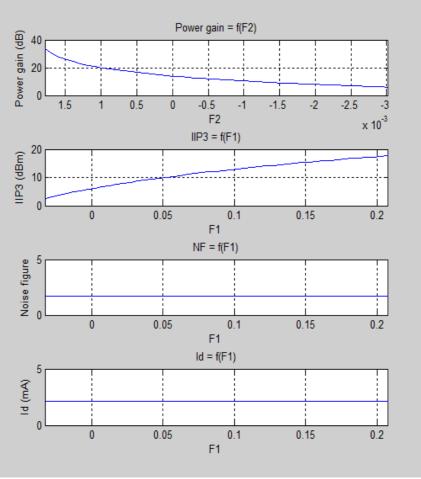

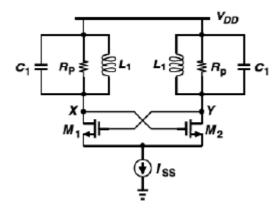

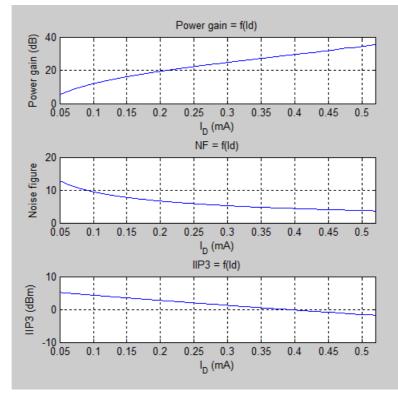

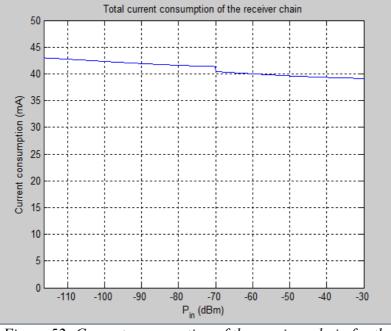

Paper [22] introduces a general LNA design that is shown to support both frequency and power tunability in a very efficient way. This design is chosen for demonstration of the connections between the parameters of the LNA (listed above) and power consumption.