## **SOVA** Based LTE Turbo Decoders

Performance and Architectures

ANG, LAY HONG LIM, WEE GUAN

Master's Thesis at Ericsson AB Supervisor: Matthias Kamuf, Ph.D

Lund, September 2009

© 2009 Ang, Lay Hong & Lim, Wee Guan

Department of Electrical and Information Technology Lund University P.O. Box 118 SE-221 00 Lund, Sweden

This thesis is set in Computer Modern 10pt with the LaTeX Documentation System

Printed in Sweden by Tryckeriet E-huset, Lund September 2009

## **Abstract**

The Max-Log-MAP algorithm is commonly used in a constituent decoder for turbo coding applications. In this thesis, the use of Soft-Output Viterbi Algorithms (SOVAs) as an alternative to Max-Log-MAP for use in the 3rd Generation Partnership Project (3GPP) Long Term Evolution (LTE) standard is investigated. The decoding performance of the Battail Rule SOVA (BR-SOVA) was found to be comparable to that of the Max-Log-MAP although there is a high price to be paid in terms of hardware complexity. A Simplified Battail Rule SOVA (SB-SOVA) algorithm that is suitable for hardware implementation is proposed, and the decoding performance of SB-SOVA is similar to BR-SOVA. A proposed hybrid-SOVA architecture that combines both Hagenauer Rule SOVA (HR-SOVA) and BR-SOVA to reduce the computational complexity of SB-SOVA is described, and the decoding performance was found to be within 0.1 dB of SB-SOVA.

To improve throughput and reduce the latency, the input data block is divided into windows to allow for parallel processing. The  $\alpha$ -stage warm-up method to determine the initial state of a window was found to give better performance as compared to the next iteration initialize (NII) method, with the performance of a windowed decoder performing within 0.1 dB of the ideal Max-Log-MAP.

Hardware architectures for the SB-SOVA and hybrid-SOVA decoders are presented and the memory requirements for SOVA were assessed to be around 10 % of that required for Max-Log-MAP on a per-window basis. The SB-SOVA and hybrid-SOVA decoders consume 87 % and 30 % more hardware resources per window respectively as compared to the Max-Log-MAP decoder. For the same degree of parallelization, the SOVA-based decoders provide 34 % higher throughput than a Max-Log-MAP decoder. The increased throughput of the SOVA architecture may enable the SB-SOVA based decoder to have lower hardware requirements as compared to the Max-Log-MAP as the the degree of parallelization required for a given data rate will be lower.

# **Contents**

## Acknowledgments

## Abbreviations

## Nomenclature

| 1 | Intr | oducti | ion                                                      |

|---|------|--------|----------------------------------------------------------|

|   | 1.1  | Turbo  | Decoding in LTE                                          |

|   | 1.2  |        | thms for Decoding Turbo Codes                            |

|   |      | 1.2.1  | Log Likelihood Ratio                                     |

|   |      | 1.2.2  | MAP Type Algorithms                                      |

|   |      | 1.2.3  | SOVA Algorithm                                           |

| 2 | Imp  | roved  | SOVA Algorithm 13                                        |

|   | 2.1  | Modifi | ications to SOVA                                         |

|   |      | 2.1.1  | Merging and Updating Depths                              |

|   |      | 2.1.2  | Reliability Thresholding                                 |

|   |      | 2.1.3  | Scaling of SOVA Outputs                                  |

|   |      | 2.1.4  | Simplification of BR-SOVA Update Rule                    |

|   |      | 2.1.5  | Reliability Update Methods for SOVA 1                    |

|   | 2.2  | Simula | ation Results                                            |

|   |      | 2.2.1  | Simulation Environment                                   |

|   |      | 2.2.2  | Optimum Reliability Thresholding and Scaling Factors for |

|   |      |        | SOVA                                                     |

|   |      | 2.2.3  | Effects of Simplified BR-SOVA Update Rule                |

|   |      | 2.2.4  | Comparison of Reliability Update Methods for SOVA 2      |

|   |      | 2.2.5  | Results for Hardware Reliability Update Method 2         |

| 3 | SIS  | O Dec  | oder Hardware Architectures 3                            |

|   | 3.1  | Hardw  | vare Architecture of Max-Log-MAP                         |

|   |      | 3.1.1  | Resource Utilization                                     |

|   |      | 3.1.2  | Memory Requirements                                      |

|   |      | 3 1 3  | Latency                                                  |

|   | 3.2    | Hardy  | vare Architecture for HR-SOVA            | 38 |  |  |

|---|--------|--------|------------------------------------------|----|--|--|

|   |        | 3.2.1  | Trellis Stage                            | 38 |  |  |

|   |        | 3.2.2  | Merge Stage                              | 41 |  |  |

|   |        | 3.2.3  | Decode Stage                             | 41 |  |  |

|   |        | 3.2.4  | Example of Hardware Architecture         | 42 |  |  |

|   |        | 3.2.5  | Latency and Throughput                   | 44 |  |  |

|   | 3.3    | Simpli | ified BR-SOVA Architecture               |    |  |  |

|   |        | 3.3.1  | Resource Utilization                     | 51 |  |  |

|   |        | 3.3.2  | Memory and Register Utilization          | 52 |  |  |

|   |        | 3.3.3  | Latency and Throughput                   | 53 |  |  |

|   | 3.4    | Hybrid | d-SOVA Architecture                      |    |  |  |

|   |        | 3.4.1  | Resource Utilization                     | 56 |  |  |

|   |        | 3.4.2  | Memory and Register Utilization          | 56 |  |  |

|   |        | 3.4.3  | Latency and Throughput                   |    |  |  |

|   | 3.5    | Impro  | ved BPCU for SB-SOVA                     |    |  |  |

|   |        | 3.5.1  | Resource Utilization                     | 60 |  |  |

|   |        | 3.5.2  | Memory requirements                      | 62 |  |  |

|   | 3.6    | Consid | derations for Parallel Windows           | 62 |  |  |

|   |        | 3.6.1  | Memory Organization for Multiple Windows |    |  |  |

|   |        | 3.6.2  | Estimation of Window Initial State       |    |  |  |

|   |        | 3.6.3  | Inter-Bank Memory Access                 |    |  |  |

|   | 3.7    | Comp   | arison of SOVA and Max-Log-MAP           |    |  |  |

|   |        | 3.7.1  | Resource Utilization                     |    |  |  |

|   |        | 3.7.2  | Memory Requirement                       |    |  |  |

|   |        | 3.7.3  | Data Throughput                          |    |  |  |

|   |        | 3.7.4  | Optimal SOVA Decoder                     | 70 |  |  |

| 4 | Cor    | clusio | ns                                       | 77 |  |  |

| В | ibliog | graphy | Bibliography 79                          |    |  |  |

# **Acknowledgments**

We would first like to thank our supervisor Matthias Kamuf for providing all his help, assistance and guidance throughout the entire thesis work. We really appreciate the freedom you have given us to do carry out our own research and at the same time being there giving us advice and pointers all along the way.

Thanks go to all our friends and colleagues at Ericsson Research who have helped to make our stay fruitful and interesting. Special thanks go to Fredrik Nordström for all the delightful chats and tips, and of course to Jim Svensson for his synthesis tools, scripts and VNC/SVN server that have helped the work proceed much more smoothly and efficiently.

We are also very grateful to Joachim Rodrigues at LTH for giving us the opportunity to take on this challenging project at Ericsson Research. Our appreciation goes to all our teachers and friends at LTH who have made our stay a very enjoyable and fruitful one. Lastly, we would like to thank our classmates Ruiyi Zhang and Jiangfeng Cai for all the fun times that we had working together at Ericsson, and for the great dinner.

## **Abbreviations**

**3GPP** 3rd Generation Partnership Project

ACS Add-Compare-Select

**AWGN** Additive White Gaussian Noise

BCJR Bahl-Cocke-Jelinek-Raviv

**BER** Bit Error Rate

**BLER** Block Error Rate

**BR-SOVA** Battail Rule SOVA

CRC Cyclic Redundancy Check

**FIFO** First In First Out

**HR-SOVA** Hagenauer Rule SOVA

**LIFO** Last In First Out

LTE Long Term Evolution

**LLR** Log-Likelihood Ratio

MAP Maximum-a-Posteriori

ML Maximum Likelihood

**MSOVA** Modified Soft-Output Viterbi Algorithm

PCU Path Comparison Unit

**RE** Register Exchange

**RSC** Recursive Systematic Convolutional

SB-SOVA Simplified Battail Rule SOVA

$\textbf{SISO} \hspace{1.5cm} \textbf{Soft-Input/Soft-Output}$

**SMU** Survivor Memory Unit

**SNR** Signal-to-Noise Ratio

**SOVA** Soft-Output Viterbi Algorithm

**VA** Viterbi Algorithm

# **Nomenclature**

| Δ.          | Estimated | 1 1  | 1: -:    | C    | 1- : + |       |

|-------------|-----------|------|----------|------|--------|-------|

| $u_{\iota}$ | Estimated | nard | decision | TOT. | DIL    | 71.1. |

|             |           |      |          |      |        |       |

$\nu$  Memory depth of convolutional encoder

L Merging depth for Viterbi Algorithm

$L(\hat{u}_k)$  A-posteriori value for bit  $u_k$

$L(u_k)$  A-priori value for bit  $u_k$

$L_c \cdot y_k$  Received channel values

$L_e(\hat{u}_k)$  Extrinsic value for bit  $u_k$

M Number of windows in a windowed decoder

N Number of trellis states

n Number of coded bits per information bit

S Sequence of state transitions through a trellis

$T_{crit}$  Combinatorial delay of the critical path

U Update depth for Soft-Output Viterbi Algorithm

$u_k$  Data bit to be transmitted at time t = k

W Window size

Y Received sequence of  $K_i$  symbols, with  $Y = \{y_{k,1}, y_{k,2}, \dots, y_{k,n}\}_{k=1}^{K_i}$

$y_{k,j}$  jth received bit for symbol at time t = k

$\Delta_{k,s}$  Metric difference at time t = k for state s

## Chapter 1

## Introduction

In this current age where high speed portable wireless devices such as mobile telephones and wireless networks are commonplace, the market demands for smaller devices with longer battery life are ever increasing. This leads to stringent requirements for wireless terminals that can provide higher throughput, having smaller chip size, and yet consume as little power as possible. To meet this goal, an entire receiver chain will need to be designed with the above requirements in mind. This thesis looks in detail at the turbo decoder, which forms a part of the outer receiver chain.

The channel encoding used in the 3rd Generation Partnership Project (3GPP) E-UTRA Release 8 "Long Term Evolution (LTE)" standard [1] is a turbo code, which is computationally intensive to decode, and typically implemented as a hardware accelerator module within the receiver. The Maximum-a-Posteriori (MAP)-type algorithms are commonly used as Soft-Input/Soft-Output (SISO) decoders for turbo decoding. The Log-MAP and Max-Log-MAP based decoders do have some drawbacks, namely in that they require relatively large amounts of on-chip memory for the storage of intermediate values, and high latency due to the backward recursions that need the last symbols in the block to be received before decoding can begin [2].

An alternative decoder to the MAP-type decoders is one that is based on the Soft-Output Viterbi Algorithm (SOVA). There are existing hardware implementations of Hagenauer Rule SOVA (HR-SOVA) [3][4][5], but the performance of HR-SOVA based decoders in simulations is typically about 0.7 dB worse [6] than Max-Log-MAP based ones. Another updating rule proposed by Battail [7], known as Battail Rule SOVA (BR-SOVA) gives better decoding performance than HR-SOVA, but there is no known hardware implementation of BR-SOVA in the literature.

This thesis aims to investigate the performance of a SOVA based turbo decoder, whilst using a Max-Log-MAP decoder as a baseline for comparison. A hardware architecture for a parallel windowed SOVA based turbo decoder is developed. Fi-

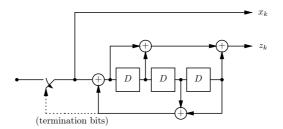

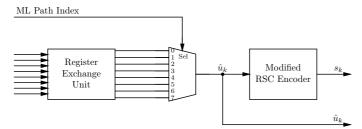

Figure 1.1: Block diagram of RSC encoder

nally, the proposed decoder is compared with a Max-Log-MAP based turbo decoder with respect to the decoding performance, hardware resource utilization, memory requirements and latency/throughput.

This chapter gives a brief introduction into the various topics covered within the thesis, so as to give context to the discussions in the chapters that follow. The channel coding algorithms used in the LTE standard are described briefly, followed by descriptions of the MAP and SOVA algorithms that can be applied to turbo decoding.

## 1.1 Turbo Decoding in LTE

The iterative turbo encoder used in LTE for data transport is made up of two 8-state, rate 1/2 Recursive Systematic Convolutional (RSC) constituent encoders that are connected in a parallel concatenated convolutional coding scheme [8].

The transfer function for a constituent convolutional encoder is given as

$$G(D) = \left[1, \frac{g_1(D)}{g_0(D)}\right]$$

where the feed-forward and feedback generator polynomials are given as

$$g_0(D) = 1 + D^2 + D^3$$

$g_1(D) = 1 + D + D^3$

A block diagram of the resulting constituent encoder is shown in Figure 1.1. Each constituent encoder generates a rate 1/2 code, and it follows that the output of the turbo encoder (before puncturing) gives a code with a rate R = 1/3.

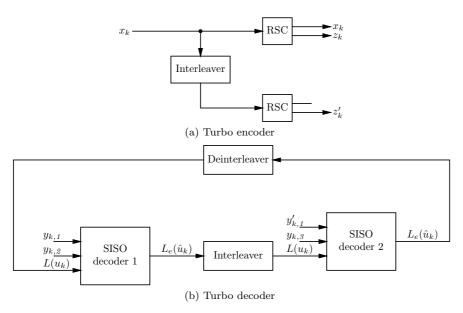

The turbo decoder in principle comprises of two SISO decoders that are separated by interleavers and deinterleavers. Block diagrams of the encoder and decoder are shown in Figure 1.2.

The format of the turbo code follows the 3GPP standard as described in [1]. It can be briefly described as follows. Consider an L-bit data block  $\{c_0, c_1, \ldots, c_{L-1}\}$

#### 1.1. TURBO DECODING IN LTE

Figure 1.2: Turbo encoder and decoder

that is checksummed by a 24-bit Cyclic Redundancy Check (CRC) with parity bits  $\{d_0, d_1, \ldots, d_{23}\}$ . The information bits to the turbo encoder will have a block length of  $K_i = L + 24$  with the following sequence.

$$\mathbf{x} = \{c_0, c_1, \dots, c_{L-1}, d_0, d_1, \dots, d_{23}\}$$

The encoded output bits of the turbo encoder will then be

$$\{x_0, z_0, z_0', x_1, z_1, z_1', \dots, x_{k-1}, z_{k-1}, z_{k-1}'\}$$

where  $z_i$  is the output of the first constituent encoder and  $z'_i$  is the output of the second constituent encoder, with the interleaved  $x_i$  as the input.  $z_i$  and  $z'_i$  are the parity bits of the first and second RSC encoders respectively.

The trellis of the turbo encoder will be terminated by feeding back the remaining bits in the shift register after all the data bits (including CRC) have been encoded using the dotted lines shown in Figure 1.1. The remaining 12 tail bits that are transmitted to terminate the trellis are given as

$$\{x_k, z_k, x_{k+1}, z_{k+1}, x_{k+2}, z_{k+2}, x_k', z_k', x_{k+1}', z_{k+1}', x_{k+2}', z_{k+2}'\}$$

which gives a total encoded output length of  $3(K_i + 4)$  bit.

A block diagram of the turbo decoder is shown in Figure 1.2b, where it can be seen that two SISO decoders are connected together through an interleaver and a

deinterleaver. In the first iteration, there is no a-priori information, so the a-priori input  $L(u_k)$  into SISO decoder 1 is zero. The extrinsic output  $L_e(\hat{u}_k)$  of SISO decoder 1 is used (after interleaving) by SISO decoder 2 as a-priori input. The extrinsic output of SISO decoder 2 will once again (after deinterleaving) be used as the a-priori input of SISO decoder 1. This feedback of extrinsic output to SISO decoder 1 starts the next iteration of the turbo decoding process. To obtain the final output, the deinterleaved extrinsic output of the SISO decoders will need to be combined with the a-priori input as described in Section 1.2.1.

The LTE turbo code internal interleaver, as described in [1], is designed to shuffle the data between the two encoders/decoders. The interleaver helps spread out the burst errors and thus improves the performance of the decoder.

The algorithms that can be used to perform turbo decoding are described in greater detail in Section 1.2.

## 1.2 Algorithms for Decoding Turbo Codes

This section presents two classes of decoders that can be used for turbo decoding, namely the MAP-type algorithms and the SOVA. Section 1.2.1 describes the Log-Likelihood Ratio (LLR) that are used to exchange information between the two constituent decoders. The details of MAP algorithm and SOVA algorithm are covered in Sections 1.2.2 and 1.2.3 respectively.

## 1.2.1 Log Likelihood Ratio

To ease the complexity of performing multiplications, operations are typically performed in the log-domain, and the Log-Likelihood Ratio (LLR) of a binary random variable  $u_k$ ,  $L(u_k)$  is defined as

$$L(u_k) = \log \frac{P(u_k = +1)}{P(u_k = -1)}$$

(1.1)

The LLR of each bit is passed between the two constituent decoders. Since  $u_k$  is in GF(2) with the elements  $\{+1, -1\}$ ,

$$P(u_k = +1) = 1 - P(u_k = -1)$$

and

$$L(u_k) = \log \frac{P(u_k = +1)}{1 - P(u_k = +1)}$$

#### 1.2. ALGORITHMS FOR DECODING TURBO CODES

Conditioning the random variable  $u_k$  on a different random variable  $y_k$ , the conditioned log-likelihood ratio  $L(u_k|y_k)$  is given by

$$L(u_k|y_k) = \log \frac{P(u_k = +1|y_k)}{P(u_k = -1|y_k)}$$

$$= \log \frac{p(y_k|u_k = +1) \cdot P(u_k = +1)}{p(y_k|u_k = -1) \cdot P(u_k = -1)}$$

$$= L(y_k|u_k) + L(u_k)$$

(1.2)

After transmitting over a channel with a fading factor a and Additive White Gaussian Noise (AWGN),

$$L(u_k|y_k) = \log \frac{p(y_k|u_k = +1) \cdot P(u_k = +1)}{p(y_k|u_k = -1) \cdot P(u_k = -1)}$$

$$= \log \frac{\exp(-E_s/N_0(y_k - a)^2)}{\exp(-E_s/N_0(y_k + a)^2)} + \log \frac{P(u_k = +1)}{P(u_k = -1)}$$

$$= 4 \cdot a \cdot \frac{E_s}{N_0} \cdot y_k + L(u_k)$$

$$= L_c \cdot y_k + L(u_k)$$

(1.3)

where  $L_c = 4 \cdot a \cdot (E_s/N_0)$  is known as the reliability value of the channel. For fading channels, a denotes the fading amplitude, but for Gaussian channels, a = 1.

The detailed derivation of the LLR values output by the constituent decoders is covered in [9]. In a similar fashion, the conditional probability can be derived, and for brevity it is stated here as follows

$$p(y_k|u_k = \pm 1) = \left(\frac{P(y_k) \cdot (1 + \exp(-L(u_k)) \cdot \exp(-L_c \cdot y_k/2))}{1 + \exp(-(L(u_k) + L_c \cdot y_k))}\right) \cdot \exp(u_k \cdot L_c \cdot y_k/2)$$

$$= B_k \cdot \exp(u_k \cdot L_c \cdot y_k/2)$$

(1.4)

where

$$B_k = \frac{P(y_k) \cdot (1 + \exp(-L(u_k)) \cdot \exp(-L_c \cdot y_k/2))}{1 + \exp(-(L(u_k) + L_c \cdot y_k))}$$

The output of the decoder is the logarithm of the ratio of the bit probability being "+1" or "-1" for a given observation of y, or

$$L(\hat{u}_k) = L(u_k|y) = \log \frac{P(u = +1|y)}{P(u = -1|y)}$$

(1.5)

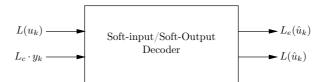

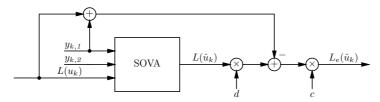

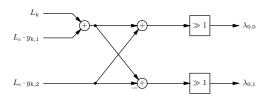

A block diagram of a SISO decoder is shown in Figure 1.3. The decoder uses the a-priori values  $L(u_k)$  for all information bits  $u_k$  and the received channel values

Figure 1.3: Block diagram of SISO decoder

$L_c \cdot y_k$  for the coded bits as inputs and returns the soft output bits of the decoder,  $L(\hat{u}_k)$  and extrinsic information  $L_e(\hat{u}_k)$ . For systematic codes, the resulting soft output information bit is given by

$$L(\hat{u}_k) = L_c \cdot y_k + L(u_k) + L_e(\hat{u}_k)$$

(1.6)

As shown in Figure 1.2b, the extrinsic output from the first constituent decoder,  $L_e(\hat{u}_k)$ , is passed via an interleaver/deinterleaver to the next constituent decoder as the a-priori input. The a-priori input to the first decoder in the first iteration is typically set to zero, as there is usually no a-priori information at this stage. By increasing the number of iterations, better decoding performance can be obtained at the expense of latency and computational cost.

## 1.2.2 MAP Type Algorithms

The traditional approach to decoding RSC codes is to use the "symbol-by-symbol" Maximum-a-Posteriori (MAP) decoding that minimizes the Bit Error Rate (BER) of the decoded bits. MAP decoding is done using the Bahl-Cocke-Jelinek-Raviv (BCJR) algorithm [10] which is optimal for estimating the outputs of a Markov process.

The MAP algorithm is not practical for implementation because of the numerical representation of probabilities, non-linear functions and the large numbers of multiplication and division operations. Log-MAP is equivalent to true MAP, but because it operates in the logarithmic domain, it avoids the implementation pitfalls associated with MAP. The Max-Log-MAP uses an approximation to simplify the Log-MAP further at the expense of some performance degradation. The MAP, Log-MAP and Max-Log-MAP algorithms will be described in the sections that follow.

#### MAP

Let  $y_{j < k}$  denote the sequence of received symbols  $y_j$  from the start of the trellis up to and including t = k - 1, and  $y_{j > k}$  be the corresponding received sequence from t = k + 1 to the end of the trellis. Using the LLR defined in (1.5),

#### 1.2. ALGORITHMS FOR DECODING TURBO CODES

$$L(\hat{u}_k) = \log \frac{P(u_k = +1|y)}{P(u_k = -1|y)} = \log \frac{\sum_{u_k = +1}^{(s',s)} P(s', s, y)}{\sum_{u_k = -1}^{(s',s)} P(s', s, y)}$$

(1.7)

where

$$P(s', s, y) = P(s', y_{j < k}) \cdot P(s, y_k | s') \cdot P(y_{j > k} | s)$$

$$= \underbrace{P(s', y_{j < k})}_{\alpha_{k-1}(s')} \cdot \underbrace{P(s | s')}_{\gamma_k(s', s)} \cdot \underbrace{P(y_{j > k} | s)}_{\beta_k(s)}$$

$$(1.8)$$

therefore

$$L(\hat{u}_k) = \log \frac{\sum_{u_k=+1}^{(s',s)} \alpha_{k-1}(s') \cdot \gamma_k(s',s) \cdot \beta_k(s)}{\sum_{u_k=-1}^{(s',s)} \alpha_{k-1}(s') \cdot \gamma_k(s',s) \cdot \beta_k(s)}$$

(1.9)

The BCJR algorithm uses both forward and backward recursions through the trellis. The branch transition probability from sequence s' to sequence s is given by the  $\gamma_k(s',s)$  term. The forward recursion is given by the  $\alpha_k(s)$  term and depends on the previous bits in the trellis. The backward recursion is given by the  $\beta_{k-1}(s')$  term, which as expected depends on the next/future bits in the trellis. Mathematically, these three terms can be written as follows

$$\gamma_k(s', s) = P(s|s') \cdot p(y_k|s', s)$$

$$= P(y_k|u_k) \cdot P(u_k)$$

(1.10)

$$\alpha_k(s) = \sum_{(s',s)} \gamma_k(s',s) \cdot \alpha_{k-1}(s')$$

(1.11)

$$\beta_{k-1}(s') = \sum_{(s',s)} \gamma_k(s',s) \cdot \beta_k(s)$$

(1.12)

As the index pair of previous and current state (s', s) determines the information bit  $u_k$  and the parity bits  $x_{k,v}$  for v = 2, ..., n in a systematic code, the probability of the received symbol given a specific data bit can be written as follows

$$P(y_k|u_k) = P(y_{k,1}|u_k) \cdot \prod_{v=2}^{n} P(y_{k,v}|x_{k,v})$$

and using (1.4),

$$P(y_k|u_k) = B_k \cdot \exp\left(\frac{1}{2}L_c \cdot y_{k,1} \cdot u_k\right) \cdot \left(\prod_{v=2}^n P(y_{k,v}|x_{k,v})\right)$$

$$= B_k \cdot \exp\left(\frac{1}{2}L_c \cdot y_{k,1} \cdot u_k + \frac{1}{2}\sum_{v=2}^n P(y_{k,v}|x_{k,v})\right)$$

(1.13)

## Log-MAP

The Log-MAP algorithm is a transformation of the MAP algorithm to the logarithmic domain, and in doing so, multiplications are converted into additions. Since it is just a change in domain, the Log-MAP algorithm gives equivalent performance to the MAP algorithm.

For brevity, the LLR expression for Log-MAP is stated as follows.

$$L(\hat{u}_{k}) = \log \frac{\sum_{u_{k}=+1}^{(s',s)} \exp\left(\alpha_{k-1}^{LM}(s')\right) \cdot \exp\left(\gamma_{k}^{LM}(s',s)\right) \cdot \exp\left(\beta_{k}^{LM}(s)\right)}{\sum_{u_{k}=-1}^{(s',s)} \exp\left(\alpha_{k-1}^{LM}(s')\right) \cdot \exp\left(\gamma_{k}^{LM}(s',s)\right) \cdot \exp\left(\beta_{k}^{LM}(s)\right)}$$

$$= \log \left(\sum_{u_{k}=+1}^{(s',s)} \exp\left(\alpha_{k-1}^{LM}(s') + \gamma_{k}^{LM}(s',s) + \beta_{k}^{LM}(s)\right)\right)$$

$$- \log \left(\sum_{u_{k}=-1}^{(s',s)} \exp\left(\alpha_{k-1}^{LM}(s') + \gamma_{k}^{LM}(s',s) + \beta_{k}^{LM}(s)\right)\right)$$

(1.14)

where  $\alpha_{k-1}^{LM}(s')$ ,  $\beta_k^{LM}(s)$  and  $\gamma_k^{LM}(s',s)$  are the forward recursion, backward recursion, and transitional probability terms respectively in the logarithmic domain.

## Max-Log-MAP

Despite having reduced the complexity of the MAP algorithm by moving to the logarithmic domain, the  $\log\left(\sum_{i=1}^k(\exp(x_i))\right)$  function in the Log-MAP remains computationally intensive to implement. The Max-Log-MAP algorithm provides reduces the complexity of the Log-MAP algorithm drastically by performing the following approximation

$$\log \left( \sum_{i=1}^{k} (\exp(x_i)) \right) = \max(\exp(x_i)) + \log \left( \sum_{i=1}^{k} (\exp(x_i - \max(x_i))) \right)$$

$$\approx \max(\exp(x_i))$$

(1.15)

By applying this approximation on the Log-MAP branch transition probabilities, Log-MAP forward and backward recursion equations, the following equations

#### 1.2. ALGORITHMS FOR DECODING TURBO CODES

are obtained

$$\alpha_k^{MLM}(s) = \max\left( \left[ \gamma_{u_k = +1}^{LM}(s', s) + \alpha_{k-1}^{LM}(s') \right], \left[ \gamma_{u_k = -1}^{LM}(s', s) + \alpha_{k-1}^{LM}(s') \right] \right)$$

(1.16)

$$\beta_k^{MLM}(s') = \max\left( \left[ \gamma_{u_k = +1}^{LM}(s', s) + \beta_k^{LM}(s) \right], \left[ \gamma_{u_k = -1}^{LM}(s', s) + \beta_k^{LM}(s) \right] \right)$$

(1.17)

$$\beta_k^{MLM}(s') = \max\left( \left[ \gamma_{u_k = +1}^{LM}(s', s) + \beta_k^{LM}(s) \right], \left[ \gamma_{u_k = -1}^{LM}(s', s) + \beta_k^{LM}(s) \right] \right)$$

(1.17)

and the resulting LLR for the Max-Log-MAP algorithm can be stated as

$$L(\hat{u}_{k}) = \max_{s',s} ([\gamma_{k}^{LM}(s',s) + \alpha_{k-1}^{MLM}(s) + \beta_{k}^{MLM}(s')],$$

$$[\gamma_{k}^{LM}(s',s) + \alpha_{k}^{MLM}(s) + \beta_{k}^{MLM}(s')])$$

$$- \max_{s',s} ([\gamma_{k}^{LM}(s',s) + \alpha_{k-1}^{MLM}(s) + \beta_{k}^{MLM}(s')],$$

$$[\gamma_{k}^{LM}(s',s) + \alpha_{k}^{MLM}(s) + \beta_{k}^{MLM}(s')])$$

(1.18)

The approximation in (1.15) degrades the performance of the Max-Log-MAP algorithm as compared with the Log-MAP. A correction factor is typically added into the Max-Log-MAP algorithm to compensate for the degradation, and is used in practice to implement Log-MAP decoders in hardware [2].

#### 1.2.3 **SOVA Algorithm**

The traditional approach to decoding convolutional codes is by using the Viterbi Algorithm (VA) that provides a Maximum Likelihood (ML) sequence [11]. The VA in the most general form is a maximum a-posteriori probability sequence estimator that finds the maximum likelihood path through the trellis diagram given a specific received sequence. Mathematically, the VA finds the trellis path that maximizes the a-posteriori probability P(S|Y).

The Soft-Output Viterbi Algorithm (SOVA) decoder outputs soft values that makes it suitable for use in turbo decoders. The modifications to enable the traditional hard-decision VA to give soft-output values was proposed in [12]. The description of SOVA that follows adopts the notation used in [13].

Assuming that the state sequence S is a Markov sequence and since the received sequence Y is independent of the trellis path selection S, the VA maximizes

$$p(S_k, Y_k) = p(S_{k-1}, Y_{k-1}) P(u_k) p(y_k | s', s)$$

(1.19)

where  $S_k = \{s_1, s_2, \dots, s_k\}, Y_k = \{y_1, y_2, \dots, y_k\}, s' = s_{k-1}, s = s_k \text{ and } u_k \text{ is the } s_k = s_k \text{ and } s$ source bit that corresponds to a state transition  $s' \to s$  in path  $S_k$ .

Since the path metric  $M_k(S_k)$  that is associated with the path  $S_k$  in the trellis is defined as

$$M_k(S_k) = \log (p(S_k, Y_k))$$

we obtain the following equation after substituting into (1.19)

$$M_k(S_k) = M_{k-1}(S_k) + \log P(u_k) + \log(p(y_k|s',s))$$

(1.20)

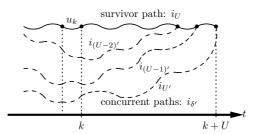

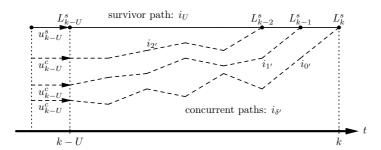

Figure 1.4: Trellis diagram showing survivor and discarded concurrent paths

A forward recursion similar to that in the Log-MAP algorithm (1.11) is used to compute the path metrics. The metric of the *i*th path at t = k can be expressed recursively [9][13] as

$$M_{k}(S_{k}) = M_{k-1}(S_{k-1}) + \frac{1}{2}L(u_{k}) \cdot u_{k} + \frac{1}{2}\sum_{v=1}^{n}L_{c} \cdot y_{k,v} \cdot x_{k,v}$$

$$M_{k}(S_{k}) = M_{k-1}(S_{k-1}) + \frac{1}{2}L(u_{k}) \cdot u_{k} + \frac{1}{2}L_{c} \cdot y_{k,1} \cdot u_{k}$$

$$+ \frac{1}{2}\sum_{v=2}^{n}L_{c} \cdot y_{k,v} \cdot x_{k,v}$$

$$(1.21)$$

where (1.22) is the special case of (1.21) for systematic codes with  $y_{k,1}$  denoting the received systematic bit. It is useful to note that both (1.21) and (1.22) only hold for convolutional codes generated by feedback encoders, and not for codes generated by feed-forward encoders.

The desired soft output bit is decided by the VA after a merging delay of U bit. At t=k+U, the VA has selected the survivor path  $i_U$  that terminates at the ML state as shown in Figure 1.4. The other (concurrent) path terminating at the ML state  $i_{U'}$  is discarded. Since the path  $i_U$  decides the soft output of  $\hat{u}_k$  at t=k, there are a total of U+1 discarded non-surviving paths denoted by  $i_{0'}, i_{1'}, \ldots, i_{U'}$ , one for each state in path  $i_U$  between t=k and t=k+U. The metric difference for a state on the path along  $i_U$  is defined as

$$\Delta_{k+l} = M_{k+l}(s_{k+l}) - M_{k+l}(s'_{k+l}) \tag{1.23}$$

The probability, P(correct) of a correct path decision of the survivor at t = k + l given that  $y_{j \le k + l}$  can be simplified as [13]

$$P(correct) = \frac{\exp(\Delta_{k+l})}{1 + \exp(\Delta_{k+l})}$$

(1.24)

#### 1.2. ALGORITHMS FOR DECODING TURBO CODES

Figure 1.5: Trellis diagram for HR-SOVA

This leads to the LLR of the binary path decision to be

$$\log \frac{P(correct)}{1 - P(correct)} = \Delta_{k+l}$$

(1.25)

The resulting soft output of the SOVA is the decision bit  $\hat{u}_k$  multiplied by the reliability values of all the errors, which can be approximated using

$$L(\hat{u}_k) \approx \hat{u}_k \cdot \min_{l=0,\dots,U} \Delta_{k+l}$$

(1.26)

where the minimum in (1.26) is taken over all the non-surviving paths that would have led to a different decision bit  $\hat{u}_k$ . Equation 1.26 shows that the same hard decisions  $\hat{u}_k$  that are obtained in classical VA, together with the updates considering the non-surviving paths are used to obtain the LLR of each bit.

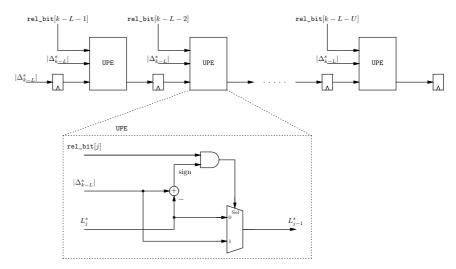

To make (1.26) easier to implement in practice, update rules are used to modify the metric differences during decoding. The update rule given in (1.26) is often referred to as the Hagenauer rule [12], or HR-SOVA, and can be written mathematically as follows:

$$L_{k-U}^s \leftarrow \min\left[L_k^s, L_{k-U}^s\right] \quad \text{when } u_{k-U}^s \neq u_{k-U}^c \tag{1.27}$$

The updating in (1.27) is applied for U time steps between t = k and t = k-U+1and thus it can be seen that each reliability value,  $L_{k-U}^{s}$  can be updated up to Utimes. As shown in Figure 1.5, the Hagenauer rule considers the survivor path, as well as up to U concurrent paths to the survivor path, using the cases when the concurrent path will give a different decision bit  $(\hat{u}_{k-U})$  to update the reliability values, thus re-stating (1.26).

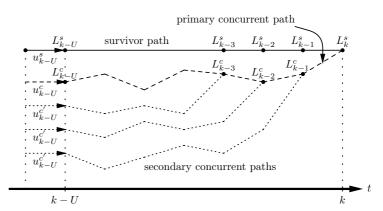

Another update rule in the literature that was described by Battail [7], often referred to as the Battail updating rule or BR-SOVA is given as:

$$L_{k-U}^s \leftarrow \min\left[L_k^s, L_{k-U}^s\right]$$

when  $u_{k-U}^s \neq u_{k-U}^c$  (1.28a)

$$L_{k-U}^s \leftarrow \min \left[ L_k^s, L_{k-U}^c \right] \qquad \text{when } u_{k-U}^s \neq u_{k-U}^c \qquad (1.28a)$$

$$L_{k-U}^s \leftarrow \min \left[ L_k^s + L_{k-U}^c, L_{k-U}^s \right] \qquad \text{when } u_{k-U}^s = u_{k-U}^c \qquad (1.28b)$$

Figure 1.6: Trellis diagram for BR-SOVA showing one primary concurrent path

The Battail rule is not documented in sufficient detail in the open literature other than the two updating rules in (1.28), and so an interpretation of BR-SOVA is used in the analysis that follows. In addition to the U concurrent paths to the survivor path considered by the Hagenauer rule, the Battail rule considers the U secondary concurrent paths to the main (primary) concurrent path. Figure 1.6 shows one primary concurrent concurrent path and the resulting secondary concurrent paths. The secondary concurrent paths to the main concurrent path are traced back to t=k-U, and the decision bit of the main concurrent path  $(u_{k-U}^c)$  is compared with the decision bit of the secondary concurrent path  $(u_{k-U}^c)$  and the HR-SOVA update rules in (1.27) are used to update  $L_{k-U}^c$ . Finally, the reliability bits of the survivor path  $(u_{k-U}^s)$  and main concurrent path  $(u_{k-U}^c)$  are compared, and the BR-SOVA updating rules in (1.28) are applied to update  $L_{k-U}^s$ .

The updates in the previous paragraph will be repeated for all U primary concurrent paths and thus up to U updates can be applied to every  $L_{k-U}^s$ . BR-SOVA thus provides for possibly the same number of reliability value updates as HR-SOVA.

## Chapter 2

# Improved SOVA Algorithm

This chapter describes the modifications that are made to the traditional Hagenauer Rule SOVA (HR-SOVA) and Battail Rule SOVA (BR-SOVA) algorithms to improve the performance of the SOVA algorithms. The modifications to the SOVA algorithms are described in Section 2.1. The results and analysis from computer simulations are presented in Section 2.2.

## 2.1 Modifications to SOVA

Based on the HR-SOVA as presented in [12] and [13], there have been various modification techniques presented to improve its performance. The algorithmic improvements to SOVA that were investigated can be divided into three main categories, namely by varying the merging and update depths, scaling and thresholding intermediate values, and modifying the reliability update values. These three categories are described in Sections 2.1.1, 2.1.2 and 2.1.3. With hardware architecture in mind, Sections 2.1.4 and 2.1.5 describe the various considerations and modifications made to the SOVA algorithm in order to improve hardware performance.

## 2.1.1 Merging and Updating Depths

In a practical decoder, it is not possible to perform VA over the entire block of channel data due to the excessive latency and storage requirements. Instead, sliding windows of merging depth L and update depth U are used to limit the traceback and decoding depths. One possible modification is to vary L and U parameters for the SOVA algorithm. Increasing L will increase the likelihood for a merged path while using a larger U increases the number of updates for the reliability value. However, it is clear that increasing these two values will increase the memory requirements and latency.

The simulation results for determining the optimal values for L and U are presented in Section 2.2.2. Hardware considerations such as performance, latency

and hardware requirements are also discussed in Section 2.2.2.

## 2.1.2 Reliability Thresholding

As described in [6], the output of the SOVA decoder tends to be over-estimated due to a correlation between the extrinsic output and the intrinsic input into the decoder. Moreover, since SOVA only considers two paths, it is possible that the output will be overly optimistic when the closest "true" competitor to the ML path is eliminated and thus the resulting metric difference between the surviving ML path and its concurrent path is larger than it should be. This occurrence will result in an over-estimation of the final reliability value  $L(\hat{u}_k)$ , which may result in errors in the output of the decoder. In order to overcome this issue, several remedies have been proposed in various papers. In [7], the authors proposed to apply a thresholding limit  $\Delta_{TH}$  on the metric difference value  $\Delta_{k,s}$  by applying the following rule

$$\Delta_{k,s} \leftarrow \Delta_{TH} \quad \text{if } \Delta_{k,s} > \Delta_{TH}$$

(2.1)

The value of  $\Delta_{TH}$  needs to be selected with caution. When using  $\Delta_{TH}$  that is too low, the resulting output may be over-compensated, resulting in an overly pessimistic reliability output which may be significant enough to adversely affect the decoding result in the next iteration. When  $\Delta_{TH}$  is too large, the thresholding does not take effect, and does not provide the necessary compensation.

According to [7], the appropriate value for  $\Delta_{TH}$  is dependent on the channel quality and the optimum value is usually determined by simulation. For the case when the SOVA decoder is implemented in hardware, quantization effects will also need to be taken into consideration. To simplify hardware implementation, the value of  $\Delta_{TH}$  can be selected to be a power of 2. The simulation results for the reliability thresholding are presented and discussed in section 2.2.

### 2.1.3 Scaling of SOVA Outputs

An alternative approach to control the extrinsic reliability values is to apply attenuation factors on two parameters, namely the immediate output of the SOVA decoder,  $L(\hat{u}_k)$ , and the input to the next decoder,  $L_e(\hat{u}_k)$  as described in [14] and [15]. To re-cap from section 1.2.3, the output of the SOVA decoder and the input to the next SOVA decoder are related by

$$L_e(\hat{u}_k) = L(\hat{u}_k) - (L(u_k) + L_c \cdot y_k)$$

=  $L(\hat{u}_k) - L_i(u_k)$  (2.2)

where  $L_i(u_k)$  represents the intrinsic input information provided to the SOVA decoder.

The attenuation of the output reliability values is applied by scaling them with a pair of parameters (c, d) as shown in Figure 2.1. Mathematically, the scaling can

#### 2.1. MODIFICATIONS TO SOVA

Figure 2.1: Modified SOVA with scaling factors c and d

Number of Bits Scale Value Binary Representation 0.250.01b3 bit 0.1b2 bit 0.50.625 0.101b4 bit 0.75 3 bit 0.11b0.8750.111b4 bit

Table 2.1: Efficient hardware scaling values

be expressed as follows

$$L_e(\hat{u}_k) = c(d \cdot L(\hat{u}_k) - L_i(u_k)) \tag{2.3}$$

As the factors c and d are attenuation factors, they obey the following condition.

$$0 < c, d \le 1 \tag{2.4}$$

The detailed analysis of this Modified Soft-Output Viterbi Algorithm (MSOVA) approach is covered in [14] where MSOVA simulations with varying (c,d) parameters are performed. However, the simulation results documented so far are only based on HR-SOVA update rule but not BR-SOVA. Since the performance of BR-SOVA in turbo decoding is to be investigated, the performance of MSOVA with the BR-SOVA update rule is also considered in this report.

With hardware considerations in mind, it is desirable to consider the computation of extrinsic reliability values in the domain of fixed point operations. This indicates that (c, d) parameters are to be quantized. Examples of scaling values of (c, d) and the number of bits that will be needed to represent these values in fixed point are tabulated in Table 2.1.

The simulation results for MSOVA with BR-SOVA and HR-SOVA update rules are presented and discussed in section 2.2.2.

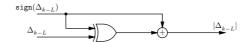

### 2.1.4 Simplification of BR-SOVA Update Rule

According to the BR-SOVA update rules given in (1.28), when  $u_{k-U}^s = u_{k-U}^c$ ,  $L_j^c$  is to be updated with reliability values of its own secondary concurrent paths,

according to the HR-SOVA update rule. The process is equivalent to that being performed for  $L_j^s$ , which is  $L_j^s \leftarrow \min \{L_j^s, \Delta_k^s\}$ . This implies that for BR-SOVA, the HR-SOVA reliability update rule needs to be applied twice for every pair of survivor-concurrent paths, with the survivor path update dependent on the results of the concurrent path update.

The additional updates will result in a more complicated implementation of BR-SOVA as compared to HR-SOVA. In addition to the hardware complexity to perform the updates, there is a need to store  $L_j^c$ , which will require extra memory to store concurrent path information. As the two updates to the reliability values have to be performed serially, the overall latency for BR-SOVA is expected to be increased.

With increased complexity, BR-SOVA is expected to take a longer time in simulation as compared to HR-SOVA. For hardware implementation, BR-SOVA is expected to consume more hardware resources and to have a longer processing latency.

Considering practical issues such as latency and hardware cost, it is desirable to investigate methodologies to reduce the simulation time, and more importantly to reduce the chip area used in hardware implementations of BR-SOVA. To this end, the following simplification for BR-SOVA is considered.

$$L_j^s \approx \begin{cases} \min\left\{\Delta_k^s, L_j^s\right\} & \text{when } u_j^s \neq u_j^c\\ \min\left\{\Delta_k^s + \Delta_j^c, L_j^s\right\} & \text{when } u_j^s = u_j^c \end{cases}$$

(2.5)

Equation (2.5) shows that  $L_j^s$  is updated with  $\Delta_j^c$  instead of  $L_j^c$  when  $u_k^s = u_k^c$ . The analogy for the above simplification is as follows. Since  $L_j^c$  is supposed to be updated with the minimum among all its concurrent  $\Delta_j$ , it can be deduced that

$$\Delta_i^c \geq L_i^c$$

which implies that

$$\Delta_k^s + \Delta_j^c \ge \Delta_k^s + L_j^c$$

This equation implies that  $L_j^s$  is updated with a value larger than  $\Delta_k^s + L_j^c$ , which means that it is less likely for  $\Delta_k^s + \Delta_j^c$  to be smaller than  $L_j^s$ . The effect of this simplification will only be that  $L_j^s$  will be updated less often than in the original BR-SOVA. The effect of reduced update occurrences for  $u_j^s = u_j^c$  may be investigated with simulations. Simulation results for the Simplified Battail Rule SOVA (SB-SOVA) update rule are presented and discussed in section 2.2.3.

The advantage in the SB-SOVA update rule can be observed as follows. With the simplification,  $L_j^s$  update can be performed immediately when the condition is met, without having to update  $L_j^c$  first. This eliminates the extra complexity involved in updating  $L_j^s$  with  $\Delta_j$  of other concurrent paths. This also eliminates the need to wait for  $L_j^c$  to be updated before  $L_j^s$  update is performed, thus reducing the latency when SB-SOVA is applied.

#### 2.1. MODIFICATIONS TO SOVA

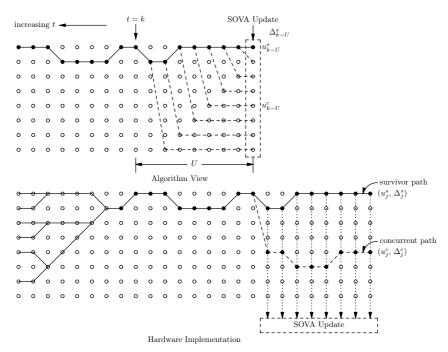

Figure 2.2: Two methods to perform SOVA updates

## 2.1.5 Reliability Update Methods for SOVA

Consider a U-stage survivor path sequence that is obtained at stage k, via Viterbi decoding traceback. The hardware decision bits and corresponding reliability values of the survivor path are denoted by

$$\{u_{k-j}^s, L_{k-j}^s\}$$

for  $j = 1, 2, \dots, U$

Given these information, there are two methods to perform updates on the reliability values  $L_{k-j}^s$ , namely the algorithmic and hardware methods. Figure 2.2 presents a graphical representation of these two methods of reliability updates for SOVA, which are described in the following sections.

#### **Algorithmic**

The algorithmic method presented in most technical papers involves performing updates on just the reliability value  $L^s_{k-U}$  of the last decision bit  $u^s_{k-U}$ . In this case, all the concurrent paths emerging from the survivor path are considered. During reliability updates,  $L^s_{k-U}$  is updated with  $\Delta^s_{k-j}$  (HR-SOVA),  $L^c_{k-U}$  and  $L^s_{k-j}$  (BR-SOVA), or  $\Delta^c_{k-U}$  and  $L^s_{k-j}$  (SB-SOVA).

Figure 2.3: Merged survivor and concurrent paths

A U-stage survivor path is expected to have at most U-1 concurrent paths. For these concurrent paths, there may be cases where the concurrent path merges with the survivor path before stage k-U (as shown in Figure 2.3). When the paths merge,

$$u_{k-U}^s = u_{k-U}^c$$

and  $L_{k-i}^s = L_{k-i}^c$ .

which implies that no update is expected for HR-SOVA since the survivor and concurrent decision bits are the same.

As for BR-SOVA, the condition when the decision bits are the same is such that

$$\begin{split} L_{k-j}^s &= \min\left\{\Delta_k^s + L_{k-j}^c, L_{k-j}^s\right\} \\ &= \min\left\{\Delta_k^s + L_{k-j}^s, L_{k-j}^s\right\} \\ &= L_{k-j}^s \quad \text{always} \end{split}$$

Thus, there will once again be no reliability update in this case.

The detailed description of the algorithmic SOVA decoding is as follows. At every stage/time index k, the state metric  $M_i$  of every state i is obtained. The ML state  $s_k$  is selected among the N states based on maximum metric value.

Starting from state  $s_k$ , a U-stage traceback is performed to obtain the ML state sequence  $\{s_{k-1},\ldots,s_{k-U}\}$ . The corresponding hard decision bits  $\{u_{k-1}^s,\ldots,u_{k-U}^s\}$  and metric difference values  $\{\Delta_{k-1}^s,\ldots,\Delta_{k-U}^s\}$  are also obtained.

For  $s_{k-1}$  to  $s_{k-U}$ , the corresponding survivor and concurrent paths are extracted to determine the decision bits  $u_{k-U}^s$  and  $u_{k-U}^c$ . The reliability value for decision bit  $u_{k-U}^s$  is then updated as follows.

For HR-SOVA,

$$L_{k-U}^s = \min_{\substack{u_{k-U}^c \neq u_{k-U}^s}} \left\{ \Delta_{k-j}^s \right\} \quad \text{for } j = 1, \dots, U$$

#### 2.1. MODIFICATIONS TO SOVA

For BR-SOVA,

$$L_{k-U}^{s} = \begin{cases} \min \left\{ \Delta_{k-j}^{s} \right\}, & u_{k-U}^{c} \neq u_{k-U}^{s} \\ \min \left\{ \Delta_{k-j}^{s} + L_{k-U}^{c} \right\}, & u_{k-U}^{c} = u_{k-U}^{s} \end{cases} \text{ for } j = 1, \dots, U$$

which can be further simplified using the simplified BR-SOVA updating rules to obtain

$$L_{k-U}^s \approx \begin{cases} \min \left\{ \Delta_{k-j}^s \right\}, & u_{k-U}^c \neq u_{k-U}^s \\ \min \left\{ \Delta_{k-j}^s + \Delta_{k-U}^c \right\}, & u_{k-U}^c = u_{k-U}^s \end{cases} \text{ for } j = 1, \dots, U$$

For the algorithmic SOVA method, the survivor path does not need to begin from a merged point. The survivor path depth U however needs to be sufficient for the path to merge at  $s_{k-U}$ .

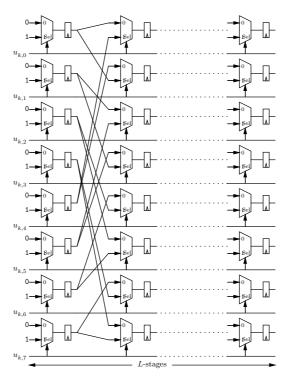

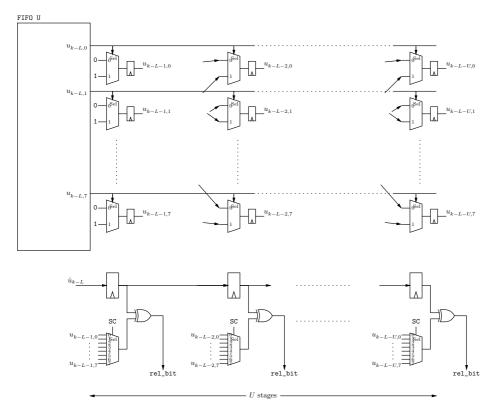

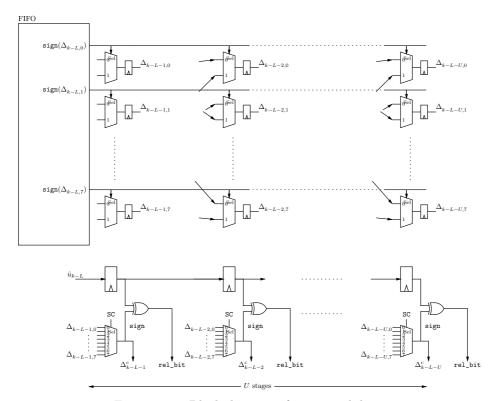

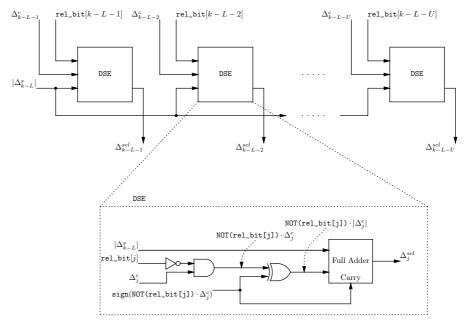

#### Hardware

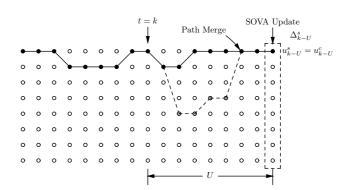

In the previous section, SOVA reliability updates are performed on a single  $L_{k-U}^s$  value with multiple concurrent paths. This section presents an alternative update method that is suitable for use in hardware implementations.

Given the same U-stage survivor path and its first concurrent path emerging from stage k-1, all U reliability values  $L_{k-j}^s$  within the same survivor path can be updated with  $L_k^s$ , as shown in the lower sub-figure of Figure 2.2.

The motivation for performing such an update method is to take advantage of the concurrent nature of hardware. With U sets of identical hardware that each performs reliability update for a single bit, the U instances of  $L_{k-j}^s$  can be updated concurrently within the same clock cycle.

Since reliability values of the survivor path from stage k-1 onwards are being updated, it is crucial to ensure that the survivor path has indeed merged. Hence, an important assumption to be made for this reliability update method is that the survivor path is starting at an ML state  $s_k$  where all the paths have merged, which means that a sufficiently large merge window, L is needed prior to performing SOVA reliability updates.

Given that the current trellis stage is computing the state metric at stage k, an L-stage Viterbi traceback is required to obtain the merged state at k-L. For all paths to merge at stage k-L, simulation results show that L has to be at least 5 to 10 times the constraint length, with the former suitable for rate R=1/2 codes and the latter for higher coding rates. From stage k-L onwards, a reliable U-stage survivor path is then determined via traceback. With that, the survivor path will have its ML state sequence starting from  $s_{k-L}$  be represented by  $s_{k-L-1}$  to  $s_{k-L-U}$ . The corresponding decision bits and metric differences will be

$$\left\{u_{k-L-1}^s,\dots,u_{k-L-U}^s\right\}, \text{ and } \left\{\Delta_{k-L-1}^s,\dots,\Delta_{k-L-U}^s\right\}$$

The first concurrent path emerging from stage k-L will have its decision bits and metric differences represented by

$$\left\{u_{k-L-1}^c,\ldots,u_{k-L-U}^c\right\},$$

and  $\left\{\Delta_{k-L-1}^c,\ldots,\Delta_{k-L-U}^c\right\}$

For each  $L_{k-L-j}^s$  to be updated with sufficient number of reliability values, U has to be 3 to 5 times the constraint length. The effect of varying the merging and updating windows are presented with simulation results in Section 2.2.4.

#### 2.2 Simulation Results

#### 2.2.1 Simulation Environment

Based on the algorithmic studies made in Section 2.1, this section presents the simulation results obtained for these studies. Simulation is performed under an in-house simulation environment based on the open-source IT++ [16] package.

As the objective of the thesis is to evaluate the performance of a SOVA based turbo decoder under the LTE environment, the LTE internal interleaver is used for all simulations. In order to have meaningful performance comparisons of the turbo decoder with academic literature, an AWGN channel is used.

The performance of SOVA for simulation is determined by its BER and Block Error Rate (BLER) performance. The receiver in LTE accepts or discards data blocks based on the CRC checksum. If the CRC checksum of a block fails, the entire data block will be discarded. Under such circumstances, the BLER is a more accurate indication for performance than BER, as the BLER is a direct indication of the data throughput performance of the turbo decoder.

In turbo decoding, the MAP and Log-MAP algorithms give the optimal baseline performance for an a-posteriori probability decoder. The Max-Log-MAP algorithm is an approximation of the Log-MAP algorithm and its performance is sufficiently comparable to that of Log-MAP. In hardware implementations for turbo decoders, the Max-Log-MAP algorithm is commonly used due to the fact that Max-Log-MAP is reasonably simpler in hardware implementations, and yet able to achieve performance that is close to Log-MAP. The Max-Log-MAP algorithm therefore serves as a basis of comparison when evaluating the performance of the SOVA algorithms.

#### 2.2.2 Optimum Reliability Thresholding and Scaling Factors for SOVA

This section presents the simulation results for SOVA with reliability thresholding  $\Delta_{TH}$  and MSOVA applied. The values of  $\Delta_{TH}$  and sets of MSOVA parameters (c,d) used for the simulation are listed as follows.

$$\Delta_{TH} = \{8, 16, 32, 64\}$$

$$(c, d) = \{0.25, 0.5, 0.68, 0.75, 0.8, 1.0\}$$

#### 2.2. SIMULATION RESULTS

Table 2.2: Simulation conditions to determine optimum  $\Delta_{TH}$

| Environment:          | AWGN channel               |  |  |  |

|-----------------------|----------------------------|--|--|--|

| Block length:         | 4416                       |  |  |  |

| Number of blocks:     | 250                        |  |  |  |

| Total data size:      | $\approx 10^6 \text{ bit}$ |  |  |  |

| Simulation Parameters |                            |  |  |  |

| T /1 CC : /C          | 1 11 TT 4.41C              |  |  |  |

Length of Survivor/Concurrent paths: U = 4416Fixed: (c, d) = (0.75, 1.00)Variant:  $\Delta_{TH} = \{8, 16, 32, 64\}$

Number of half iterations: 12, 16

The parameters listed above are applied to both HR-SOVA and BR-SOVA. For Max-Log-MAP, a log-scale factor of 0.75 is applied to the extrinsic reliability output  $L_e(\hat{u}_k)$ , as the addition of a log-scale factor will improve the Max-Log-MAP decoder's performance [14].

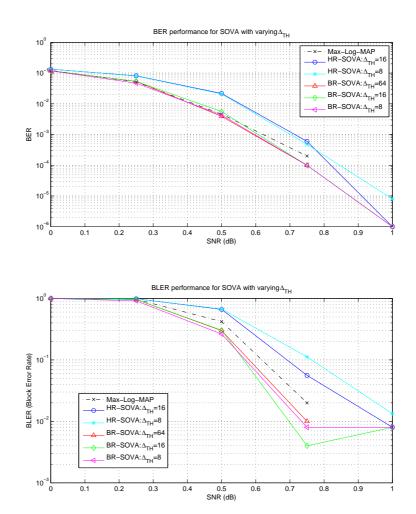

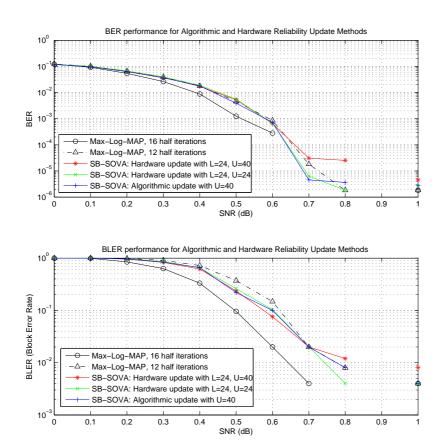

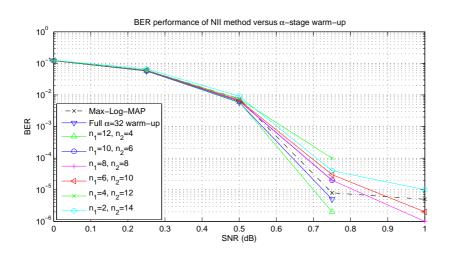

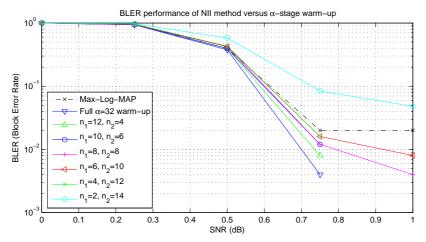

In order to determine the effect of  $\Delta_{TH}$ , simulations are performed with conditions listed in Table 2.2. The BER and BLER performance curves are shown in Figure 2.4. Note that the results of  $\Delta_{TH}=32$ , 64 for HR-SOVA and  $\Delta_{TH}=32$  for BR-SOVA are not included in the plots because for both SOVAs, the results for  $\Delta_{TH}=16$  and  $\Delta_{TH}=32$  are similar and thus only results for  $\Delta_{TH}=16$  are shown. In the case of  $\Delta_{TH}=64$ , the results obtained by using HR-SOVA indicate that  $\Delta_{TH}$  is too large for the thresholding to be effective and thus the non-meaningful result has been omitted from the plots.

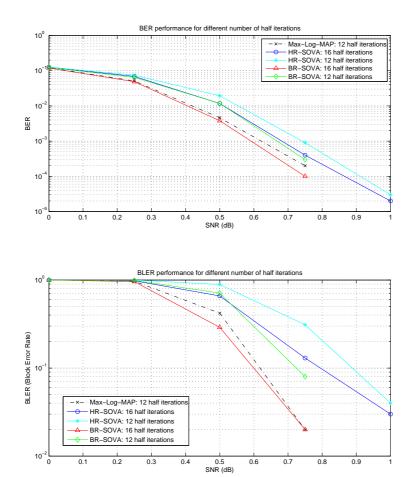

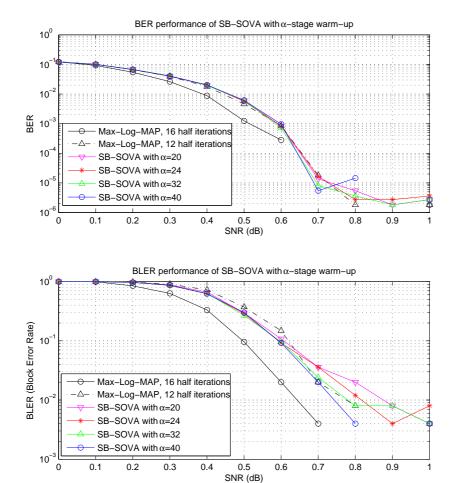

Another important observation from the simulation results is that the HR-SOVA and BR-SOVA turbo decoders both require at least 16 half iterations to obtain BER/BLER performance that is comparable to Max-Log-MAP with 12 half iterations. This is illustrated in a separate graph as shown in Figure 2.5. The number of iterations has an impact on the overall data throughput and is discussed in Section 3.7.

As observed from Figure 2.4, the performance for HR-SOVA with  $\Delta_{TH}=16$  is better than  $\Delta_{TH}=8$ . With reliability thresholding, the performance of HR-SOVA is approximately 0.1 to 0.2 dB worse than Max-Log-MAP. The performance of HR-SOVA is found to be similar to that of Max-Log-MAP at lower Signal-to-Noise Ratio (SNR), but at higher SNR, the BLER performance is worse than Max-Log-MAP and increasing the thresholding value does not improve the performance.

The performance for BR-SOVA with reliability thresholding is found to be comparable to Max-Log-MAP for BER performance. Its BLER performance is found to be approximately 0.1 dB better than Max-Log-MAP. At SNR of between

Figure 2.4: BER and BLER performance for SOVA with varying  $\Delta_{TH}$

0 dB and 0.5 dB, the BLER performance of BR-SOVA is best at  $\Delta_{TH}=8$ . For SNR higher than 0.5 dB, BR-SOVA with  $\Delta_{TH}\geq 16$  and  $\Delta_{TH}=64$  have BLER that is better than Max-Log-MAP.

The simulation results in Figure 2.4 are based on SOVA reliability updating performed over the entire block length  $K_i$ , using the algorithmic method as described

## 2.2. SIMULATION RESULTS

Figure 2.5: BER and BLER performance for SOVA with varying number of iterations  $\frac{1}{2}$

in section 2.1.5, that is  $U=K_i$ . Although the performance for BR-SOVA is better than Max-Log-MAP, it is however not feasible from the hardware architecture point of view. The algorithmic method translates to a higher hardware resource utilization, especially when the block length is large. To take a more practical approach, the reliability update path is instead limited by a window size U, where  $U < K_i$ .

Table 2.3: Simulation conditions to determine optimum MSOVA parameters

| Environment:                      | AWGN channel                                           |  |  |

|-----------------------------------|--------------------------------------------------------|--|--|

| Block length:                     | 4 416                                                  |  |  |

| Number of blocks:                 | 250                                                    |  |  |

| Total data size:                  | $\approx 10^6$ bit                                     |  |  |

| Simulation Parame                 | ters for HR-SOVA                                       |  |  |

| Update Depth $U$ :                | 40                                                     |  |  |

| $\Delta_{TH}$ :                   | 16                                                     |  |  |

| (c,d):                            | (0.75, 1.0) (0.75, 0.75) (0.75, 0.8) (0.68, 0.8)       |  |  |

| Simulation Parameters for BR-SOVA |                                                        |  |  |

| Update Depth $L$ :                | 40                                                     |  |  |

| $\Delta_{\mathit{TH}}$ :          | 8                                                      |  |  |

| (c,d):                            | (0.75, 1.0) $(0.75, 0.75)$ $(0.75, 0.8)$ $(0.68, 0.8)$ |  |  |

The value of U then becomes an additional parameter to vary for the simulation. As a rule thumb, an update window U of 10 times the constraint length is sufficient for all paths to merge, and thus U=40 is selected for the following simulations.

The simulation results presented so far are for conditions where the MSOVA parameters are kept constant, while determining the optimum  $\Delta_{TH}$  for each SOVA method. To determine the optimum MSOVA parameters, simulations under conditions listed in Table 2.3 are performed and the results are shown in Figure 2.6.

As observed from the results, the optimum (c,d) parameters for HR-SOVA is found to be (0.75,0.8). However, it should be noted that it is not possible to precisely represent the value 0.8 using fixed point representation which will translate into a performance degradation when implemented in hardware. To mitigate this, more bits may be used to represent the scale factor. As an example, 0.8 can be approximated by 0.796875 = 0.110011b which will require 7 bit to represent. A larger multiplier will be needed, and the result will have a longer wordlength. This will translate to either higher storage requirements for the extrinsic values, or will require truncation of the result of the multiplication. The truncation of the result will however reduce the advantage of choosing to have higher precision for the multiplication.

For BR-SOVA, the parameter set (0.75, 1.00) is observed to give the best performance, with performance comparable to that of Max-Log-MAP.

As observed from the simulation results, the improvements on HR-SOVA is possible with  $\Delta_{TH}$  and (c,d) parameters, but the price to pay is the increased wordlength required to implement the scale factor of 0.8. For BR-SOVA, per-

#### 2.2. SIMULATION RESULTS

Figure 2.6: Simulation results for SOVA with varying (c, d) parameters

formance that is comparable or even better than Max-Log-MAP is achieved with attenuation of only the extrinsic reliability output (parameter c) and  $\Delta_{TH}$ . There is no need for further attenuation of the intrinsic reliability output (parameter d) to obtain desirable BER/BLER performance for BR-SOVA. This is equivalent to the same log scale factor being applied to Max-Log-MAP. Thus, it can be concluded that for BR-SOVA, a properly selected reliability threshold value and an attenuation of the extrinsic reliability output are sufficient to obtain acceptable BER and BLER performance.

With the above presented results, the optimum MSOVA parameters and reliability threshold values for HR-SOVA and BR-SOVA are summarized as follows:

Table 2.4: Simulation conditions with SB-SOVA

| Environment: | AWGN channel |

|--------------|--------------|

|              |              |

Block length:  $4\,416$ Number of blocks: 250Total data size:  $\approx 10^6$  bit

#### Simulation Parameters

Update method: Algorithmic with U = 40

(c,d) = (0.75, 1.00)

$\Delta_{TH} = \begin{cases} 8 & \text{SNR} \le 0.75 \text{ dB} \\ 16 & \text{SNR} > 0.75 \text{ dB} \end{cases}$

HR-SOVA:

$$\begin{aligned} (c,d) &= (0.75,0.8) \\ \Delta_{TH} &= 16 \quad \text{for all SNR} \end{aligned}$$

BR-SOVA:

$$(c,d) = (0.75, 1.0)$$

$$\Delta_{TH} = \begin{cases} 8 & \text{SNR} \le 0.5 \text{ dB} \\ 16 & \text{SNR} > 0.5 \text{ dB} \end{cases}$$

#### 2.2.3 Effects of Simplified BR-SOVA Update Rule

As described in section 2.1.4, the main challenge of implementing BR-SOVA in hardware is due to the high complexity involved in updating the concurrent reliability values  $L_j^c$ . The SB-SOVA update rule described in Section 2.1.4 will eliminate the process of updating the concurrent reliability value  $L_j^c$ . This simplification will reduce the hardware complexity of SB-SOVA as compared to BR-SOVA.

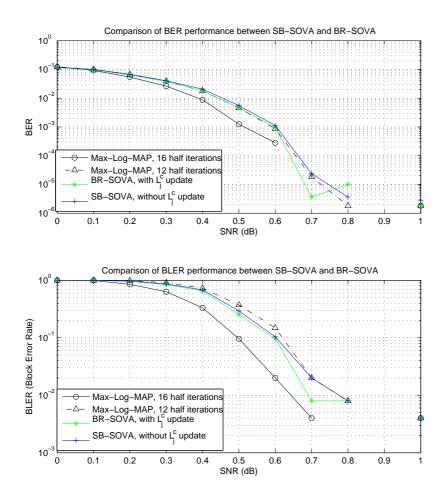

To determine the extent of the degradation in the performance of SB-SOVA, BER and BLER performance simulations under the conditions in Table 2.4 were performed and the BER and BLER plots are shown in Figure 2.7.

The simulation results show that SB-SOVA has less than 0.1 dB degradation as compared to BR-SOVA. Even with this degradation, the performance of SB-SOVA is still comparable to that of Max-Log-MAP with 12 iterations, and with less than 0.15 dB in degradation as compared to Max-Log-MAP with 16 iterations.

## 2.2. SIMULATION RESULTS

Figure 2.7: Simulation results for SB-SOVA versus BR-SOVA

This shows that SB-SOVA update rule is a reasonable simplification to make for BR-SOVA from the BER/BLER performance point of view.

# 2.2.4 Comparison of Reliability Update Methods for SOVA

As described in section 2.1.5, there are mainly two ways to perform SOVA reliability updates on the traceback trellis, namely the algorithmic and hardware methods.

Table 2.5: Simulation conditions with different reliability update methods

| Environment:               | AWGN channel               |

|----------------------------|----------------------------|

| Block length:              | 4 416                      |

| Number of blocks:          | 250                        |

| Total data size:           | $\approx 10^6 \text{ bit}$ |

| Simulation Parameters      |                            |

| $\Delta_{TH} = 8$          |                            |

| (c,d) = (0.75, 1.0)        |                            |

| Reliability update method: |                            |

| Algorithmic $U$ :          | 40                         |

| Hardware $(L, U)$ :        | (24,40), (20,20)           |

The simulation results presented so far are only based on the algorithmic method. In this section, simulations are performed to show the equivalence of the algorithmic and hardware methods.

The performance of the two methods for SB-SOVA are presented in Figure 2.8 with the simulation conditions in Table 2.5. The results show that the BER and BLER performance of the two methods deviate from each other by at most 0.05 dB. This implies that the two reliability update methods are equivalent. Since the results for the algorithmic and hardware methods are similar, all future simulation results presented will utilize one of the two proposed methods.

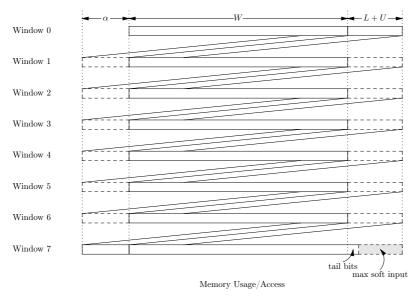

## 2.2.5 Results for Hardware Reliability Update Method

As described in Section 2.1.5, the hardware update method is made up of an L-step merge stage and a U-step update/decode stage. At the merge stage, the traceback has to be sufficiently long for all states to merge. Based on academic studies, selecting L that is at least 5 times the constraint length is sufficient for all paths to merge into a common starting state. For LTE turbo codes, the constraint length is 4 and hence a minimum L=20 is sufficient.

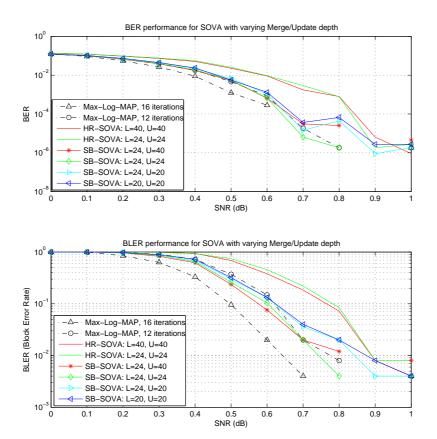

Simulations can be performed on SOVA to determine the minimum (L,U) parameter set that will give desirable performance. The conditions tabulated in Table 2.6 are used to run the simulation. The BER and BLER performance curves are shown in Figure 2.9. As observed from Figure 2.9, the depth of SOVA update window has a significant impact on the performance of both HR-SOVA and SB-SOVA. For similar performance, HR-SOVA will need a longer reliability update path U than SB-SOVA. With (L,U)=(24,40), SB-SOVA is able to achieve similar performance as Max-Log-MAP(12 iterations) and less than 0.2 dB degra-

#### 2.2. SIMULATION RESULTS

Figure 2.8: Simulation results for different reliability update methods

dation in performance as compared to Max-Log-MAP with 16 iterations. For the depths of (L,U)=(24,24), the performance of SB-SOVA is only 0.1 dB worse than Max-Log-MAP with the same number of iterations. For a shorter update depths of (L,U)=(24,20), the performance of SB-SOVA is still reasonably good, with less than 0.2 dB degradation from Max-Log-MAP. It is noted that the required  $\Delta_{TH}$  increases with the SNR for SB-SOVA. At higher SNR, a larger  $\Delta_{TH}$  is required to achieve satisfactory performance.

As for HR-SOVA, larger depths are required to improve its performance. For (L,U)=(40,40), HR-SOVA is still 0.2 dB worse off than SB-SOVA with smaller depths.

# CHAPTER 2. IMPROVED SOVA ALGORITHM

Table 2.6: Simulation conditions to obtain merge and update depths

| Environment:      | AWGN channel                                                                                                      |

|-------------------|-------------------------------------------------------------------------------------------------------------------|

| Block length:     | 4416                                                                                                              |

| Number of blocks: | 250                                                                                                               |

| Total data size:  | $\approx 10^6 \text{ bit}$                                                                                        |

| Simulation Parame | ters for HR-SOVA                                                                                                  |

| Update method:    | Hardware                                                                                                          |

| (L,U):            | (40,40) $(24,24)$                                                                                                 |

|                   | $(c,d) = (0.75, 0.80),  \Delta_{TH} = 16$                                                                         |

| Simulation Parame | ters for SB-SOVA                                                                                                  |

| Update method:    | Hardware                                                                                                          |

| (L,U):            | (24,40) $(24,24)$ $(24,20)$ $(20,20)$                                                                             |

|                   | (c,d) = (0.75, 1.00)                                                                                              |

|                   | $\Delta_{TH} = \begin{cases} 8 & \text{SNR} \le 0.75 \text{ dB} \\ 16 & \text{SNR} > 0.75 \text{ dB} \end{cases}$ |

The above simulation results serve as a reference for selecting the appropriate merge and update depths to be used in hardware architecture for an SB-SOVA turbo decoder.

# 2.2. SIMULATION RESULTS

Figure 2.9: BER and BLER performance of SOVA for varying merge and update depths  $\,$

# Chapter 3

# **SISO** Decoder Hardware Architectures

The simulation results presented in Section 2.2 determined the SOVA parameters that are needed for hardware implementation such as the merging and update depths. The simulation results also showed that the performance of the proposed SB-SOVA decoder was similar to that of a Max-Log-MAP decoder.

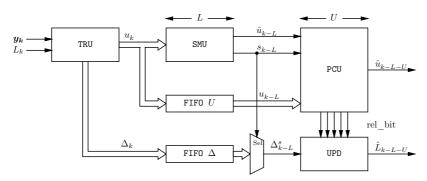

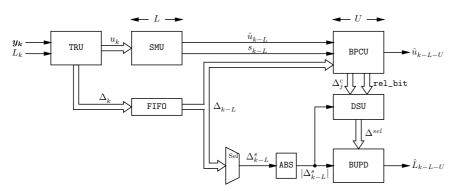

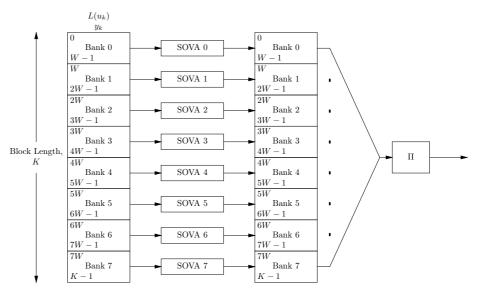

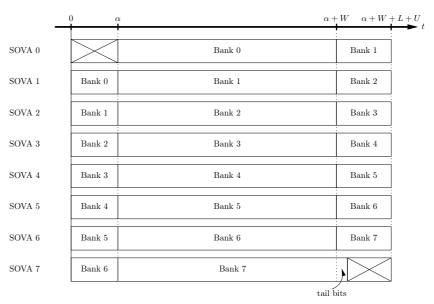

This chapter presents a discussion on the various hardware architectures that can be applied to implementations of SISO decoders. It begins with a literature review of the existing decoders based on Max-Log-MAP and HR-SOVA in Sections 3.1 and 3.2 respectively. Next, the proposed hardware architecture for SB-SOVA is presented in Section 3.3 together with optimizations that can be made to reduce the hardware complexity of the SB-SOVA decoder in Sections 3.4 and 3.5. In Section 3.6, considerations for a parallelized decoder is discussed.

Throughout the chapter, the key implementation considerations for the hardware design, namely the hardware complexity, memory utilization and latency, will be presented and discussed. Section 3.7 concludes the chapter by comparing the proposed SOVA based decoders with a baseline of the more traditional Max-Log-MAP based implementations so that the trade-offs between the hardware costs and performance can be evaluated.

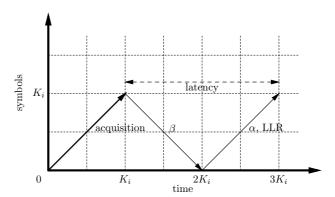

# 3.1 Hardware Architecture of Max-Log-MAP

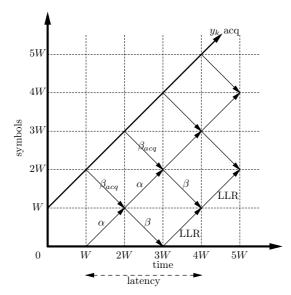

A typical hardware architecture for a Max-Log-MAP turbo decoder consists of recursion units to process both the forward recursion state metric  $\alpha_k(s)$  and the backward recursion state metric  $\beta_{k-1}(s')$ , as described in section 1.2.2. Due to the backward recursive nature of  $\beta_{k-1}(s')$ , computation of the first  $\beta_{k-1}(s')$  can only begin when the last bit of the block has been received. The timing behavior for a classical Max-Log-MAP architecture is as shown in Figure 3.1.

As shown in Figure 3.1, the latency for the first decoded output to be ready is  $3K_i$ , where  $K_i$  is the data block length. The latency marked in the diagram excludes the acquisition time for the channel data  $y_k$  and  $L(u_k)$  since it is assumed

Figure 3.1: Timing behavior of a classical MAP-based turbo decoder

that all data are available before the start of the turbo decoding. The latency also excludes the time taken before the first branch metric  $\gamma$  is available, since this value is expected to be much smaller than  $K_i$ . When the block length  $K_i$  is large, such as 6 144 bit in LTE, the resulting latency is significant. To reduce the latency, the input data block is usually divided into multiple windows, each of size W. Various architectures with different configurations of forward and backward recursion units have been proposed in [2] and [17]. The trade-off lies between required latency and chip area.

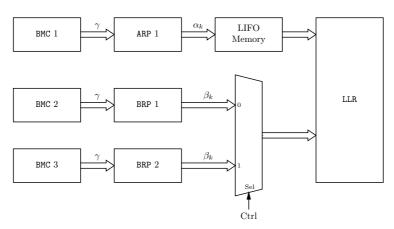

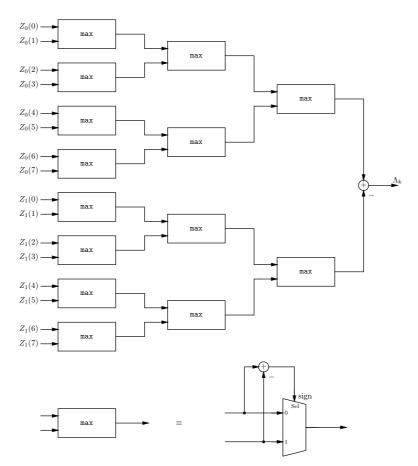

A hardware architecture of a Max-Log-MAP SISO decoder is presented in Figure 3.2. The architecture consists of three branch metric computation (BMC) units, one forward/alpha recursion processing (ARP) unit, two backward/beta recursion processing BRP units and a LLR unit. These hardware units are all executing concurrently. The BMC units are responsible for computing the branch metrics  $\gamma$ , as illustrated in (1.10). The ARP unit is responsible for processing the forward state metric  $\alpha$  according to (1.11) while the BRP units determine the backward state metric  $\beta$  according to (1.12). The purpose of having two BRP units is that while one unit is in acquisition mode, the other unit is performing the actual computation of the backward state metric as shown in Figure 3.3. The first BRP is used for acquisition to determine initial backward state metric  $\beta_k$  and the second BRP will process  $\beta_{k-1}$  down to  $\beta_{k-W}$ . Lastly, the LLR unit computes the final reliability value  $L_e(\hat{u}_k)$  using both  $\alpha$  and  $\beta$ . The block diagrams of the ARP and LLR units are as shown in Figure 3.4 and Figure 3.5 respectively.

The ARP determines forward state metrics  $\alpha_{k-1}$  to  $\alpha_{k-W}$  for each of the N states in a window of W. These  $N\times W$  forward state metrics will be stored in the memory and will be used later to compute the final state metric together with the backward state metrics  $\beta_{k-W}$  to  $\beta_{k-1}$ . As  $\alpha$  and  $\beta$  are calculated in opposite directions, the output of ARP has to be stored in a Last In First Out (LIFO) memory.

The hardware considerations for the Max-Log-MAP SISO decoder described

# 3.1. HARDWARE ARCHITECTURE OF MAX-LOG-MAP

Figure 3.2: System architecture of a Max-Log-MAP decoder

Figure 3.3: Write behavior diagram for Max-Log-MAP decoder

above are covered in the following sections.

# 3.1.1 Resource Utilization

An estimated hardware resource utilization for the Max-Log-MAP turbo decoder is computed as follows. The block diagram of a recursion unit is shown in Figure 3.4.

Figure 3.4: ARP unit for Max-Log-MAP

Each recursion unit is made up of 3N units of  $\eta_{\alpha}$ -bit adders and N units of  $\eta_{\alpha}$ -bit MUXes to compute the state metric. The block diagram of the LLR unit is as shown in Figure 3.5. As the objective of the LLR unit is to select the maximum reliability value, the unit is made up of multiplexers and adders to perform comparison and selection.

As observed from Figure 3.2, that there are N units of  $\eta_{\beta}$ -bit MUXes being used to select the  $\beta$  metric between BRP 1 and BRP 2 to be used by the LLR block.

The overall hardware resource utilization for Max-Log-MAP is summarized in Table 3.1.

## 3.1.2 Memory Requirements

The memory requirement for storing forward state metric  $\alpha$  for each window is computed as follows. For turbo decoder with M=8 and W=768, the storage requirement for  $\alpha$  will be

$$N \cdot W = 6\,144 \,\,\eta_{\alpha}$$

bit

where  $\eta_{\alpha}$  is the data width of  $\alpha$ . If  $\eta_{\alpha}=8$ , the storage requirement becomes  $49\,152=48$  kbit for each window. The total storage for the entire data block will be  $48\times8=384$  kbit. As the storage requirement is proportional to the total block length  $K_i$ , the total storage requirements for Max-Log-MAP is relatively high.

#### 3.1.3 Latency

As shown in the Figure 3.3, the decoder takes 3W cycles to decode a block of W symbols. The latency can be reduced to 2W if values  $\beta$  and LLR can be obtained concurrently. Since  $\alpha$  has already been computed between t=W and t=2W, the

#### 3.1. HARDWARE ARCHITECTURE OF MAX-LOG-MAP

Figure 3.5: LLR unit for Max-Log-MAP

LLR can be computed immediately once  $\beta$  is available between t=2W and t=3W, and written into memory. Since  $\beta$  is made available in the reverse order, the LLR will be computed in reverse order and thus can be stored in a LIFO memory. With this, the LLR values read out from the LIFO in the next iteration will be in the correct ascending order.

With parallel processing of a windowed channel input, the total latency is reduced from  $2K_i$  to 2W. 2W can still be a large number, if the block length of the channel input is large. For example, in LTE, the maximum block length  $K_i$  is 6144. If the channel data block is divided into 8 windows, the size of each window will be W = 768, which gives a latency of 1536 clock cycles.

| Resources in $\eta_{\alpha,\beta}$ bit  |          |        |  |  |  |

|-----------------------------------------|----------|--------|--|--|--|

| Adders MUXes (2-te                      |          |        |  |  |  |

| BMC (3 units)                           | 15       | -      |  |  |  |

| Recursion Units (ARP, BRP 1, BRP 2)     | 9N       | 3N     |  |  |  |

| $\beta$ selection between BRP 1 & BRP 2 | -        | N      |  |  |  |

| LLR unit                                | 6N - 1   | 2(N-1) |  |  |  |

| Total Resource Usage                    | 15N + 14 | 6N-2   |  |  |  |

Table 3.1: Resource utilization for Max-Log-MAP

Figure 3.6: Hardware stages in SOVA

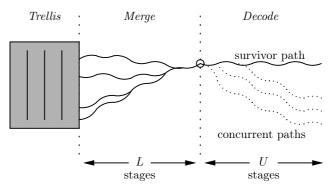

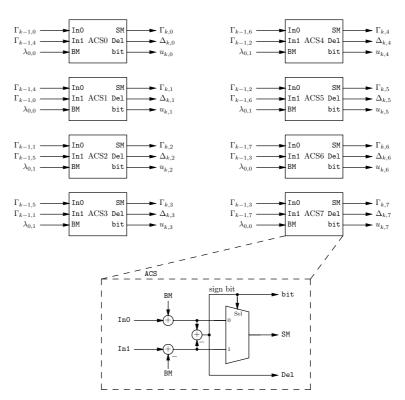

# 3.2 Hardware Architecture for HR-SOVA

Various hardware architectures for SOVA have been proposed [3][4][5], and these architectures are typically made up of 3 stages, namely the trellis, merge and decode stages, as illustrated in Figure 3.6.

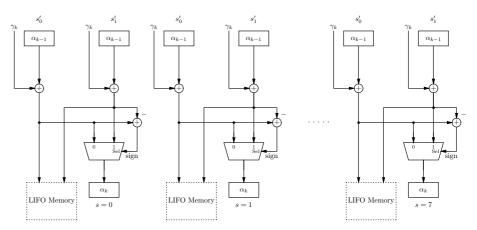

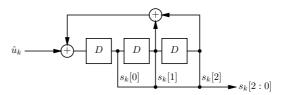

## 3.2.1 Trellis Stage

The first stage is the *trellis* stage that computes the state metrics of each of the  $2^{\nu}$  states, according to (1.22), that can be separated into the recursion and the branch metric terms as as shown in (3.1).

$$M_k(S_k) = M_{k-1}(S_{k-1}) + \underbrace{\frac{1}{2}L(u_k) \cdot u_k + \frac{1}{2}L_c \cdot y_{k,1} \cdot u_k + \frac{1}{2}\sum_{v=2}^n L_c \cdot y_{k,v} \cdot x_{k,v}}_{\text{branch metric}}$$

(3.1)

#### 3.2. HARDWARE ARCHITECTURE FOR HR-SOVA

Figure 3.7: BMC module in the trellis unit

Assuming that the expected parity bit  $x_{k,2}=+1$ , or equivalently that the parity bit has a value of '0', and let the branch metrics for the cases when the expected systematic bits of  $u_k=0$  and  $u_k=1$  be denoted by  $\lambda_{0,0}$  and  $\lambda_{1,0}$  respectively. These branch metrics are then calculated as follows

$$\lambda_{0,0} = \frac{1}{2}L_k(+1) + \frac{1}{2}L_c \cdot y_{k,1}(+1) + \frac{1}{2}L_c \cdot y_{k,2}(+1)$$

$$= \left(\frac{1}{2}L_k + \frac{1}{2}L_c \cdot y_{k,1}\right) + \frac{1}{2}L_c \cdot y_{k,2}$$

$$\lambda_{1,0} = \frac{1}{2}L_k(-1) + \frac{1}{2}L_c \cdot y_{k,1}(-1) + \frac{1}{2}L_c \cdot y_{k,2}(+1)$$

$$= -\left(\frac{1}{2}L_k + \frac{1}{2}L_c \cdot y_{k,1}\right) + \frac{1}{2}L_c \cdot y_{k,2}$$

(3.2)

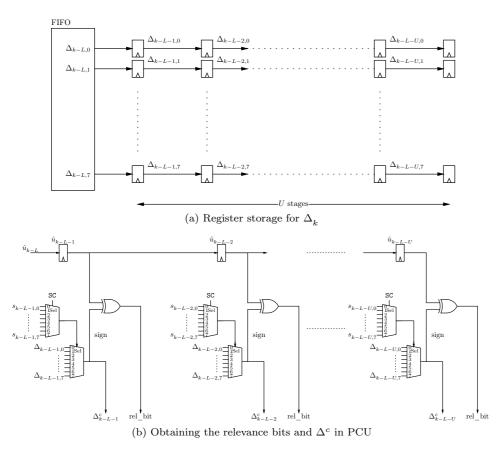

where  $y_{k,1}$  and  $y_{k,2}$  are the received channel systematic and parity values respectively, and  $L_k$  is input extrinsic information. Likewise, by assuming once again that the expected parity bit  $x_{k,2}=-1$ , the branch metrics for the expected systematic bits of  $u_k=0$  and  $u_k=1$  denoted by  $\lambda_{0,1}$  and  $\lambda_{1,1}$  respectively can be calculated.

$$\lambda_{0,1} = \frac{1}{2}L_k(+1) + \frac{1}{2}L_c \cdot y_{k,1}(+1) + \frac{1}{2}L_c \cdot y_{k,2}(-1)$$

$$= \left(\frac{1}{2}L_k + \frac{1}{2}L_c \cdot y_{k,1}\right) - \frac{1}{2}L_c \cdot y_{k,2} = -\lambda_{1,0}$$

$$\lambda_{1,1} = \frac{1}{2}L_k(-1) + \frac{1}{2}L_c \cdot y_{k,1}(-1) + \frac{1}{2}L_c \cdot y_{k,2}(-1)$$

$$= -\left(\frac{1}{2}L_k + \frac{1}{2}L_c \cdot y_{k,1}\right) - \frac{1}{2}L_c \cdot y_{k,2} = -\lambda_{0,0}$$

(3.5)

It can be observed that  $\lambda_{0,1}$  and  $\lambda_{1,1}$  are simply the negative values of  $\lambda_{1,0}$  and  $\lambda_{0,0}$  respectively. This implies that there is only a need to generate two of the four branch metrics, since the other two can be easily obtained in the ACS when needed. A branch metric calculation unit BMC as shown in Figure 3.7 is used to generate  $\lambda_{0,0}$  and  $\lambda_{0,1}$ .

Other than the BMC unit, there are  $2^{\nu}$  ACS in the trellis unit that will perform recursion by adding the branch metric to the previous survivor path metric, compare

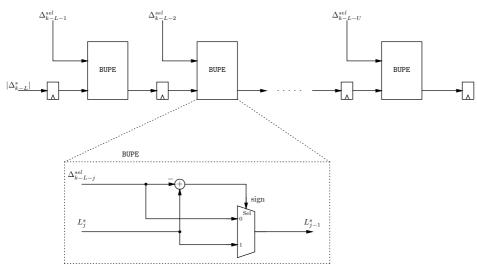

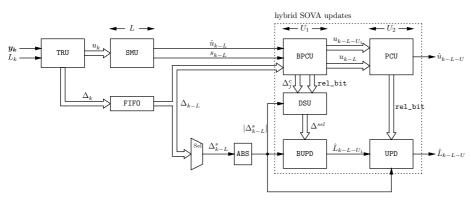

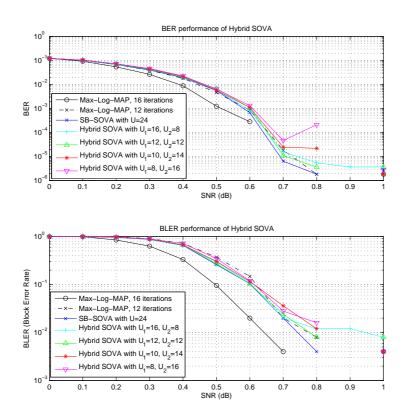

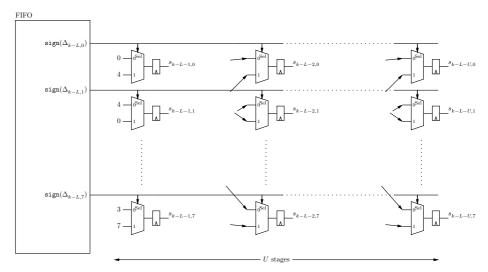

Figure 3.8: Trellis unit for LTE consisting of 8 ACS units