# Hardware-software model co-simulation for GPU IP development

JAIME GANCEDO RODRIGO

MASTER'S THESIS

DEPARTMENT OF ELECTRICAL AND INFORMATION TECHNOLOGY

FACULTY OF ENGINEERING | LTH | LUND UNIVERSITY

# Hardware-software model co-simulation for GPU IP development

Jaime Gancedo Rodrigo jaimegancedo@gmail.com

$\begin{array}{c} \textbf{Department of Electrical and Information Technology} \\ \textbf{Lund University} \end{array}$

Supervisor: Liang Liu

Asst.Supervisor: Reimar Döffinger (Arm)

Examiner: Erik Larsson

April 19, 2018

$"Head\ first,\ hands\ afterwards."$

From the Spanish: "Primero la cabeza, después las manos."

Life lesson, Someone very wise

### **Abstract**

This Master's thesis project aims to explore the possibility of a mixed simulation environment in which parts of a software model for emulating a hardware design may be swapped with their corresponding RTL description. More specifically, this work focuses on the sofware model for Arm's next-generation Mali GPU, which is used to understand system on chip properties, including functionality and performance. A component of this model (written in C++) is substituted with its hardware model (written in SystemVerilog) to be able to run simulations in a system context at a faster emulation speed, and with higher accuracy in the results compared to a pure-software model execution. For this, a "co-simulation" environment is developed, using SystemVerilog's DPI-C as the main communication interface between C++ and SystemVerilog. The proposed environment contains new software and hardware blocks to enable the desired objective without major modifications in neither the software Mali model nor the substituted component. Metrics and results for characterizing this co-simulation environment are also provided, namely timing accuracy, data correctness and simulation time with respect to other previously available simulation options. These results hope to show that the proposed environment may open new use-cases and improve development and verification time of hardware components in a system such as the Mali GPU.

# Acknowledgments

I would like to begin by thanking my supervisor, Professor Liang Liu and my examiner, Professor Erik Larsson for their help during this project, specially on the initial arrangements. Likewise, I am grateful to my supervisor at Arm, Reimar Döffinger, for guiding me in such a challenging task and Noelia Rodríguez, for making me a part of the GPU modelling team during my time at Arm Lund.

To my family, specially my parents, who have supported me ever since I can remember, been by my side at the best and not so good times and helped me reach my goals and dreams. I can hardly express how grateful I am.

To my professors and friends of *Universidad Politécnica de Cartagena*, for helping me become an engineer, make me realize what I wanted my profession to be and grant me some of the best opportunities of my life. This Master's Thesis probably wouldn't have happened without you.

To my friends in Lund: Berta, Javier G., Javier M., Sergio, Manuel, Iratxe, Diego and everyone else for making me feel like at home, remember my Spanish, get to love vegetables, enjoy the small things, for all the technical discussions after office hours and, in general, for making these two years in Sweden a memorable experience.

To my life-long friends from Cartagena: Ignacio, Marina, Daniel, Helena, Ester, Carlos, David, Deborah and everyone else for having me forget about everything else and feel as if time had stopped when I am back home. I am also grateful to Peter Casanave, for being my English teacher for so many years and my friend. You would not believe it if I told you I have just looked at the dictionary two or three times to write this document!

To every person that is not mentioned here, but has played a smaller or bigger part in my life, and the aforementioned: Everything we live and experience, both good and bad, makes us who we are. Thank you for being a part of this journey.

## Popular Science Summary

# Hardware-software model co-simulation for GPU IP development: Software and hardware under the same simulation

The possibility of combining hardware designs and software in the same simulation environment opens new options and improves significantly the flexibility of verification processes as well as characterization time of electronic designs. A practical method to realize this is developed and presented in this work for the case of a real Graphics Processing Unit IP.

Nowadays electronics designers and manufacturers compete in an increasingly faster race to be able to provide the best and most efficient solutions to the market's expectations. The easiest example is the tendency of smartphone designers to provide a brand-new mobile phone model every year to meet consumers' demand. To meet these tighter and tighter deadlines, these companies need to find new ways of designing and verifying their products faster and more efficiently. In this context enters the work presented in this thesis: One of many possible solutions to improve the verification time of a hardware unit/block.

Digital electronic circuits are commonly designed and modelled using Hardware Design Languages (HDLs), which are similar to computer languages such as C or Java, but different in the sense that HDLs actually describe the physical layout and connections of a digital circuit. These HDL designs can be simulated to verify their correct performance and characteristics with very high detail but, at the same time, this type of simulations are costly in terms of computational time and resources, due to the nature of the magnitudes and mechanisms being replicated on the computer running the simulation.

On the other hand, software is written in computer languages directly, compiled to machine language and run sequentially by computers, in a much faster and efficient manner. Therefore, what if the best of the two could be combined to simulate a digital design in which only a specific internal block is described in a HDL while the rest of the design is a software program? This would allow to reduce the simulation time of that block greatly, while at the same type preserve the accuracy that a simulation of a HDL design can provide.

This thesis work is based on a specific part of Arm's next-generation Mali Graphics Processing Unit (GPU), for which a solution for mixing hardware and software in the same simulation is proposed. For this specific case, such mechanism will allow to improve the development and testing time of new features for a Mali

hardware IP, while at the same time open new use-cases for future work in this direction.

# Table of Contents

| 1   | Background                                                |                                              |                                                      |     |  |

|-----|-----------------------------------------------------------|----------------------------------------------|------------------------------------------------------|-----|--|

|     | 1.1                                                       | The G                                        | Graphics Processing Unit                             | 1   |  |

|     |                                                           | 1.1.1                                        | Functional differences between a GPU and a CPU       |     |  |

|     |                                                           | 1.1.2                                        | An example of GPU architecture: The Mali-G72         |     |  |

|     | 1.2                                                       | vare-software model co-simulation            | 3                                                    |     |  |

|     |                                                           | 1.2.1                                        | Hardware simulation                                  | :   |  |

|     |                                                           | 1.2.2                                        | Software models for faster hardware simulation       |     |  |

|     |                                                           | 1.2.3                                        | Co-simulation                                        |     |  |

|     | 1.3                                                       | Previous works on co-simulation environments |                                                      | į   |  |

| 2   | Cha                                                       | llenges                                      | and objectives                                       | _ 9 |  |

| · · |                                                           | Main                                         | actors in this work                                  | Ç   |  |

|     |                                                           | 2.1.1                                        | The Mali model                                       | Ģ   |  |

|     |                                                           | 2.1.2                                        | The Texture Unit (TU)                                | 10  |  |

|     |                                                           | 2.1.3                                        | Objectives of the proposed co-simulation environment | 10  |  |

|     | 2.2                                                       | nulation options and solution                | 12                                                   |     |  |

|     |                                                           | 2.2.1                                        | Description and comparison of possible options       | 12  |  |

|     |                                                           | 2.2.2                                        | Choice of co-simulation tool: SystemVerilog's DPI-C  | 10  |  |

| 3   | Implementation and results                                |                                              |                                                      |     |  |

|     | 3.1                                                       | The c                                        | o-simulation environment                             | 19  |  |

|     |                                                           | 3.1.1                                        | SystemVerilog testbench and logic                    | 20  |  |

|     |                                                           | 3.1.2                                        | Model top-level wrapper                              | 22  |  |

|     |                                                           | 3.1.3                                        | SystemVerilog co-simulation wrapper                  | 23  |  |

|     |                                                           | 3.1.4                                        | The model's co-simulation class                      | 2   |  |

|     | 3.2 Results and analysis of the co-simulation environment |                                              | s and analysis of the co-simulation environment      | 36  |  |

|     |                                                           | 3.2.1                                        | The reference graphics job                           | 3   |  |

|     |                                                           | 3.2.2                                        | Timing accuracy                                      | 3   |  |

|     |                                                           | 3.2.3                                        | Data correctness                                     | 3   |  |

|     |                                                           | 3.2.4                                        | Simulation time                                      | 39  |  |

| 4   | Con                                                       | clusion                                      | s and future work                                    | 43  |  |

|     | 4.1                                                       | Concl                                        | usions                                               | 43  |  |

|     | 4.2                                                       | Future                                       | e work                                               | 44  |  |

References\_\_\_\_\_\_ 47

# List of Figures

| 1.1  | Mali-G72 high-level architecture - Arm [4]                            | 2  |

|------|-----------------------------------------------------------------------|----|

| 2.1  | High-level diagram of the co-simulation environment                   | 11 |

| 3.1  | General diagram of the final co-simulation environment                | 20 |

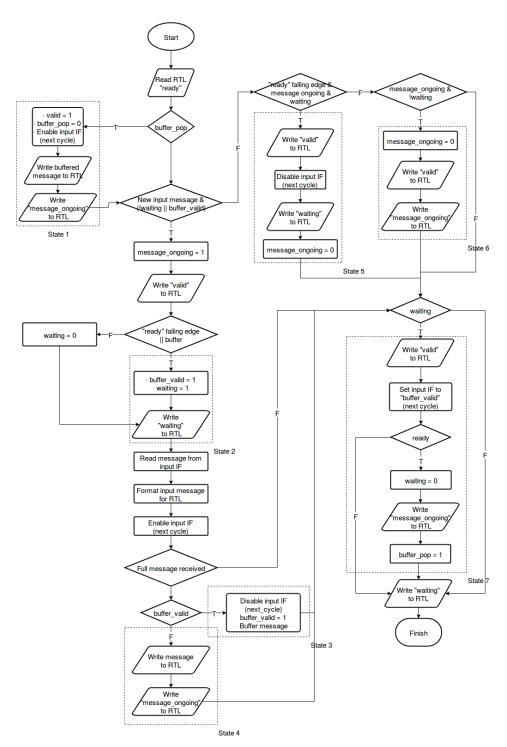

| 3.2  | Flow chart of the testbench logic                                     | 21 |

| 3.3  | Block diagram of C-written model top-level wrapper                    | 22 |

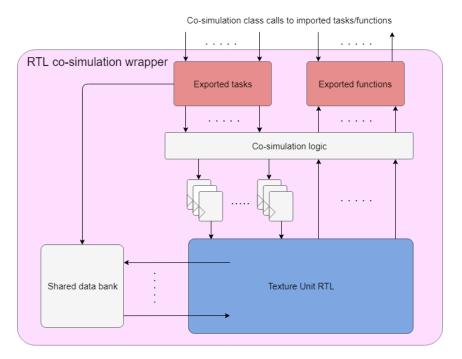

| 3.4  | Block diagram of RTL co-simulation wrapper                            | 24 |

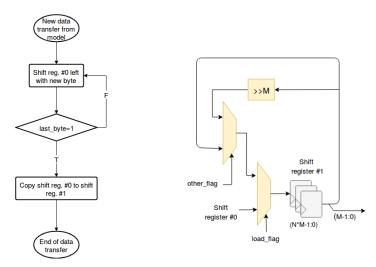

| 3.5  | Co-simulation wrapper logic for wide-words data or data received in   |    |

|      | several cycles                                                        | 25 |

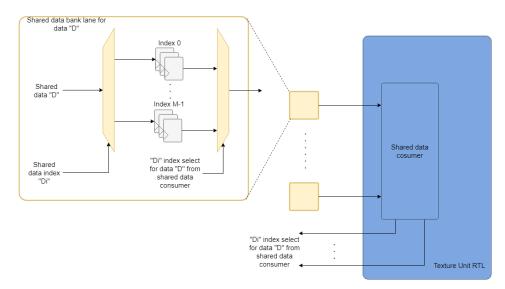

| 3.6  | Block diagram of the co-simulation wrapper's shared data bank         | 27 |

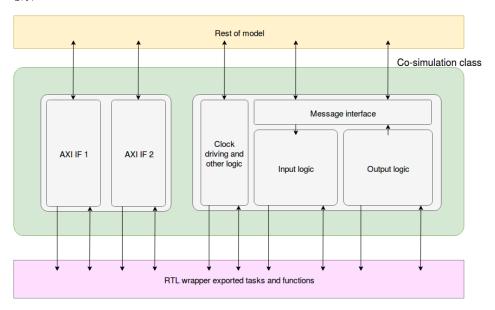

| 3.7  | Block diagram of the co-simulation class                              | 28 |

| 3.8  | Flow charts of co-simulation class' main methods                      | 29 |

| 3.9  | Flow chart of input message logic of co-simulation class              | 30 |

| 3.10 | Flow chart of output message logic of co-simulation class             | 32 |

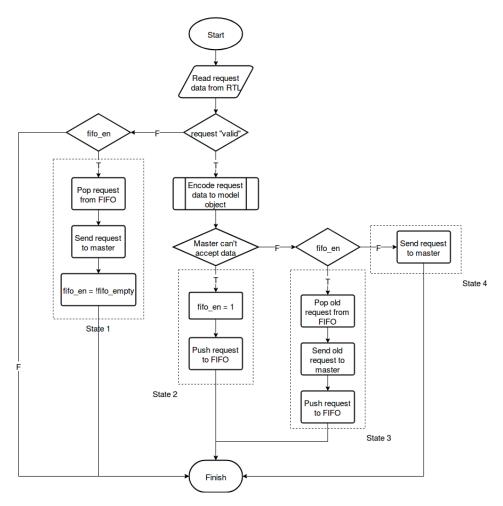

| 3.11 | Flow chart of <i>compute</i> method of AXI interface class            | 34 |

| 3.12 | Flow chart of read request logic of AXI interface class               | 35 |

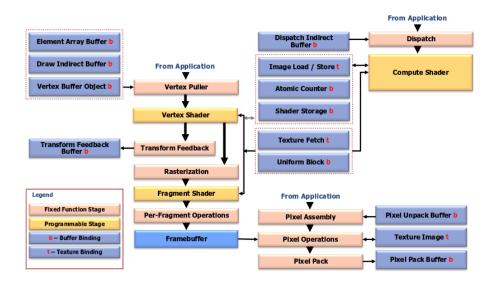

| 3.13 | Block diagram of GLES 3.1 pipeline [19]                               | 37 |

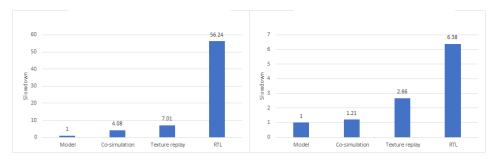

| 3.14 | Relative slowdown of the different simulation options with respect to |    |

|      | the software model                                                    | 40 |

# List of Tables

| 2.1<br>2.2 | Advantages and disadvantages of Tcl as a co-simulation tool Advantages and disadvantages of SystemVerilog's DPI as a co-simulation tool |    |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.3<br>2.4 |                                                                                                                                         | 16 |

| 3.1        | Cycle count relative difference of software model and co-simulation with RTL-only simulation                                            | 38 |

## **Abbreviations**

- ABI Application Binary Interface

- API Application Programming Interface

- ASIC Application-Specific Integrated Circuit

- AXI Advanced eXtensible Interface

- CAD Computer-Aided Design

- **CPU** Central Processing Unit

- **DPI** Direct Programming Interface

- **DUT** Device Under Test

- EDA Electronic Design Automation

- FIFO First In First Out

- $\mathbf{FMI}$ Functional Mock-up Interface

- GLES OpenGL for Embedded Systems

- GPU Graphics Processing Unit

- ${f GUI}$  Graphical User Interface

- $\mathbf{HDL}$  Hardware Description Language

- **HLS** High-Level Synthesis

- IP Intellectual Property

- LOC Lines Of Code

- RTL Register-Transfer Level

- Tcl Tool command language

- TU Texture Unit

- VHDL VHSIC Hardware Description Language

- ${f VLSI}$  Very-Large-Scale Integration

In this introductory chapter several terms and concepts, which are the basic foundation from which this thesis work is built, are presented and explained. The first section will focus on the Graphics Processing Unit (GPU), discussing its differences with a Central Processing Unit (CPU) and presenting an example very related to this work: the Mali-G72 by Arm. Following this, the concept of cosimulation is introduced, for which the definition of a hardware model simulation and software models for hardware designs need to be provided and described first. Finally, a collection of previous works that are relevant for this thesis are shown and discussed, from which abundant information for both implementation options and metrics for the results can be extracted.

### 1.1 The Graphics Processing Unit

A GPU is a specific processor optimized for those calculations primarily needed in graphical operations. These calculations are usually parallelized and performed in floating-point representation, requisites important for rendering 3D graphics. This specific hardware architecture allows for a processing power several orders of magnitude higher than a conventional CPU in the previously mentioned tasks [1].

The GPU used to be a hardware component exclusive to static machines and computers, as its use usually implied an increased complexity in the system as well as a higher power consumption (in opposition with superior performance for graphical tasks). However, technological advancement has allowed the miniaturization and power optimization of the GPU, turning it into a suitable solution for superior graphical performance in mobile devices like smart-phones.

#### 1.1.1 Functional differences between a GPU and a CPU

A CPU is a general-purpose circuit capable of executing common computer instructions, such as arithmetic and logic operations or writes/reads to the system's memory. CPUs exploit the concept of pipelining, as well as other mechanisms, to provide a very high instruction throughput with a reasonable power consumption. It is the basic building block of a modern computer system due to the fact that, in principle, it is optimized to perform any operation and has access to every subsystem of the main architecture.

The vast majority of programs are typically written in a manner such that its operations are executed sequentially [2]. Due to this, a single CPU is optimized to run this type of tasks as fast as possible. This is a very important obstacle for improving the computational efficiency of programs or algorithms that are inherently parallelizable, such as 3D graphics rendering, machine learning or cryptography. GPUs are a solution to this inconvenient, as their architecture is designed to handle efficiently parallel tasks.

A typical CPU architecture contains few cores, accompanied with cache memory to make the handling of several software threads simultaneously feasible. On the other hand, a GPU is designed with hundreds of cores capable of processing thousands of threads at the same time. This means an occasional advantage for the GPU with respect to CPU, which will be able to accelerate certain software over a factor of 100 compared to a CPU. Furthermore, a GPU will achieve this speedup being more power and cost efficient than a CPU [3].

#### 1.1.2 An example of GPU architecture: The Mali-G72

With the aim of introducing the reader to a system similar to the one in which this work has been based on, as well as to show an example of a GPU architecture, the Mali-G72 is presented in this section. This Arm's mobile GPU is one of the most popular commercial solutions for a wide range of devices. Only in 2016, more than one billion Mali GPUs were shipped. Depending on the main requisite for each system, different Mali models are available, each with specific emphasis on high performance, high area efficiency or ultra-low power consumption. The Mali-G72 is the most powerful model in the "High performance" family [4].

Figure 1.1: Mali-G72 high-level architecture - Arm [4]

In general terms, this GPU is composed of up to 32 cores, each of which contains several execution engine blocks, a message fabric and some specific units, like the Texture Unit (TU). Along this array of cores, other caches, interfaces and blocks complete the architecture of this system. As it has previously been presented, this system exploits the inherent parallelization of tasks such as graphics rendering and machine learning by employing several computing cores for running many threads simultaneously.

The work of this thesis is focused on the top-level interface of the TU for the next-generation Mali GPU.

#### 1.2 Hardware-software model co-simulation

In this section, two of the most widely used principles for simulating hardware designs, hardware models simulation and software models, will be described in order to later introduce the concept of *co-simulation*, the general idea behind this thesis work.

#### 1.2.1 Hardware simulation

Digital hardware designs are typically written in a Hardware Description Language (HDL), such as VHSIC Hardware Description Language (VHDL) or Verilog. These computer languages are created to allow a designer to describe the behavior of a digital electronic circuit from a higher-level perspective, while still being precise. Designs written in a HDL may undergo processes like synthesis (for netlist generation) or compilation for simulation in specific tools designed for these languages.

Looking more closely into the latter, behavioral simulation for HDL compiled code is typically realized using an event-driven approach. In an event-driven simulation, time is represented as an integral multiple of the resolution, which is the minimum time unit in the simulation. Any simulation contains two phases: Statement execution and Event processing which are executed in every time step. In the former phase, for each event (a statement containing a signal in a VHDL sensitivity list, for example), a new value and the time when a target signal will be changed are created and stored in a queue, forming a value/time pair called transaction. In the Event processing phase, transactions happening in the current time are removed from the queue. For each removed transaction, if it represents a value change of a signal, it will be treated as an event, triggering the signal update [5].

Event-driven simulation is the most popular mechanism for simulating hardware designs due to the accuracy it offers and moderate efficiency in computational expense. However, this approach is still costly, making the simulation of very big or complex systems slow.

#### 1.2.2 Software models for faster hardware simulation

Software models are programs written in any computer language which mimic the intended behavior (and optionally other features) of a digital system with different degrees of accuracy. These are very valuable for exploring design options,

simplify verification of certain parts of a system or be used as a golden reference for hardware verification. Software models of a hardware design can be classified according to the level of abstraction they provide [6]. From lowest to highest:

- Continuous time. Operations are described as continuous actions, p.e. the behavior of an analog electronic circuit using differential equations.

- **Discrete-event**. Activities are grouped into time points called *events*. Changes in the inputs of a digital circuit will trigger toggles in intermediate nets resulting in a change of the outputs in times that may be irregularly spaced. This level of abstraction provides relevant simulation information such as propagation delays in combinational logic, glitches and clock edges. This is a model-wise analogy to event-driven simulations for digital circuits, described in the previous section.

- Cycle-accurate. A cycle-accurate model uses clock edges as the basic timing unit. These level of abstraction can't provide propagation delays or glitches, as all activities between clock edges will be grouped at the positive or negative edge. Therefore, activities happen "immediately", or after an integer number of clock cycles. This is usually the abstraction level chosen for use as a golden reference in verification of hardware designs for its balance between accuracy and complexity.

- Instruction-accurate. In this level of abstraction, activities are expressed in steps of "one microprocessor instruction". Effectively, every step of such simulation contains several cycles of processing. This is used to simulate complex software, such as operating systems. Since the time count in these simulations is in terms of instructions, the only possible mapping to real time units would be to assign a processing time (p.e. in clock cycles) for each instruction.

- Transaction-accurate. If the system is too complex for an instruction-accurate approach, transaction-accurate models are used. In this type, the behavior of the system is expressed as interactions between components. These interactions are called *transactions*. The time for every transaction depends on what is actually being modeled, but may range from thousands to millions of clock cycles. These models are most common in early phases of a design, to explore different options and evaluate how they affect the system as a whole.

The main reasons encouraging the use of software models over HDL descriptions for a given hardware design are:

- Faster implementation time, as software languages are, in general, less verbose and demanding for the designer.

- Higher flexibility, since options for configuring the behavior of the modeled system can be toggled very easily.

- Improved computational cost of simulations, as the resulting "simulation" is simply an object code that can be directly executed by a computer, in opposition to HDL compiled code for running simulations in a dedicated event-driven simulation software.

In opposition to these advantages, hardware models generally cannot replace HDL described systems when:

- A high accuracy for the behavior of the system is required.

- The design is to be translated into a netlist (except for some High-Level Synthesis (HLS) languages, such as Catapult-C). They may only be used for simulation/verification purposes and not for physical implementation.

#### 1.2.3 Co-simulation

For several reasons, which will be introduced shortly, it is very convenient and interesting to simulate simultaneously software and hardware models under a common framework. Such simulation, in which one or several pieces of software and hardware are communicated in some manner to provide a single result output, is called "Hardware-software model co-simulation".

This mechanism allows mixing these different entities under a common testbench, while still moderately preserving the loose coupling between them. In other words, if the co-simulation framework is well designed, most blocks can, for example, be replaced for an updated simulation with a new version of a hardware component while maintaining the former software. Co-simulation can therefore be very interesting for design exploration, where it provides a fast solution for testing new features and evaluating how they affect the system as a whole.

Another scenario where the use of co-simulation can be advantageous is in full-system integration, since nowadays virtually every electronic system is a combination of software and hardware. A possible flow would be to verify software and hardware separately, using the corresponding methods and tools for each, and then use co-simulation to verify that the two entities can work together as expected.

Finally, co-simulation also allows a more efficient parallel development of the hardware and software components of a system, which is directly beneficial for shortening development times nowadays that time-to-market is becoming shorter and shorter [7].

Since hardware designs are typically verified in tools based off event-driven simulation, the most common approach to enable co-simulation is integrating (via different solutions) the capability of running external object code in some HDL simulation tool. Some examples of these solutions will be presented and discussed in the following section.

#### 1.3 Previous works on co-simulation environments

Simulations combining hardware and software models can be implemented in different ways, of varying complexity and results, depending on the engineering needs and available flows. One example is the use of scripting languages in Electronic Design Automation (EDA) tools to interface with Register-Transfer Level (RTL)-level signals in the own tools' default simulation environment. One example could be using the language Tcl inside Xilninx's Vivado simulator to generate and drive stimuli to a hardware block for unit-level testing.

Another typical example in the industry is SystemVerilog DPI (Direct Programming Interface), an interface that allows to communicate SystemVerilog code with foreign languages (typically C, C++ or SystemC, among others).

Apart from these examples, several academic works further prove the value of co-simulation. For instance, Stefano Centomo et al. present the results of a tool-independent environment for co-simulation using SystemC to describe the hardware part of the design and Functional Mock-up Interface (FMI) as the bridge between the RTL description of the design and the rest of the system modeled in software using the tool Modelica. In this case, the main metric used to determine the usefulness of this approach is the average CPU time that the environment takes to simulate a second of simulation time which, in this case, yields very promising results. However, the authors point out some shortcomings in FMI, such as the fact that event-driven simulation is not possible [8].

On a similar note, but more closely related to this Master's thesis, the work of Dominik Widhalm et al. presents the use of Perl for creating test stimuli and environment templates for the simulated verification of SystemC described hardware designs [9]. Four different methods are compared: code generation, which becomes complicated because for some basic constructs a C code has to be developed; code conversion, that is, to convert Perl code directly into C code, which presents the problem of outputting unreadable C code; code transformation, similar to the previous but using the intermediate constructs of the Perl interpreter and the embedding approach, that takes on running the actual Perl script in a real Perl environment running inside the SystemC simulation domain. To compare these different methods, a single test case is used: a linear voltage ramp used as input to an ADC, letting the simulation build the respective histogram for every voltage step, and then merging all the histograms to calculate the static parameters of the ADC. The results are varied, but an important contribution from this work are the metrics used for comparison of the different methods:

- Lines Of Code (LOC) required to implement the test case.

- Size of the resulting executables.

- Runtime: Total simulation time of the test case.

This study is concluded stating that the preferred option should be the embedded approach, as it is re-usable in every possible test-case, only having to change the Perl script to be used in that case. The only disadvantage is the fact that runtimes are longer than in other methods due to including the whole Perl environment embedded on System C. However, this inconvenient might be overshadowed by the overall saved time thanks to re-usability.

An additional interesting work, from industry in this case, is that of Michael D. McKinney, Senior Member of the Technical Staff in Texas Instruments [10], who describes the integration of Perl, Tool command language (Tcl) and C++ into a simulation-based verification environment for Application-Specific Integrated Circuit (ASIC) designs. In such proposed environment, simulations that combine HDL designs with software models (one written in Perl, in this case) are executed in the following manner: The HDL simulator is invoked, which then loads a core Tcl subroutine, responsible for several front-end tasks related to the simulator,

Graphical User Interface (GUI) and VHDL verification environment. Later in each test-specific file, another Tcl routine is invoked again to execute a Perl interpreter, which will run the Perl-written reference model to generate the stimuli and expected output of the RTL unit under test. Tcl is then responsible again for driving these stimuli to the RTL design being simulated, control the simulation time execution (interestingly for the sake of this thesis work) and read the output generated, in order to compare it with that of the golden reference.

This approach, which yields very interesting results, does however present several inconveniences that are very relevant to discuss. First, since Perl and Tcl are different languages, they cannot share the interpreter, or the internal variables that each use. This was solved in [10] using files to write and read data between processes. However, this creates a considerable overhead due to the creation, writing, reading and parsing of the files. In addition, both processes need to agree on the internal format of the files, which can be a feature difficult to implement. Secondly, this approach grants complete control of the simulator to Tcl, which is a good solution for automating the flow and tests. However, this also means that the HDL debugging features that are present in the simulator are not available, creating an additional layer of complexity for the debugging of the RTL design. Finally, other issues arise as a result of choosing Tcl as the controller of the flow, along with the way this integration is realized. One is the fact that syntax errors in the Tcl scripts cannot be detected until runtime, due to the interpreted nature of the language. Another is that Tcl will sometimes be busy many real-time seconds operating with files (which are sometimes very long and heavy). This causes the simulator to appear "hung" for some time. Finally, once Tcl has completed the needed operations for a specific phase, it runs time steps for the simulation with the appropriate command. Since the simulator updates its GUI and other elements every time a "run" command is executed, if the time-step for each call to this command is too small, the GUI will keep refreshing every time, causing again an additional overhead to execution time as well.

## Challenges and objectives

In this chapter the specifics on the challenges and objectives of this thesis work will be presented. For this matter, the main actors have to be described, namely the Mali GPU software model and Mali's TU block. Once the scenario is presented, different options to implement co-simulation will be discussed and compared. Finally, the chosen option that complies best with all constraints and was found the most suitable is shown, with a motivation for this decision.

#### 2.1 Main actors in this work

Before presenting the objectives and challenges of this work, it is necessary to briefly describe the two main actors on which this study is built upon: The software model for Arm's Mali GPU and the RTL implementation of the TU, a hardware unit which is part of the hardware micro-architecture of this GPU.

#### 2.1.1 The Mali model

The Mali model is a C++ software developed by Arm which mimics the behavior of the Mali's GPU hardware, taking advantage of the flexibility that software can provide in opposition to HDL. For future reference, it is relevant to highlight that its abstraction level can be considered as in between the *cycle-accurate* and *discrete-event* levels, following the classification presented in section 1.2.2. It is also commonly referred to as *cycle-approximate*.

The model exposes a top-level interface for other applications. This interface, in the form of a C library, provides functions for creating an instance of the model, configure it or perform tasks that the top-level of the GPU would receive in a real implementation, such as processing certain graphics jobs. Once the model completes a top-level task, it will output a file containing the memory addresses and data that the Mali GPU would have written for that task in a real system. This can also be referred to as memory dump. The objective of the proposed cosimulation solution is to be able to run these tasks on the model to simulate the processing of graphics jobs just in the same way as it is "traditionally" done in the model, with the particularity of using the TU's RTL in place of the model's counterpart.

The model is one of the main actors in this work, and its operation and special characteristics determine to some extent how the final solution was designed and the main principles behind its performance and behavior. For instance, the model will read values from the previous cycle at the rising edge of the next, will process that data, and finally provide an output in the falling edge of that same cycle.

#### 2.1.2 The Texture Unit (TU)

The Texture unit is a hardware block contained in the Mali micro-architecture responsible for processing several graphics operations with, surprisingly, textures. Jobs received by this unit are processed in a pipelined manner with the order for each job not necessarily being preserved in the output. That is, a job #0 which arrives before another job #1 may be finished by the pipeline after job #1 is.

The RTL implementation of this unit is also one of the major actors in this work, as its inclusion in a co-simulation with the software model for the rest of the GPU has been the main motivation for this thesis work. More specifically, its interface is where a great part of the co-simulation work has been carried out, so it is relevant to mention in a summarized manner the different sub-interfaces it exposes:

- A **control** interface, with signals to monitor the state of the unit and receive basic configuration.

- A **message input** interface, that receives texturing messages from other parts of the GPU.

- A message output interface, that sends texturing result messages to other parts of the GPU.

- A shared data interface, that reads shared data from other entities in the GPU micro-architecture that may be required in texturing operations, such as state, current operation status, etc.

- Two Advanced eXtensible Interface (AXI) interfaces for requesting data from other memories in the GPU to internal caches.

Finally, it is important to note that this hardware Intellectual Property (IP) is described in HDL with SystemVerilog. This fact will condition the options available for co-simulation, since the execution of object code is also conditioned by the event-driven simulation tool which, at the same time, is constrained by the possibilities existent in the specification of the HDL in which the hardware design being simulated is described.

#### 2.1.3 Objectives of the proposed co-simulation environment

As was mentioned before, software models of a hardware design are a key resource for tasks like design exploration, behavioral emulation of the real system or performance evaluation. For the case of Arm's Mali, the C++ model allows to realize these tasks, as well as testing early features and others advantages. A different approach to software models for realizing these tasks would be simply designing a

hardware block and simulating its behavior and performance once implemented. However, the development time penalty for every iteration in this latter case is much higher, and so is the computational cost of the simulation, which can become a real problem for top-level tests.

The main motivation for this thesis work is to explore whether the best of the two worlds can be combined: the accuracy of a typical RTL simulation (event-driven) with the speed and flexibility of a software model run. To achieve this, it is necessary to create a co-simulation environment where, in this specific case, the TU in the Mali model has been effectively substituted by its corresponding RTL block. The expected outcome of such setup is a testbench where both inputs and outputs are those that the Mali model would require/produce standalone but with the added detail/accuracy in the TU part of the design that would be expected from a GPU's RTL top-level simulation, with a much lower computational cost in comparison to running the equivalent simulation for the RTL description of the whole system.

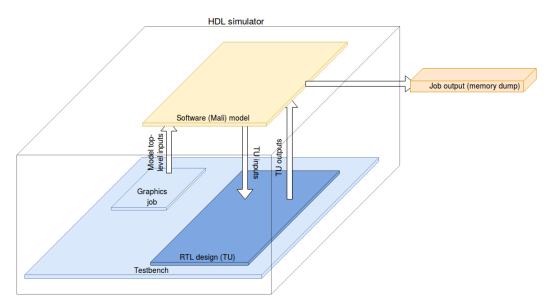

Figure 2.1: High-level diagram of the co-simulation environment

The co-simulation environment that this thesis aimed to create is specific to the case of executing a Mali model top-level run (such as a graphical job of some kind). The main particularity, and the main reason to speak of "co-simulation" is that the TU class in the model will effectively be replaced with its RTL block, in a way such that the model's execution hands over the stimuli to the TU's RTL (instead of simply letting the TU class process them), which will then, via the event-driven simulator (Cadence's Xcelium in this case) process the texturing messages and output texturing result signals. These output signals will be read by the model, which will process them and use them for the rest of the tasks necessary in the graphics job that was run. At the end of the job execution, the model will output the written memory by the result of the job in a file. In other

words, the co-simulation will run a job in the Mali model, written in C++, whose TU is actually not software, but a RTL block, written in SystemVerilog. This idea is shown in the high-level representation of Figure 2.1, where synthesizable RTL blocks are depicted in dark blue, non-synthesizable RTL in light blue, software in yellow and output files of the simulation in orange.

To enable the effective substitution of this unit's RTL in the model execution, the data for each interface in the TU (see section 2.1.2) has to be handled in the final co-simulation solution in a way such that the model can process data generated from the event-driven simulation of RTL and, on the opposite, that the RTL can process data sent in from the C++ object code execution.

Moreover, since the model execution cannot handle discrete-events with as high precision as an event-driven simulation, timing mismatches and delays in data transitions should be taken into account if a seamless co-simulation is desired. These may affect performance metrics or the total cycle-count of a complete graphics job run, but shouldn't make notable differences in the functionality and data correctness.

An extra possibility is that the model may obviate hardware elements or subsystems that are necessary for the real GPU to work, but maybe not essential or trivial if the system is inspected in a pure functional level, as in the case of most software models. For example, a 256-bits wide bus in RTL may be represented as a class in C++ whose members are the different fields of the original message. Therefore some interface logic and/or data storage may be necessary in any of the two sides (software or RTL) to overcome this issue.

#### 2.2 Co-simulation options and solution

The challenges described in this chapter for implementing a co-simulation for this specific case may be overcomed via different ways. Several practical possibilities exist in order to simulate a hardware design with a software component and, inversely, run a program which interacts with a hardware design simulation. The options are very diverse, each with its own advantages and disadvantages. Therefore, only those actually considered for this work will be briefly introduced in this section, with a motivation on why it might or not be the best solution for this concrete scenario. In the end, the chosen alternative will be presented, along with the reasons why it is considered the most suitable.

#### 2.2.1 Description and comparison of possible options

Three candidate methods to implement the proposed co-simulation environment are presented now: Tcl, SystemVerilog's Direct Programming Interface (DPI) and DPI-C and SystemC. These are an interesting set of options, since each communicate with RTL designs and/or software models in a different way, and with different advantages and disadvantages.

#### Tcl

Tcl is a high-level, interpreted programming language which was developed by John Ousterhout as a scripting solution for his Very-Large-Scale Integration (VLSI) layout tool Magic [11]. Since this was one of the very first software of its category, and due to the open-source licensing that both Magic and Tcl were released with, Tcl has become a de facto standard for command scripting in most popular EDA and Computer-Aided Design (CAD) tools. Apart from being multi-platform, it can be used for many different tasks, becoming an interesting candidate for scripting an entire work flow, including verification under simulation [12].

A moderately successful example of using Tcl for co-simulation of a hardware and software model in the same environment was presented in Michael D. McKinney's work, in Section 1.3. This solution had some inconveniences, mainly because of the problem of sharing data between Perl and Tcl, but is very illustrative of how Tcl can be a powerful language for the purpose of co-simulation.

From the experience of the author of this thesis work, and the research conducted, Tcl presents two major problems:

- The **real-time overhead** it introduces if used as the driver/controller of the simulation. Applicable in general to any Tcl-driven simulation flow. Caused by the fact that Tcl interacts with the HDL, event-driven simulator every time it needs to change the value of a signal or control simulation time.

- The data coherence with other computer languages. This is not a problem if Tcl is used in a typical case (driving stimuli of a RTL Device Under Test (DUT) and collecting the output for processing) but is very relevant if software models become an actor in the simulation, as they are commonly written in some other language.

The first problem can be overcome if it is taken into account during the design phase of the Tcl scripts that will control the simulation. The main idea is basically to try to reduce as much as possible Tcl commands that interact directly with the HDL code, such as *force*, run, etc. To achieve this, some testbench-exclusive RTL units may be necessary. An example-comparison of this approach would be to improve the trivial algorithm:

- 1. Drive every input signal to the DUT using force.

- 2. Execute the run command for "clock period" seconds.

- 3. Repeat every clock cycle.

with the more efficient option:

- 1. Drive all stimuli in an ordered manner to a behavioral First In First Out (FIFO) memory, using *force*.

- 2. Execute the *run* command for "simulation-length" seconds. The FIFO will output stimuli signals in the desired manner every clock cycle.

As the reader will imagine, the faster approach requires the implementation/use of a behavioral FIFO, which in most HDLs is, however, not a complex task. With this improvement, calls to run are dramatically reduced and, therefore, the simulation time.

Regarding data coherency, the difficulties seem to be more complex. In [10], the solution of using files to share data variables between languages comes with a huge performance impact, as well as complications in the implementation. One could rapidly think that there might be a better way to communicate Tcl with some other language. In the specific case of this thesis work, the challenge would be to interface a C/C++ software model with/from Tcl scripts. According to Tcl's wiki [13], this can be somewhat easier than for other languages, since Tcl is a C library. It is then possible to create and call a Tcl interpreter from a C program, and also to wrap C/C++ code to make it callable from a Tcl script.

In summary, it is actually possible to use Tcl as a means to implement a co-simulation environment with a software and hardware model, but several non-idealities will come at a cost.

#### SystemVerilog's DPI and DPI-C

According to the IEEE's SystemVerilog language specification [14], DPI is an interface between SystemVerilog and some other foreign programming language in which two layers exist isolated: the SystemVerilog layer and the foreign language layer. Any programming language may be used as the foreign language, since the SystemVerilog side is absolutely indifferent in that sense. However, SystemVerilog currently has only one foreign language layer defined: for the C programming language.

DPI allows importing functions or similar constructs from the foreign language and, similarly, to export SystemVerilog subroutines to the foreign language: tasks and functions. For imported and exported subroutines, a rich subset of SystemVerilog data types is supported by the interface, being most of them C-compatible types, packed types and user-defined types built from types of the two previous categories.

For the case of a software model written in C++, it is possible to import and export subroutines, always assuring that in the language boundary only C types and conventions are used. If C++ features need to be supported by DPI for some reason, linkage semantics and the whole foreign language layer would have to be defined for it. This includes defining how actual arguments are passed to SystemVerilog, how they can be accessed from C++, how SystemVerilog specific data types are represented in C++ (by translating them to and from C-like types), etc

Another important fact to take into account in this case is that some DPI imported subroutines (from the foreign language to SystemVerilog) will require that the context of their call is known. This is the case for subroutines that will call exported subroutines (from SystemVerilog to the foreign language) or access SystemVerilog objects as part of their execution. For this situation, the subroutines have to be specified as *context*, triggering a special instrumentation in their call instances that can provide the mentioned context. This however, presents the downside of decreasing simulation performance, and will affect directly the intended setup for this work, since the main idea is that calls to the top-level

interface functions of the Mali model happen from a SystemVerilog testbench with those functions as DPI imports, which will then call functions imported in the model from SystemVerilog's subroutines to interact with the RTL testbench.

#### SystemC

SystemC is a set of C++ classes and macros that provide a transaction-level interface for modeling and verification purposes of hardware designs written in a HDL. This is a very interesting solution for models written in C++, as SystemC can be used directly as a means to communicate with a RTL hardware design.

The interoperability with SystemVerilog is, in principle, quite straightforward. SystemC modules can instantiate SystemVerilog modules and vice-versa, effectively creating a single module hierarchy with mixed language components. Similarly, SystemC can call SystemVerilog tasks and functions, and SystemVerilog can call SystemC methods, which matches most design flow requirements and also provides a higher simulation efficiency. In fact, even SystemC signals can be bound to SystemVerilog ports and vice-versa [15]. Another advantage is that, since SystemC is part of C++, no extra interfaces or components are necessary between the model and HDL design.

However, despite all the previous positive facts about the use of SystemC for mixed simulation purposes, several complications exist:

- Because SystemC typically uses SystemVerilog's DPI as the communication bridge with SystemVerilog, and DPI defines a C interface, but not a C++ one, DPI cannot be used to traverse SystemC hierarchy, since handles to instances or objects are not easily possible.

- SystemC offers a transaction-level abstraction, which provides a lower detail when compared to the SystemVerilog scheduler.

- Because of the previous, an extra service layer is necessary on top of DPI to take care of the synchronization between the two "worlds".

Regarding the software side, yet more disadvantages exist:

- To use SystemC in a software model, the model has to be designed considering the support for these classes or, at least, providing some compatible interface.

- Currently every EDA vendor uses proprietary binaries for System C. This is an inconvenience if the simulation setup needs to be ported often, or if a more general work flow is in place.

- Following the stated above, each EDA tool will have compatibility for SystemC only for specific gcc compiler versions, which limits the options for the software model implementation.

- If a robust and long-lasting interface with a HDL simulation is desired, SystemC may again not be a good option, as it means using the C++ Application Binary Interface (ABI) directly. The problem is that C++'s ABI has changed several times historically, and this represents a risk in this case, as the compatibility of the SystemC interface can be lost when re-compiling for a new version [16].

#### Comparison of the three options

The three options previously presented to implement co-simulation in this work have different advantages and disadvantages, which the reader will probably have already detected in each one's description. To serve as a quick summary, pros and cons of each option are presented in Table 2.1, Table 2.2 and Table 2.3, for Tcl, SystemVerilog's DPI and SystemC respectively.

|                       | $\mathbf{T}_{\mathbf{CL}}$   |

|-----------------------|------------------------------|

| Advantages            | ${\bf Disadvantages}$        |

| De-facto in EDA tools | Big overhead for simulations |

| Discrete-event level  | Complex embedding in C++     |

**Table 2.1:** Advantages and disadvantages of Tcl as a co-simulation tool

| SystemVerilog's DPI                   |               |  |  |  |

|---------------------------------------|---------------|--|--|--|

| Advantages                            | Disadvantages |  |  |  |

| Widely supported by EDA tools         | -             |  |  |  |

| Discrete-event level                  | -             |  |  |  |

| Computational overhead is low         | -             |  |  |  |

| Well-defined interface for C language | -             |  |  |  |

**Table 2.2:** Advantages and disadvantages of SystemVerilog's DPI as a co-simulation tool

| $\mathbf{SystemC}$         |                                         |  |

|----------------------------|-----------------------------------------|--|

| Advantages                 | Disadvantages                           |  |

| Low computational overhead | Proprietary binaries for each tool      |  |

| Easy integration with SV   | Transaction level                       |  |

| -                          | C++ ABI changes                         |  |

| -                          | Limited compatibility with gcc versions |  |

**Table 2.3:** Advantages and disadvantages of SystemC as a cosimulation tool

#### 2.2.2 Choice of co-simulation tool: SystemVerilog's DPI-C

In the end, SystemVerilog's DPI, with its definition of the foreign language interface for the C language, DPI-C, was chosen as the tool with which the proposed cosimulation environment would be implemented. The main reasons for this decision are:

- The interface between C and SystemVerilog is well defined and consistent and since no extra elements (like the case of SystemC for C++) are introduced, the feasibility of this solution is assured so long as the C standard and SystemVerilog's DPI-C definition remain as they are at the moment of writing this document.

- SystemVerilog, with DPI-C, is supported by most, if not all, EDA vendors, and is fully-supported with Cadence's Xcelium simulator, which was used for this thesis work.

- It is the most logical option for the specific case of the Mali model, as it already exposes a C top-level interface with a set of functions to create an instance to the model, configure it and execute tasks with it, such as graphics jobs.

- In contrast with the previous, if another option was to be used for implementing a co-simulation environment between the Mali model and RTL designs, an important refactoring of the model's code would be necessary. This is completely out of the scope of this project.

- The computational overhead introduced by DPI-C, although existing due to effects like the *context* of imported subroutines, is much lower than in other solutions, permitting an efficient implementation of the co-simulation environment.

After presenting the reasons for selecting this tool, some important and more detailed background information about the data equivalency between SystemVerilog and C and SystemVerilog functions and tasks will be given hereunder, as they represent a central part of this work and the basic theory behind the co-simulation environment implementation.

#### Data equivalency between languages

The equivalency between data types of SystemVerilog and C is very well defined in DPI. Specifically, Annex H in SystemVerilog's language specification is dedicated to the foreign language specification of C for DPI, and all the details on data representation are clarified. However, to simplify as maximum as possible the implementation of the languages interface part of the co-simulation environment created in this thesis, only the basic types mapping was used. These one-to-one relations, extracted from the SystemVerilog's language specification, are shown in Table 2.4. It is worth noting that the encodings for the bit and logic types are usually given in a separate file, svdpi.h, which is implementation-dependent and typically provided by each EDA vendor with their HDL simulators.

#### Rules for functions and tasks

Functions and tasks of SystemVerilog, also collectively referred to as "subroutines", allow the division of large procedures into smaller ones. Both can contain *input*, *output* or *input/output* arguments, and will have visibility of variables and signals in their same scope or module. These constructs are the main enablers of the

| SystemVerilog type         | ${f C}$ type          |

|----------------------------|-----------------------|

| byte                       | $_{ m char}$          |

| $\operatorname{shortint}$  | short int             |

| $\operatorname{int}$       | $\operatorname{int}$  |

| $\operatorname{longint}$   | long long             |

| $\operatorname{real}$      | double                |

| $\operatorname{shortreal}$ | float                 |

| ${ m chandle}$             | void *                |

| $\operatorname{string}$    | ${\rm const~char~}^*$ |

| bit                        | unsigned char         |

| $\log i c / { m reg}$      | unsigned char         |

Table 2.4: Mapping of SystemVerilog and C data types [14]

communication between SystemVerilog and C via DPI, as they can be exported to C from SystemVerilog, and then imported in C as external functions. Likewise, C functions can be imported in SystemVerilog.

Following the SystemVerilog's language specification, several rules distinguishing tasks from functions exist, very relevant for this work:

- A task may contain time-controlling statements, such as a call to the simulator software to run the current simulation for a specific amount of time units.

- A function can enable other functions, but cannot enable a task, while a task may enable other tasks and functions.

- A nonvoid function shall return a single value, while a task or void function don't need to return a value.

- A nonvoid function can be used as an expression's operand, being the value of that operand the value that the function would return.

Because of these rules, and since in the suggested co-simulation environment the software model will be responsible for controlling the testbench clock and the simulator time steps, the following decisions were made regarding tasks and functions:

- Since only tasks can contain time-controlling statements, and for the sake of simplification, all exported subroutines given to the software model with the objective of **writing** values in SystemVerilog will be **tasks**.

- Because tasks can enable other tasks and also functions, but not the other way around, the top-level interface C functions provided by the software model will be imported in SystemVerilog as tasks.

- To improve readability and, again, simplify the setup, all exported subroutines given to the software model with the objective of **reading** values in SystemVerilog will be **functions**.

# Implementation and results

In this chapter, the details of the actual work developed in this thesis work are presented and explained. The solution created to satisfy the constraints given by the objectives shown in Chapter 2 is composed of several software and HDL blocks and constructs, which specifics will be explained, along with the reason behind such design. Following this, the results achieved with the proposed co-simulation environment for GPU IP development will be shown, with some metrics that are considered relevant for this case. Some of these metrics will be presented against other manners of simulating a top-level system test for a RTL block with the aim of highlighting the strengths and weaknesses of the co-simulation solution.

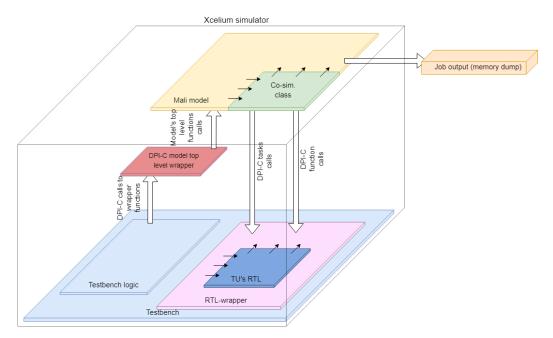

## 3.1 The co-simulation environment

A general diagram of the final co-simulation environment that was created is shown in Figure 3.1 where, apart from the color correspondence explained for Figure 2.1 in Section 2.1.3, now RTL blocks in SystemVerilog with DPI-C functions and tasks are depicted in pink, a collection of functions in C that interact with SystemVerilog objects in red and C++ classes with imported SystemVerilog tasks and functions in green. In this proposed co-simulation environment, the testbench is a very simple block which acts only as the main simulator "container". It has some basic logic to instantiate the software model and call its top-level functions (via a model top-level wrapper written in C), as well as an instance to the RTL wrapper or, from now on in this text, co-simulation wrapper. The co-simulation wrapper is a structural RTL block which contains an instance to the RTL IP, in this case, Mali's TU, along with some interface logic necessary for co-simulation purposes. Finally, the Mali model has been modified to include a custom TU class, from now on, co-simulation class, which effectively replaces the C++ class that modeled the TU behavior and acts as an interface between the software model's TU interface and the cosimulation wrapper. It is important to note that, although testbench logic and the co-simulation wrapper both exist in the testbench, they are completely isolated from each other, being the custom Mali software model the only communication channel possible between them.

As the diagram hints, the co-simulation environment relies on DPI-C to:

1. Allow the testbench to create an instance of the software model, by using DPI-C imported functions from the model top-level wrapper.

- 2. Allow the testbench to call a top-level model's function to run a graphics job, using the same imported functions as before.

- 3. During model execution, let the co-simulation class of the custom software model call TU co-simulation wrapper's imported SystemVerilog tasks and functions to write and read signals to/from TU's RTL, respectively.

Figure 3.1: General diagram of the final co-simulation environment

The result of this co-simulation environment, in general terms, is a framework for executing top-level software model simulations in the same manner as a typical model run but with the added value of using TU's RTL model in place of the original C++ class responsible of modeling this GPU block. A more in-depth and detailed explanation of each block developed for implementing this co-simulation environment is provided hereunder.

# 3.1.1 SystemVerilog testbench and logic

As explained earlier, the SystemVerilog testbench is the starting piece of the co-simulation environment. This HDL block contains some basic logic to create a Mali software model instance and communicate with its top-level interface via the C-written model top-level wrapper (see Section 3.1.2), along with an instance of the co-simulation wrapper that contains the TU's RTL.

First of all, the testbench contains a set of declarations, among them, the instantiation of the co-simulation wrapper, import statements for the DPI-C functions used to interface the top-level of the custom Mali model and several variables that will later be used inside the *begin* block. The most relevant variables to mention are:

- Arguments with which the software model will be initialized. Among them, a flag specifically developed in this thesis work to state that it is the custom model for co-simulation that wants to be instantiated.

- Path to the graphics job that will be run in the co-simulation setup.

- A *print\_stats* flag whose value tells the testbench whether or not model run statistics should be printed out.

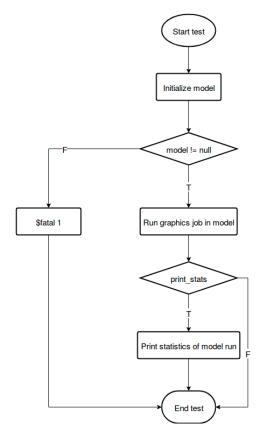

Figure 3.2: Flow chart of the testbench logic

Following the flow chart in Figure 3.2., the testbench logic works as follows. When the simulation starts, the testbench creates and initializes an instance of the software model using a C imported function from the model top-level wrapper, checking that this instance has been correctly created. If, for some reason, the instance does not exist at this point, the testbench returns a fatal error and terminates the simulation. Otherwise, the simulation will continue, and a graphics job will be run in the model using another C imported function from the top-level wrapper. At this point, the custom Mali model will run the graphics job, interacting with the co-simulation wrapper of the TU when necessary without the testbench intervention. If any execution error happens, the model is responsible for handling such situation. In practice, an error condition in the model will

simply be automatically converted by the simulator in a fatal error. Having the model finished the graphics job, the testbench will then finalize by checking if the *print\_stats* flag was set. If so, model statistics of the graphics job run will be required using another C imported function.

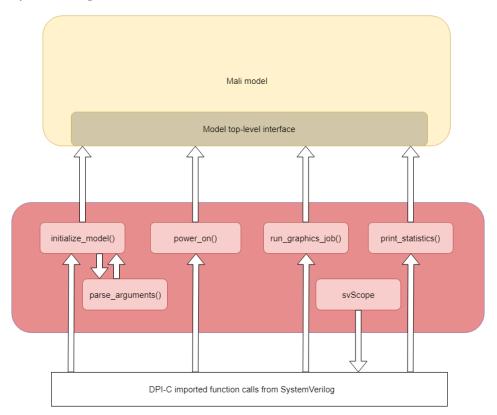

# 3.1.2 Model top-level wrapper

Written in C, between the simulation testbench and the custom Mali model, the model's top-level wrapper acts as a simplified DPI-C compatible interface between the model's top-level functions and the testbench logic. This block exposes several high-level C functions to the HDL testbench all of which internally call model's top-level functions. These wrapper's functions can be imported and called from SystemVerilog to create and control a model instance.

Figure 3.3: Block diagram of C-written model top-level wrapper

A block diagram representing this entity is given in Figure 3.3 and a summarized explanation of each function is given hereunder:

• initialize model() is responsible for creating an instance of the custom Mali model with the specified arguments/modifiers. These arguments are parsed and converted to the format used by the model's top-level interface in the auxiliar function parse arguments().

- power\_on() performs several operations in the model, such as register writes, mimicking the behavior of a power-on sequence of the GPU. This function was heavily used for debugging the communication between the testbench and the Mali model in the beginning of this thesis work, but has not been included in the final testbench logic, as it is not relevant for characterizing the behavior of co-simulation with the TU.

- run\_graphics\_job() encapsulates the necessary operations to request the model to compute a certain graphics job, given as a separate input file.

- print\_statistics() will request the model to print the statistics obtained from running the graphics job with the previous function.

Finally, an important bit of this entity deserves a more detailed explanation, the DPI-C handler svScope. This variable exists in any SystemVerilog environment using DPI-C to communicate C object code with SystemVerilog and represents, as its name suggests, the current scope in the HDL hierarchy for which the imported C functions have visibility. Every time a C function needs to interact in some way with the HDL hierarchy (p.e. calling an imported SystemVerilog function/task or returning a result value), it will try to do so at the level specified by svScope, effectively being blind to any other levels of the hierarchy.

This fact brought many problems at the beginning of this thesis work, as the previously presented functions were called from the testbench and would return a value to the testbench, but also some would call SystemVerilog imported functions/tasks to interface with the co-simulation wrapper of the TU's RTL. More concretely, the  $run\_graphics\_job()$  execution would, at a given point in time, arrive to the co-simulation class, which would try to communicate with the co-simulation wrapper, using a wrong svScope (still pointing to the testbench). The solution to this problem was to let all of these functions modify the current svScope in the necessary way to ensure that the hierarchical reference pointed by svScope was always the intended.

# 3.1.3 System Verilog co-simulation wrapper

The SystemVerilog co-simulation wrapper was developed to act as a bridge interface between the RTL implementation of the TU and the custom Mali model or, more specifically, the co-simulation class of the custom model. Within it, a collection of logic, registers, tasks and functions are responsible for enabling communication via DPI-C to the co-simulation class, adapt the data received from the model for the TU's RTL to consume and adapt the data output from the TU for the model to consume. This entity works in such a way that for both the co-simulation wrapper and the TU's RTL the communication is transparent and direct, except for some effects introduced that will be explained later. A block diagram of the co-simulation wrapper is shown in Figure 3.4 and the details on each part of it are given hereunder.

Figure 3.4: Block diagram of RTL co-simulation wrapper

## Exported tasks and functions

To implement a way for the co-simulation class to interface with RTL signals, a number of tasks and functions were implemented in SystemVerilog, one or more for each of the interfaces of the TU (see Section 2.1.2). Tasks were chosen as the mechanism for the model to write values into RTL signals, being one of the main reasons that tasks can consume simulation time, while functions do not grant this possibility. Similarly, functions were chosen as the manner for the model to read values of signals. This is essential for the case of driving the clock signal. Because the model controls the simulation, it needs to control the clock as well and, therefore, be able to advance the simulation time every time a clock edge is generated.

All of these tasks and functions are declared as DPI-C exports, so that the co-simulation class can import them as extern "C" functions and use them seamlessly from a software point-of-view. At this point, these subroutines simply allow the writing or reading of certain variables in the co-simulation wrapper.

## Co-simulation logic

Data signals are treated differently in the software model and in the RTL implementation. This might yield some cases where, for example, some data may wait N cycles in the model to be available as a *struct* or *object*, while that same data in the RTL implementation would be received, in smaller words, during those N

(a) Flow chart of write mechanism (b) Hardware logic for shift register #1 of wide data signals to shift reg. #1

**Figure 3.5:** Co-simulation wrapper logic for wide-words data or data received in several cycles

cycles. Another case sharing the solution that is going to be presented is that of RTL input signals wider than 64 bits, which cannot directly cross the DPI-C interface with native C/SystemVerilog variable representations. The only possible approach to solve this is to divide the transmission of this type of data between model and RTL in several calls to the same task, once the data is available in the model, and use some extra logic in the co-simulation wrapper to manage that data in a way the RTL interfaces can accept. Such approach, used in every input signal affected with dedicated variables and logic in each case, is shown in two diagrams on Figure 3.5, where shift register #0 and #1 are two separate SystemVerilog variables. The decision of using two separate variables for this implementation is mainly to ensure that a wrapper-stored signal can be offloaded to some RTL unit's input port while new data for the same port is being written by the model at the same time.

When some signal affected by this situation is to be written, the process in Subfigure 3.5a will trigger. The model side of the setup will be responsible of writing only one byte in every task call, so that this new byte will be shifted left into a "shift register #0". When the last byte is written to this register, a flag will be set to indicate that the loaded value can be copied to the "shift register #1". The value stored every cycle in shift register #1 depends on some logic, depicted in Subfigure 3.5b. The output value (connected to the corresponding input signal of the RTL interface) will always be a M-1 to 0 slice of the register, being M the width of the RTL interface. Every clock cycle, the new value of shift register #1 can either be:

- That of shift register #0 (has the highest priority).

- The previous value shifted right M bits (the new data word is connected to the RTL input).

- The previous value, if for some reason the word offload has to be paused. This is the case for some of the input signals, and depends on the type of interface being used. For example, handhsake-based interfaces will require this if the slave marks "not ready" at some point of the transmission.

The last detail worth mentioning for input signals is that those whose data representation in the model are directly mappable to variables or signals in SystemVerilog are directly updated by the model but also others have to be registered before being connected to the RTL interface for timing alignment or other reasons, like the one just presented. As a result, these signals will suffer a one-cycle delay as a side-effect.

Regarding output signals from the TU's RTL, the intermediate logic of the cosimulation wrapper simply bypasses values in most cases. However, some signals which are wider than 64 bits have to be sliced in some way for the model to be able to read them in successive calls to SystemVerilog functions through the DPI-C interface. For these cases, a combinational copy of these signals is updated in the wrapper in the form of a byte vector of length  $\frac{M}{8}$ , where M is once again the total width of the signal in bits.

### Shared data bank

While designing the part of the co-simulation environment corresponding to the shared data interface of the TU, a previously overlooked fact was found. As mentioned in Section 2.1.2, this interface reads data stored in other parts of the GPU micro-architecture required for texturing operations. In the software model implementation of this interface, the raw data structures that are read are given directly to the TU class while, in the RTL implementation, the shared data interface actually contains signals used to address a memory satellite inside the TU. The signals that would directly map to those the software model exposes to the former TU class are, in fact, one of the interfaces of this internal RTL memory satellite. Therefore, some mechanism was needed to overcome this interfaces' misalignment.

The implemented solution by passes the RTL memory satellite and allows the custom Mali model to write the shared data directly to the internal consumer deeper into the TU's RTL implementation. A diagram of this structure can be observed in Figure 3.6. Additional hardware is introduced in the co-simulation wrapper in the form of a "shared data bank". This bank contains M lanes, one for each type of data, which at the same time contain I indexes each. This yields a total of  $M \cdot I$  registers, of varying sizes depending on the data.

The access to this shared data bank can be done either by the custom software model via SystemVerilog exported tasks, to write into some specific lane and lane index, or either by the RTL data consumer, to address a specific piece of data and read it. However, the select signals of the data consumer, as well as the actual data signals are internal to the TU RTL implementation. To effectively bypass the

Figure 3.6: Block diagram of the co-simulation wrapper's shared data bank

memory satellite and give visibility to this signals from the co-simulation wrapper's perspective, two methods are put into place:

- For the input data signals to the consumer, their value is permanently altered during the simulation, using the SystemVerilog force statement. This allows to "connect" these internal signals directly to the output of the shared data bank's lanes, forcing the simulator to overlook the actual connection that the signals would normally have considering the RTL logic.

- For the select signals of the data consumer, which are outputs, their value is used in a combinational statement in the shared data bank to continuously address their corresponding bank lane using hierarchical expressions. An illustrative example of such expressions would be:

$$u$$

texture unit. $u$  data consumer.select signal  $0$

Which, in this case, would return the current value of the data consumer's signal  $select\_signal\_0$ .

## 3.1.4 The model's co-simulation class