## Evaluation of flexible SPA based LDPC decoder using hardware friendly approximation methods

DEEPAK YADAV AFSHIN SERAJ MASTER'S THESIS DEPARTMENT OF ELECTRICAL AND INFORMATION TECHNOLOGY FACULTY OF ENGINEERING | LTH | LUND UNIVERSITY

## Evaluation of flexible SPA based LDPC decoder using hardware friendly approximation methods

Deepak Yadav deepak.yadav.943@student.lu.se Afshin Seraj afshin.seraj.877@student.lu.se

Department of Electrical and Information Technology Lund University

> Supervisor: Erik Ledfelt (Ericsson) Alberth Arvidsson (Ericsson) Magnus Malmberg (Ericsson) Liang Liu (LTH)

> > Examiner: Erik Larsson

September 22, 2017

© 2017 Printed in Sweden Tryckeriet i E-huset, Lund

## Abstract

Low Density Parity Check (LDPC) coding has recently become a hot topic for its near-shannon performance, and will be used in the next generation of telecommunication systems (5G), the original algorithm for decoding LDPC codes is Sum-Product Algorithm (SPA). As the frequently-used Min-Sum Algorithm (MSA) is an overestimation of SPA, more accurate approximations of SPA are demanded in high-accuracy applications. This thesis studies the different ways of approximating the SPA and evaluates the cost and accuracy of an SPA decoder based on an optimum approximation. In a general comparison between main approximation methods, Simple Piecewise Linear (SPWL) approximation showed the most area-efficiency. After studying the different mathematical formats of SPA, the Soft-XOR based format with forward-backward scheme was found to be the most hardware-efficient one. Its core function (Soft-XOR) was implemented with Centered Recursive Interpolation (CRI) approximation, which achieved the highest efficiency, compare to other approximations. A Check Node Unit (CNU), which is the main computational part of LDPC decoders, was implemented based on the CRI-based Soft-XOR. The CNU uses a pipe-lined forward-backward architecture, and its speed and area are flexible and can be changed in instantiation. A SPA decoder with flooding schedule based on the developed CNU is estimated to have an area of 1.6M as equivalent gate count, with a clocking frequency of 1.25GHz. The accuracy loss, compare to floating point SPA, is 0.3dB for 10 iterations and a throughput of 10 Gb/s. The accuracy loss becomes less than 0.1 dB for 20 iterations with a throughput of 5Gb/s and the same area. Comparing MSA and SPA, the developed SPA CNU is 2.1 times larger than the developed MSA CNU, but gains 0.3dB more accuracy for 10 iterations. The accuracy gain increases with higher number of iterations. A comparison with other works is also provided. The IEEE 802.11n Wi-Fi standard is used for the decoder and the 18nm CMOS technology is used for synthesis.

## Acknowledgment

We would like to express our gratitude towards our thesis supervisors Erik Ledfelt, Albert Arvidsson and Magnus Malmberg at Ericsson for their continuous guidance and support. We are also thankful to Charlotte Sköld for providing us with this opportunity to learn. Special thanks to all the Ericsson ASIC IP1 team members with whom we have had great time.

We would also like to thank our academic supervisior Liang Liu at LTH.

## Popular Science Summary

You have to get lost before you can be found, a quote by Jeff Rasley goes very well for Low Density Parity Check (LDPC) codes. First invented by Gallager in 1962 but kind of lost during the journey of evolution of telecommunication networks because of their high complexity and demanding computations, which technology was not so advanced to handle, at that time. However, during late 1990s, success of turbo codes invoked the re-discovery of codes. Recently it has attracted tremendous research interest among the scientific community, as today's technology is advanced enough and to make LDPC decoders completely commercial. In a wireless network, the information is not just simply sent, but first encoded. In a sense, all the transmitted bits are tied together, according to some mathematical rules. Therefore, if noise destructs parts of the information while traveling, the LDPC decoder at the receiver side, can automatically detect and retrieve those parts, based on the other parts of the code. Here, our main focus is on the decoder. For actual hardware implementation of the decoder, some level of approximation of the ideal algorithm is always necessary, which reduces the accuracy depending on the approximation.

Ericsson is developing the next-generation wireless network for 5G, and already possesses a form of "Min-Sum" approximation of the LDPC decoder. As the current requirements demand more accurate decoders, the goal of this thesis is to find and evaluate a more accurate but more costly version of LDPC decoder, with more flexibility. Thus, several promising approximation methods were selected and evaluated based on their complexity, cost, and their accuracy towards error correction. After performing several trade-offs, an approximation method is chosen and the cost of a LDPC decoder using that approximation, is derived. With this acquired data, a trade-off between accuracy and cost can be made, depending on the application.

# Table of Contents

| 1 | Intro                                | oduction                            | _ 1  |  |  |

|---|--------------------------------------|-------------------------------------|------|--|--|

|   | 1.1                                  | Background                          | 1    |  |  |

|   | 1.2                                  | Goals                               | 1    |  |  |

|   | 1.3                                  | Structure                           | 2    |  |  |

| 2 | Арр                                  | roximation Methods                  |      |  |  |

|   | 2.1                                  | Candidate Approximation Methods     | 3    |  |  |

|   | 2.2                                  | Behavioral Model                    | 7    |  |  |

|   | 2.3                                  | Result                              | 8    |  |  |

|   | 2.4                                  | Conclusion                          | 12   |  |  |

| 3 | Low                                  | Density Parity Check (LDPC)         | _ 15 |  |  |

|   | 3.1                                  | Introduction                        | 15   |  |  |

|   | 3.2                                  | Modulation and LLRs                 | 15   |  |  |

|   | 3.3                                  | Sum-Product Algorithm (SPA)         | 17   |  |  |

|   | 3.4                                  | CN update Methods                   | 19   |  |  |

|   | 3.5                                  | IEEE 802.11n H Matrix               | 22   |  |  |

|   | 3.6                                  | Conclusion                          | 23   |  |  |

| 4 | Approximation of $\boxplus$ function |                                     |      |  |  |

|   | 4.1                                  | Min-Sum Approximation               | 26   |  |  |

|   | 4.2                                  | Double-PWL Approximation            | 26   |  |  |

|   | 4.3                                  | Single-PWL Approximation            | 27   |  |  |

|   | 4.4                                  | CRI-based Approximation             | 27   |  |  |

|   | 4.5                                  | Result and Conclusion               | 28   |  |  |

| 5 | Sim                                  | ulation Results                     | _ 31 |  |  |

|   | 5.1                                  | Effect of iterations on BER         | 31   |  |  |

|   | 5.2                                  | Effect of total bits on BER for SPA | 31   |  |  |

|   | 5.3                                  | Number Representation               | 33   |  |  |

| 6 | Hard                                 | dware Architecture                  | _ 35 |  |  |

|   | 6.1                                  | CNU Implementation                  | 35   |  |  |

|   | 6.2                                  | Permutation Network                 | 40   |  |  |

|    | 6.3       Memory       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .< | 41<br>42        |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 7  | Synthesis<br>7.1 Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>45</b><br>48 |

| 8  | Conclusion         8.1       Future Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                 |

| Re | ferences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _ 53            |

# List of Figures

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9<br>2.10<br>2.11<br>2.12<br>2.13 | Hyperbolic Tangent FunctionPWL concept [9]Algorithm description of CRIBlock diagram for behavioral modelComparator and Decoder circuitsArea vs Precision for different sub regionsArea vs precision for different combinations in 6-curve PWNLArea vs Precision for best combinations (6-curve PWNL)Area vs PrecisionComparison of area vs precision with different regions for SPWLArea vs Precision for CRIComparison of different approximation methodSPWL vs SPWL+CRI | 3<br>5<br>7<br>8<br>9<br>10<br>11<br>11<br>12<br>13<br>13<br>13<br>14<br>14 |

|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| 3.1<br>3.2<br>3.3<br>3.4                                                                    | Overall view of a simple communication system                                                                                                                                                                                                                                                                                                                                                                                                                             | 16<br>17<br>22<br>22                                                        |

| <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> </ul>    | soft XOR function                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 25<br>26<br>28<br>29<br>29<br>30                                            |

| 5.1<br>5.2<br>5.3                                                                           | SNR vs BER for different iterations                                                                                                                                                                                                                                                                                                                                                                                                                                       | 32<br>32<br>33                                                              |

| 6.1<br>6.2                                                                                  | Top level architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 36<br>37                                                                    |

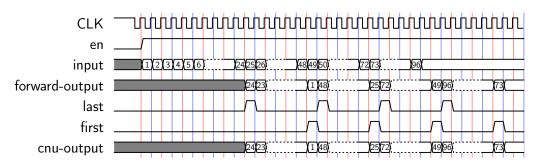

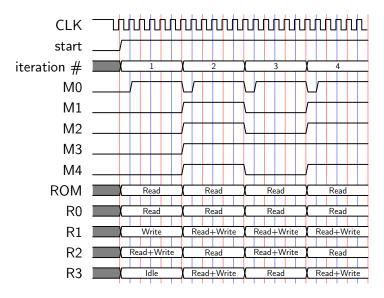

| 6.3 | CNU timing diagram                   | 37 |

|-----|--------------------------------------|----|

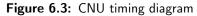

| 6.4 | CNU hardware architecture for SPA    | 38 |

| 6.5 | Implemented Min-Sum CNU architecture | 39 |

| 6.6 | Barrel shifter                       | 41 |

| 6.7 | Memory access timing diagram         | 43 |

| 6.8 | Data Flow                            | 44 |

# List of Tables

| 2.1 | Estimation of area based on simple logic blocks (the unit is a FA or 28 transistors) | 8  |

|-----|--------------------------------------------------------------------------------------|----|

| 7.1 | Area comparison for different implementations of Soft-Xor                            | 46 |

| 7.2 | Synthesis Area results of implemented flooding SPA-based decoder                     |    |

|     | architecture                                                                         | 46 |

| 7.3 | Area distribution for SPA CNU                                                        | 47 |

| 7.4 | Area comparison of implemented SPA and estimated Min-Sum CNU                         | 47 |

| 7.5 | LDPC Decoder Comparison                                                              | 48 |

| 7.6 | Decoder with proposed CNU and different speeds                                       | 49 |

|     |                                                                                      |    |

## Acronyms

**BER** Bit Error Rate. **BP** Belief Propagation. BPSK Binary Phase-Shift Keying. **CN** Check Node. **CNU** Check Node Unit.  ${\bf CRI}\,$  Centered Recursive Interpolation. LDPC Low Density Parity Check.  ${\bf LLR}\,$  Log-likelihood Ratio.  ${\bf MSA}\,$  Min-Sum Algorithm.  $\mathbf{NOF}\_\mathbf{BITS}$  Number of bits. **RAM** Random Access Memory.  ${\bf ROM}\,$  Read Only Memory. **SNR** Signal-to-Noise Ratio. **SPA** Sum-Product Algorithm. **SPWL** Simple Piecewise Linear. **VN** Variable Node.

# $\_\______ Chapter <math>\bot$ Introduction

## 1.1 Background

Low Density Parity Check (LDPC) coding technique has regained a lot of attention, due to its capability to reach Shannon's limits, i.e. transmitting maximum possible amount of data with minimum power, and therefore, it will be used for the next generation of telecommunication systems (5G). The theoretical algorithm that runs very successfully on LDPC decoders, is Sum-Product Algorithm (SPA). However, the hardware implementation of a pure-SPA algorithm requires implementing trigonometrical functions, such as tanh, which make the hardware unfeasibly expensive. Therefore, lots of research has been done to estimate the behavior of pure-SPA, in both algorithmic level, and hardware level. On algorithmic level, the Min-Sum Algorithm (MSA) approximation, has reduced the hardware size considerably, by introducing a SNR degradation of 0.8dB, compare to SPA [1],[2]. To compensate for the over-estimation of MSA, two successful branches of MSA, known as "Offset Min-Sum(OMS)" and "Normalized Min-Sum (NMS)". have reduced the SNR degradation to the range of 0.2dB for NMS and 0.5dB for OMS, by introducing slightly more cost and complexity [3],[4]. The complexity comes from the fact that OMS/NMS require a channel estimation to tune their scaling/offset factors, based on the channel's noise. Also, the channel mismatch effect induces a higher error floor for NMS [1]. However, these two algorithms have found extensive commercial use. On the hardware level, also, there exists a variety of hardware-friendly approximations of SPA, and the mathematical functions involved in its CNU (Check-Node Unit), that is the main computational part [5], [6], [7]. These approximations put LDPC decoders on a spectrum, ranging from the most accurate one, to the least costly one, that is "Min-Sum". This thesis investigates high-precision LDPC decoders from a hardware perspective, and its goals are as follows:

### 1.2 Goals

- 1. Exploring different hardware-based approximation methods.

- 2. Finding the best approximation of SPA, from a hardware perspective.

- 3. Developing a flexible CNU in RTL, based on the chosen approximation.

4. Evaluating the cost and precision of a total high-precision LDPC decoder, based on the developed CNU, and assesses if the increase in precision justifies the cost.

### 1.3 Structure

Chapter 2 is dedicated to the investigation of different approximation methods and their comparison in terms of precision and hardware-cost. In chapter 3, we will cover the theoretical part of LDPC decoder, compare its different mathematical formulations, and select a hardware-efficient one for implementation. chapter 4 is specified to the core function of the LDPC decoder. In this chapter, a number of its different implementations with different approximations will be described and assessed in RTL level, and the best one will be selected. In chapter 5, there is an investigation of the BER/SNR behavior of the simulated SPA with different quantizations (number of bits) and number of iterations. The BER/SNR performance of MSA is also provided to compare. The chapter concludes with a brief explanation for choosing the fixed-point number representation for the system. Chapter 6 describes the RTL (system-verilog) implementation of a flexible pipelined forward-backward Check Node Unit (CNU) with the selected core function. The number of inputs that the developed CNU accepts each cycle, can be adjusted by changing a variable in the code, which can provide the opportunity to easily tune the speed, cost and latency (critical path), before fabrication. Also, in this chapter a flooding LDPC decoder architecture, based on the developed CNU is suggested and its cost is estimated. Synthesis results and conclusion are provided in chapters 7 and 8, respectively.

# \_\_\_\_\_<sub>Chapter</sub> 2 Approximation Methods

In this chapter, several popular approximation methods will be focused on, and will be compared to each other in terms of precision and estimated hardware cost. As case study, the Hyperbolic tangent (tanh) function has been chosen. Hyperbolic tangent function is among the most frequently used functions, and has applications in LDPC decoders, as will be discussed in section 3.4. Moreover, its common, yet challenging, shape provides a suitable framework to investigate and fairly compare the approximation methods. In this chapter, after an introduction to the function, 7 candidate approximation methods are briefly introduced, among which 5 are simulated in C++ to assess their precision versus area consumption. Methods used for rough estimation of area at algorithm level (C++), will be explained later.

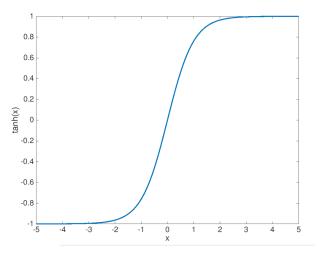

Figure 2.1: Hyperbolic Tangent Function

## 2.1 Candidate Approximation Methods

The Tanh() function is shown in Figure 2.1. Two properties of this function can be exploited to make the approximating hardware more efficient. One is that

tanh(x) is almost constant for x < -4 and x > 4, and another one is that tanh() is an odd function tanh(-x) = -tanh(x). Thus, the range to be considered for approximation can be limited to 0 < x < 4.

#### 2.1.1 Isosceles Triangular Approximation

The derivative of the tanh() function resembles an isosceles Triangle that can be estimated as Equation 2.1 . Integrating this equation, an estimation of tanh() function is achieved in Equation 2.2 [8]. Computation of this equation needs one multiplier, an adder and a shifter. This method is proven to have worse area-precision characteristic than LUT in [9] and is therefore not implemented in this work.

$$tanh = \begin{cases} 1 - \frac{|x|}{2} & 0 \le x \le 2\\ 0 & \text{otherwise} \end{cases}$$

(2.1)

$$tanh' = \begin{cases} x - 0.25 * sign(x) * x^2 & 0 \le |x| \le 2\\ 0 & \text{otherwise} \end{cases}$$

(2.2)

### 2.1.2 Look-up Table (LUT)

One of the most used method of approximation is selecting a few points in the curve and storing them in a LUT. A LUT is simply a mapping of each subrange of inputs to a certain output. Therefore, the maximum error occurs in the middle of each subrange, and, of course, more points result in better accuracy. A typical improvement is storing the mean amount of output in each subrange, and reducing the error by half [10] (which is also used in this work). LUTs are constructed in two different ways. The straight forward one is storing the selected outputs in a ROM.  $2^i$  outputs must be stored, where "i" is the number of bits in the input. A decoder maps the inputs to their corresponding outputs in ROM. The other method is called "bit-level mapping" and is simply mapping the inputs to outputs with purely combinational logic. This enables the synthesizer to optimize away some logic, after the input/output pattern is known [9].

Since in this comparison C++ is used to estimate area, ROM-based method is considered for comparison, because its area can easily be estimated with mathematical expressions. In both methods, LUT area can be much smaller, if selected inputs are equally distributed over the total range, which makes the decoder much smaller. Such equally spaced inputs also provide excellent framework for LUT to be combined with other methods. Here, two combinational methods, named SPWL and LUT+CRI, enormously benefit from such a setting, as will be shown later. However, if inputs are not equally spaced, we can concentrate more inputs where more change in the function occurs, and reduce the number of required stored points. Such method is called RALUT (Range Addressable Look-Up Table) and is discussed in [9]. Other methods in between these two extremes of LUT and RALUT also can be used to reduce the area of decoder and yet benefit from higher accuracy per number of stored points. For instance, In [11], the curve is divided into 3 subregions in a RALUT fashion and then, each of this subregions is divided into 8 equal subregions in a LUT fashion.

#### 2.1.3 Piece-wise Non-linear Approximation (PWNL)

The total range 0 < x < 4 can be divided into N sub-regions, and each sub-region is approximated with a second order polynomial  $(ax^2 + bx + c)$  and the coefficients (a,b and c) are stored in LUTs (Look-Up Table). This method is accurate but needs three multiplication, and consequently, a relatively higher area/delay compare to other methods.

#### 2.1.4 Coefficient-based Piece-wise Linear Approximation (CPWL)

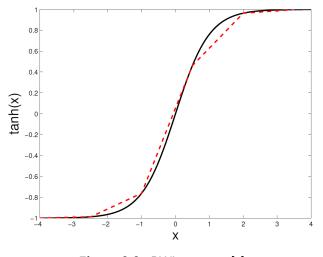

As shown in Figure 2.2, PWL is Similar to the previous method, but each subregion is approximated with a line (first-order equation).

Figure 2.2: PWL concept [9]

There are two methods for PWL hardware implementation. The first is CPWL which includes storing coefficients "a" and "b" in equation: (ax + b) in LUT, and the computation will be based on these two values. The disadvantage is having to use a multiplier, which can be expensive, and is therefore not implemented here. The second method [12] is here called SPWL (Simple Piece-wise Linear Approximation) and can be considerably more area efficient. It is described in 2.1.5.

#### 2.1.5 Simple Piecewise Linear (SPWL)

Instead of storing the coefficients, a number of points in the curve can be chosen to be stored in a LUT, and computation of Equation 2.3 can be based on them.

$$y = \frac{y_h - y_l}{x_h - x_l} (x - x_l) + y_l \tag{2.3}$$

To improve precision, instead of approximating the function with a straight line between the two end points  $(y_h, x_h)$  and  $(y_l, x_l)$ , one can use another straight line that minimizes the error, possibly by half, without loosing any area [12][13]. In other words, instead of saving  $y_h$  and  $y_l$  as  $tanh(x_h)$  and  $tanh(x_l)$  respectively, slightly modified values can be saved in ROM. This approach is not taken in our C++ implementation.

At first sight, a divider and a multiplier are needed to compute Equation 2.3. However, if the points are equally distributed on X axis, as discussed in 2.1.2,  $x_h - x_l$  is a known number which makes the devision trivial. Also, if  $x_h - x_l$  is a power of 2, the devision is a simple shifter and the multiplication can be simplified. In this case,  $x - x_l$  can actually be a few LSB bits of the input. If the number of the input bits is I and the number of subregions is N, then the last M bits (LSB bits) of the input are chosen as the multiplicand  $(x - x_l)$ , where M is derived from Equation 2.4.

$$M = I - \log_2(N) \tag{2.4}$$

Following this pattern in our C++ implementation, we sweep I, N and O(number of output bits) and by obtaining their corresponding precision and area consumption, we are able to choose an optimum value for these three variables.

#### 2.1.6 Centered Recursive Interpolation (CRI)

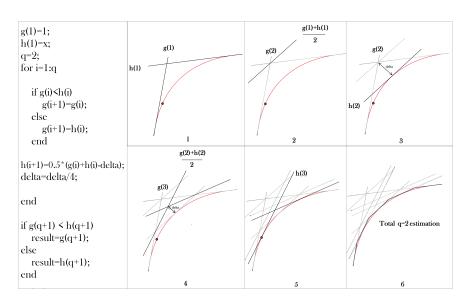

CRI (Centered Recursive Interpolation) is a recursive algorithm that estimates the function after a known number of clock cycles. The theory is specified in [14] and used to approximate the sigmoid function in [15]. First the curve under interest is initially estimated with a few lines, all tangent to the curve (here, 2-line case is studied, g=x and g=1, which do not need any computation to be calculated). An optimum choosing of *delta* gives best precision. The code and the figures showing the approximation in each step, are shown in Figure 2.3. The primary advantage of CRI is absent of any multiplier and memory. It is verified that accuracy of CRI does not improve much for "q" more than 4. In the example of Figure 2.3, q=2 is chosen. As shown, the precision improves with clock cycle.

From the hardware perspective, the iterations could be performed all in one clock cycle, or each in one cycle. The disadvantage of the latter is more latency and complexity due to added registers to the design, while the former suffers from higher area consumption. Here, we consider the former alternative for our later analysis.

#### 2.1.7 SPWL+CRI

To get better precision than SPWL, we presented a combined method of SPWL and CRI. In this method, other than fetching  $y(x_1) = y_l$  and  $y(x_2) = y_h$  from ROM, as in SPWL,  $y(x_0)$  and  $y(x_3)$  are also fetched. Therefore, similar to SPWL, enough data is available to derive the two initial lines for CRI, according to Equation 2.5.

#### Approximation Methods

Figure 2.3: Algorithm description of CRI

$$y(1) = \frac{y(x_3) - y(x_2)}{x_2 - x_1}(x - x_2) + y_2 \quad y(2) = \frac{y(x_1) - y(x_0)}{x_2 - x_1}(x - x_1) + y_1 \quad (2.5)$$

Therefore, two simple multipliers and a CRI computation is added to gain more precision.

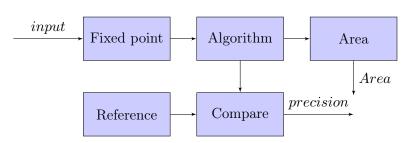

### 2.2 Behavioral Model

A behavioral model is realized in C++ in order to implement the above algorithms in fixed point number representation. Figure 2.4 describes how the model works. A parametrized fixed point class is written in C++ in order to convert input data into fixed point. In Figure 2.4, *Fixedpoint* block takes input data and it requires number of integer bits and fraction bits as an input from user. The output from this block will be fixed point data based on given integer and fraction bits. In *Algorithm* block, a particular algorithm is selected to produce an approximation of *tanh* function.

A reference model of *tanh* function is generated inside reference block by using same input data. Output from reference and algorithm block are compared to get precision. Area calculation are done based on area equation described in below section. Area versus precision curves was plotted in order to compare accuracy of different method.

Figure 2.4: Block diagram for behavioral model

## 2.3 Result

The results of the 5 implemented algorithms are presented below. The unit for area is the number of full adders(FA), which when multiplied by 28 (the number of transistors in a FA), gives the number of transistors used in the design. The Area estimation is based on the Table 2.1.

| Table 2.1: | Estimation of area  | a based | on simple | logic b | olocks ( | the unit |

|------------|---------------------|---------|-----------|---------|----------|----------|

| is a F/    | A or 28 transistors | )       |           |         |          |          |

| Logic       | Area                 | description                                              |

|-------------|----------------------|----------------------------------------------------------|

| Adder       | N                    | N = no. of bits for inputs                               |

| Multiplier  | N * M                | N= no. of bits for input 1; $M=$ no. of bits for input 2 |

| Comparator  | 0.64N                | N= no. of bits for inputs                                |

| And/OR gate | (N-1) * 0.21         | N = no. of inputs                                        |

| Decoder     | $2^N * (N-1) * 0.21$ | N = no. of inputs                                        |

| ROM         | (M*N)/(28*2)         | M = Length; N = Width                                    |

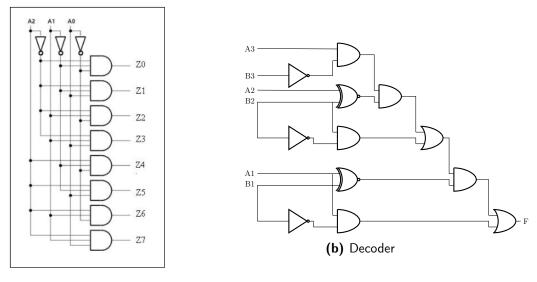

The area of the comparator (Figure 2.5) and AND gate in Table 2.1 are calculated in Equation 2.7 and Equation 2.6, respectively. The area of the decoder (Figure 2.5), which will be used in 2.3.2, is calculated in Equation 2.8. In the table, Inverters in *decoder* are omitted and ROM is without *decoder*.

$$area(AND) = \frac{6*N}{28}$$

$$= 0.21N$$

(2.6)

$$area(Comparator) = \frac{NOT(2*N) + AND(6*(2N-1)) + XOR(4N) + or(6*(N-1)))}{28}$$

= 0.64N

(2.7)

$$area(Decoder) = \frac{6 * (2^i * (i-1))}{28}$$

(2.8)

(a) Comparator

Figure 2.5: Comparator and Decoder circuits

#### 2.3.1 Piecewise non-linear approximation

The approximated area for 3 multiplications and 2 additions is calculated by Equation 2.9. The area for the LUT for storing the coefficients is omitted, as it is much smaller compare to the rest of the design.

$$area = i^2 + 3ij + 4i + 2j \tag{2.9}$$

where, i= number of input bits and j=number of coefficient bits.

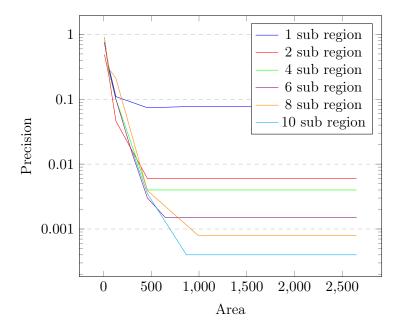

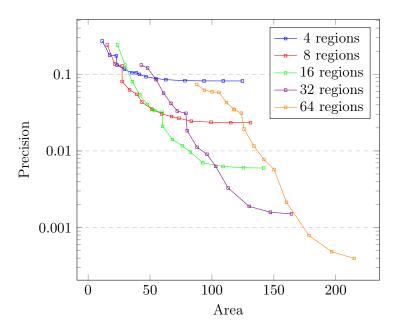

As mentioned in the above section, we will get different precision and area with different number of sub regions. So in order to find out good number of sub regions, the whole range is divided into different number of sub regions and for each case, area and precision was calculated. Figure 2.6 shows the area versus precision plot for different number of sub regions or curves. Area was calculated by sweeping number of fraction bits for input as well as coefficients while keeping output bits the same. It can be seen from the plot that precision is improved with increase in number of subregions. After analyzing the result, six number of curves was selected for further optimization, i.e. when  $(i \neq j)$ .

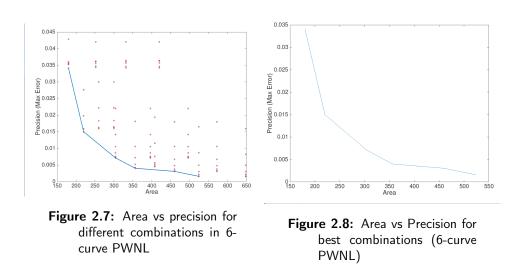

In order to find out best combination of input, coefficient and output bits, a framework was made that will select different combination of these three and produce error and area for each case. Figure 2.7 shows results from above framework, for 6 curves. In the plot each data point represents different combination of bits for each of three. From Figure 2.7 minimum precision and minimum area combination needs to be selected as final result. Figure 2.8 shows best data points

Figure 2.6: Area vs Precision for different sub regions

selected from Figure 2.7.

#### 2.3.2 LUT

Equation 2.10 is used to calculate the area for this method. The first term computes the area of decoder, and the second term is the area of the ROM (see Table 2.1).

$$area = \frac{6 * r * (\log_2 r - 1) + (r - 1) * o}{28}$$

(2.10)

where o=number of output bits and r=number of regions

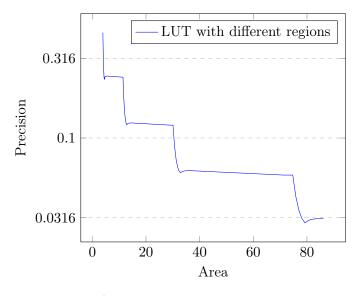

Figure 2.9 shows a curve for area and precision. The figure was plotted by sweeping output bits and number of regions, and selecting the best combinations. From figure, it can be seen that as we increase number of regions which means more number of LUTs, we get better precision but also bigger area.

#### 2.3.3 Simple piecewise linear approximation

Implementation of SPWL approximation requires a multiplier and a look-up table. According to theory (2.1.5), a part of the input bits goes to LUT and the rest (a few LSB bits) is the multiplicand, according to Equation 2.4. Area of SPWL is calculated as Equation 2.11, that is the area of the LUT added to the area of the multiplier (the last term).

$$area = \frac{6 * r * (\log_2 r - 1) + (r - 1) * o}{28} + o * (i - \log_2 r)$$

(2.11)

where i=number of input bits, o=number of output bits and r=number of regions By sweeping the above three variables in the model and choosing the optimum combinations, we calculated the corresponding area. Figure 2.10 shows the variation in precision with respect to area. The minimum of all these curves will be derived and considered for our total comparison.

#### 2.3.4 CRI

CRI algorithm requires only adders, comparators and shifters. To calculate the approximation area, Table 2.1 is used.

area = n \* (2 \* adders + 1 \* comparator) + 1 \* comparator = n \* (2.7 \* i) + 0.6 (2.12)

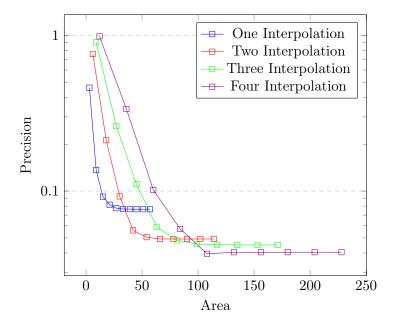

where i=number of input bits, n=number of interpolation By sweeping input bits as well as number of interpolation, Figure 2.11 was plotted.

#### 2.3.5 SPWL+CRI

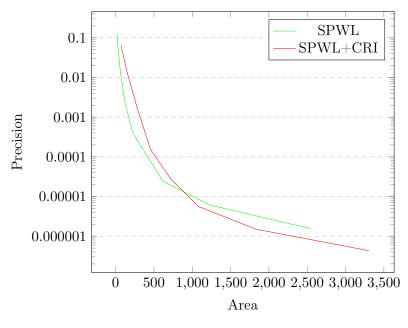

From section 2.3.3, we observed that SPWL is giving best precision. To improve it even further, some computation was added to SPWL. Equation 2.13 was used to calculate its area. Compare to Equation 2.11, the area of ROM is twice (two values are stored for each entry, which are tanh() and delta), as well as that of multiplier (two multipliers are used). The last term denotes the CRI area. We swept the same variables as in the SPWL case, and by selecting the optimum combinations, plotted the area-precision curve in Figure 2.12 and Figure 2.13.

$$area = \frac{6*r*(\log_2 r - 1) + r*o}{28} + 2*o*(i - \log_2 r) + 9*o$$

(2.13)

where i=number of input bits, o=number of output bits and r=number of regions

Figure 2.9: Area vs Precision

## 2.4 Conclusion

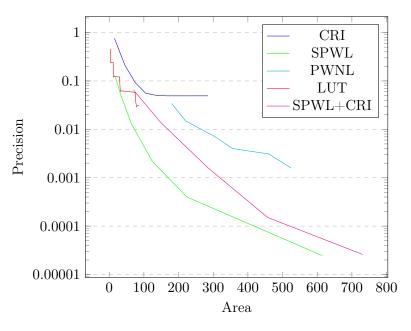

Figure 2.12 shows the behavior of the five implemented methods. It is apparent that, for less number of regions (and consequently less area and error) SPWL is outperforming others but as we go for more regions for instance 256 or 512, SPWL+CRI showed better performance. Figure 2.13 shows this trend. CRI saturates very soon and LUT's size increases dramatically as better precisions are required. For PWNL, the area consumption is the highest and it shows the worst performance, when small area is concerned.

One conclusion that can be taken from this figure, is that LUT alone is not the best solution, especially if precisions better than 0.01 are required. This is because the area of the decoder increases exponentially (Equation 2.10). Therefore, LUT can work well as a primary course approximator, and adding a computational method to its results is highly beneficial. Heavier computations pay off for better precisions. This pattern is seen in Figure 2.13, noting that SPWL+CRI has more computational power compare to SPWL. With this pattern in mind, it is possible that for even better precisions than 0.000001, the PWNL becomes the best alternative among these 5 methods, as it has the most computational power.

Figure 2.10: Comparison of area vs precision with different regions for SPWL

Figure 2.11: Area vs Precision for CRI

Figure 2.12: Comparison of different approximation method

Figure 2.13: SPWL vs SPWL+CRI

# Low Density Parity Check (LDPC)

Chapter 3

### 3.1 Introduction

As the signal is transmitted from the transmitter to the receiver, a lot of noise is added to it. A very basic approach for the receiver to convert the transmitted analog information is to its corresponding bital value is equalizing the signal with the demodulator (rounding the analog signal to the closest defined value, that is mapped to a defined set of bits). Such an approach is called "hard decision". A better approach that is more immune to noise, is adding some extra bits to the signal before transmitting it. Therefore the bital message is coded to a larger message (called codeword) and then, will be transmitted through the channel. As later will be shown, coding highly increases the system's efficiency, meaning that we can achieve a certain Bit Error Rate (BER) with consuming lower power or Signal-to-Noise Ratio (SNR).

Low Density Parity Check (LDPC) is one of the most capable coding schemes that was first introduced by Gallager[16] and has widely been used in telecommunication systems. Among the algorithms to decode LDPC codes, Sum-Product Algorithm (SPA) and Min-Sum Algorithm (MSA) are the most common ones. SPA is focused in this work, where all the bits in the received codeword (which is 5-bit long in Figure 3.1) communicate with each other and detect the mistakes caused by noise and recover the original message (2-bit long in Figure 3.1). This is why SPA is also called Belief Propagation (BP) algorithm. MSA is an efficient approximation of the SPA, normally resulting in inferior accuracy (BER) but more chip area efficiency.

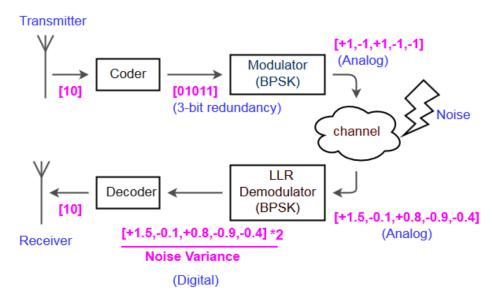

Figure 3.1 shows the overview of a basic wireless system, that is considered in this thesis. Since the focus of the thesis is on the decoder, Binary Phase-Shift Keying (BPSK) modulation/demodulation has been used, which is relatively simple.

### 3.2 Modulation and LLRs

In Figure 3.1, BPSK modulation is used, which, for example, performs the mapping:  $[0,1] \rightarrow [+1,-1]$ . This modulation is called "Living-Zero" modulation, and will be assumed as default in the remaining. The output of the demodulator could be either bits or Log-likelihood Ratio (LLR) values of bits. In the first

Figure 3.1: Overall view of a simple communication system

case, the demodulator equalizes its inputs, by finding the closest bital codeword that the analog signal is most likely representing. This is called "hard decision". The decoder is very easy in this case, as it only maps the found codeword to its corresponding message.

In the second case, which is the case for LDPC codes, the demodulator outputs a LLR value (also called soft-value), corresponding to each bit. The LDPC decoder will use these LLRs to make "soft decisions" on its inputs. In LLR case, the demodulator (Figure 3.1), first detects the phase of the analog input, digitalizes it, and finally converts it into an LLR value. We here show the digitalized input, as variable "u". Equation 3.1 shows how the LLR value of each input (corresponding to one bit) is calculated [17].

$$LLR(u) = \log \frac{P(bit \ 0 \ was \ sent)}{P(bit \ 1 \ was \ sent)}$$

(3.1)

In Equation 3.1, the numerator is the probability that bit '0' was sent, and the denominator is the probability that bit '1' is sent. if the numerator is bigger than the denominator, the LLR becomes positive. therefore, a positive LLR is more likely to represent a '0' rather than '1'. Obviously, unsure transmitted bits have their LLR values closer to 0, as both numerator and denominator are close to each other, in these cases.

The LLR value of a bit is very descriptive, because its sign determines whether the bit is probably '1' or '0', and its magnitude shows how much this probability can be counted on, or how sure that prediction is. For example, an LLR value of "+0.1" means that the actual bit is more likely to be '0', but we are not very sure about that.

The probabilities in Equation 3.1 can easily be calculated, in case of BPSK. If

the channel has white-Gaussian Noise, which is a usual case, Equation 3.2 holds:

$$P(\text{ modulated bit} = x) = \frac{1}{2\pi\sigma^2} * exp[-\frac{(u-x)^2}{2\sigma^2}]$$

(3.2)

Where the modulated bit (x) can be '+1' (in case of bit '0') or '-1' (in case of bit '1'). Equation 3.1 can then be rewritten as Equation 3.3. Therefore, in BPSK case, LLR value production is reduced to a mere multiplication. This is also shown in Figure 3.1.

$$LLR(u) = \log \frac{\frac{1}{2\pi\sigma^2} * exp[-\frac{(u-1)^2}{2\sigma^2}]}{\frac{1}{2\pi\sigma^2} * exp[-\frac{(u+1)^2}{2\sigma^2}]} = \frac{2}{\sigma^2} * u$$

(3.3)

## 3.3 Sum-Product Algorithm (SPA)

LDPC decoder receives a codeword, except that the elements of the codeword are not bits, but Log-likelihood Ratio (LLR) values (please refer to section 3.2). How SPA maps this codeword of LLRs to the correct bital codeword, and later the original message, is discussed in this section.

At the transmitter side, the LDPC coder converts the message to the bital codeword by the binary matrix G, as shown in Equation 3.4, where "c" is the codeword.

$$message * G = c \tag{3.4}$$

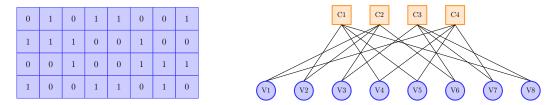

The binary parity-check matrix (H) is used at the decoder, and is a matrix of size M \* N, which is related to G by equation  $G * H^T = 0$ . The number of columns (N) in H equals the size of the codeword, that should be decoded and the number of rows (M) equals the size of the uncoded message. H is a low density matrix in which most elements are '0'. In SPA, each row of H represents a "Check Node (CN)" and each column represents a "Variable Node (VN)", and a '1' in H dictates that the corresponding VN (representing that column) should be connected to the corresponding CN (representing that row). An example of a H matrix with (N=8) VNs and (M=4) CNs, and its corresponding graph is shown in Figure 3.2.

**Figure 3.2:** H matrix(4,8) and its corresponding graph

SPA works as connected CNs and VNs constantly communicate with each other, by sending messages through the connections. Each VN represents a bit in the codeword. First, each VN gets its corresponding LLR in the received codeword, that here we call the VN's *intrinsic LLR*. In the beginning, VNs send their LLRs to their connected CNs. Each CN processes all the messages sent from its connected VNs, and finally predicts a value for each VN. Each VN then gets all these suggested values from its connected CNs, adds them all together and also to its *intrinsic LLR*, and obtains a more precise LLR. This concludes one iteration. If the stop criteria is not met, each VN computes and sends its so-far computed LLR (with little change) to each CN and iterations continue, until the stop criteria is met. As the algorithm proceeds, the computed LLR for each VN gets closer to either '+1' or '-1'.

For notations, if the  $m^{th}$  CN is connected to the  $n^{th}$  VN, the message from that CN to that VN is shown as  $\Lambda_{m \to n}$ , and the message in the opposite direction is  $\lambda_{n \to m}$ . At the beginning of the algorithm, the messages are initialized as follows:

$$\Lambda_{m \to n} = 0, \ \lambda_{n \to m} = u_i \tag{3.5}$$

where U is the codeword, and  $u_n$  is the  $n^{th}$  variable of the codeword (in LLR). Each iteration of the algorithm executes the following three steps [18]:

#### step (i) (CN update)

All the CNs produce their messages to all their connected VNs. If the number of VNs is N, the message from  $m^{th}$  CN to the  $n^{th}$  VN can be computed with different formulas, among which, Equation 3.6 is a good example. Section 3.4 is devoted to elaboration of these different formulas, and covers the general mathematics of Check-Node computation.

$$\Lambda_{m \to n} = 2tanh^{-1} \prod_{n=1, n \neq n'}^{N} tanh[\frac{\lambda_{n' \to m}}{2}]$$

(3.6)

The notation  $(n' \neq n)$  in Equation 3.6 denotes that, to compute the message to a certain VN, the message from all the other connected VNs is taken into account, unless the message that has come from that VN.

#### step (ii) (VN update)

All the VNs produce their messages to all their connected CNs. If the number of CNs is M, The message from  $n^{th}$  VN to the  $m^{th}$  CN is computed according to Equation 3.7.

$$\lambda_{n \to m} = u_n + \sum_{m=1, m \neq m'}^M \Lambda_{m \to n}$$

(3.7)

#### step (iii) (stop criterion)

At each iteration, a more precise codeword is expected to be acheived. The obtained codeword(c) at the end of each iteration is determined as:

$$\forall n, \ c_n = u_n + \sum \Lambda_{m \to n} \tag{3.8}$$

There are many different stop criteria for SPA. One is based on the fact that for each valid codeword 'c',  $H * (\hat{c})^T = 0$ , where  $\hat{c}$  is the transformation of 'c' to a digital codeword, using hard-decision. This condition can be checked at the end of each iteration. Another way is performing parity check at CNs, depending on whether "Even" or "Odd" parity check is used. In case of Even parity check, there should be an "Even" number of '1's (negative LLRs) in the set of variables (VNs) connected to each CN. In this case, each CN can check this condition by first mapping positive entries to '0' and negative entries to '1' and digitally XOR them. If the result is '0', it means there has been an "Even" number of positive entries, and the condition is satisfied. When all the CNs are satisfied, the algorithm stops. Based on the same rule, each CN can multiply all of its incoming LLR messages together. A positive result implies that there has been an even number of negative LLRs among them, and the CN is satisfied. A simpler way of stoping the algorithm is when the algorithm reaches a certain number of iterations, but this could lead to inefficiency in time.

Once the set criteria is met, the already-obtained codeword ('c' which is in LLR) is a defined coodeword and corresponds to a defined message. The codeword 'c' is then transformed to digital codeword (ĉ) using hard-decision. Then, according to Equation 3.4, the corresponding actual message can be calculated as:

$$\hat{c} * G^{-1} = message \tag{3.9}$$

#### 3.4 CN update Methods

#### 3.4.1 $\boxplus$ -based

In this section, the operation of a CN will be covered (please refer to [17] for more elaborate explanations). CN operation is based on the parity-check rule, that is, in case of "Even" parity check, the number of 1's (negative LLRs) in the messages from VNs, must be even. To calculate the message to a given VN, the CN processes the LLRs that it receives from other VNs. Let's assume there is an even number of 1's from other VNs. Thus, it is likely that this VN represents a '0' bit (or a negative LLR). Therefore, CN predicts and sends a negative LLR to this VN. This message will have its share in reducing the so-far predicted LLR of that VN (Equation 3.8), that will be used in next iteration (Equation 3.7). In this way, as algorithm proceeds, wrong LLRs gradually change their signs. If there are N number of VNs connected to a CN, in order for the CN to compute a proper LLR for the  $N^{th}$  variable  $(V_n)$ , Equation 3.10 must be calculated (refer to Equation 3.1 for definition of LLR).

$$\Lambda_{The\ CN\to n} = \log \frac{P(\ correct\ bit\ for\ V_n = 0)}{P(\ correct\ bit\ for\ V_n = 1)} = \log \frac{P("Even"\ no.\ of\ 1's\ in\ other\ VNs)}{P("Odd"\ no.\ of\ 1's\ in\ other\ VNs)}$$

(3.10)

As briefly discussed in 3.3, if a set of digital bits (0,1) get XORed with each other, and the result is '0', it means there has been an "Even" number of '1's in that set. As a result,

$$\Lambda_{m \to N} = ln \frac{P(\hat{u}_1 \oplus \hat{u}_2 \oplus \hat{u}_3 \dots \oplus \hat{u}_{N-1} = 0)}{P(\hat{u}_1 \oplus \hat{u}_2 \oplus \hat{u}_3 \dots \oplus \hat{u}_{N-1} = 1)}$$

(3.11)

For notations,  $\hat{u}_n$  is the correct  $n^{th}$  digital bit of the codeword, and  $\oplus$  is the digital XOR.  $u_n$  is the message received from  $V_n$ , which is  $\lambda_{n \to m}$ .  $LLR(u_n)$  is the LLR form of that message. To calculate the probabilities in Equation 3.11, we need the functionality of digital XOR:

$$P(\hat{u}_1 \oplus \hat{u}_2 = 0) = P(\hat{u}_1 = 1) \cdot P(\hat{u}_2 = 1) + P(\hat{u}_1 = 0) \cdot P(\hat{u}_2 = 0)$$

(3.12)

Also, from Equation 3.2:

$$LLR(u) = \frac{P(\hat{u}=1)}{P(\hat{u}=0)} = \frac{P(\hat{u}=1)}{1 - P(\hat{u}=1)} \to P(\hat{u}=1) = \frac{e^{LLR(u)}}{1 + e^{LLR(u)}}$$

(3.13)

and,

$$P(\hat{u}=0) = 1 - P(\hat{u}=1) = \frac{1}{1 + e^{LLR(u)}}$$

(3.14)

Replacing Equation 3.13 and Equation 3.14 in Equation 3.12 results in:

$$P(\hat{u}_1 \oplus \hat{u}_2 = 0) = \frac{e^{LLR(u_1)}}{1 + e^{LLR(u_1)}} \cdot \frac{e^{LLR(u_2)}}{1 + e^{LLR(u_2)}} + \frac{1}{1 + e^{LLR(u_1)}} \cdot \frac{1}{1 + e^{LLR(u_2)}}$$

(3.15)

With the help of the above equation, and computing  $P(\hat{u}_1 \oplus \hat{u}_2 = 1)$  with the same procedure, we can define and calculate an important double-input function, called Soft-XOR and denoted as  $\boxplus$ :

$$LLR(u_1) \boxplus LLR(u_2) = ln \frac{P(\hat{u}_1 \oplus \hat{u}_2 = 0)}{P(\hat{u}_1 \oplus \hat{u}_2 = 1)} = ln \frac{1 + e^{LLR(u_1)} e^{LLR(u_2)}}{e^{LLR(u_1)} e^{LLR(u_2)}}$$

(3.16)

Soft-XOR ( $\boxplus)$  is associative and commutative, and it can be proved that Equation 3.11 can be computed as:

$$\Lambda_{m \to N} = LLR(u_1) \boxplus LLR(u_2) \boxplus ... LLR(u_{N-1}) = \sum_{j=1}^{j=N-1} \boxplus u_j$$

(3.17)

Thus, the operation of CN can be simply summarized; i.e. to generate the massage to any VN, all the messages coming from "other" VNs have to be Soft-XORed, and the result will be the desired message.

#### 3.4.2 tanh - based

By using advanced mathematics, it can be proven that Equation 3.17 can be rewritten as Equation 3.18 [17].

$$\sum_{j=1}^{j=N} \boxplus u_j = 2tanh^{-1} \prod_{n'=1}^{N} tanh[\frac{\lambda_{n' \to m}}{2}]$$

(3.18)

$\Lambda_{m \to n}$  is then calculated by eliminating  $\lambda_{n \to m}$  from the above equation, which leads to Equation 3.6, which is mentioned in 3.4.

#### 3.4.3 $\Phi$ – based

CN-update step is the hardware-consuming part of the algorithm. Equation 3.6 in its current form requires some multiplications and also some approximators for the tanh and one for  $tanh^{-1}$  function. [7] suggests an efficient way to implement this. Since in most fixed-point hardware implementations, the use of summation is preferred over multiplication [7], and Equation 3.6 can be rewritten to replace the multiplication with summation (by taking advantage of the fact that multiplication is converted to summation in Log-domain). As elaborated in [19], If we define variable  $\lambda_i$  as Equation 3.19 :

$$\lambda_i = \prod_{n' \neq n} tanh[\frac{\lambda_{n' \to m}}{2}] \tag{3.19}$$

Thus:

$$ln(\lambda_i) = \sum_{n' \neq n} ln(tanh[\frac{\lambda_{n' \to m}}{2}])$$

(3.20)

Therefore, the CN-update equation (Equation 3.6) can be rewritten as:

$$\Lambda_{m \to n} = 2tanh^{-1}(exp(\sum_{n' \neq n} ln(tanh[\frac{\lambda_{n' \to m}}{2}])))$$

(3.21)

If function  $\Phi$  is defined as:

$$\Phi = -tanh^{-1}(exp(x)) = -ln(tanh(x)) \tag{3.22}$$

The ultimate  $\Phi$  – based CN-update equation becomes:

$$\Lambda_{m \to n} = \Phi(\sum_{n' \neq n} \Phi[\frac{\lambda_{n' \to m}}{2}]) \tag{3.23}$$

As seen, this equation benefits from multiple summations, instead of multiplications. However, the disadvantage is that  $\Phi$  function is highly non-linear; As it has one infinity on X-axis and another on Y-axis, and the latter one must be properly taken care of. [6] has approximated this function using PWL approximation with 9 lines, and explained the  $\Phi$ -based schematic of the CNU.

#### 3.5 IEEE 802.11n H Matrix

Section 3.3 has described the parity check matrix (H). IEEE 802.11n standard was chosen in order to implement a LDPC decoder, in this work. This section will discuss the H matrix for this standard. There are 12 different H matrixes depending on 3 different codeword block lengths (1944, 1296,648 bits). And each codeword block length can be implemented using 4 different code rates i.e.  $\frac{1}{2}, \frac{2}{3}, \frac{3}{4}, \frac{3}{4}$  $\frac{5}{6}$ , each is suitable for a specific noise level in the communication channel. Figure 3.3 shows a parity check matrix for block length of 1944 bits and code rate of  $\frac{5}{6}$ . As can be seen, the elements of this matrix are numbers, instead of bits (0 or 1). Each number, represents a square matrix of bits (0's or 1's) with size (sub block size) \* (sub block size). For each block length, there is a specific sub-block size. For example, for the block length of 1944, the sub-block size is 81. An element with number "n" specifies that a unity matrix of size 81\*81 (in this case) must be rotated "n" times, and then be put at that location. Right-Rotation means all the elements of each column will be transferred to their right column, and the right-most column comes to the location of the first column (Figure 3.4). Hence, there are 324 check nodes and 1944 variable nodes for Figure 3.3.

|      | 13 | 48 | 80 | 66 | 4  | 74 | $\overline{7}$ | 30 | 76 | 52 | 37 | 60 | _  | 49 | 73 | 31 | 74 | 73 | 23 | _  | 1 | 0 | _ | _ |

|------|----|----|----|----|----|----|----------------|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|

| H -  | 69 | 63 | 74 | 56 | 64 | 77 | 57             | 65 | 6  | 16 | 51 | _  | 64 | _  | 68 | 9  | 48 | 62 | 54 | 27 | _ | 0 | 0 | _ |

| 11 — | 51 | 15 | 0  | 80 | 24 | 25 | 42             | 54 | 44 | 71 | 71 | 9  | 67 | 35 | _  | 58 | _  | 29 | _  | 53 | 0 | _ | 0 | 0 |

|      | 16 | 29 | 36 | 41 | 44 | 56 | 59             | 37 | 50 | 24 | _  | 65 | 4  | 65 | 52 | _  | 4  | _  | 73 | 52 | 1 | _ | _ | 0 |

| Figure 3.3: H matrix | (block length = 1944bits, code rate = $\frac{5}{6}$ | ) |

|----------------------|-----------------------------------------------------|---|

|----------------------|-----------------------------------------------------|---|

| Qu | asi-c | yelle r | H-Mat |   | Size | (4 10 | ,0 10 |                    | 00  |     | 1 | 0 | 0 0 |     | 0 | 1  |

|----|-------|---------|-------|---|------|-------|-------|--------------------|-----|-----|---|---|-----|-----|---|----|

| 0  | 2     | 0       | 1     | 4 | 3    | 7     | 2     |                    | 0 0 |     | 0 |   |     | 0 0 | 0 | 1  |

|    |       |         |       |   |      |       |       | N                  | 0 0 | 0 ( | 0 | 0 | 1   | 0 0 | 0 | 1  |

| 8  | 9     | 5       | 6     | 1 | 7    | 2     | 5     | N                  | 0 ( |     |   |   |     | 0   |   | 1  |

|    |       |         |       |   |      |       | -     | - `, I             | 0 ( | 0 ( | 0 | 0 | 0 ( | ) 1 | 0 | U, |

| 4  | 3     | 0       | 5     | 0 | 6    | 9     | 0     | 1                  | 0   | 0 0 | 0 | 0 | 0   | 0 0 | 1 |    |

|    |       |         |       | - | -    |       |       |                    | 0 0 | 0 ( | 0 | 0 | 0 0 | 0 0 | 0 | •  |

| 5  | 9     | 1       | 4     | 2 | 3    | 6     | 5     |                    | 1   | 0 0 | 0 | 0 | 0   | 0 0 | 0 |    |

| _  |       |         |       |   |      |       |       | л , <mark>,</mark> | 0 1 | 1 0 | 0 | 0 | 0   | 0 0 | 0 | 1  |

Figure 3.4: Right Rotation

Let's assume H is cyclic entry in a H matrix and sub block size is 81 bits. So, in case of 0 for the first element, we have path from variable node to check node like  $[VN_1 \rightarrow CN_1, VN_2 \rightarrow CN_2, ..., VN_{81} \rightarrow CN_{81}]$ . But in case of a rotation according to values in H matrix, from Figure 3.3, first element is 13. After cyclic shifts we get new path from variable node to check node like  $[VN_1 \rightarrow CN_{14}, VN_2 \rightarrow CN_{15}, ..., VN_{81} \rightarrow CN_{13}]$ . An entry of "-" in H matrix means those variable nodes are not connected to any check nodes. For instance, in Figure 3.3 first row and 24th column is "-", means last 81 variables are not connected anywhere. To handle this routing, we need a permutation network that will route incoming information to correct variable nodes and check nodes.

## 3.6 Conclusion

Evaluating these three popular CN computation methods from hardware perspective, one can argue that  $\phi$  function has two infinities, which make the PWL approximation quite costly. Also, the the tanh *-based* method requires a lot of multipliers, that are expensive in fixed-point hardwares. Therefore, the  $\boxplus$ -based method was selected as the most hardware-friendly one among these three methods, as it requires the approximation of the  $\boxplus$  function, which does not have any infinities, and its approximation can be simplified, as will be illustrated in the next chapter.

# Approximation of ⊞ function

Chapter 4

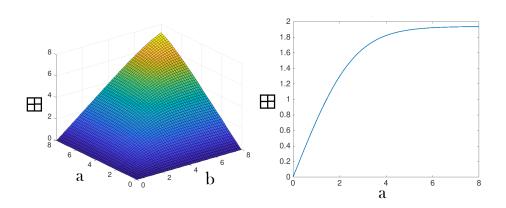

As discussed in section 3.4.1,  $\boxplus$  can be a core function for CN calculation, and for its hardware simplicity, it was chosen over the other computation schemes, in this work. The equation of this double-input function is described in Equation 4.1, and is plotted in Figure 4.1.

$$a \boxplus b = ln \frac{1 + e^a e^b}{e^a e^b} \tag{4.1}$$

Figure 4.1: soft XOR function

In Figure 4.1, the figure on the left shows the  $\boxplus$  when the inputs are swept from 0 to +8. The figure on the right is basically an intersection of the left figure, where "b" is set at the constant value of "2".

Equation 4.1 can be made simpler to approximate by some mathematical manipulations, and can be rewritten as Equation 4.2 [20]

$$a \boxplus b = sign(a)sign(b)Min^*(|a|, |b|)$$

(4.2)

where,

$$Min^{*}(a,b) = min(a,b) - ln(1 + e^{-|a-b|}) + ln(1 + e^{-|a+b|})$$

(4.3)

In this way, the sign calculation (which requires a simple digital XOR) can be departed from the absolute (magnitude) calculation, which is done by  $Min^*$ function.  $Min^*$  takes the absolutes of both inputs and generates the absolute of the result. It is worth noting that for positive inputs:  $\boxplus = Min^*$ . For simplicity, from now on we only consider positive inputs, where this condition holds. The remaining of this section is dedicated to different approximations of Equation 4.3.

## 4.1 Min-Sum Approximation

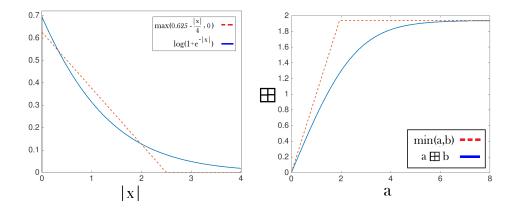

Equation 4.3 has three terms. The first term (min(a, b)) contains the largest portion of the total function of  $Min^*$ . In Figure 4.2, the right figure shows this term and its closeness to the complete function. Therefore, this term can be an approximation of the  $Min^*$  function, and the LDPC decoding algorithm that is based on such approximation is called Min-Sum Algorithm (MSA). This algorithm is very popular, especially for its small cost.

## 4.2 Double-PWL Approximation

In applications where more precision is required, the approximation of the second and third term of Equation 4.3 is also considered. For both these terms, the approximation of the function  $ln(1 + e^{-|x|})$  is required. The left figure in Figure 4.2 is approximating this function, using PWL with one single line (Equation 4.4) [5].

$$ln(1+e^{-|x|}) \sim max(0.625 - \frac{|x|}{4}, 0)$$

(4.4)

Figure 4.2: Soft XOR Approximation

#### 4.3 Single-PWL Approximation

In order to reduce hardware cost but maintain precision, this approximation is based on considering only the first and second term of Equation 4.3 and the last term can be ignored, and the error will not be considerable [22][20]. The reason for ignoring the third term is that for (a + b) > 2.5,  $log(1 + e^{-(a+b)}) \sim 0$ , and therefore this equation only has value for small values of "a" and "b". Also, in our C++ simulations that deals a normal range of -8 < a, b < 8, it was observed that small values barely have an effect on the overall result. However, in some applications that deal with small LLRs (probably where Noise variance  $(\sigma^2)$  is considerably high as shown in Equation 3.3), ignoring this equation might deteriorate the performance. Therefore, Equation 4.3 can be approximated as:

$$Min^{*}(a,b) = min(a,b) - max(0.625 - \frac{|a-b|}{4},0)$$

(4.5)

where |a - b| is in fact max(a, b) - min(a, b) in hardware implementation.

#### 4.4 CRI-based Approximation

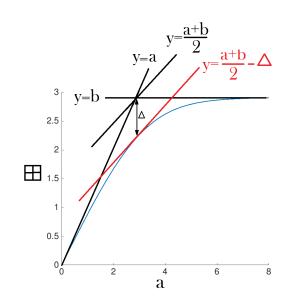

In this method, we utilized the CRI technique (discussed in 2.3.4) to estimate the  $Min^*$  function. Here, we have used a single-step CRI (q = 1). For this, two lines that are tangent to the original curve are needed as initial approximation, plus a suitable  $delta(\Delta)$ . As the initial tangent lines, we can use y = a and y = b. Figure 4.6 shows the original curve, and these two lines. The approximated curve is shown in Equation 4.6.

$$Min^*(a,b) = min(a,b,\frac{a+b}{2} - \Delta)$$

(4.6)

The calculation of  $\Delta$  is explained as follows. As seen in Figure 4.6,  $\Delta$  is the difference between the intersection of the two lines and the original curve, where a = b. According to Equation 4.3, this difference is:

$$\Delta = \ln(1+e^0) - \ln(1+e^{-(a+b)}) \tag{4.7}$$

for (a + b) > 2.5,  $log(1 + e^{-(a+b)}) \sim 0$ . As discussed in the above section, this term can be ignored, without considerable loss of accuracy. Therefore,  $\Delta$  is estimated as:

$$\Delta \sim 0.625 \tag{4.8}$$

As Figure 4.6 shows,  $\Delta = 0.625$  makes the  $\frac{a+b}{2} - \Delta$  line to be tangent to the original curve, at a = b point. As illustrated in section 2.3.4,  $\Delta$  can be quite flexible, and can be lowered by some small amount, so that the  $\frac{a+b}{2} - \Delta$  line passes through the original curve, instead of being tangent to it. Through MATLAB simulations, it was observed that instead of  $\Delta = 0.625$ , using 0.8 or 0.9 results in better accuracy. Therefore, the  $Min^*$  is estimated as Equation 4.9. It is worth to note that in this equation, the absolute function will not be implemented

Figure 4.3: CRI-based approximation of Soft-XOR (b=3)

in hardware, as negative values become naturally large, as the MSB bit becomes '1'.

$$Min^{*}(a,b) = min(a,b, |\frac{a+b}{2} - 0.8|)$$

(4.9)

In [23], the  $Min^*$  equation is estimated as Equation 4.10 which, if rewritten in a more hardware-friendly form, resembles Equation 4.9, with some modifications.

$$Min^{*}(a,b) = max(min(a,b) - max(0.9 - \frac{|a-b|}{2},0),0)$$

(4.10)

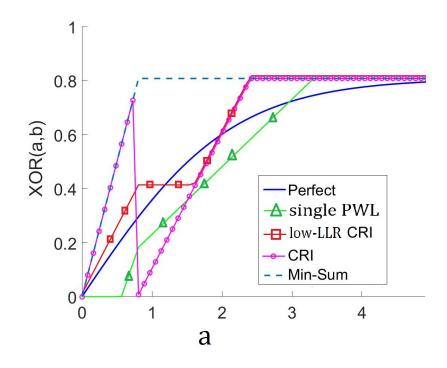

Finally, For those applications in which LLR values are considerably small (probably because of high Noise Variance), ignoring the  $log(1+e^{-(a+b)}) \sim 0$  might deteriorate the performance. In those applications, this term can be approximated with a single line (Equation 4.4) and  $\Delta \sim min(0.8, \frac{a+b}{4}) \sim min(0.8, \frac{max(a,b)}{2})$  can be achieved (denoted as Low-LLR CRI). Its hardware implementation consumes slightly more area than Equation 4.9, but approximates the small LLRs more accurately. In this work, we will regard Equation 4.9 as the CRI approximation.

## 4.5 Result and Conclusion

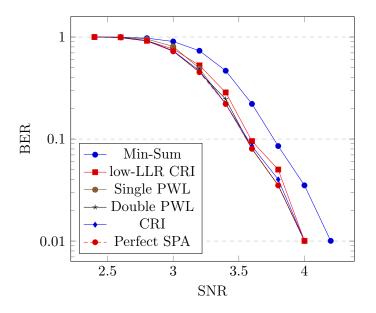

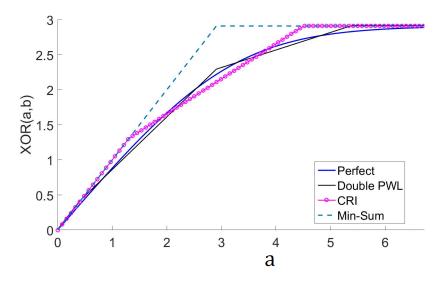

Five common methods to approximate the  $\boxplus$  function have been explored. Figure 4.5 and Figure 4.6 depict these approximations for large LLRs and small LLRs, respectively. The simulation result of BER/SNR of the LDPC decoder is shown in Figure 4.4, for each of these approximations. In this picture, SPA denotes the exact SPA algorithm. Figure 4.4 shows the approximations for different ranges. in

Figure 4.4: SNR vs BER for different soft-xors

Figure 4.5: Soft-xor approximations for large LLR ranges (b=3). Single-PWL, Double-PWL and low-LLR CRI all work identically.

low LLRs, CRI version performs only slightly better than "Min-Sum", but in large LLRs, behaves almost similar to Double-PWL. The RTL results of the approximations are also provided in chapter 7. "min-sum" has the worst performance but smallest area, as it uses only one comparator. However, simulations show that as soon as some computations are added to Min-Sum, its performance starts to

**Figure 4.6:** Soft-xor approximations for small LLR ranges (b=0.8). Double PWL works almost identical to low-LLR CRI.

rapidly improve and become very close to SPA, which suggest that SPA algorithm is highly robust to inaccuracies, and rough estimations perform very well. It can be seen that all the mentioned approximation methods demonstrate an excellent performance in regard of accuracy, except for "Min-Sum". Thus, when it comes to adding computations to  $\boxplus$ , the cost must be the main concern. CRI-based method manages to add the smallest computation, and there is a decrease of 62% in BER of the "CRI-based" with offset 0.8, compare to "Min-Sum". We have tried two different version of CRI-based approximation with different offsets, and offset of "0.8" is more optimal. Overall, it can be seen that the CRI-based  $\boxplus$  approximation, with relatively small area consumption, is a suitable choice for applications in which a near-SPA BER/SNR is required. "Min-Sum" based  $\boxplus$  is the best candidate where hardware cost is the primary concern. As the final note, it was shown that although PWL was determined as the most efficient approximation method in chapter 2, but in soft-xor case, CRI outperformed PWL, which illustrates that the efficient approximation depends on the type of the function, as well. Soft-xor is a double-input function and does not require high accuracies. Also, its special mathematics made it possible to be approximated in more area-efficient ways than using LUT or PWL.

# \_\_\_\_<sub>Chapter</sub> 5 Simulation Results

In this chapter we will discuss and analyze the SPA behavior (BER/SNR) and its dependency on the number of iterations and number of bits (quantization). The analysis is based on a C++ simulator that is formerly developed to simulate a complete SPA decoder with flooding schedule. It takes its inputs from a BPSK demodulator, and computes the decoded bital message and then calculates its corresponding BER versus SNR (BER/SNR).

## 5.1 Effect of iterations on BER

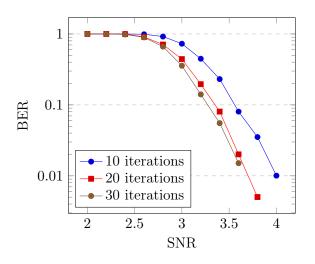

This section is about how number of iterations are effecting decoding performance. Figure 5.1 shows that we can get same BER performance by increasing iterations at low SNR and there is reduction in BER as iterations increases. This was expected because with every iteration received input route between variable node and check node, which decrease the error. However, using high number of iterations for simulation might not very efficient because simulation time would increase very much. But in hardware this would done very fast. Therefore, to reduce simulation time, number of iterations are kept to 10 for other simulations. In RTL design number of iterations is used as stopping criteria.

## 5.2 Effect of total bits on BER for SPA

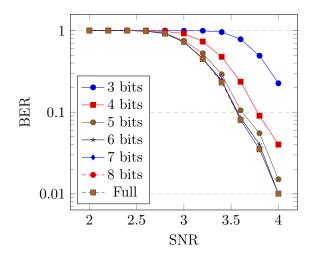

This section describes the effect of total bits of variables on bit error rate. Figure 5.2 shows our simulated results. It is obvious that as we decrease number of bits error would increase because much information can lost in those bits. From simulation we found that only two number of integer bits are enough to represent LLR integer parts. Therefore, in all curves integer bits were kept same while fractional bits were varying. As SPA is memory hungry, so even an increase of single bit is very expensive. Finding a good number of bits that can give reasonable decoding performance is required. In Figure 5.2 first curve is giving worst performance because of very less number of information bits. But as we increase information bits, the BER would improve. However, after 4 information bits there is not much improvement. And "*Full*" curve is without any fixed point limitation. Through this figure it can be seen that BER for 8 information bits are almost equivalent to

Figure 5.1: SNR vs BER for different iterations

full precision.

Figure 5.2: SNR vs BER, for different number of bits

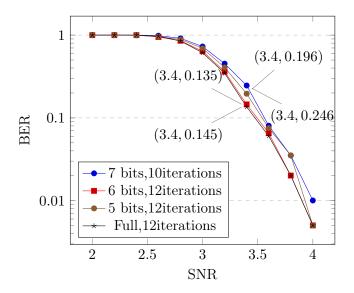

In Section 5.1, we discussed about impact of iterations on BER. As we know by increasing iterations, BER will decrease but on the other hand the total time of decoding would also increase. Hence there is a trade-off between iterations and decoding time. Figure 5.3 compares different number of iterations with different number of bits. In this figure, for an instance at 3.4 SNR first case which is 7 bits and 10 iterations has a BER of 0.246. But an increase of iterations by 2 and decrease of bits by 2 gave better result. By doing so, BER was decreased from 0.246 to 0.196, which means a decrement of 0.05. However, decoding time is increased but we save 2 bits and this has major effect on memory requirement. Total memory required is  $(7776 * NOF\_BITS)$  bits. If we would have chosen 7 bits and 10 iterations, then our memory size would be of 54432 bits. But for 5 bits and 12 iterations, memory size required is 38880 bits. Our net memory saving is around 15.5K bits. As this save is only for one RAM and we have 4 RAMs, so net save would be 68K bits which is quite high. If even low BER is a requirement then 6bits with 12 iterations would also be a reasonable selection. This has a quite close performance to the ideal case. Therefore, from this we can conclude that an increase of 20% in iteration and decrease of 28% in bits would reduce the memory size by 28% for one RAM. Now if we compare 6 bits, 12 iterations and 5 bits, 12 iterations, memory size is decrease by 20% while BER is increase by 25%.

Figure 5.3: Comparison of SNR vs BER for different bits and iterations

## 5.3 Number Representation

Among the three popular numeric systems, that are fixed-point, floating point (FP) and logarithmic (LNS), the fixed-point has been selected in this work, and all the simulations, approximations and hardware implementations are based on that. There are two reasons that FP and LNS were not selected for SPA application:

#### 5.3.1 SPA's Incompatibility with FP and LNS

LNS and FP provide higher accuracy for representing low values, but lower accuracy for larger values. However, as shown in Figure 4.4 and Figure 4.6 in chapter 4, the Soft-XOR approximations that exhibit low accuracy for estimating small values perform as adequately as others, but those that estimate large values with low accuracy, perform poorly in BER/SNR performance. This illustrates that

large values are more important for CN computation of SPA (at least for our case study with normal noise level). Therefore, LNS and also FP behave in the opposite direction of the accuracy of SPA. However, a number representation that is inverse of LNS could work in favor of the mentioned property of SPA. For example, in such a numeric system, 3 is represented by 8 if the base is 2. Exploration of this system remains for future work.

#### 5.3.2 Difficult Addition in FP and LNS

Another limitation on FP, LNS and it's inverse is the VNU. VNU's main task is addition, which is relatively difficult for any numeric system other than fixed-point. For LNS and its inverse, one way is that some hardware is added to the I/Os of all CNUs to act as converters to/from fixed-point. Therefore, VNU handles fixedpoint additions and will be small. For LNS, the added hardware has to perform logarithm to all inputs and inverse-logarithm to all outputs of CNUs. Another way is performing addition without such converters, which is much larger than fixed-point addition.

## \_\_\_\_\_<sub>Chapter</sub> 6 Hardware Architecture

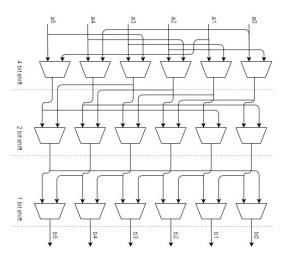

This chapter describes the SPA ASIC architecture of flooding LDPC decoder. The overall architectures were designed to be compatible with any IEEE 802.11n code rates. IEEE 802.11n has three different codeword block length of 1944, 1296, 648 bits and each block length has four different code rate i.e  $\frac{1}{2}$ ,  $\frac{2}{3}$ ,  $\frac{3}{4}$ ,  $\frac{5}{6}$ . The difference between these block lengths is number of variables and number of entries in their respectively H matrix. In case of large codeword block length, the memory bandwidth increases and vice-versa. For 648 bits block length, sub block size is 27 bits, for 1296 bits sub block size is 54 bits and for 1944 bits sub block size is 81 bits. However, the increase in sub block size is a multiple of 3, this symmetry can be utilized in design of a configurable hardware for all block lengths. However, the memory overhead leads to a trade-off situitation, while designing a configurable LDPC decoder, because of large sub-block sizes. For instance in case of 1944 bits block length, if we process one entry from H matrix at a time, then the incoming data will be 81 \* NOF BITS bits, where NOF BITS = number of bits of a *variable.* So, for *NOF* BITS = 7 (which is a usual case), it requires a memory with a width of of 567-bits, which is quite large and inefficient. Also, the speed of decoding is dependent on how many entries in H matrix we process at a time. If we process more than one entry at a time, then memory bandwidth would increase accordingly. These problems needs to be tackled properly, in order to design an efficient LDPC decoder.

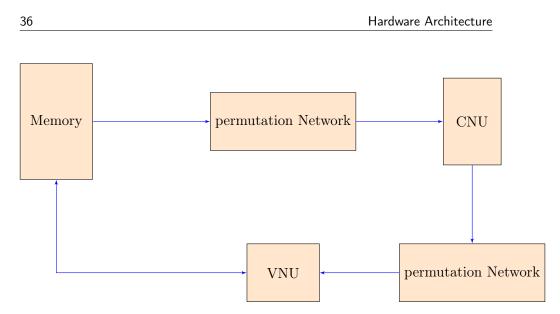

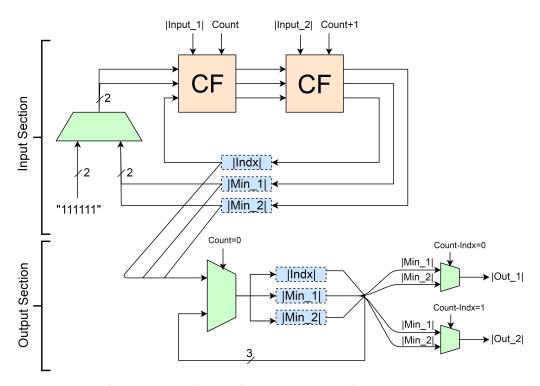

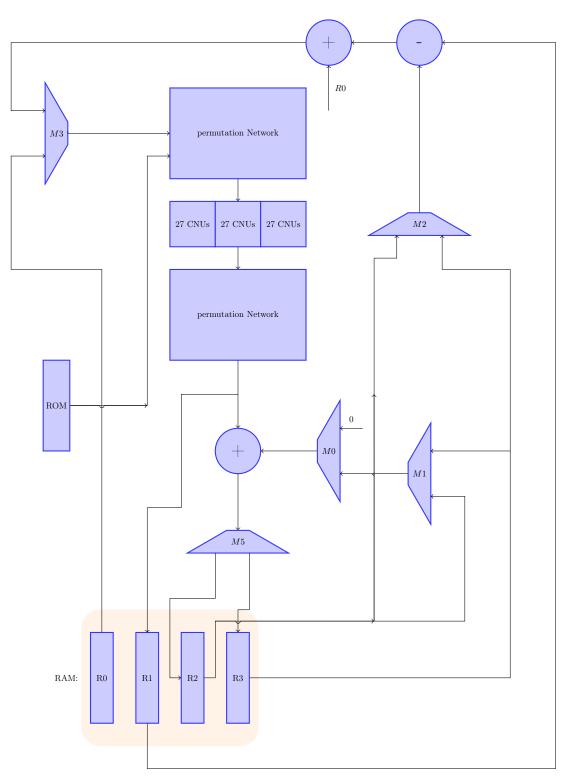

Therefore, we decided to divide a RAM into three parts, each one with a width of  $27 * NOF\_BITS$  bits. More detail explanation can be found in memory section below. Figure 6.1 shows the top level architecture of a LDPC decoder based on SPA. RAMs and ROM are used to store all the necessary information. Permutation network will perform cyclic shift of incoming variables based on entries in a particular H matrix. CNU is the Check Node Unit, which updates all the incoming information coming from variable nodes. Similarly VNU is Variable Node Unit which update all the incoming variables. Detailed explanation of every block in Figure 6.1 is described below.

## 6.1 CNU Implementation

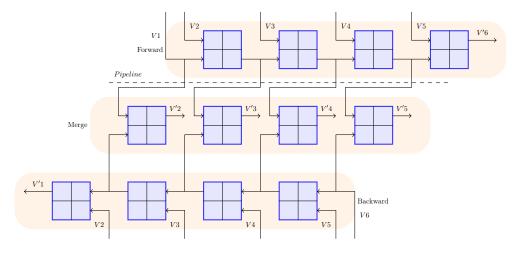

Check Node Update unit is the major processing unit as described in section 3.4. To implement the SPA CNU in hardware, a forward-backward [18] ap-

Figure 6.1: Top level architecture