# ADSP-21160 SHARC® DSP Instruction Set Reference

Revision 2.1, April 2013

Part Number 82-001967-01

Analog Devices, Inc. One Technology Way Norwood, Mass. 02062-9106

## **Copyright Information**

© 2013 Analog Devices, Inc., ALL RIGHTS RESERVED. This document may not be reproduced in any form without prior, express written consent from Analog Devices, Inc.

Printed in the USA.

#### Disclaimer

Analog Devices, Inc. reserves the right to change this product without prior notice. Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use; nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under the patent rights of Analog Devices, Inc.

#### Trademark and Service Mark Notice

The Analog Devices logo, Blackfin, SHARC, TigerSHARC, CrossCore, VisualDSP++, and EZ-KIT Lite are registered trademarks of Analog Devices, Inc.

All other brand and product names are trademarks or service marks of their respective owners.

# **Contents**

## **PREFACE**

|   | Purpose of This Manual xi          |

|---|------------------------------------|

|   | Intended Audience x                |

|   | Manual Contents xii                |

|   | What's New in This Manual xiii     |

|   | Technical Supportxiv               |

|   | Supported Processors xv            |

|   | Product Informationxv              |

|   | Analog Devices Web Sitexvi         |

|   | EngineerZone xv                    |

|   | Notation Conventionsxvii           |

|   | Register Diagram Conventions xviii |

| Ι | NSTRUCTION SUMMARY                 |

|   | Chapter Overview                   |

|   | Development Tools                  |

|   | Compute and Move/Modify Summary    |

|   | Program Flow Control Summary       |

|   | Immediate Move Summary             |

|   |                                    |

| Miscellaneous Operations Summary                   | 1-9  |

|----------------------------------------------------|------|

| Register Types Summary                             | 1-10 |

| Memory Addressing Summary                          | 1-16 |

| Instruction Set Notation Summary                   | 1-17 |

| Conditional Execution Codes Summary                | 1-20 |

| SISD/SIMD Conditional Testing Summary              | 1-22 |

| Instruction Opcode Acronym Summary                 | 1-23 |

| Universal Register Codes                           | 1-28 |

| ADSP-21160 Instruction Opcode Map                  | 1-33 |

| COMPUTE AND MOVE                                   |      |

| Group I Instructions                               | 2-1  |

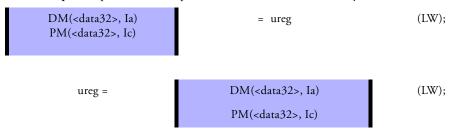

| Type 1: Compute, Dreg«···»DM   Dreg«···»PM         | 2-3  |

| Type 2: Compute                                    | 2-7  |

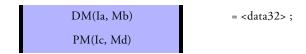

| Type 3: Compute, ureg«···»DM   PM, register modify | 2-9  |

| Type 4: Compute, dreg«···»DM   PM, data modify     | 2-14 |

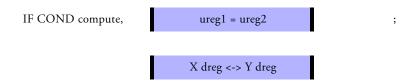

| Type 5: Compute, ureg«····»ureg   Xdreg<->Ydreg    | 2-19 |

| Type 6: Immediate Shift, dreg«···»DM   PM          | 2-23 |

| Type 7: Compute, modify                            | 2-28 |

| PROGRAM FLOW CONTROL                               |      |

| Group II Instructions                              | 3-1  |

| Type 8: Direct Jump   Call                         | 3-3  |

| Type 9: Indirect Jump   Call, Compute              | 3-8  |

| Type 10: Indirect Jump   Compute, dreg«····»DM     |      |

| Type 11: Return From Subroutine   Interrupt, Compute 3-19 |

|-----------------------------------------------------------|

| Type 12: Do Until Counter Expired                         |

| Type 13: Do Until                                         |

| IMMEDIATE MOVE INSTRUCTIONS                               |

| Group III Instructions                                    |

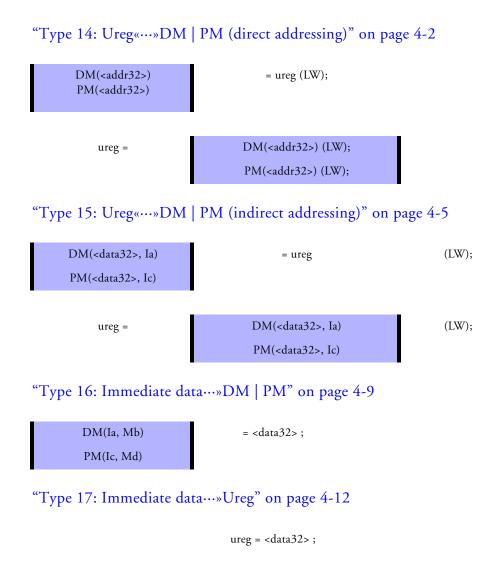

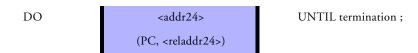

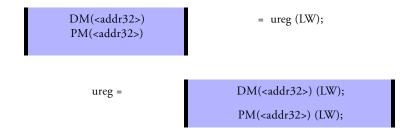

| Type 14: Ureg«···»DM   PM (direct addressing) 4-2         |

| Type 15: Ureg«···»DM   PM (indirect addressing) 4-5       |

| Type 16: Immediate data···»DM   PM                        |

| Type 17: Immediate data···»Ureg                           |

| MISCELLANEOUS OPERATIONS                                  |

| Group IV Instructions                                     |

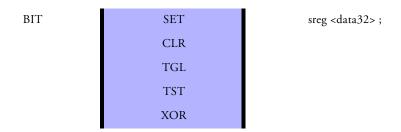

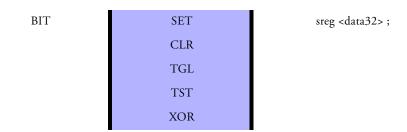

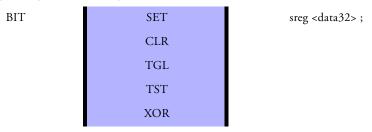

| Type 18: System Register Bit Manipulation 5-2             |

| Type 19: I Register Modify   Bit-Reverse                  |

| Type 20: Push, Pop Stacks, Flush Cache                    |

| Type 21: Nop                                              |

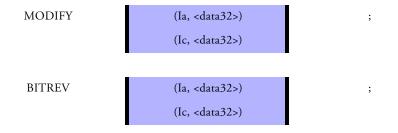

| Type 22: Idle                                             |

| Type 25: Cjump/Rframe 5-13                                |

| COMPUTATIONS REFERENCE                                    |

| Compute Field                                             |

| ALU Operations                                            |

| Fixed-Point ALU Operations                                |

| Floating-Point ALU Operations                             |

| $Rn = Rx + Ry \qquad$         | . 6-7 |

|-------------------------------|-------|

| Rn = Rx - Ry                  | . 6-8 |

| Rn = Rx + Ry + CI             | . 6-9 |

| $Rn = Rx - Ry + CI - 1 \dots$ | 6-10  |

| $Rn = (Rx + Ry)/2 \dots$      | 6-11  |

| COMP(Rx, Ry)                  | 6-12  |

| COMPU(Rx, Ry)                 | 6-13  |

| Rn = Rx + CI                  | 6-14  |

| $Rn = Rx + CI - 1 \dots$      | 6-15  |

| $Rn = Rx + 1 \dots$           | 6-16  |

| $Rn = Rx - 1 \dots$           | 6-17  |

| Rn = -Rx                      | 6-18  |

| Rn = ABS Rx                   | 6-19  |

| Rn = PASS Rx                  | 6-20  |

| $Rn = Rx \ AND \ Ry $         | 6-21  |

| Rn = Rx OR Ry                 | 6-22  |

| Rn = Rx XOR Ry                | 6-23  |

| Rn = NOT Rx                   | 6-24  |

| Rn = MIN(Rx, Ry)              | 6-25  |

| Rn = MAX(Rx, Ry)              | 6-26  |

| Rn = CLIP Rx BY Ry            | 6-27  |

| $Fn = Fx + Fy \dots$          | 6-28  |

| $Fn = Fx - Fy \dots$          | 6-29  |

| Fn = ABS (Fx + Fy)            | 6-30  |

| Fn = ABS (Fx - Fy)                                                       | 6-31 |

|--------------------------------------------------------------------------|------|

| $Fn = (Fx + Fy)/2 \qquad$                                                | 6-32 |

| COMP(Fx, Fy)                                                             | 6-33 |

| Fn = -Fx                                                                 | 6-34 |

| Fn = ABS Fx                                                              | 6-35 |

| Fn = PASS Fx                                                             | 6-36 |

| Fn = RND Fx                                                              | 6-37 |

| Fn = SCALB Fx BY Ry                                                      | 6-38 |

| Rn = MANT Fx                                                             | 6-39 |

| Rn = LOGB Fx                                                             | 6-40 |

| Rn = FIX Fx<br>Rn = TRUNC Fx<br>Rn = FIX Fx BY Ry<br>Rn = TRUNC Fx BY Ry | 6-41 |

| Fn = FLOAT Rx BY Ry Fn = FLOAT Rx                                        | 6-43 |

| Fn = RECIPS Fx                                                           | 6-44 |

| Fn = RSQRTS Fx                                                           | 6-46 |

| Fn = Fx COPYSIGN Fy                                                      | 6-48 |

| Fn = MIN(Fx, Fy)                                                         | 6-49 |

| Fn = MAX(Fx, Fy)                                                         | 6-50 |

| Fn = CLIP Fx BY Fy                                                       | 6-51 |

| Multiplier Operations                                                                                      | 6-52 |

|------------------------------------------------------------------------------------------------------------|------|

| Multiplier Fixed-Point Operations                                                                          | 6-53 |

| Multiplier Floating-Point Operations                                                                       | 6-54 |

| Mod1 and Mod2 Modifiers                                                                                    | 6-54 |

| Rn = Rx * Ry mod2<br>MRF = Rx * Ry mod2<br>MRB Rx * Ry mod2                                                | 6-56 |

| Rn = MRF + Rx * Ry mod2<br>Rn = MRB + Rx * Ry mod2<br>MRF = MRF + Rx * Ry mod2<br>MRB = MRB + Rx * Ry mod2 | 6-57 |

| Rn = MRF – Rx * Ry mod2<br>Rn = MRB – Rx * Ry mod2<br>MRF = MRF – Rx * Ry mod2<br>MRB = MRB – Rx * Ry mod2 | 6-58 |

| Rn = SAT MRF mod1<br>Rn = SAT MRB mod1<br>MRF = SAT MRF mod1<br>MRB = SAT MRB mod1                         | 6-59 |

| Rn = RND MRF mod1<br>Rn = RND MRB mod1<br>MRF = RND MRF mod1<br>MRB = RND MRB mod1                         | 6-60 |

| MRF = 0 $MRB = 0$                                                                                          | 6-61 |

| MRxF/B = Rn/Rn = MRxF/B                                                                                    | 6-62 |

| Fn = Fx * Fv                                                                                               | 6-64 |

| Shifter Operations                                                                   | 6-64 |

|--------------------------------------------------------------------------------------|------|

| Shifter Opcodes                                                                      | 6-64 |

| Rn = LSHIFT Rx BY Ry<br>Rn = LSHIFT Rx BY <data8></data8>                            | 6-66 |

| Rn = Rn OR LSHIFT Rx BY Ry Rn = Rn OR LSHIFT Rx BY <data8></data8>                   | 6-67 |

| Rn = ASHIFT Rx BY Ry Rn = ASHIFT Rx BY <data8></data8>                               | 6-68 |

| Rn = Rn OR ASHIFT Rx BY Ry Rn = Rn OR ASHIFT Rx BY <data8></data8>                   | 6-69 |

| Rn = ROT Rx BY Ry Rn = ROT Rx BY <data8></data8>                                     | 6-70 |

| Rn = BCLR Rx BY Ry Rn = BCLR Rx BY <data8></data8>                                   | 6-71 |

| Rn = BSET Rx BY Ry<br>Rn = BSET Rx BY <data8></data8>                                | 6-72 |

| Rn = BTGL Rx BY Ry Rn = BTGL Rx BY <data8></data8>                                   | 6-73 |

| BTST Rx BY Ry BTST Rx BY <data8></data8>                                             | 6-74 |

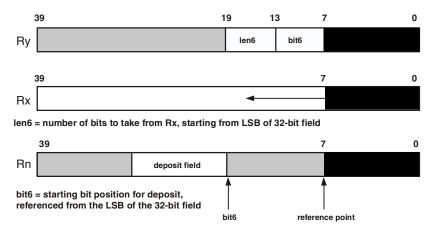

| Rn = FDEP Rx BY Ry Rn = FDEP Rx BY <bit6>:<len6></len6></bit6>                       | 6-75 |

| Rn = Rn OR FDEP Rx BY Ry Rn = Rn OR FDEP Rx BY <bit6>:<len6></len6></bit6>           | 6-77 |

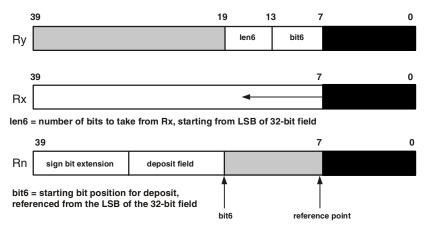

| Rn = FDEP Rx BY Ry (SE)<br>Rn = FDEP Rx BY <bit6>:<len6> (SE)</len6></bit6>          | 6-79 |

| Rn = Rn OR FDEP Rx BY Ry (SE) Rn = Rn OR FDEP Rx BY <bit6>:<len6> (SE)</len6></bit6> |      |

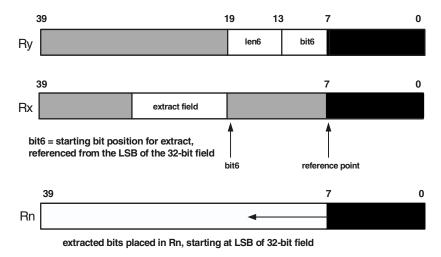

| Rn = FEXT Rx BY Ry Rn = FEXT Rx BY <bit6>:<len6></len6></bit6>              | 6-83  |

|-----------------------------------------------------------------------------|-------|

| Rn = FEXT Rx BY Ry (SE)<br>Rn = FEXT Rx BY <bit6>:<len6> (SE)</len6></bit6> | 6-85  |

| Rn = EXP Rx                                                                 | 6-87  |

| Rn = EXP Rx (EX)                                                            | 6-88  |

| Rn = LEFTZ Rx                                                               | 6-89  |

| Rn = LEFTO Rx                                                               | 6-90  |

| Rn = FPACK Fx                                                               | 6-91  |

| Fn = FUNPACK Rx                                                             | 6-92  |

| Multifunction Computations                                                  | 6-93  |

| Operand Constraints                                                         |       |

| Parallel Add and Subtract                                                   | 6-95  |

| Parallel Multiplier and ALU                                                 | 6-98  |

| Parallel Multiplier With Add and Subtract                                   | 6-101 |

## **INDEX**

# **PREFACE**

Thank you for purchasing Analog Devices SHARC® digital signal processor (DSP).

# **Purpose of This Manual**

The ADSP-21160 SHARC DSP Instruction Set Reference provides assembly syntax information for the ADSP-21160 Super Harvard Architecture (SHARC) Digital Signal Processor (DSP). The syntax descriptions cover instructions that execute within the DSP's processor core (processing elements, program sequencer, and data address generators). For architecture and design information on the DSP, see *ADSP-21160 SHARC DSP Hardware Reference*.

## Intended Audience

The primary audience for this manual is a programmer who is familiar with Analog Devices processors. The manual assumes the audience has a working knowledge of the appropriate processor architecture and instruction set. Programmers who are unfamiliar with Analog Devices processors can use this manual, but should supplement it with other texts, such as hardware and programming reference manuals that describe their target architecture.

## **Manual Contents**

This reference presents instruction information organized by the type of the instruction. Instruction types relate to the machine language opcode for the instruction. On this DSP, the opcodes categorize the instructions by the portions of the DSP architecture that execute the instructions. The following chapters cover the different types of instructions.

- "Instruction Summary" on page 1-1 This chapter provides a syntax summary of all instructions and describes the conventions that are used on the instruction reference pages.

- "Compute and Move" on page 2-1 These instruction specify a compute operation in parallel with one or two data moves or an index register modify.

- "Program Flow Control" on page 3-1 These instructions specify various types of branches, calls, returns, and loops. Some may also specify a compute operation and/or a data move.

- "Immediate Move Instructions" on page 4-1 These instructions use immediate instruction fields as operators for addressing.

- "Miscellaneous Operations" on page 5-1 These instructions include bit modify, bit test, no operation, idle, and cache manipulation.

- "Computations Reference" on page 6-1 This chapter describes computation and multifunction computation operations that are available within many instructions' opcodes through a COMPUTE field that specifies a compute operation using the ALU, multiplier, or shifter.

Each of the DSP's instructions is specified in this text. The reference page for an instruction shows the syntax of the instruction, describes its function, gives one or two assembly-language examples, and identifies fields of its opcode. The instructions are referred to by type, ranging from 1 to 25.

These types correspond to the opcodes that ADSP-21160 DSPs recognize, but are for reference only and have no bearing on programming.

Some instructions have more than one syntactical form; for example, instruction "Type 4: Compute, dreg«···»DM | PM, data modify" on page 2-14 has four distinct forms.

Many instructions can be conditional. These instructions are prefaced by IF COND; for example:

```

If COND compute, |DM(Ia,Mb)| = ureg;

```

In a conditional instruction, the execution of the entire instruction is based on the specified condition.

## What's New in This Manual

This manual is Revision 4.1 of ADSP-21160 SHARC DSP Instruction Set Reference. This revision corrects minor typographical errors and the following issues:

- Active low signals represented correctly in equations for ALU conditions in Chapter 1, "Instruction Summary".

- AU flag removed and descriptions of the AV and AI flags corrected for the Rn = MANT Fx instruction in Chapter 6, "Computations Reference".

# **Technical Support**

You can reach Analog Devices processors and DSP technical support in the following ways:

Post your questions in the processors and DSP support community at EngineerZone<sup>®</sup>:

```

http://ez.analog.com/community/dsp

```

- Submit your questions to technical support directly at: http://www.analog.com/support

- E-mail your questions about processors, DSPs, and tools development software from CrossCore<sup>®</sup> Embedded Studio or VisualDSP++<sup>®</sup>:

Choose Help > Email Support. This creates an e-mail to processor.tools.support@analog.com and automatically attaches your CrossCore Embedded Studio or VisualDSP++ version information and license.dat file.

E-mail your questions about processors and processor applications to:

```

processor.support@analog.com or

processor.china@analog.com (Greater China support)

```

- In the USA only, call 1-800-ANALOGD (1-800-262-5643)

- Contact your Analog Devices sales office or authorized distributor.

Locate one at:

```

www.analog.com/adi-sales

```

Send questions by mail to:

Processors and DSP Technical Support Analog Devices, Inc.

Three Technology Way

P.O. Box 9106

Norwood, MA 02062-9106

USA

# **Supported Processors**

The name "SHARC" refers to a family of high-performance, floating-point embedded processors. Refer to the CCES or VisualDSP++ online help for a complete list of supported processors.

## **Product Information**

Product information can be obtained from the Analog Devices Web site and the CCES or VisualDSP++ online help.

## **Analog Devices Web Site**

The Analog Devices Web site, www.analog.com, provides information about a broad range of products—analog integrated circuits, amplifiers, converters, and digital signal processors.

To access a complete technical library for each processor family, go to <a href="http://www.analog.com/processors/technical\_library">http://www.analog.com/processors/technical\_library</a>. The manuals selection opens a list of current manuals related to the product as well as a link to the previous revisions of the manuals. When locating your manual title, note a possible errata check mark next to the title that leads to the current correction report against the manual.

Also note, myAnalog is a free feature of the Analog Devices Web site that allows customization of a Web page to display only the latest information about products you are interested in. You can choose to receive weekly e-mail notifications containing updates to the Web pages that meet your interests, including documentation errata against all manuals. myAnalog provides access to books, application notes, data sheets, code examples, and more.

Visit my Analog to sign up. If you are a registered user, just log on. Your user name is your e-mail address.

## **EngineerZone**

EngineerZone is a technical support forum from Analog Devices, Inc. It allows you direct access to ADI technical support engineers. You can search FAQs and technical information to get quick answers to your embedded processing and DSP design questions.

Use EngineerZone to connect with other DSP developers who face similar design challenges. You can also use this open forum to share knowledge and collaborate with the ADI support team and your peers. Visit <a href="http://ez.analog.com">http://ez.analog.com</a> to sign up.

# **Notation Conventions**

Text conventions in this manual are identified and described as follows.

| Example       | Description                                                                                                                                                                                                                                                                                                 |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| File > Close  | Titles in reference sections indicate the location of an item within the IDE environment's menu system (for example, the Close command appears on the File menu).                                                                                                                                           |

| {this   that} | Alternative required items in syntax descriptions appear within curly brackets and separated by vertical bars; read the example as this or that. One or the other is required.                                                                                                                              |

| [this   that] | Optional items in syntax descriptions appear within brackets and separated by vertical bars; read the example as an optional this or that.                                                                                                                                                                  |

| [this,]       | Optional item lists in syntax descriptions appear within brackets delimited by commas and terminated with an ellipsis; read the example as an optional comma-separated list of this.                                                                                                                        |

| .SECTION      | Commands, directives, keywords, and feature names are in text with letter gothic font.                                                                                                                                                                                                                      |

| filename      | Non-keyword placeholders appear in text with italic style format.                                                                                                                                                                                                                                           |

| (i)           | Note: For correct operation, A Note provides supplementary information on a related topic. In the online version of this book, the word Note appears instead of this symbol.                                                                                                                                |

| ×             | Caution: Incorrect device operation may result if Caution: Device damage may result if A Caution identifies conditions or inappropriate usage of the product that could lead to undesirable results or product damage. In the online version of this book, the word Caution appears instead of this symbol. |

| $\Diamond$    | Warning: Injury to device users may result if A Warning identifies conditions or inappropriate usage of the product that could lead to conditions that are potentially hazardous for devices users. In the online version of this book, the word Warning appears instead of this symbol.                    |

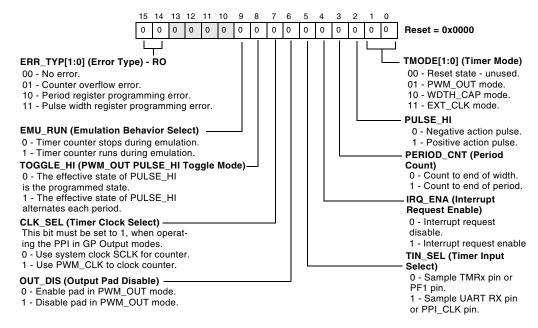

## **Register Diagram Conventions**

Register diagrams use the following conventions:

- The descriptive name of the register appears at the top, followed by the short form of the name in parentheses.

- If the register is read-only (RO), write-1-to-set (W1S), or write-1-to-clear (W1C), this information appears under the name. Read/write is the default and is not noted. Additional descriptive text may follow.

- If any bits in the register do not follow the overall read/write convention, this is noted in the bit description after the bit name.

- If a bit has a short name, the short name appears first in the bit description, followed by the long name in parentheses.

- The reset value appears in binary in the individual bits and in hexadecimal to the right of the register.

- Bits marked x have an unknown reset value. Consequently, the reset value of registers that contain such bits is undefined or dependent on pin values at reset.

- Shaded bits are reserved.

- To ensure upward compatibility with future implementations, write back the value that is read for reserved bits in a register, unless otherwise specified.

The following figure shows an example of these conventions.

#### Timer Configuration Registers (TIMERx\_CONFIG)

Figure 1. Register Diagram Example

# 1 INSTRUCTION SUMMARY

This instruction set summary provides a syntax summary for each instruction and includes a cross reference to each instruction's reference page.

# **Chapter Overview**

The following summary topics appear in this chapter.

- "Development Tools" on page 1-2

- "Compute and Move/Modify Summary" on page 1-3

- "Program Flow Control Summary" on page 1-5

- "Immediate Move Summary" on page 1-7

- "Miscellaneous Operations Summary" on page 1-8

- "Register Types Summary" on page 1-10

- "Memory Addressing Summary" on page 1-16

- "Instruction Set Notation Summary" on page 1-17

- "Conditional Execution Codes Summary" on page 1-20

- "SISD/SIMD Conditional Testing Summary" on page 1-22

- "Instruction Opcode Acronym Summary" on page 1-23

#### **Development Tools**

- "Universal Register Codes" on page 1-28

- "ADSP-21160 Instruction Opcode Map" on page 1-33

# **Development Tools**

The processor is supported by a complete set of software and hardware development tools, including Analog Devices' emulators and the Cross-Core Embedded Studio or VisualDSP++ development environment. (The emulator hardware that supports other Analog Devices processors also emulates the processor.)

The development environments support advanced application code development and debug with features such as:

- Create, compile, assemble, and link application programs written in C++, C, and assembly

- Load, run, step, halt, and set breakpoints in application programs

- Read and write data and program memory

- · Read and write core and peripheral registers

- Plot memory

Analog Devices DSP emulators use the IEEE 1149.1 JTAG test access port to monitor and control the target board processor during emulation. The emulator provides full speed emulation, allowing inspection and modification of memory, registers, and processor stacks. Nonintrusive in-circuit emulation is assured by the use of the processor JTAG interface—the emulator does not affect target system loading or timing.

Software tools also include Board Support Packages (BSPs). Hardware tools also include standalone evaluation systems (boards and extenders). In addition to the software and hardware development tools available from Analog Devices, third parties provide a wide range of tools supporting the Blackfin processors. Third party software tools include DSP libraries, real-time operating systems, and block diagram design tools.

# Compute and Move/Modify Summary

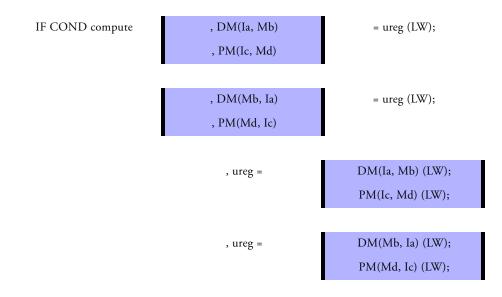

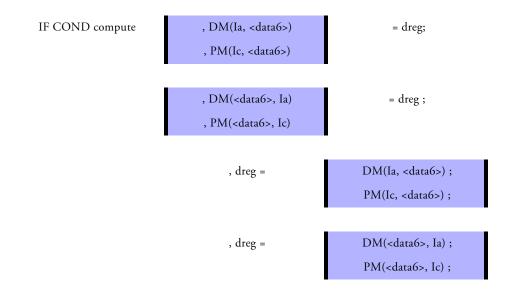

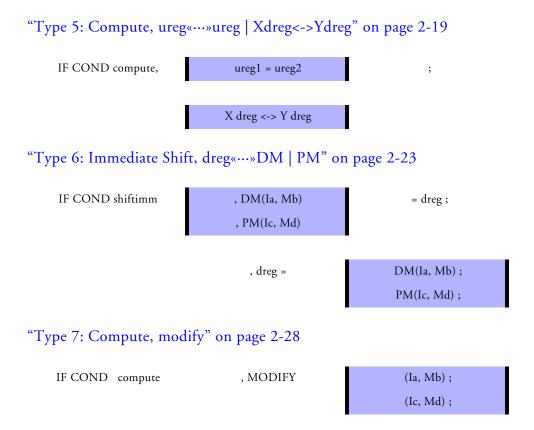

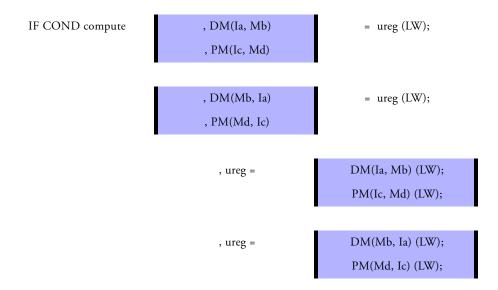

Compute and move/modify instructions are classed as Group I instructions, and they provide math, conditional, memory/register access services. The series of tables that follow summarize the Group I instructions. For a complete description of these instructions, see the noted pages.

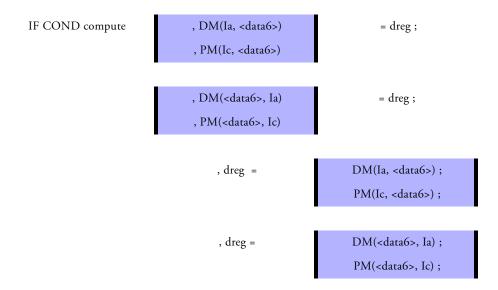

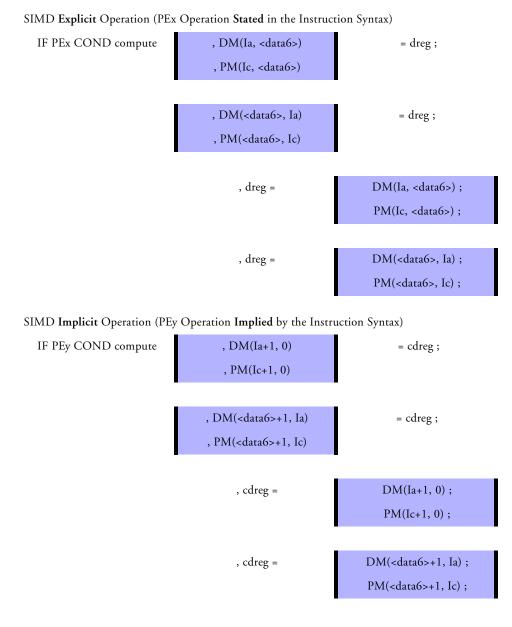

"Type 1: Compute, Dreg«····»DM | Dreg«···»PM" on page 2-3

"Type 2: Compute" on page 2-7

IF COND compute;

### Compute and Move/Modify Summary

"Type 3: Compute, ureg«····»DM | PM, register modify" on page 2-9

"Type 4: Compute, dreg«···»DM | PM, data modify" on page 2-14

# **Program Flow Control Summary**

Program flow control instructions are classed as Group II instructions, and they let you control program execution flow. The series of tables that follow summarize the Group II instructions. For a complete description of these instructions, see the noted pages.

#### **Program Flow Control Summary**

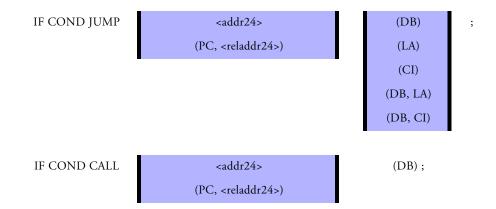

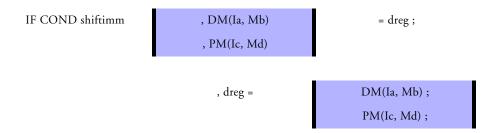

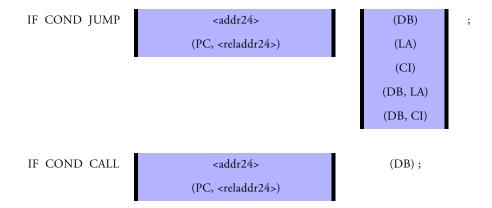

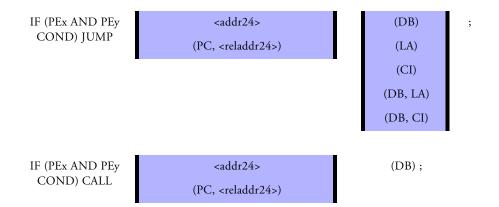

"Type 8: Direct Jump | Call" on page 3-3

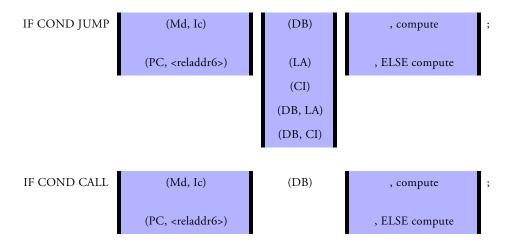

"Type 9: Indirect Jump | Call, Compute" on page 3-8

"Type 10: Indirect Jump | Compute, dreg«····»DM" on page 3-14

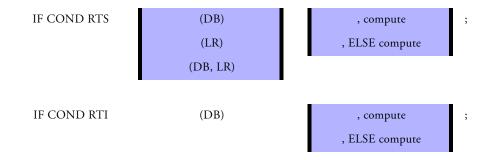

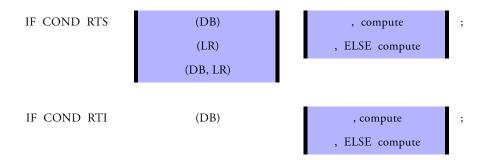

"Type 11: Return From Subroutine | Interrupt, Compute" on page 3-19

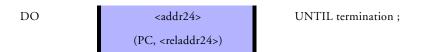

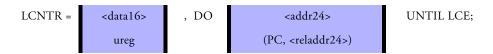

"Type 12: Do Until Counter Expired" on page 3-24

"Type 13: Do Until" on page 3-26

# **Immediate Move Summary**

Immediate move instructions are classed as Group III instructions, and they provide memory/register access services. The series of tables that follow summarize the Group III instructions. For a complete description of these instructions, see the noted pages.

#### **Miscellaneous Operations Summary**

# Miscellaneous Operations Summary

Miscellaneous instructions are classed as Group IV instructions, and they provide system register, bit manipulation, and low power services. The

series of tables that follow summarize the Group IV instructions. For a complete description of these instructions, see the noted pages.

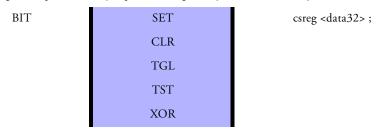

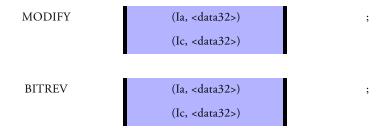

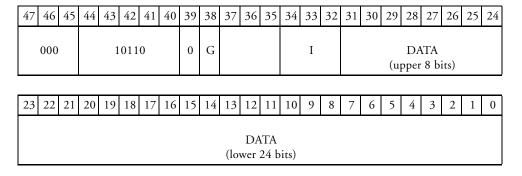

"Type 18: System Register Bit Manipulation" on page 5-2

"Type 19: I Register Modify | Bit-Reverse" on page 5-6

"Type 20: Push, Pop Stacks, Flush Cache" on page 5-9

"Type 21: Nop" on page 5-11

NOP;

## **Register Types Summary**

# **Register Types Summary**

Table 1-1 and Table 1-2 list ADSP-21160 DSP registers. The registers in Table 1-1 are in the core processor portion of the processor. The registers in Table 1-2 are in the integrated I/O processor and external port sections of the DSP.

## **Instruction Summary**

Table 1-1. Universal Registers (Ureg)

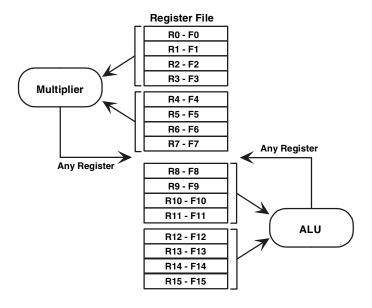

| Register Type                  | Register(s)                                                                          | Function                                                     |

|--------------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------|

| Register File<br>(ureg & dreg) | R0, R1, R2, R3, R4, R5, R6, R7, R8, R9, R10, R11, R12, R13, R14, R15                 | Processing element X register file locations, fixed-point    |

|                                | F0, F1, F2, F3, F4, F5, F6, F7, F8, F9, F10, F11, F12, F13, F14, F15                 | Processing element X register file locations, floating-point |

|                                | S0, S1, S2, S3, S4, S5, S6, S7, S8, S9, S10, S11, S12, S13, S14, S15                 | Processing element Y register file locations, fixed-point    |

|                                | SF0, SF1, SF2, SF3, SF4, SF5, SF6, SF7, SF8, SF9, SF10, SF11, SF12, SF13, SF14, SF15 | Processing element Y register file locations, floating-point |

| Program Sequencer              | PC                                                                                   | Program counter (read-only)                                  |

|                                | PCSTK                                                                                | Top of PC stack                                              |

|                                | PCSTKP                                                                               | PC stack pointer                                             |

|                                | FADDR                                                                                | Fetch address (read-only)                                    |

|                                | DADDR                                                                                | Decode address (read-only)                                   |

|                                | LADDR                                                                                | Loop termination address, code; top of loop address stack    |

|                                | CURLCNTR                                                                             | Current loop counter; top of loop count stack                |

|                                | LCNTR                                                                                | Loop count for next nested counter-controlled loop           |

## **Register Types Summary**

Table 1-1. Universal Registers (Ureg) (Cont'd)

| Register Type | Register(s)                             | Function                          |

|---------------|-----------------------------------------|-----------------------------------|

| Data Address  | 10, 11, 12, 13, 14, 15, 16, 17          | DAG1 index registers              |

| Generators    | M0, M1, M2, M3, M4, M5, M6, M7          | DAG1 modify registers             |

|               | L0, L1, L2, L3, L4, L5, L6, L7          | DAG1 length registers             |

|               | B0, B1, B2, B3, B4, B5, B6, B7          | DAG1 base registers               |

|               | I8, I9, I10, I11, I12, I13, I14, I15    | DAG2 index registers              |

|               | M8, M9, M10, M11, M12, M13, M14, M15    | DAG2 modify registers             |

|               | L8, L9, L10, L11, L12, L13, L14,<br>L15 | DAG2 length registers             |

|               | B8, B9, B10, B11, B12, B13, B14, B15    | DAG2 base registers               |

| Bus Exchange  | PX1                                     | PMD-DMD bus exchange 1 (32 bits)  |

|               | PX2                                     | PMD-DMD bus exchange 2 (32 bits)  |

|               | PX                                      | 64-bit combination of PX1 and PX2 |

| Timer         | TPERIOD                                 | Timer period                      |

|               | TCOUNT                                  | Timer counter                     |

## **Instruction Summary**

Table 1-1. Universal Registers (Ureg) (Cont'd)

| Register Type    | Register(s) | Function                                                           |

|------------------|-------------|--------------------------------------------------------------------|

| System Registers | MODE1       | Mode control & status                                              |

| (sreg & ureg)    | MODE2       | Mode control & status                                              |

|                  | IRPTL       | Interrupt latch                                                    |

|                  | IMASK       | Interrupt mask                                                     |

|                  | IMASKP      | Interrupt mask pointer (for nesting)                               |

|                  | MMASK       | Mode mask                                                          |

|                  | FLAGS       | Flag pins input/output state                                       |

|                  | LIRPTL      | Link Port interrupt latch, mask, and pointer                       |

|                  | ASTATx      | Element x arithmetic status flags, bit test flag, etc.             |

|                  | ASTATy      | Element y arithmetic status flags, bit test flag, etc.             |

|                  | STKYx       | Element x sticky arithmetic status flags, stack status flags, etc. |

|                  | STKYy       | Element y sticky arithmetic status flags, stack status flags, etc. |

|                  | USTAT1      | User status register 1                                             |

|                  | USTAT2      | User status register 2                                             |

|                  | USTAT3      | User status register 3                                             |

|                  | USTAT4      | User status register 4                                             |

## **Register Types Summary**

Table 1-2. I/O and Multiplier Registers

| Register Type                     | Register(s)                                                  | Function                     |

|-----------------------------------|--------------------------------------------------------------|------------------------------|

| IOP registers<br>(system control) | SYSCON                                                       | System control               |

|                                   | SYSTAT                                                       | System status                |

|                                   | WAIT                                                         | Memory wait states           |

|                                   | VIRPT                                                        | Multiprocessor IRQ           |

| IOP registers<br>(system control) | MSGR0, MSGR1, MSGR2,<br>MSGR3, MSGR4, MSGR5,<br>MSGR6, MSGR7 | Message registers            |

|                                   | BMAX                                                         | Bus timeout max              |

|                                   | BCNT                                                         | Bus timeout count            |

|                                   | ELAST                                                        | External address last        |

| IOP registers<br>(DMA)            | EPB0, EPB1, EPB2, EPB3                                       | External port FIFO buffers   |

|                                   | DMAC10, DMAC11, DMAC12,<br>DMAC13                            | DMA controls (EPB0-3)        |

|                                   | DMASTAT                                                      | DMA status                   |

|                                   | II0, IM0, C0, CP0, GP0, DB0, DA0                             | DMA 0 parameters (SPORT0 RX) |

|                                   | II1, IM1, C1, CP1, GP1, DB1, DA1                             | DMA 1 parameters (SPORT1 RX) |

|                                   | II2, IM2, C2, CP2, GP2, DB2, DA2                             | DMA 2 parameters (SPORT0 TX) |

|                                   | II3, IM3, C3, CP3, GP3, DB3, DA3                             | DMA 3 parameters (SPORT1 TX) |

## **Instruction Summary**

Table 1-2. I/O and Multiplier Registers (Cont'd)

| Register Type                 | Register(s)                                      | Function                 |

|-------------------------------|--------------------------------------------------|--------------------------|

| IOP registers<br>(DMA)        | II4, IM4, C4, CP4, GP4, DB4, DA4                 | DMA 4 parameters (LBUF0) |

|                               | II5, IM5, C5, CP5, GP5, DB5, DA5                 | DMA 5 parameters (LBUF1) |

|                               | II6, IM6, C6, CP6, GP6, DB6, DA6                 | DMA 6 parameters (LBUF2) |

|                               | II7, IM7, C7, CP7, GP7, DB7, DA7                 | DMA 7 parameters (LBUF3) |

|                               | II8, IM8, C8, CP8, GP8, DB8, DA8                 | DMA 8 parameters (LBUF4) |

|                               | II9, IM9, C9, CP9, GP9, DB9, DA9                 | DMA 9 parameters (LBUF5) |

|                               | II10, IM10, C10, CP10, GP10,<br>EI10, EM10, EC10 | DMA 10 parameters (EPB0) |

|                               | II11, IM11, C11, CP11, GP11,<br>EI11, EM11, EC11 | DMA 11 parameters (EPB1) |

|                               | II12, IM12, C12, CP12, GP12,<br>EI12, EM12, EC12 | DMA 12 parameters (EPB2) |

|                               | II13, IM13, C13, CP13, GP13,<br>EI13, EM13, EC13 | DMA 7 parameters (EPB3)  |

| IOP registers<br>(Link ports) | LBUF0, LBUF1, LBUF2, LBUF3,<br>LBUF4, LBUF5      | Link port buffers        |

|                               | LCTL0, LCTL1                                     | Link buffer control      |

|                               | LCOM                                             | Link common control      |

|                               | LAR                                              | Link assignment          |

|                               | LSRQ                                             | Link service request     |

|                               | LPATH1, LPATH2, LPATH3                           | Link path (mesh)         |

|                               | LPCNT                                            | Link path count (mesh)   |

|                               | CNST1, CNST2                                     | Link constant (mesh)     |

## **Memory Addressing Summary**

Table 1-2. I/O and Multiplier Registers (Cont'd)

| Register Type             | Register(s)                                                                                             | Function                       |

|---------------------------|---------------------------------------------------------------------------------------------------------|--------------------------------|

| IOP registers<br>(SPORTs) | STCTL0, SRCTL0, TX0, RX0,<br>TDIV0, RDIV0, MTCS0, MRCS0,<br>MTCCS0, MRCCS0, SPATH0,<br>KEYWD0, KEYMASK0 | SPORT 0 registers              |

|                           | STCTL1, SRCTL1, TX1, RX1,<br>TDIV1, RDIV1, MTCS, MRCS1,<br>MTCCS1, MRCCS1, SPATH1,<br>KEYWD1, KEYMASK1  | SPORT 1 registers              |

| Multiplier registers      | MR, MR0, MR1, MR2,                                                                                      | Multiplier results             |

|                           | MRF, MR0F, MR1F, MR2F                                                                                   | Multiplier results, foreground |

|                           | MRB, MR0B, MR1B, MR2B                                                                                   | Multiplier results, background |

# **Memory Addressing Summary**

ADSP-21160 processors support the following types of addressing.

### **Direct Addressing**

• Absolute address (Instruction Types 8, 12, 13, 14)

```

dm(0x000015F0) = astat;

if ne jump label2; {'label2' is an address label}

```

• PC-relative address (Instruction Types 8, 9, 10, 12, 13)

```

call(pc,10), r0=r6+r3;

do(pc,length) until sz; {'length' is a variable}

```

**Indirect Addressing** (using DAG registers):

• Post-modify with M register, update I register (Instruction Types 1, 3, 6, 16)

```

f5=pm(i9,m12);

dm(i0,m3)=r3, r1=pm(i15,m10);

```

• Pre-modify with M register, no update (Instruction Types 3, 9, 10)

```

r1=pm(m10,i15);

jump(m13,i11);

```

• Post-modify with immediate value, update I register (Instruction Type 4)

```

f15=dm(i0,6);

if av r1=pm(i15,0x11);

```

• Pre-modify with immediate value, no update (Instruction Types 4, 15)

```

if av r1=pm(0x11,i15);

dm(127,i5)=laddr;

```

# **Instruction Set Notation Summary**

The conventions for ADSP-210xx instruction syntax descriptions appear in Table 1-3 on page 1-18. Other parts of the instruction syntax and opcode information also appear in this section.

## **Instruction Set Notation Summary**

Table 1-3. Instruction Set Notation

| Notation               | Meaning                                                                                                                                |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| UPPERCASE              | Explicit syntax—assembler keyword (notation only; assembler is case-insensitive and lowercase is the preferred programming convention) |

| ;                      | Semicolon (instruction terminator)                                                                                                     |

| ,                      | Comma (separates parallel operations in an instruction)                                                                                |

| italics                | Optional part of instruction                                                                                                           |

| option1  <br>  option2 | List of options between vertical bars (choose one)                                                                                     |

| compute                | ALU, multiplier, shifter or multifunction operation (see the chapter "Computations Reference").                                        |

| shiftimm               | Shifter immediate operation (see the chapter "Computations Reference").                                                                |

| cond                   | Status condition (see condition codes in Table 1-4 on page 1-20)                                                                       |

| termination            | Loop termination condition (see condition codes in Table 1-4 on page 1-20)                                                             |

| ureg                   | Universal register                                                                                                                     |

| cureg                  | Complementary universal register (see Table 1-10 on page 1-30)                                                                         |

| sreg                   | System register                                                                                                                        |

| csreg                  | Complementary system register (see Table 1-10 on page 1-30)                                                                            |

| dreg                   | Data register (register file): R15-R0 or F15-F0                                                                                        |

| cdreg                  | Complementary data register (register file): R15-R0 or F15-F0 (see Table 1-10 on page 1-30)                                            |

| creg                   | One of 32 cache entries, an entry consisting of a CH, CL, & CA                                                                         |

| Ia                     | I7-I0 (DAG1 index register)                                                                                                            |

| Mb                     | M7-M0 (DAG1 modify register)                                                                                                           |

| Ic                     | I15-I8 (DAG2 index register)                                                                                                           |

| Md                     | M15-M8 (DAG2 modify register)                                                                                                          |

| <datan></datan>        | n-bit immediate data value                                                                                                             |

### **Instruction Summary**

Table 1-3. Instruction Set Notation (Cont'd)

| Notation              | Meaning                                                  |

|-----------------------|----------------------------------------------------------|

| <addrn></addrn>       | n-bit immediate address value                            |

| <reladdrn></reladdrn> | n-bit immediate PC-relative address value                |

| +1                    | the incremented data, address or register value          |

| (DB)                  | Delayed branch                                           |

| (LA)                  | Loop abort (pop loop and PC stacks on branch)            |

| (CI)                  | Clear interrupt                                          |

| (LR)                  | Loop reentry                                             |

| (LW)                  | Long Word (forces Long word access in Normal word range) |

## Conditional Execution Codes Summary

In a conditional instruction, execution of the entire instruction depends on the specified condition (cond or terminate). Table 1-4 lists the codes that you can use in conditionals (IF and DO UNTIL).

Table 1-4. IF Condition and Do/Until Termination Mnemonics

| Condition From | Description             | True if               | Mnemonic |

|----------------|-------------------------|-----------------------|----------|

| ALU            | ALU = 0                 | AZ = 1                | EQ       |

|                | ALU ≠ 0                 | AZ = 0                | NE       |

|                | ALU > 0                 | footnote <sup>1</sup> | GT       |

|                | ALU < zero              | footnote <sup>2</sup> | LT       |

|                | ALU ≥ 0                 | footnote <sup>3</sup> | GE       |

|                | $ALU \le 0$             | footnote <sup>4</sup> | LE       |

|                | ALU carry               | AC = 1                | AC       |

|                | ALU not carry           | AC = 0                | NOT AC   |

|                | ALU overflow            | AV = 1                | AV       |

|                | ALU not overflow        | AV = 0                | NOT AV   |

| Multiplier     | Multiplier overflow     | MV = 1                | MV       |

|                | Multiplier not overflow | MV= 0                 | NOT MV   |

|                | Multiplier sign         | MN = 1                | MS       |

|                | Multiplier not sign     | MN = 0                | NOT MS   |

| Shifter        | Shifter overflow        | SV = 1                | SV       |

|                | Shifter not overflow    | SV = 0                | NOT SV   |

|                | Shifter zero            | SZ = 1                | SZ       |

|                | Shifter not zero        | SZ = 0                | NOT SZ   |

| Bit Test       | Bit test flag true      | BTF = 1               | TF       |

|                | Bit test flag false     | BTF = 0               | NOT TF   |

Table 1-4. IF Condition and Do/Until Termination Mnemonics (Cont'd)

| Condition From | Description                   | True if      | Mnemonic     |

|----------------|-------------------------------|--------------|--------------|

| Flag Input     | Flag0 asserted                | FIO = 1      | FLAG0_IN     |

|                | Flag0 not asserted            | FI0 = 0      | NOT FLAG0_IN |

|                | Flag1 asserted                | FI1 = 1      | FLAG1_IN     |

|                | Flag1 not asserted            | FI1 = 0      | NOT FLAG1_IN |

|                | Flag2 asserted                | FI2 = 1      | FLAG2_IN     |

|                | Flag2 not asserted            | FI2 = 0      | NOT FLAG2_IN |

|                | Flag3 asserted                | FI3 = 1      | FLAG3_IN     |

|                | Flag3 not asserted            | FI3 = 0      | NOT FLAG3_IN |

| Mode           | Bus master true               |              | BM           |

|                | Bus master false              |              | NOT BM       |

| Sequencer      | Loop counter expired (Do)     | CURLCNTR = 1 | LCE          |

|                | Loop counter not expired (If) | CURLCNTR ≠ 1 | NOT ICE      |

|                | Always false (Do)             | Always       | FOREVER      |

|                | Always true (If)              | Always       | TRUE         |

<sup>1</sup> ALU greater than (GT) is true if: [AF and (AN xor (AV and ALUSAT)) or (AF and AN)] or AZ = 0

<sup>2</sup> ALU less than (LT) is true if:  $[\overline{AF}]$  and  $(\overline{AN}]$  xor  $(\overline{AV}]$  and  $\overline{ALUSAT}$ ) or  $(\overline{AF}]$  and  $(\overline{AN}]$  and  $(\overline{AN}]$  = 1

<sup>3</sup> ALU greater equal (GE) is true if:  $[\overline{AF} \text{ and } (AN \text{ xor } (AV \text{ and } \overline{ALUSAT})) \text{ or } (AF \text{ and } AN \text{ and } \overline{AZ})] = 0$

<sup>4</sup> ALU lesser or equal (LE) is true if: [AF and (AN xor (AV and ALUSAT)) or (AF and AN)] or AZ = 1

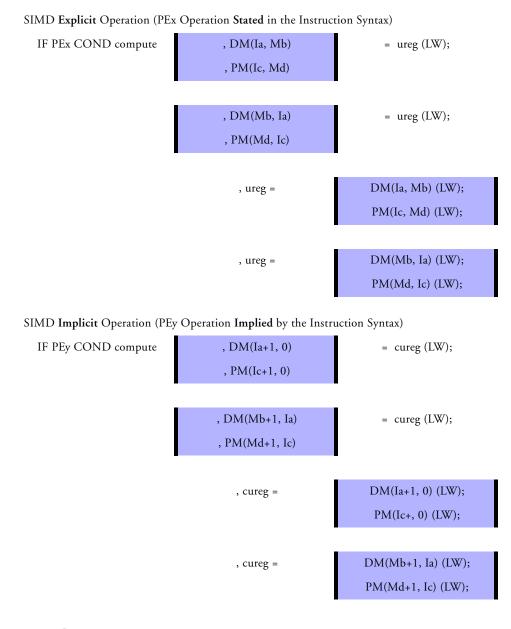

# SISD/SIMD Conditional Testing Summary

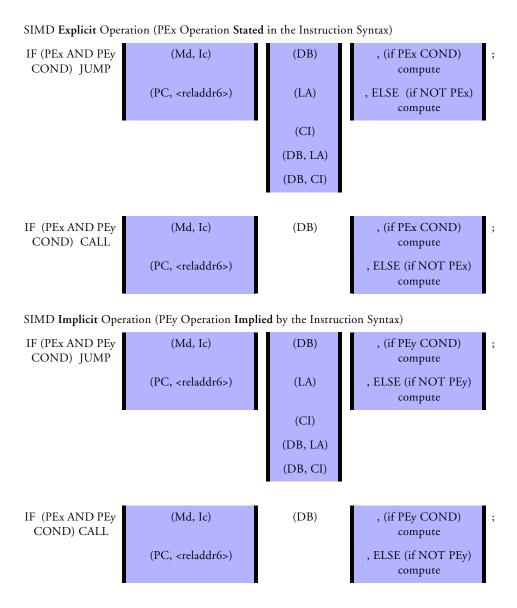

The processor handles conditional execution differently in SISD versus SIMD mode. There are three ways that conditionals differ in SIMD mode:

- In conditional computation (If ... Compute) instructions, each processing element executes the computation based on evaluating the condition in that processing element.

- In conditional program control (If ... Jump/Call) instructions, the program sequencer executes the Jump/Call based on a logical AND of the conditions in both processing elements.

- In conditional computation instructions with an Else clause, each

processing element executes the Else computation based on evaluating the inverse of the condition (Not Cond) in that processing

element.

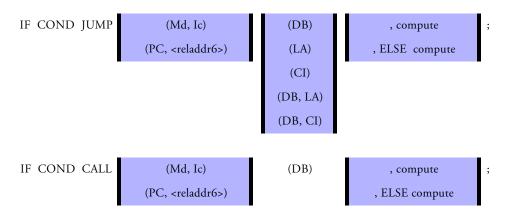

Table 1-5 on page 1-22 and Table 1-6 on page 1-23 compare SISD and SIMD If-Else conditional execution, which are available in the Type 9, 10, and 11 instructions.

Table 1-5. SISD Mode Conditional Execution

| Conditional test | ELSE modifier    | Results for Type 11 (RTS)      |

|------------------|------------------|--------------------------------|

| 0 (false)        | 0 (without else) | rts nops, compute nops         |

| 0 (false)        | 1 (else)         | rts nops, compute executes     |

| 1 (true)         | 0 (without else) | rts executes, compute executes |

| 1 (true)         | 1 (else)         | rts executes, compute nops     |

Table 1-6. SIMD Mode Conditional Execution

| Conditional test |     | Else modifier | Results for Type 11 (RTS)                        |  |

|------------------|-----|---------------|--------------------------------------------------|--|

| PEx              | PEy |               |                                                  |  |

| 0                | 0   | 0             | rts nops, pex compute nops, pey compute nops     |  |

| 0                | 1   | 0             | rts nops, pex compute nops, pey compute executes |  |

| 1                | 0   | 0             | rts nops, pex compute exe., pey compute nops     |  |

| 1                | 1   | 0             | rts exe., pex compute exe., pey compute exe.     |  |

| 0                | 0   | 1             | rts nops, pex compute exe., pey compute exe.     |  |

| 0                | 1   | 1             | rts nops, pex compute exe., pey compute nops     |  |

| 1                | 0   | 1             | rts nops, pex compute nops, pey compute exe.     |  |

| 1                | 1   | 1             | rts exe., pex compute nops, pey compute nops     |  |

For more information and examples, see the following instruction reference pages.

- "Type 9: Indirect Jump | Call, Compute" on page 3-8

- "Type 10: Indirect Jump | Compute, dreg«···»DM" on page 3-14

- "Type 11: Return From Subroutine | Interrupt, Compute" on page 3-19

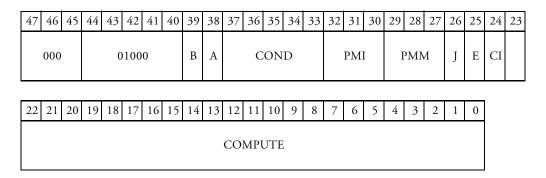

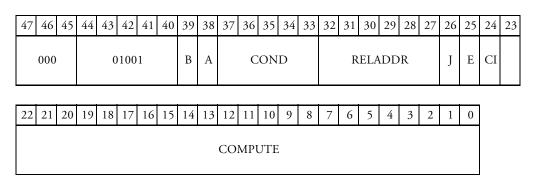

## **Instruction Opcode Acronym Summary**

In ADSP-21160 DSP opcodes, some bits are explicitly defined to be zeros or ones. The values of other bits or fields set various parameters for the instruction. The terms in Table 1-7 define these opcode bits and fields. Unspecified bits are ignored when the processor decodes the instruction, but are reserved for future use.

## **Instruction Opcode Acronym Summary**

Table 1-7. Opcode Acronyms

| Bit/Field | Description                                                        | States |                                      |

|-----------|--------------------------------------------------------------------|--------|--------------------------------------|

| A         | Loop abort code                                                    | 0      | Do not pop loop, PC stacks on branch |

|           |                                                                    | 1      | Pop loop, PC stacks on branch        |

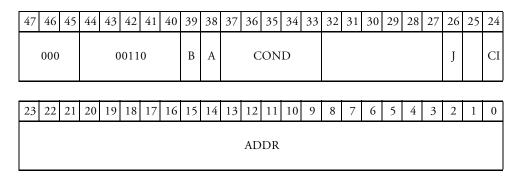

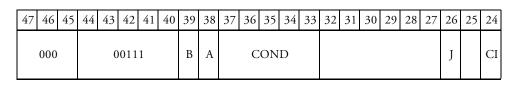

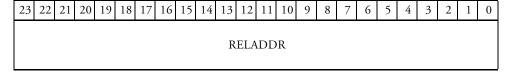

| ADDR      | Immediate address field                                            |        |                                      |

| AI        | Computation unit register                                          | 0000   | MR0F                                 |

|           |                                                                    | 0001   | MR1F                                 |

|           |                                                                    | 0010   | MR2F                                 |

|           |                                                                    | 0100   | MR0B                                 |

|           |                                                                    | 0101   | MR1B                                 |

|           |                                                                    | 0110   | MR2B                                 |

| В         | Branch type                                                        | 0      | Jump                                 |

|           |                                                                    | 1      | Call                                 |

| ВОР       | Bit Operation select codes                                         | 000    | Set                                  |

|           |                                                                    | 001    | Clear                                |

|           |                                                                    | 010    | Toggle                               |

|           |                                                                    | 100    | Test                                 |

|           |                                                                    | 101    | XOR                                  |

| COMPUTE   | Compute operation field (see "Computations Reference" on page 6-1) |        |                                      |

| COND      | Status Condition codes                                             | 0-31   |                                      |

| CI        | Clear interrupt code                                               | 0      | Do not clear current interrupt       |

|           |                                                                    | 1      | Clear current interrupt              |

| CREG      | Instruction cache entry                                            | 0-31   |                                      |

## **Instruction Summary**

Table 1-7. Opcode Acronyms (Cont'd)

| Bit/Field | Description                            | States         |                                                                                             |

|-----------|----------------------------------------|----------------|---------------------------------------------------------------------------------------------|

| CS        | Instruction cache register select code | 00<br>01<br>11 | Lower half of instruction RAM entry  Upper half of instruction RAM entry  Address CAM entry |

| CU        | Computation unit select codes          | 00             | ALU                                                                                         |

|           |                                        | 01             | Multiplier                                                                                  |

|           |                                        | 10             | Shifter                                                                                     |

| DATA      | Immediate data field                   |                |                                                                                             |

| DEC       | Counter decrement code                 | 0              | No counter decrement                                                                        |

|           |                                        | 1              | Counter decrement                                                                           |

| DMD       | Memory access direction                | 0              | Read                                                                                        |

|           |                                        | 1              | Write                                                                                       |

| DMI       | Index (I) register numbers, DAG1       | 0-7            |                                                                                             |

| DMM       | Modify (M) register numbers, DAG1      | 0-7            |                                                                                             |

| DREG      | Register file locations                | 0-15           |                                                                                             |

| Е         | ELSE clause code                       | 0              | No ELSE clause                                                                              |

|           |                                        | 1              | ELSE clause                                                                                 |

| FC        | Flush cache code                       | 0              | No cache flush                                                                              |

|           |                                        | 1              | Cache flush                                                                                 |

| G         | DAG/Memory select                      | 0              | DAG1 or Data Memory                                                                         |

|           |                                        | 1              | DAG2 or Program Memory                                                                      |

| INC       | Counter increment code                 | 0              | No counter increment                                                                        |

|           |                                        | 1              | Counter increment                                                                           |

## **Instruction Opcode Acronym Summary**

Table 1-7. Opcode Acronyms (Cont'd)

| Bit/Field | Description                                      | States |                                |

|-----------|--------------------------------------------------|--------|--------------------------------|

| J         | Jump Type                                        | 0      | Non-delayed                    |

|           |                                                  | 1      | Delayed                        |

| L         | Long Word memory address                         | 0      | Access size based on memory    |

|           |                                                  | 1      | map                            |

|           |                                                  |        | Long word (64-bit) access size |

| LPO       | Loop stack pop code                              | 0      | No stack pop                   |

|           |                                                  | 1      | Stack pop                      |

| LPU       | Loop stack push code                             | 0      | No stack push                  |

|           |                                                  | 1      | Stack push                     |

| LR        | Loop reentry code                                | 0      | No loop reentry                |

|           |                                                  | 1      | Loop reentry                   |

| NUM       | Interrupt vector                                 | 0-7    |                                |

| PMD       | Memory access direction                          | 0      | Read                           |

|           |                                                  | 1      | Write                          |

| PMI       | Index (I) register numbers, DAG2                 | 8–15   |                                |

| PMM       | Modify (M) register numbers, DAG2                | 8–15   |                                |

| PPO       | PC stack pop code                                | 0      | No stack pop                   |

|           |                                                  | 1      | Stack pop                      |

| PPU       | PC stack push code                               | 0      | No stack push                  |

|           |                                                  | 1      | Stack push                     |

| RELADDR   | PC-relative address field                        |        |                                |

| S         | UREG transfer/instruction cache read-load select | 0      | instruction cache read-load    |

|           | read road screet                                 | 1      | ureg transfer                  |

## **Instruction Summary**

Table 1-7. Opcode Acronyms (Cont'd)

| Bit/Field                 | Description                                                              | States                                              |

|---------------------------|--------------------------------------------------------------------------|-----------------------------------------------------|

| SPO                       | Status stack pop code                                                    | 0 No stack pop                                      |

|                           |                                                                          | 1 Stack pop                                         |

| SPU                       | Status stack push code                                                   | 0 No stack push                                     |

|                           |                                                                          | 1 Stack push                                        |

| SREG                      | System Register code                                                     | 0–15 (see "Universal Register Codes" on page 1-28)  |

| TERM                      | Termination Condition codes                                              | 0-31                                                |

| U                         | Update, index (I) register                                               | 0 Pre-modify, no update                             |

|                           |                                                                          | 1 Post-modify with update                           |

| UREG                      | Universal Register code                                                  | 0–256 (see "Universal Register Codes" on page 1-28) |

| RA, RM, RN,<br>RS, RX, RY | Register file locations for compute operands and results                 | 0–15                                                |

| RXA                       | ALU x-operand register file location for multifunction operations        | 8–11                                                |

| RXM                       | Multiplier x-operand register file location for multifunction operations | 0–3                                                 |

| RYA                       | ALU y-operand register file location for multifunction operations        | 12–15                                               |

| RYM                       | Multiplier y-operand register file location for multifunction operations | 4–7                                                 |

# **Universal Register Codes**

Table 1-8, Table 1-9 on page 1-29, Table 1-10 on page 1-30, and Table 1-11 on page 1-31 in this section list the bit codes for register that appear within opcode fields.

Table 1-8. Universal Registers

| Register | Description                       |

|----------|-----------------------------------|

| PC       | program counter                   |

| PCSTK    | top of PC stack                   |

| PCSTKP   | PC stack pointer                  |

| FADDR    | fetch address                     |

| DADDR    | decode address                    |

| LADDR    | loop termination address          |

| CURLCNTR | current loop counter              |

| LCNTR    | loop counter                      |

| R15-R0   | X element register file locations |

| S15–S0   | Y element register file locations |

| I15–I0   | DAG1 and DAG2 index registers     |

| M15-M0   | DAG1 and DAG2 modify registers    |

| L15-L0   | DAG1 and DAG2 length registers    |

| B15-B0   | DAG1 and DAG2 base registers      |

| PX       | 48-bit PX1 and PX2 combination    |

| PX1      | bus exchange 1 (16 bits)          |

| PX2      | bus exchange 2 (32 bits)          |

| TPERIOD  | timer period                      |

| TCOUNT   | timer counter                     |

Table 1-9. Universal and System Registers

| Register | Description                  |

|----------|------------------------------|

| MODE1    | mode control 1               |

| MODE2    | mode control 2               |

| IRPTL    | interrupt latch              |

| IMASK    | interrupt mask               |

| IMASKP   | interrupt mask pointer       |

| MMASK    | Mode mask                    |

| FLAGS    | Flag pins input/output state |

| ASTATx   | X element arithmetic status  |

| STKYx    | X element sticky status      |

| ASTATy   | Y element arithmetic status  |

| STKYy    | Y element sticky status      |

| USTAT1   | user status reg 1            |

| USTAT2   | user status reg 2            |

| USTAT3   | user status reg 3            |

| USTAT4   | user status reg 4            |

## **Universal Register Codes**

Table 1-10. Complementary Registers (Ureg-Cureg)

| Register Type                 | SIMD Mode Complementary Registers                                                                           |

|-------------------------------|-------------------------------------------------------------------------------------------------------------|

| Data register (dreg & ureg)   | R0-S0 R1-S1 R2-S2 R3-S3 R4-S4 R5-S5 R6-S6 R7-S7 R8-S8 R9-S9 R10-S10 R11-S11 R12-S12 R13-S13 R14-S14 R15-S15 |

| System register (sreg & ureg) | USTAT1-USTAT2<br>USTAT3-USTAT4<br>ASTATx-ASTATy<br>STKYx-STKYy                                              |

| Bus exchange register (ureg)  | PX1-PX2                                                                                                     |

Table 1-11 shows how Ureg register codes appear to PEx.

Table 1-11. Processing Element X Universal Register Codes (SISD/SIMD)

| Bits: 3210 ↓ | Bits: 7654<br>0000 | 0001 | 0010 | 0011 | 0100 | 0101 | 0110         | 0111   |

|--------------|--------------------|------|------|------|------|------|--------------|--------|

| 0000         | R0                 | 10   | M0   | L0   | В0   | S0   | FADDR        | USTAT1 |

| 0001         | R1                 | I1   | M1   | L1   | B1   | S1   | DADDR        | USTAT2 |

| 0010         | R2                 | I2   | M2   | L2   | B2   | S2   |              | MODE1  |

| 0011         | R3                 | I3   | М3   | L3   | В3   | S3   | PC           | MMASK  |

| 0100         | R4                 | I4   | M4   | L4   | B4   | S4   | PCSTK        | MODE2  |

| 0101         | R5                 | I5   | M5   | L5   | B5   | S5   | PCSTKP       | FLAGS  |

| 0110         | R6                 | I6   | M6   | L6   | В6   | S6   | LADDR        | ASTATx |

| 0111         | R7                 | I7   | M7   | L7   | В7   | S7   | CURLCNT<br>R | ASTATy |

| 1000         | R8                 | I8   | M8   | L8   | B8   | S8   | LCNTR        | STKYx  |

| 1001         | R9                 | I9   | M9   | L9   | В9   | S9   | EMUCLK       | STKYy  |

| 1010         | R10                | I10  | M10  | L10  | B10  | S10  | EMUCLK2      | IRPTL  |

| 1011         | R11                | I11  | M11  | L11  | B11  | S11  | PX           | IMASK  |

| 1100         | R12                | I12  | M12  | L12  | B12  | S12  | PX1          | IMASKP |

| 1101         | R13                | I13  | M13  | L13  | B13  | S13  | PX2          | LRPTL  |

| 1110         | R14                | I14  | M14  | L14  | B14  | S14  | TPERIOD      | USTAT3 |

| 1111         | R15                | I15  | M15  | L15  | B15  | S15  | TCOUNT       | USTAT4 |

## **Universal Register Codes**

Table 1-12 shows how Ureg register codes appear to PEy.

Table 1-12. Processing Element Y Universal Register Codes (SIMD)

| Bits: 3210 ↓ | Bits: 7654<br>0000 | 0001 | 0010 | 0011 | 0100 | 0101 | 0110         | 0111   |

|--------------|--------------------|------|------|------|------|------|--------------|--------|

| 0000         | S0                 | 10   | M0   | L0   | В0   | R0   | FADDR        | USTAT2 |

| 0001         | S1                 | I1   | M1   | L1   | B1   | R1   | DADDR        | USTAT1 |

| 0010         | S2                 | I2   | M2   | L2   | B2   | R2   |              | MODE1  |

| 0011         | S3                 | I3   | М3   | L3   | В3   | R3   | PC           | MMASK  |

| 0100         | S4                 | I4   | M4   | L4   | B4   | R4   | PCSTK        | MODE2  |

| 0101         | S5                 | I5   | M5   | L5   | B5   | R5   | PCSTKP       | FLAGS  |

| 0110         | S6                 | I6   | M6   | L6   | В6   | R6   | LADDR        | ASTATy |

| 0111         | S7                 | I7   | M7   | L7   | B7   | R7   | CURLCNT<br>R | ASTATx |

| 1000         | S8                 | I8   | M8   | L8   | B8   | R8   | LCNTR        | STKYy  |

| 1001         | S9                 | I9   | M9   | L9   | В9   | R9   | EMUCLK       | STKYx  |

| 1010         | S10                | I10  | M10  | L10  | B10  | R10  | EMUCLK2      | IRPTL  |

| 1011         | S11                | I11  | M11  | L11  | B11  | R11  | PX           | IMASK  |

| 1100         | S12                | I12  | M12  | L12  | B12  | R12  | PX2          | IMASKP |

| 1101         | S13                | I13  | M13  | L13  | B13  | R13  | PX1          | LRPTL  |

| 1110         | S14                | I14  | M14  | L14  | B14  | R14  | TPERIOD      | USTAT4 |

| 1111         | S15                | I15  | M15  | L15  | B15  | R15  | TCOUNT       | USTAT3 |

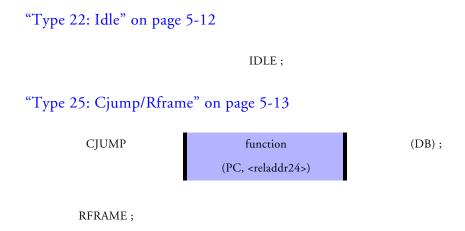

Table 1-13. ADSP-21160 DSP Opcodes (Bits 47-27)

| Instruction Type                                       | 47   46   45   44   43   42   41   40   39   38 |     |    |             |         |      |    | 37   | 36  | 35 | 34          | 33 | 32   | 31  | 30 | 29 | 28  | 27 |     |            |    |

|--------------------------------------------------------|-------------------------------------------------|-----|----|-------------|---------|------|----|------|-----|----|-------------|----|------|-----|----|----|-----|----|-----|------------|----|

| "Type 1: Compute,<br>Dreg«···»DM  <br>Dreg«···»PM"     |                                                 | 001 |    | D<br>M<br>D |         | DM   | Ī  | Ι    | OMN | Л  | P<br>M<br>D | D  | )M ] | DRI | EG |    | PM: | I  |     | PMN        | M  |

| "Type 2: Compute"                                      |                                                 | 000 | ١  |             | (       | 0000 | )1 |      |     |    |             | C  | ON   | ID  |    |    |     |    |     |            |    |

| "Type 3: Compute, ureg«····»DM   PM, register modify"  |                                                 | 010 | )  | U           | I       |      |    |      | М   |    |             | C  | ON   | ID  |    | G  | D   | L  | U   | JRE(       | G> |

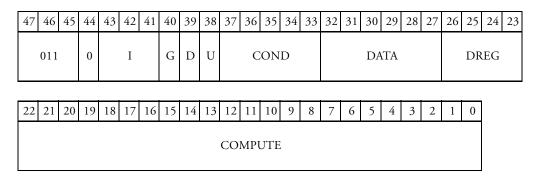

| "Type 4: Compute,<br>dreg«···»DM   PM,<br>data modify" |                                                 | 011 |    | 0           | I       |      |    | G    | D   | U  |             | C  | ON   | ID  |    |    |     | DA | ΑТА |            |    |

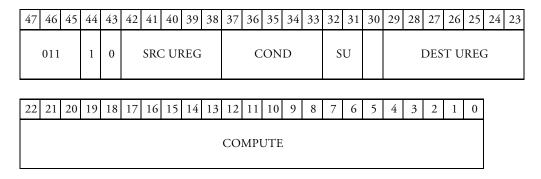

| (a) "Type 5: Compute, ureg«····»ureg   Xdreg<->Ydreg"  |                                                 | 011 |    | 1           | 0 SRC U |      |    | C UI | REG |    |             | C  | ON   | ID  |    | S  | U   |    |     | DES<br>IRE |    |

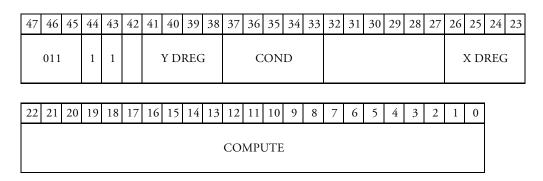

| (b) "Type 5: Compute, ureg«····»ureg   Xdreg<->Ydreg"  |                                                 | 011 |    | 1           | 1       |      |    | Y D  | REG | ì  |             | C  | ON   | ID  |    |    |     |    |     |            |    |

| (a) "Type 6: Immediate Shift,<br>dreg«···»DM   PM"     |                                                 | 100 | )  | 0           |         | I    |    |      | М   |    |             | C  | ON   | ID  |    | G  | D   |    | DA' | ΓΑΕ        | X  |

| Instruction Type                                       | 47                                              | 46  | 45 | 44          | 43      | 42   | 41 | 40   | 39  | 38 | 37          | 36 | 35   | 34  | 33 | 32 | 31  | 30 | 29  | 28         | 27 |

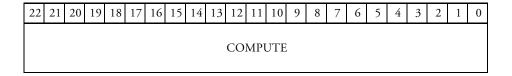

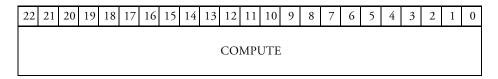

Table 1-14. ADSP-21160 DSP Opcodes (Bits 26-0)

|                                                                                                                        | 22 2 | 21 20 19 18 17 16 | 15 14 13 12 11 10 9 8 | 7   | 6 | 5 4 | 3 | 2 | 1  | 0 |

|------------------------------------------------------------------------------------------------------------------------|------|-------------------|-----------------------|-----|---|-----|---|---|----|---|