## Outline

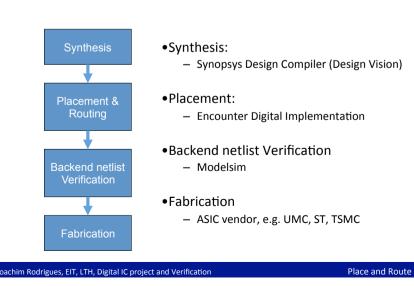

- Backend ASIC Design flow (Physical Design)

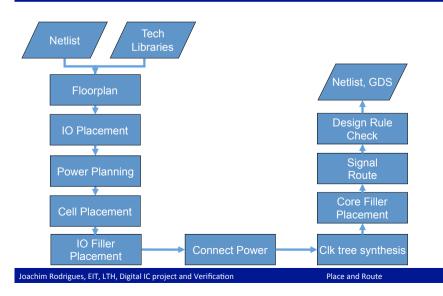

- General steps

- Input files

- Floorplanning

- Placement

- ClockTree-synthesis

- Routing

Joachim Rodrigues, EIT, LTH, Digital IC project and Verification

Place and Route

# **Typical Backend Design Flow**

# SoC Encounter Flow

## SoC Encounter Flow

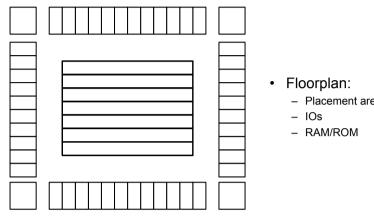

# - Placement area

Place and Route

## SoC Encounter Flow

Joachim Rodrigues, EIT, LTH, Digital IC project and Verification

# SoC Encounter Flow

# SoC Encounter Flow

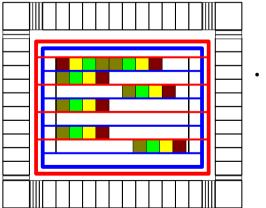

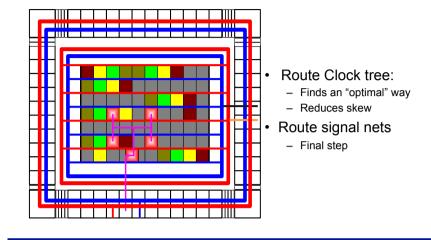

- Place Cells:

- Place all the standard cells into the rows

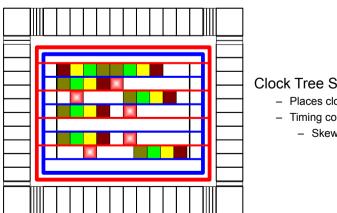

Clock Tree Synthesis:

- Places clock buffers

- Timing constraints - Skew etc

## SoC Encounter Flow

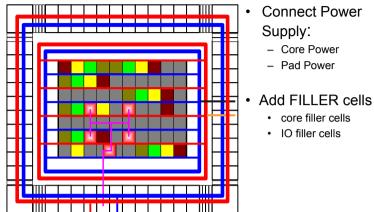

# **Connect Power**

## SoC Encounter Flow

Joachim Rodrigues, EIT, LTH, Digital IC project and Verification

oachim Rodrigues, EIT, LTH, Digital IC project and Verification

Place and Route

Place and Route

Joachim Rodrigues, EIT, LTH, Digital IC project and Verification

Place and Route

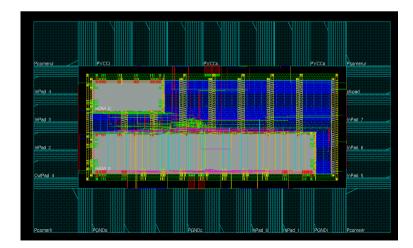

## Demo Layout

## **Technology Description Files**

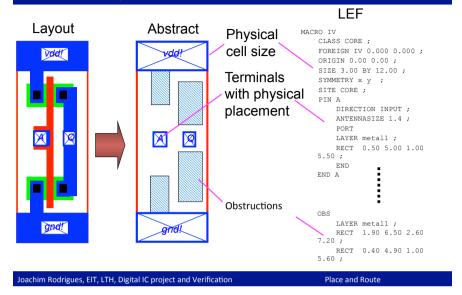

## LEF: Library Exchange Format

- Technology: Design rules, Capacitance, Resistance, Antenna factor, Vias

> header.lef

- Cells & pads: Size, Class, Placement, Pin Information, Obstructions.

- ➤ Standard cell.lef

- ➤ IO.lef

## **LEF-Example:** Inverter

## **Design Description Files**

Enc: Encounter Format

Netlist, Layout

DEF: Design Exchange Format (not used in our flow.

Netlist, Lavout

## Verilog

- Netlist, generated from synthesis tool

Joachim Rodrigues, EIT, LTH, Digital IC project and Verification

Place and Route

## Required Data for PnR (Faraday 130nm)

- LEF: Library Exchange Format

- header.lef

- standardCell.lef : Cell Library

- IO.lef : Pad Library

- memory.lef : custom

- lib/tlf: libraries that contain timing information

- sdc: Synopsys Design Constraint (generated during synthesis). Optional

- Memory: memory.lib

- Design (netlist): your\_design.v

## Starting the SoC Encounter

## inittde dig130x17

## encounter

Remember to maintain the directory hierarchy.

# Design Import

### <u>Design -> Import Design</u>

/usr/local-eit/cad2/far130/syn2010/

| I                       | - Design Import                                                                                 | ·   |

|-------------------------|-------------------------------------------------------------------------------------------------|-----|

|                         | Basic Advanced                                                                                  |     |

| Needs to be             | Vorlog Notlist:                                                                                 |     |

| specified               | Top Cell: I Auto Assign 🕹 By User: MEDIANFILTER_N8                                              |     |

|                         | Timing Libraries:                                                                               |     |

|                         | Max Timing Libraries: foc0h_a33_133_generic_io_wc.lib fsc0h_d_sc_wc.lib                         |     |

|                         | Min Timing Libraries: foc0h_a33_t33_generic_io_bc.lib foc0l_a33_t33_generic_io_bc.lib           |     |

|                         | Common Timing Libraries:                                                                        |     |

|                         |                                                                                                 | _   |

| Will be                 | LEF Files: header6m21_V55.lef fsc0h_d_sc.lef foc0h_a33_t33_generic_io.lef SYUD130_64X8X1CM2.lef |     |

|                         | Timing Constraint File: medfilt.sdc                                                             |     |

| provided                | IO Assignment File: MedFilt.io                                                                  |     |

|                         | QK Seve Losd Cancel Help                                                                        |     |

| chim Rodrigues, EIT, LT | H, Digital IC project and Verification Place and Ro                                             | ute |

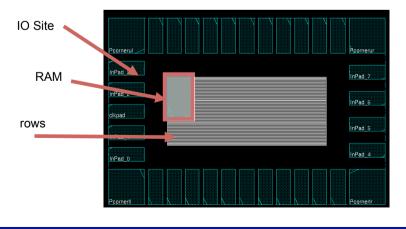

## Floorplan

- A starting floorplan is created (required area is estimated by the tool)

- Global and detailed routing grids are created

- The core rows are created

- Sites for IOs are created

- IO and block to core distance is defined by the user

Joachim Rodrigues, EIT, LTH, Digital IC project and Verification

Place and Route

# Floorplanning

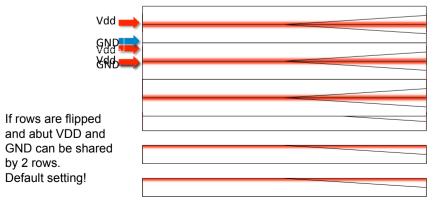

## Core Rows

## Floorplan Setup

## <u>Floorplan -> Specify Floorplan</u>

|                       | — Specify Floorplan 🔹 🗖                                   |

|-----------------------|-----------------------------------------------------------|

|                       | Basic Advanced                                            |

|                       | Design Dimensions                                         |

|                       | Specify By:  Size  Die/IO/Core Coordinates                |

|                       | ◆ Core Size by: ◆ Aspect Ratio: Ratio (H/W): 0.4364714€   |

|                       | Core Utilization: 0.089606                                |

| Core utilization      | Cell Utilization: 0.0087                                  |

|                       | Dimension: Width: 674.5                                   |

|                       | Height: 294.4                                             |

|                       | Die Size by: Width: 1178.5                                |

|                       | Height: 798.4                                             |

|                       | Core Margins by: 🔶 Core to IO Boundary                    |

|                       | 🔶 Core to Die Boundary                                    |

| IO to core distance 🛑 | to Left: 100.0 Core to Top: 100.0                         |

|                       | Core to Right: 100.0 Core to Bottom: 100.0                |

|                       | Die Size Calculation Use: 💊 Max IO Height 🔶 Min IO Height |

|                       | Floorplan Origin at: 🔶 Lower Left Corner 🕹 Center         |

|                       | Unit: Micron                                              |

|                       |                                                           |

|                       | OK <u>A</u> pply <u>C</u> ancel <u>H</u> elp              |

|                       |                                                           |

## **IO Placement**

- Specify location/orientation of pads

- Input, output

- core-power, pad-power

- Recommendation:

- Put core power supply on top or botton

- Use gaps in the pad frame for additional power supply.

- !No CORE power supply at the corners!

- The more supplies the better

#### achim Rodrigues, EIT, LTH, Digital IC project and Verification

#### Place and Route

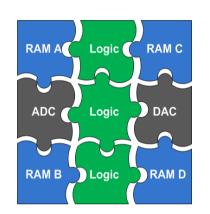

## **Block Placement**

Joachim Rodrigues, EIT, LTH, Digital IC project and Verification

Place and Route

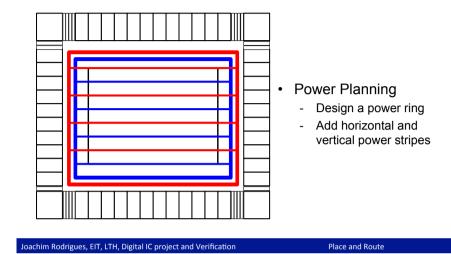

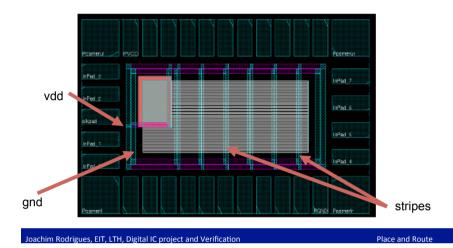

## Power Rings

- Power paths are planned and modified before routing

- Creation of power rings that surround all blocks and core.

- Creation of stripes over rows

- Connects rings, stripes and pads

## Power Rings cont'd

## **Connecting Power (sRoute)**

#### between

- IO power pins within IO rows

- CORE ring wires and the IO power pins

- stripes and core rings

- block power pins and the CORE ring wires

### Route-> Special Route

#### Joachim Rodrigues, EIT, LTH, Digital IC project and Verification

Place and Route

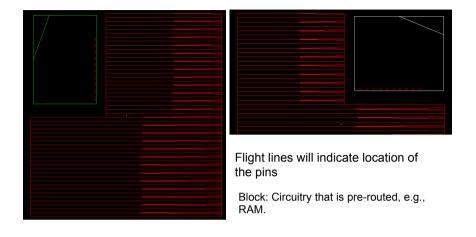

## **Cell Placement**

- · Initial cell placement

- Moves, swaps changes orientation of cells to minimize required wire length

- · Optimizes for wire length and net crossings

- A post CTS optimization may be carried out to optimize the design

#### Place -> Standard Cells

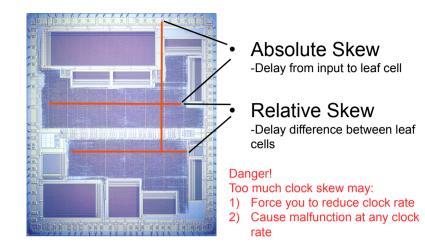

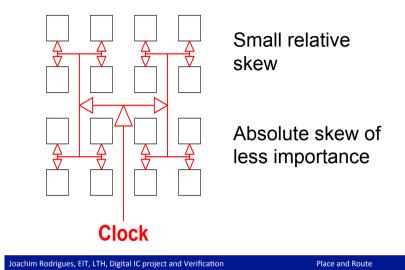

## Clock Tree Synthesis

- Clockpad and output need to defined in a specification file.

- clockpad/O

- Clock tree is synthesized and routed with highest priority to minimize clock skew.

## **Clock Skew**

## **Distributed Buffers in H-tree**

## CTS commands

Joachim Rodrigues, EIT, LTH, Digital IC project and Verification

create\_clock -period value -name clk\_name

-add [get ports clk]

• Generate Clock tree specification createClockTreeSpec -output file name.ctstch

-routeClknet -buffer buffer\_list

Specify CTS file and synthesize clock tree.

specifyClockTree -clkfile file\_name.ctstch

clockDesign -specFile file\_name.ctstch -clk clk\_name

deleteTrialRoute

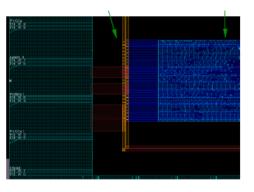

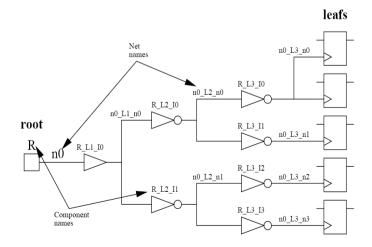

## Synthesized Clock tree

#### Clock buffers are placed in the core row gaps

Place and Route

Place and Route

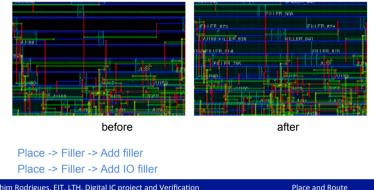

## Core filler cell

Core filler cells ensure the continuity of power/ground rails and N+/P+ wells in the row.

Filler cells will close any gap it is important to perform CTS before filler cell placement.

loachim Rodrigues, EIT, LTH, Digital IC project and Verification

## Verification and Tapeout

## Verification (in SoCEnc)

- Connectivity, Antenna ....

## Export

- Verilog (netlist) Post-layout simulation

- sdf (timina)

- GDS II + tapeout

#### Verify

pachim Rodrigues, EIT, LTH, Digital IC project and Verification

Place and Route

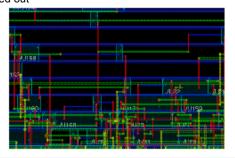

## **Signal Routing**

- Signal routing

- Connects cells according to netlist

- Metal wires are connected over several layers

- Routing time is strongly dependent on the design complexity

Route -> Nano Route

m Rodrigues, EIT, LTH, Digital IC project and Verificatio

Place and Route

# **Routing Script**

- Each command is automatically written in a script file encounter.cmd

- Script needs to be trimmed (remove unnecessary commands)

- Easy to change parameters

- Can be reused with modifications

- Time to do PnR iteratively is reduced

- Serves as documentation and makes it possible to repeat the flow

pachim Rodrigues, EIT, LTH, Digital IC project and Verification

# What's next?

- Continue in the lab with Assignment 1

- The design needs to be taken through

- Simulation, including post-synthesis

- Synthesis

- Place and Route

Joachim Rodrigues, EIT, LTH, Digital IC project and Verification

Place and Route