### Contents

- This document presents the project which will be offered in the digital track of ETIN35

- Please get an idea of the different projects and contact the project supervisor for more information

- By March 13th you need to send an email to Joachim Rodrigues where you state:

- 1st preference

- 2nd preference

- Project partner

## **Projects**

- Channel Estimation-Steffen Malkowsky

- Successive Interference Cancellation -Steffen Malkowsky

- QR Decomposition- Hemanth Prabhu

- RISC processor- Michal Stala

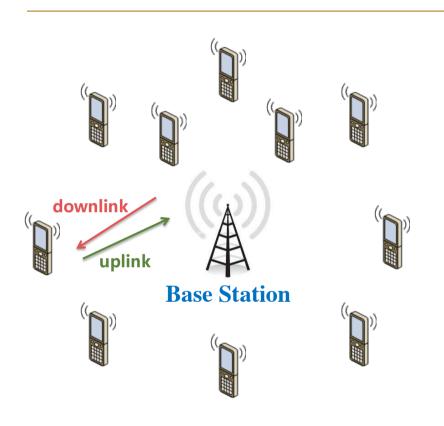

## **System View I**

$$y_{100\times 1} = H_{100\times 10} * s_{10\times 1} + n_{100\times 1}$$

## **System View II**

# Channel Estimation (one user) I - Steffen Malkowsky

1 sample per input valid, every 10<sup>th</sup> subcarrier

Pilot symbol

Overall 1200 subcarriers (120 estimates, interpolate rest)

Model input valid as random

Perform least square, i.e., divide by pilot

Store estimates in memories

# Channel Estimation (one user) II - Steffen Malkowsky

#### Grade 3:

On-the-fly linear interpolation between the estimates

### Grade 4/5:

Compare more advanced on-the-fly interpolation, e.g. second order, cubic spline or Lagrangian interpolation

Optimize throughput

Do something better than Least-squares

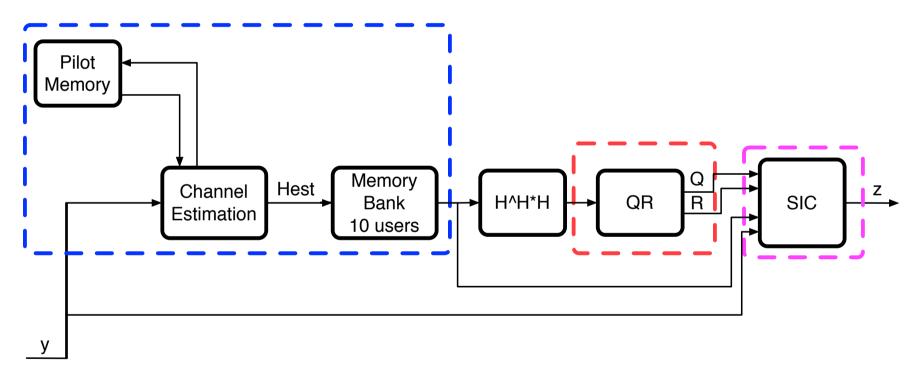

# Successive Interference Cancellation I - Steffen Malkowsky

Assume Q, R and Hest matrices are given at input (pre-buffer if necessary)

Vector y is received

Build pseudoinverse of H and calculate first symbol

Subtract symbol from received values and calculate next symbol

10 users

Hard detection

# **Successive Interference Cancellation II- Steffen Malkowsky**

#### Grade (4)/5:

Build Matlab model for SIC (with help)

Generate input values for Q, R and H in Matlab

Implement in VHDL

Optimize throughput

### **QR** Decomposition

### - Hemanth Prabhu

- In this project the students will design a QR-decomposition accelerator.

- QRD is a well known linear algebra method, mainly used for solving linear equations.

- It is extensively used in signal processing and communication systems.

$$A = QR, \ Q = (q_1 \dots q_n), \ R = \begin{pmatrix} r_{11} & r_{12} & \dots & r_{1n} \\ 0 & r_{22} & & r_{2n} \\ \vdots & & \ddots & \vdots \\ 0 & & 0 & r_{nn} \end{pmatrix}$$

## **QR** Decomposition

### - Hemanth Prabhu

- Student need to perform QRD using "Given's Rotation".

- Use "CORDIC" processing elements to perform arithmetic's.

- Systolic Array

- Highly parallel architecture

- Easy implementation

## **QR** Decomposition

### - Hemanth Prabhu

#### • Grade 4:

Floating point model in Matlab.

Fixed point model in CatapultC or C++ (optional)

Cordic Processing elements for Given's Rotation

#### • Grade 5 :

Fully working systolic array based Given's Rotation.

Area/power comparison with state-of-art implementation.

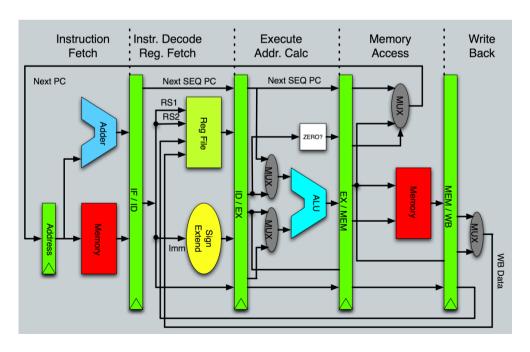

# Mini-MIPS project (Michal Stala)

- 32-bit RISC with a subset of MIPS instructions.

- Grade 3: Fully verified pipelined Mini-MIPS.

- Alt 1

- » Grade 4 : Xilinx Ethernet I/O

- » Grade 5: Extra functionality (accelerator or extended instruction set)

- Alt 2

- » Grade 4/5 : Viterbi decoder in Catapult

- Alt 3

- » Grade 4/5 : open for suggestions (Multicore?)

- Prerequisite course:

- EITF35 Introduction to Structured VLSI Design

- EITF20 Computer Architecture

## Mandatory tasks

- Task 1: behavior modeling

- Task 2: synthesizable pipelined implementation

- Task 3: P&R in 65nm CMOS

- Task 4: Verification in FPGA