# EITF35: Introduction to Structured VLSI Design

# Introduction to FPGA design

Rakesh Gangarajaiah

Rakesh.gangarajaiah@eit.lth.se

Slides from Chenxin Zhang and Steffan Malkowsky

- What is FPGA?

- Field Programmable Gate Array

- What is FPGA?

- Field Programmable Gate Array

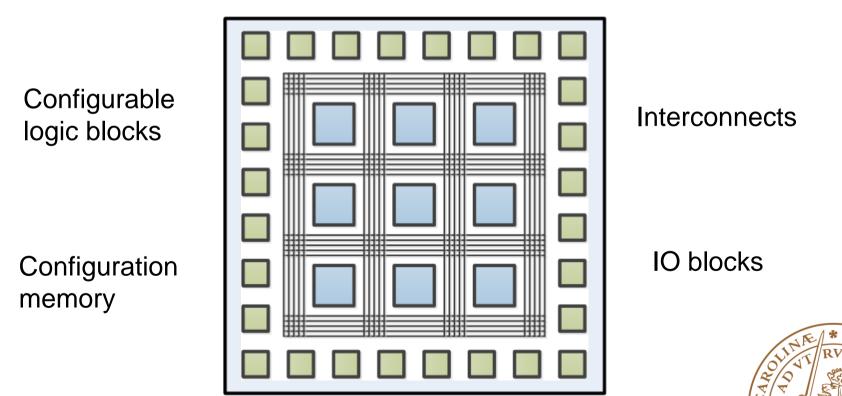

- Configurable logic blocks + interconnects + IOs + memory

- Why do we use it?

- High performance & Flexible

- Shorter time to market

- What is FPGA?

- Field Programmable Gate Array

- Configurable logic blocks + interconnects + IOs + memory

- Why do we use it?

- High performance & Flexible

- Shorter time to market

- Where do we use it?

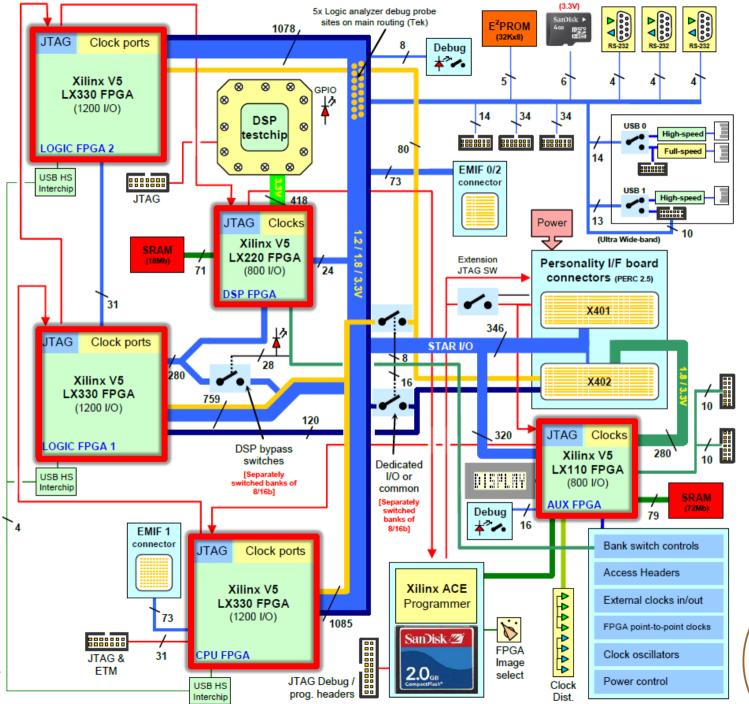

- Prototyping

- Computer vision

- Medical imaging

- Software-defined radio

#### **FPGA vs. Microprocessor**

|                                 | Intel Itanium 2                                  | Xilinx Virtex-II Pro<br>(XC2VP100)     |  |  |

|---------------------------------|--------------------------------------------------|----------------------------------------|--|--|

| Technology                      | 0.13 µm                                          | 0.13 µm                                |  |  |

| Clock speed                     | 1.6 GHz                                          | 180 MHz                                |  |  |

| Internal memory bandwidth       | 102 GBytes/S                                     | 7.5 TBytes/S                           |  |  |

| # Processing units              | 5 FPU (2 MACs+1 FPU)<br>6 MMU<br>6 Integer units | 212 FPU or<br>300+Integer units or<br> |  |  |

| Power consumption               | 130 W                                            | 15 W                                   |  |  |

| Peak performance                | 8 GFLOPs                                         | 38 GFLOPs                              |  |  |

| Sustained performance           | ~2GFLOPs                                         | ~19 GFLOPs                             |  |  |

| IO/External memory<br>bandwidth | 6.4 GBytes/S                                     | 67 GBytes/S                            |  |  |

|                                 |                                                  | (Courtesy: Nallatech)                  |  |  |

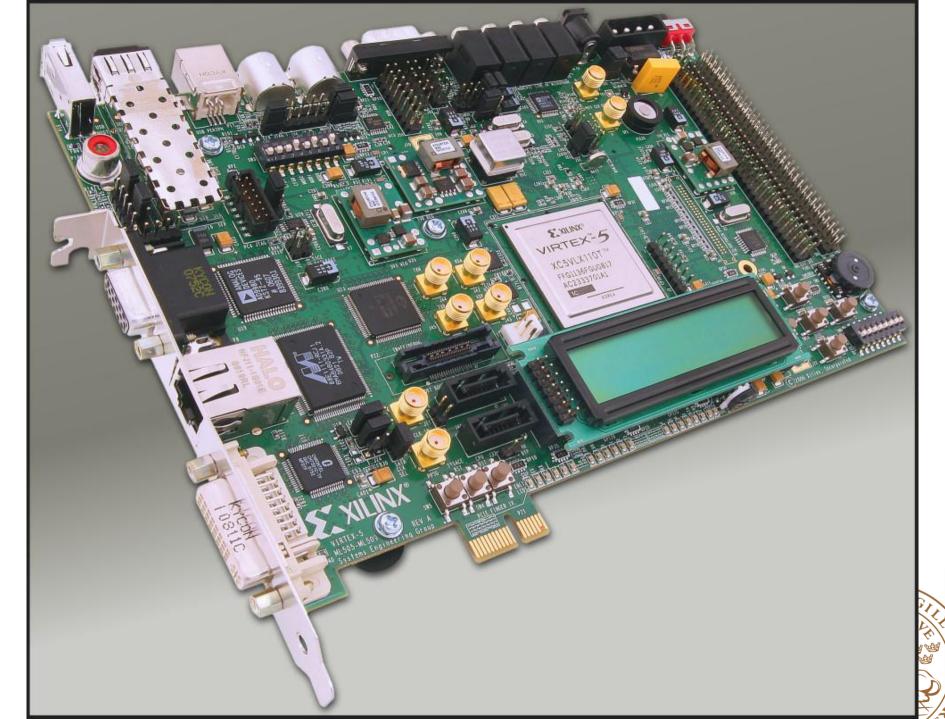

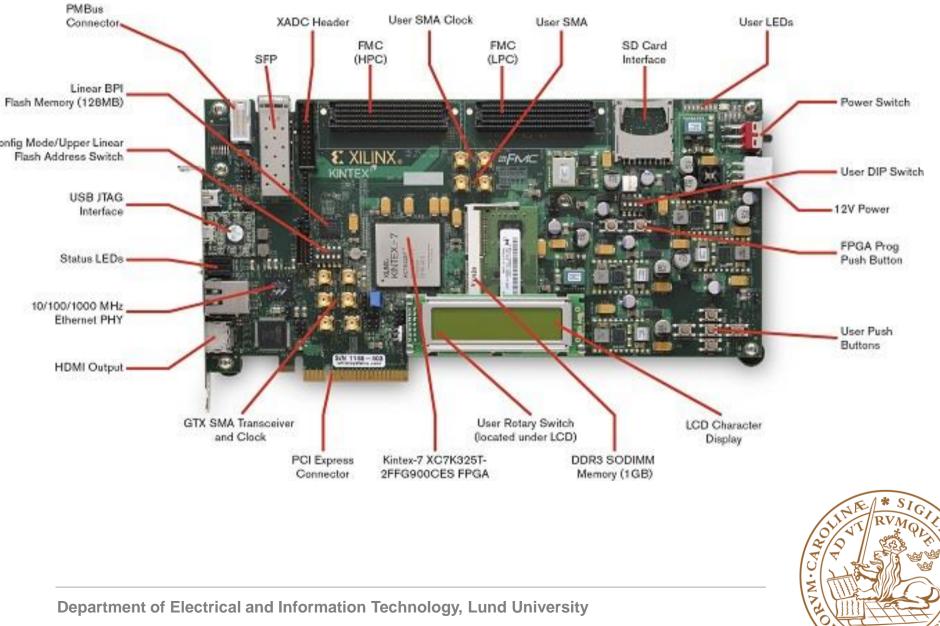

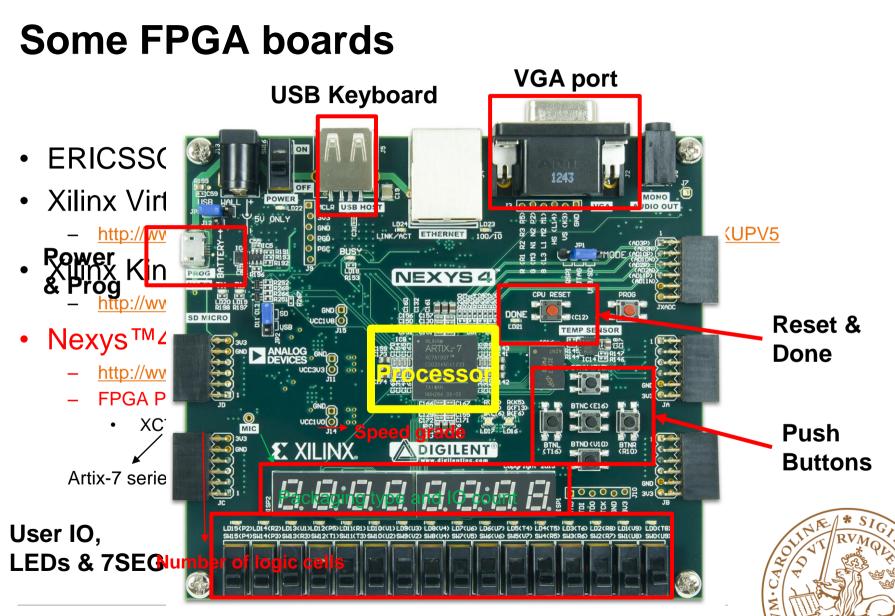

## **FPGA** devices

- Manufactures:

- Xilinx: Virtex, Kintex, Artix, Spartan

- Altera: Cyclone, Arria, Stratix

- Lattice Semiconductor: flash, low power

- Microsemi (Actel): antifuse, mix-signal

- Achronix: high speed

- QuickLogic: application-specific (handheld)

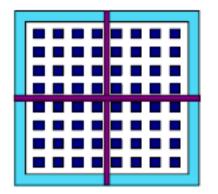

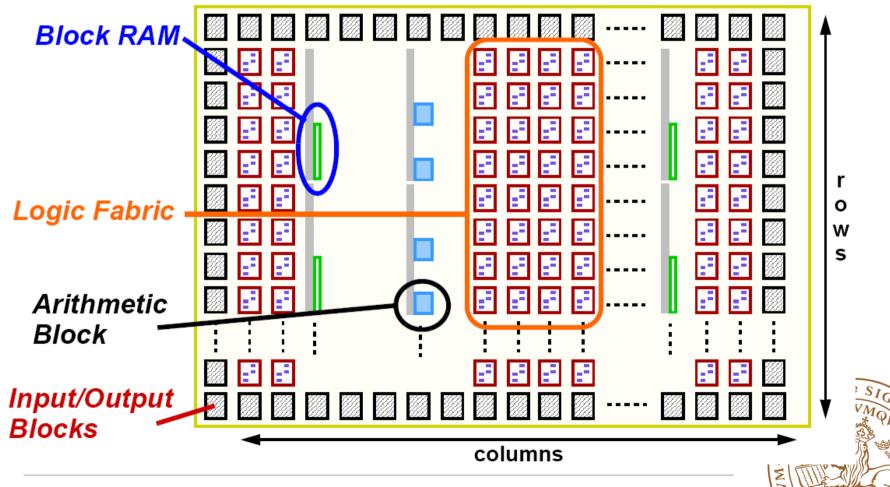

# **FPGA** architectures

- Early FPGAs

- N x N array of unit cells (CLB + routing)

- Configurable Logic Blocks

- Special routing along center axis

- Next Generation FPGAs

- M x N unit cells

- Small block RAMs around edges

- More recent FPGAs

- Added block RAM arrays

- Added multiplier cores

- Added processor cores

# **FPGA** architecture trends

- Memories

- Single & Dual-port RAMs

- Digital Signal Processor Engines

- Embedded Processors

- Hardcore (dedicated processors)

- Soft core (synthesized from a HDL)

- High speed/performance I/O connectivity

- PCIe interface block

- I/O transceiver

- Gigabit Ethernet

- HPC and LPC interfaces

- Clock management blocks

# **Programming technology**

| Feature                | ature SRAM Antifuse        |                                | Flash/E2PROM                      |  |

|------------------------|----------------------------|--------------------------------|-----------------------------------|--|

| Technology             | State-of-the-art           | One or more generations behind | One or more generations behind    |  |

| Reprogrammable         | Yes No (in system)         |                                | Yes<br>(in system or offline)     |  |

| Reprogramming<br>speed | Fast                       |                                | 3x slower than SRAM               |  |

| Volatile               | Yes                        | No                             | No                                |  |

| Instant-on             | No                         | Yes                            | Yes                               |  |

| Security               | Acceptable                 | Very Good                      | Very Good                         |  |

| Size of Config. Cell   | Large<br>(Six transistors) | Very small                     | Medium-small<br>(Two transistors) |  |

| Power consumption      | Medium                     | Low                            | Medium                            |  |

|                        |                            |                                |                                   |  |

とう

#### Xilinx FPGA architecture

**SRAM-based FPGA**

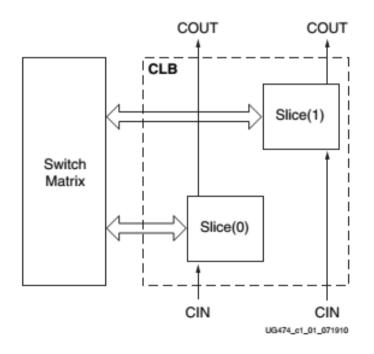

# Configurable logic block (CLB) (I)

• One CLB contains two slices (7 series Xilinx FPGA)

# Configurable logic block (CLB) (II)

- One CLB contains two slices

- Each slice:

- Four Look-up tables (LUTs)

- Eight D Flip-Flops (DFFs)

- Multiplexers and arithmetic gates

- Carry logic

- 2/3 of all slices are SLICEL and 1/3 SLICEM

- Distributed RAM and Shift registers in SLICEM

- Higher Interconnect density in 7 series

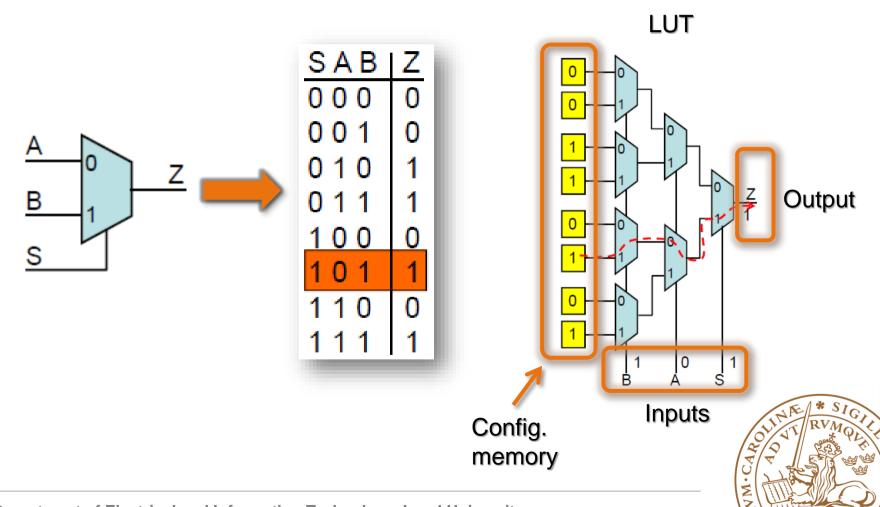

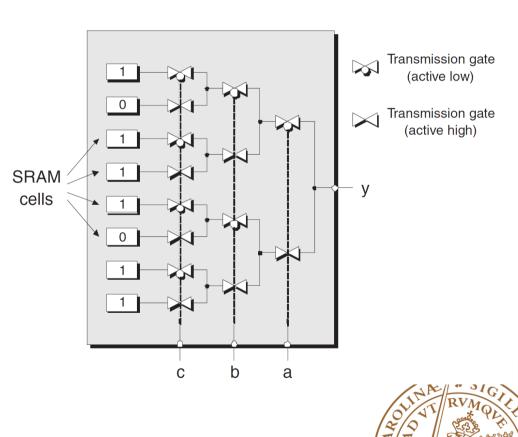

# Look-up table (LUT) (I)

# Look-up table (LUT) (II)

- Inputs are used as a pointer into a LUT.

- Decoded using a hierarchy of transmissiongate MUXs.

- Transmission-gate: "pass" or "high-impedance".

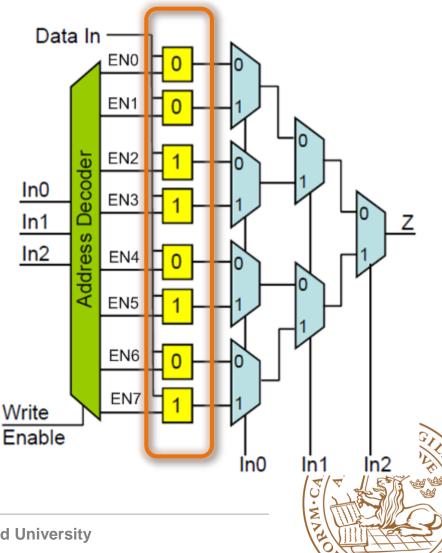

#### LUT based RAM (Distributed RAM)

- Normal LUT performs "read" operation.

- For "write" operation, address decoders + write enable.

- Can be concatenated to created larger RAMs.

- Can also be used as shift registers (some of the LUTs).

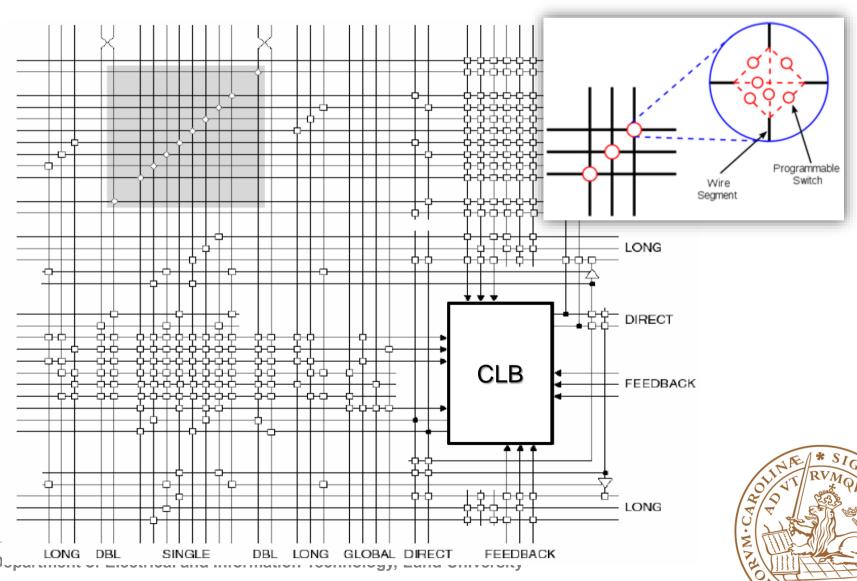

#### **Programmable Interconnects (I)**

#### **Programmable Interconnects (II)**

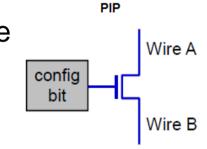

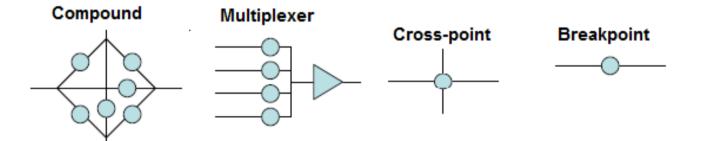

- Programmable swich, also called programmable interconnect points (PIP).

- Implemented using transmission gates.

- Several types of PIPs:

## Xilinx Artix-7 FPGA

#### • XC7A100T:

- ~8000 CLBs

- ~5000 kb of BRAMs

- ~1200 Kb Distributed RAM

- 240 DSP units

| Table 1-1: | Artix-7 FPGA | <b>CLB Resources</b> | (Cont'd) |

|------------|--------------|----------------------|----------|

|------------|--------------|----------------------|----------|

| Device | Slices <sup>(1)</sup> | SLICEL | SLICEM | 6-input<br>LUTs | Distributed RAM<br>(Kb) | Shift<br>Register<br>(Kb) | Flip-Flops |

|--------|-----------------------|--------|--------|-----------------|-------------------------|---------------------------|------------|

| 7A50T  | 8,150                 | 5,750  | 2,400  | 32,600          | 600                     | 300                       | 65,200     |

| 7A75T  | 11,800 <sup>(2)</sup> | 8,232  | 3,568  | 47,200          | 892                     | 446                       | 94,400     |

| 7A100T | 15,850                | 11,100 | 4,750  | 63,400          | 1,188                   | 594                       | 126,800    |

| 7A200T | 33,650                | 22,100 | 11,550 | 134,600         | 2,888                   | 1,444                     | 269,200    |

#### Notes:

1. Each 7 series FPGA slice contains four LUTs and eight flip-flops; only SLICEMs can use their LUTs as distributed RAM or SRLs.

2. Number of slices corresponding to the number of LUTs and flip-flops supported in the device.

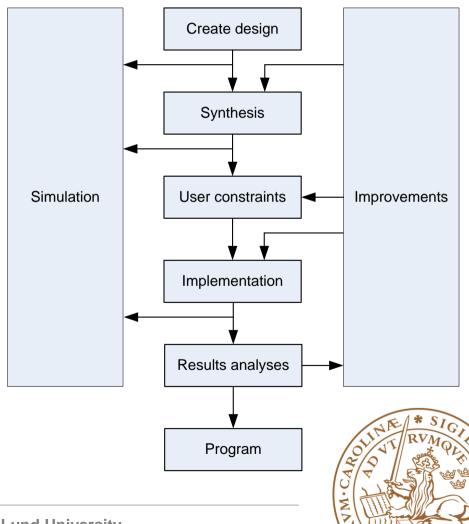

# **FPGA Design flow**

- Synthesis

- Parses HDL design

- Infers Xilinx primitives

- Generates design netlist

- Translate

- Merges incoming netlists and constraints into a design file

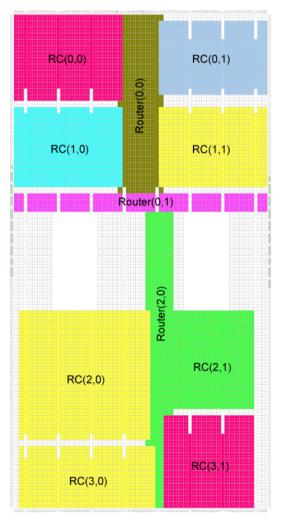

- Map

- Maps (places) design into the available resources on the target device

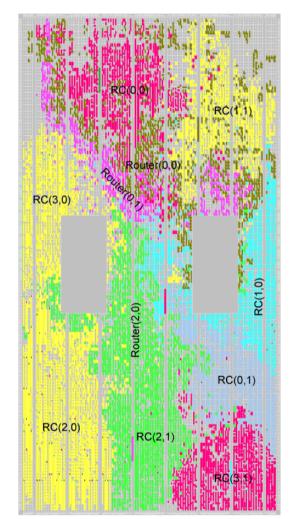

- Place and Route

- Places and routes design

#### Design constraints

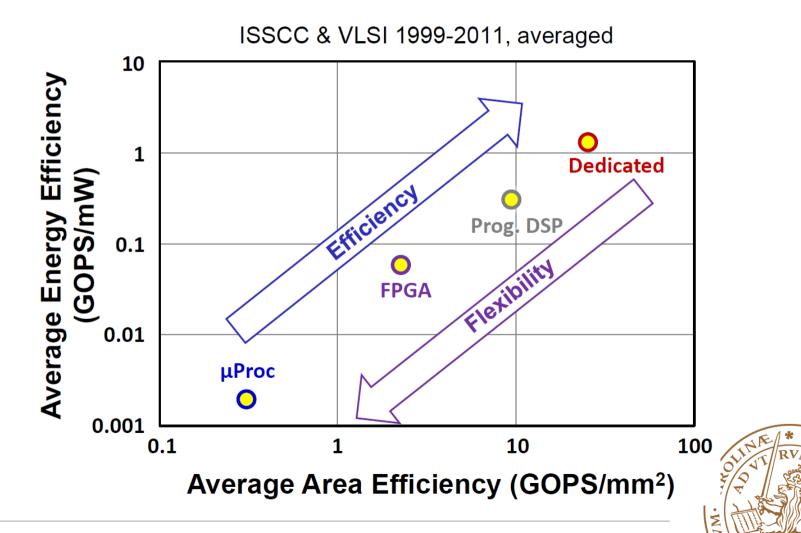

#### **Are FPGAs perfect?**

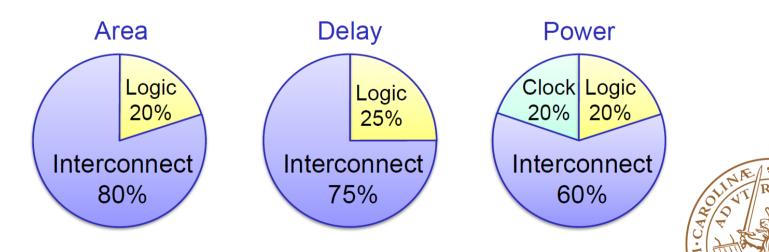

#### **FPGAs** are inefficient

- Compared to ASICs, penalties in FPGAs:

- Area: 17 54x

- Speed: 3 7x

- Power: 6 62x

#### Main culprit: INTERCONNECT!

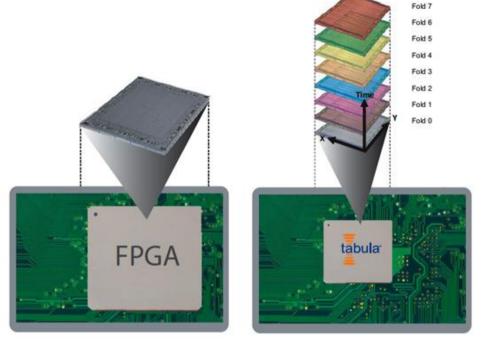

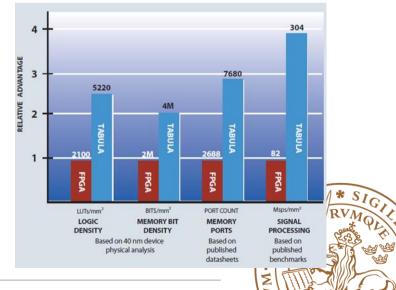

# **Tabula Spacetime**

- Ultra-rapid full/partial reconfiguration with makes it possible to fold more functions onto the same hardware: multi-GHz rates

- Their claim:

- 2.5x logic density

- 3.7x DSP performance

#### www.tabula.com

# **Coarse-grained reconfigurable architecture**

- Currently in FPGA

- Dedicated building blocks: multiplier, DSP core, processor

- Partial configuration

- Moving torwards coarse-grained architecture:

- Block-level instead of bit manipulations

- Lower area and power consumption

- High-level programming: e.g. xilinx vivado

- Run-time configuration

# **Introduction to Xilinx Software**

- Xilinx Vivado

- Integrated tool for design, simulation, synthesis, implementation and FPGA debug

- IP generator

- Tool used to instantiate Xilinx and third-party IPs into your design

- Clock generator, Dividers, BRAM etc.

- Integrated Logic Analyzer

- Used for real time debugging

# **Introduction to Xilinx Software**

• Xilinx Vivado

#### References

- Clive "Max" Maxfield, "The Design Warrior's Guide to FPGAs – Devices, Tools and Flows", ELSEVIER, 2004.

- Bill Jason P. Tomas, "Introduction to Field Programmable Gate Arrays (FPGAs)".

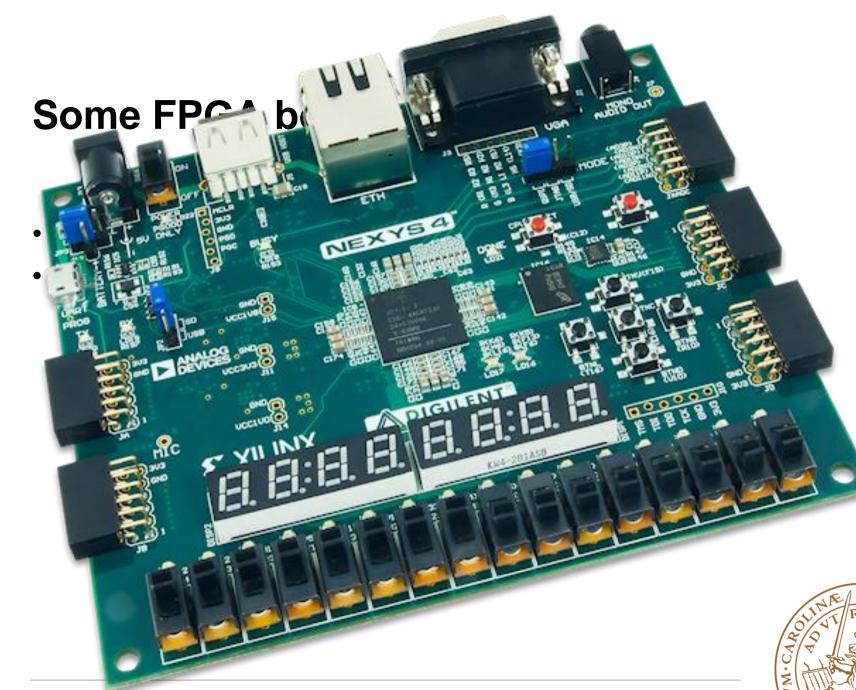

- Xilinx, "Nexys-4 FPGA Family Data Sheet".