### Outline

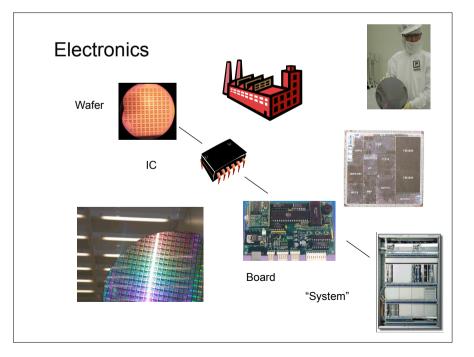

- <u>Electronics</u>

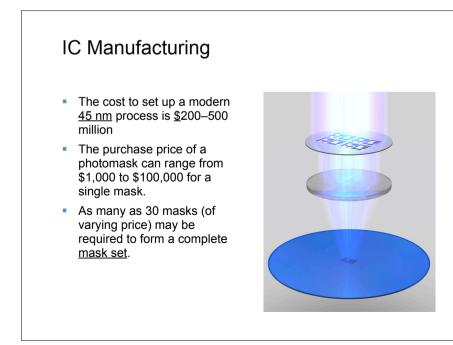

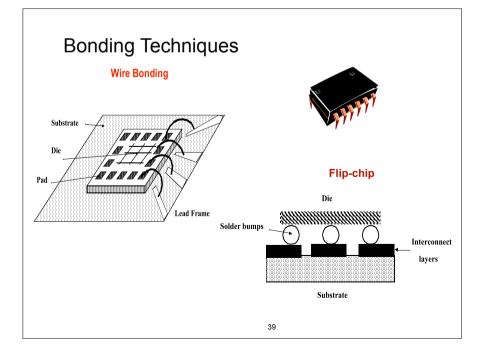

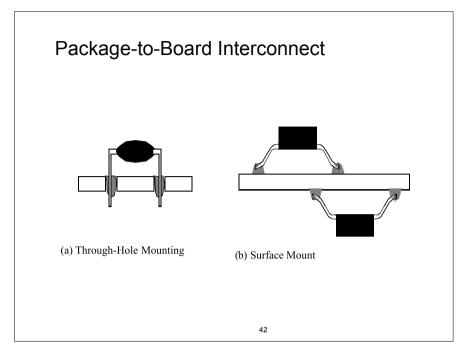

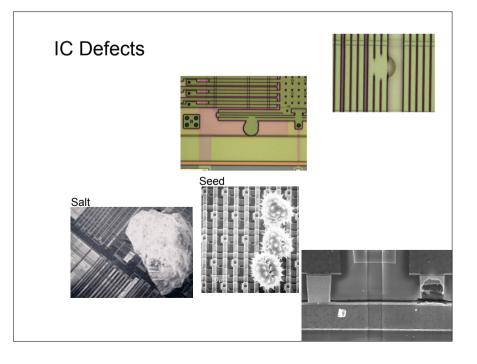

- Manufacturing

- Test, diagnosis, and verification

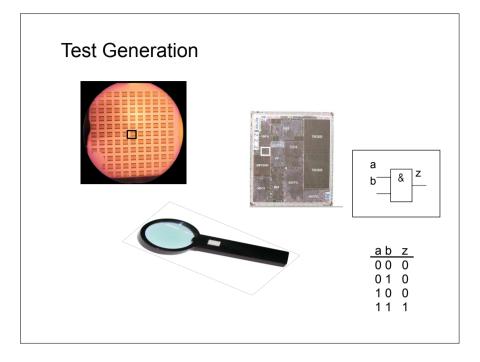

- Test generation

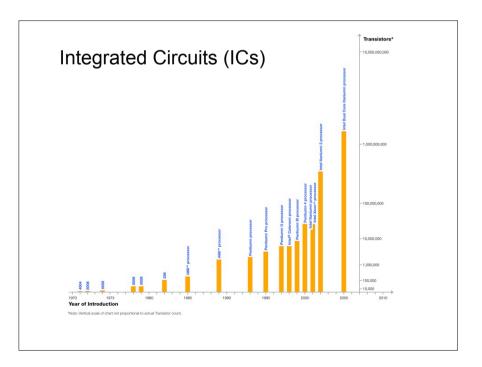

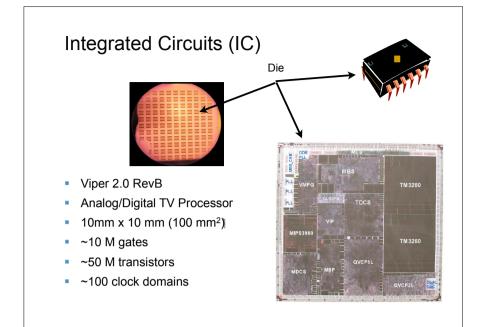

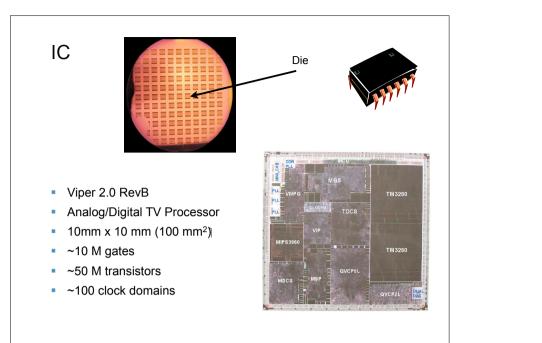

### Integrated Circuits (ICs)

- Small Scale Integration (SSI), early 1960s example, Philips TAA320 had two transistors

- Medium Scale Integration (MSI), late 1960s example, Intel 4004 had 2300 transistors

- Large Scale Integration (LSI), mid-1970s example, Intel 8008 had 4500 transistors

- Very-Large Scale Integration (VLSI), 1980s, example, Intel 80286, 134000 transistors

- Ultra-Large Scale Integration (ULSI), now, more than 1 million transistors

- Wafer-scale integration (WSI)

- System-on-a-chip

- Three dimensional integrated circuits (3D-ICs)

### Outline

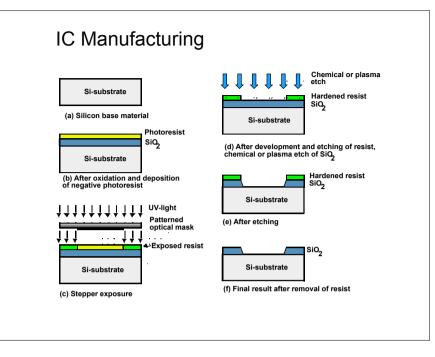

- Electronics

- <u>Manufacturing</u>

- Test, diagnosis, and verification

- Test generation

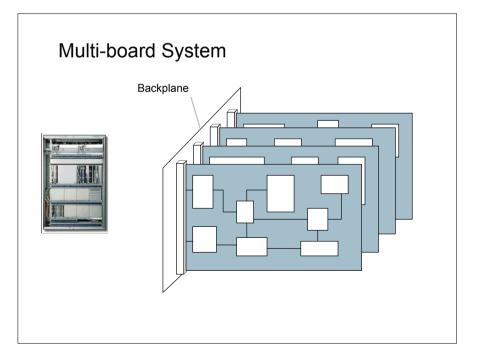

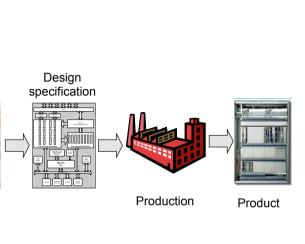

### Design specifica

Design

Making Electronic Products

# Outline Electronics Manufacturing Test diagnosis, and verification Test generation

| B Defects             |                          |  |  |

|-----------------------|--------------------------|--|--|

| Defect classes        | Occurrence frequency (%) |  |  |

| Shorts                | 51                       |  |  |

| Opens                 | 1                        |  |  |

| Missing components    | 6                        |  |  |

| Wrong components      | 13                       |  |  |

| Reversed components   | 6                        |  |  |

| Bent leads            | 8                        |  |  |

| Analog specifications | 5                        |  |  |

| Digital logic         | 5                        |  |  |

| Performance (timing)  | 5                        |  |  |

Ref.: J. Bateson, In-Circuit Testing, Van Nostrand Reinhold, 1985.

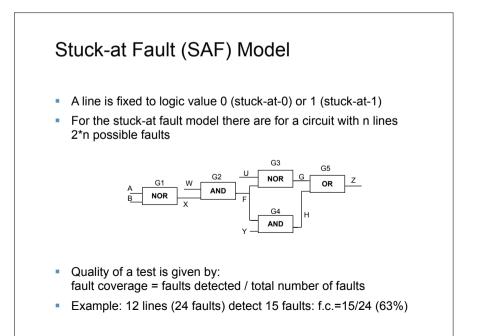

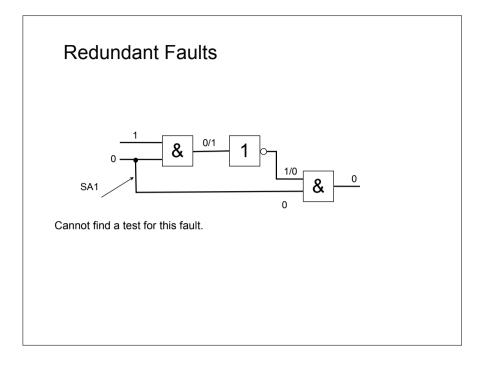

### Fault Models

- Real defects too numerous and often not analyzable

- A fault model identifies targets for testing

- A fault model makes analysis possible

- Effectiveness measurable by experiments

- A defect manifests itself as a fault

- A fault is modeled by a fault model

- Example of fault models:

- Stuck-at Fault, Bridging Fault, Shorts (Resistive shorts), Opens, Delay Faults, Transient Fault

- So far stuck-at fault model is the most used one:

- Motivations: Simple and covers quite well possible defects

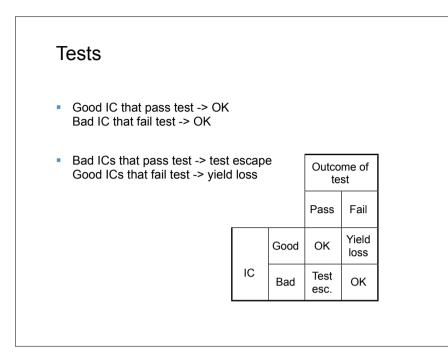

### Verification, Test and Diagnosis

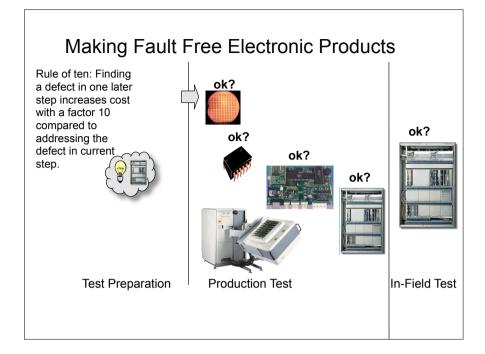

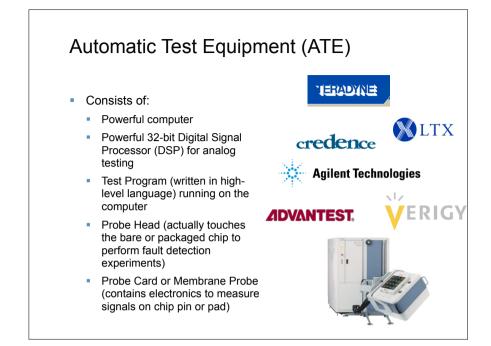

- <u>Verification</u> is to verify the correctness of the design. It is performed through simulation, hardware emulation, or formal methods. It is performed once prior to manufacturing. Responsible for quality of design.

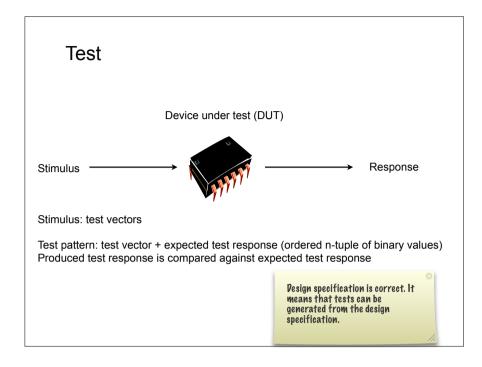

- <u>Test</u> verifies the correctness of manufactured hardware. Test is a two-part process:

- Test generation: software process executed once during design, and

- Test application: electrical tests applied to hardware. Test application performed on every manufactured device. Responsible for quality of devices.

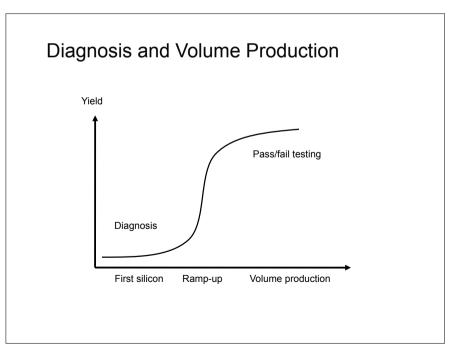

- <u>Diagnosis</u>: Identification of a specific fault that is present on DUT.

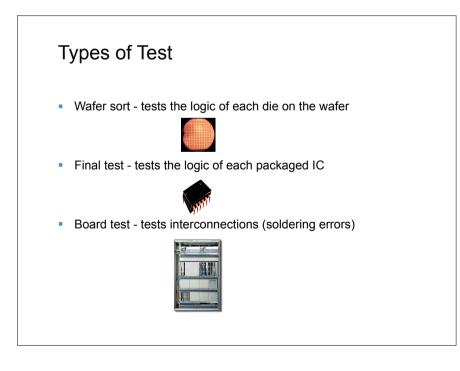

### Types of Test

- Production

- Wafer sort (or probe)

- Final test (package) Test of pa

- Acceptance

- Sample

- Go/No-go

- Characterization (performance)

- Stress screening (burn-in) At h out

- Diagnostic (repair)

- On-line

Test of die on the wafer Test of packaged chips Test to demonstrate compliance with purchaser's requirements Test some but not all parts Pass or fail test Test actual parameters At high temperature to get wear-Test to pinpoint defective part Test while system is in operation

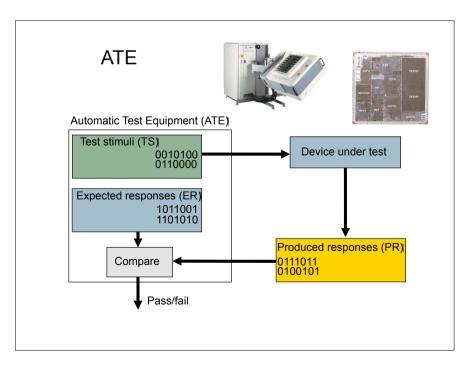

### **Objective with Test**

- Specify the test vector

- Determine correct response (expected response)

- Evaluate cost of test (# patterns related to cost)

- Evaluate quality of test

- Fault coverage = No of faults detected / No. faults modeled

- Yield = Number of good parts / Total number of tested parts

## Outline Electronics Manufacturing Test, diagnosis, and verification Test generation

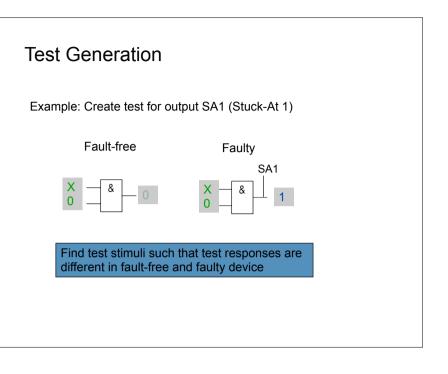

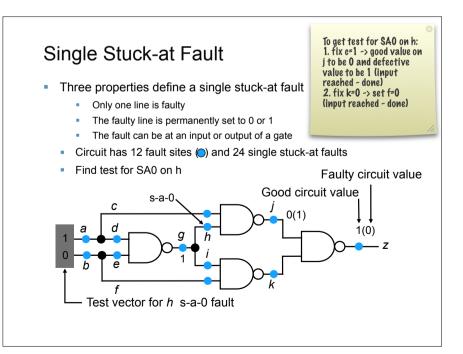

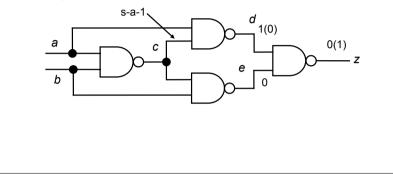

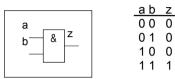

### Single Stuck-at Fault

- Let us generate a s-a-1 on the same line

- To get c=0, set a=1 and b=1

- To get fault effect on d (1/0), set a=1

- To get fault effect on z (0/1), set e=0

- To get e=0, set b=1 and c=1 (but c=0 see above)

### Stuck-at Faults

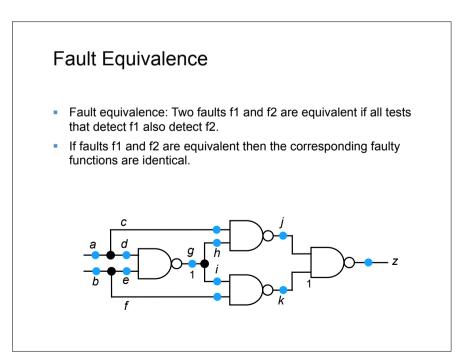

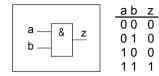

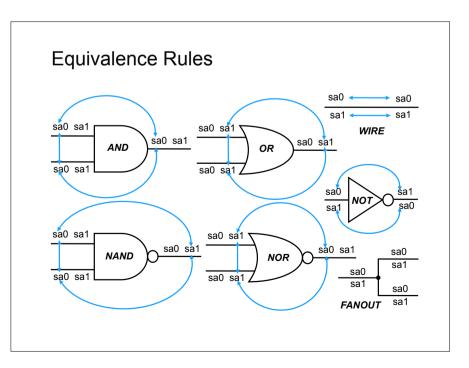

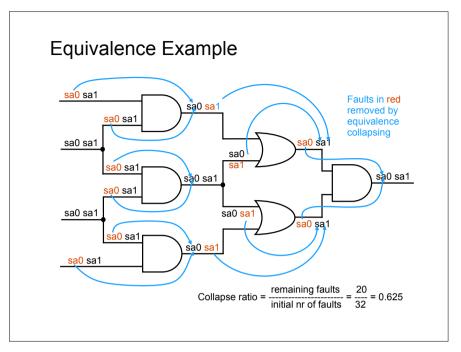

Minimize fault list through: 4 exhaustively generated vectors but only 3 deterministic vectors needed: <u>Fault equivalence</u>

Value fault free/faulty (v/v<sub>f</sub>)

Stuck-at 0 on a: a=1/0,  $b=1 \rightarrow z=1/0$  //vector (stimulus) 11

Stuck-at 0 on b: b=1/0,  $a=1 \rightarrow z=1/0$  //vector (stimulus) 11

Stuck-at 0 on z: b=1,  $a=1 \rightarrow z=1/0$  //vector (stimulus) 11

Stuck-at 1 on a: a=0/1,  $b=1 \rightarrow z=0/1$  //vector (stimulus) 01

Stuck-at 1 on b: b=0/1,  $a=1 \rightarrow z=0/1$  //vector (stimulus) 10

Stuck-at 1 on z: a=0,  $b=x \rightarrow z=0/1$  //vector (stimulus) 0x or x0

### Exhaustive Test Generation Deterministic Test Generation Random Test Generation Pseudo-random Test Generation

### **Exhaustive Test Generation**

- Try all possible alternatives.

- For a 2-input design, 2<sup>2</sup> (4 vectors are needed).

- For a 30-input pin design, 2<sup>30</sup> (1073741824 vectors are needed)

- I vectors per second and we know that there are 60\*60\*24\*365=31536000 seconds in a year

- 2<sup>30</sup> / 31536000 = 34 years

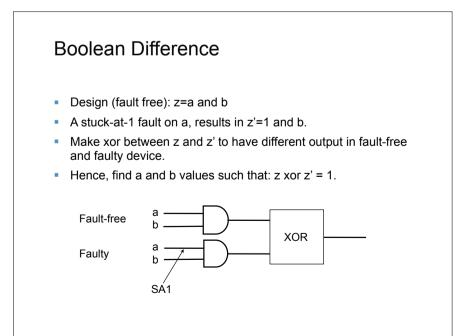

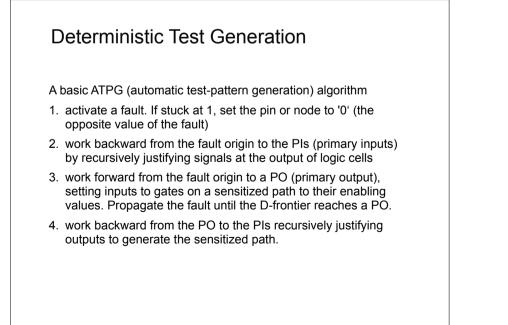

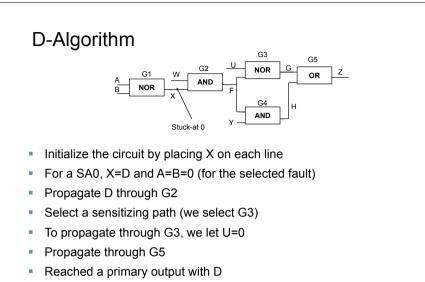

### **Deterministic Test Generation** While fault coverage < desired limit { Select an uncovered fault f Generate test for the fault f Evaluate fault coverage Needed functions to generate a test: Excite (provoke) the fault ÷., Sensitize (propagate) the results to primary outputs . Justify other values in the circuit ATPG: D-algorithm ÷., Path-Oriented Decision-Making (PODEM) Fanout-oriented Test Generation (FAN) Structure-oriented cost-reducing automatic test pattern generation (SOCRATES)

### **D**-notation OR D Five-valued algebra (0,1,X,D,D') 0 1 D Х . 0 0 1 D D Х D=1/0 D'=0/1 1 1 1 1 1 1 D D D Х 1 1 D' D' 1 1 D' Х Х Х Х Х Х 1 AND AND 0 D D' Х 1 0 0 0 0 0 0 Stuck-at 0 on A -> D 0 D' Х 1 1 Line A = D D D D 0 0 Х To propagate D (fault effect) to D' 0 D' D' 0 Х Z (check table) set B=1 Х х Х х 0 Х

Justify values on H, Y, U, W. H=0 (ok). F=0? Conflict! Select Y=0

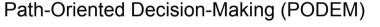

- In the D-algorithm the search space is the entire circuit. Every internal gate can be a decision point.

- However, the end result for any ATPG algorithm are always the primary inputs.

- The number of primary inputs is in general much smaller than the number of gates

- The PODEM algorithm makes decisions only at primary inputs

- D-frontier is kept but the J-frontier is not needed

NOR R

G3

NOR G

G4

AND

w U F G Н Ζ

х

1 0 D D' 0 D'

х х

х

х х х х х х х

x 1 х D х x х

x

G2

AND

Х

D

w/

Stuck-at 0

В

х х

0

0 D

G1

NOR в

Gate

G1 0

G2

G3 0 0 D х 1 0 D D' х х

G5 0 0 D

А

х

0

NOR

Q

NOR

XNOR

M

Operation

Initialization

Provoke

D-drive

D-drive

D-drive

G5

OR

х

х

х

н

Ζ

- Assign A=1. Good.

- Assign B=0. Lead to H=0. Not good.

- Assign B=1. Good

- Assign C=0.

- Assign E=0. Lead to J=0 and L=1

- As with C and E, assign F=G=0. Lead to K=0, M=1, N=0. and Q=1

- We can proagate D on P, and then D' on R

- Hence: 110000 is the test stimulus for a stuck-at 0 on line H

### D-Algorithm

D=1/0

1

2

3

4

5

6

XOR

XOR

XNOR

XNOR

G

### Fanout-oriented Test Generation (FAN)

Fujiwara H. and Shimono T., On the acceleration of test generation algorithms, IEEE Transactions on Computers, Vol. C-31, No. 6, pages 555-560,1983

Two major extensions to PODEM

- Backtracking may stop at internal lines

- Multiple backtrace-procedures attempts to simultaneously satisfy a set of objectives

Test generation time is reduced.

### **Testability Analysis**

- Objective:

- Guide test generation algorithm

- Predict hard to test areas in a circuit

- Example: Sandia Controllability/Observability Analysis Program (SCOAP)

- Controllability: Effort to control a value at a line

- CC0 combinational 0-controllability

- CC1 combinational 1-controllability

- SC0 sequential 0-controllability

- SC1 sequential 1-controllability

- Observability: Effort to observe a value

- CO observability controllability

- SO sequential observability

### Structure-oriented Cost-reducing Automatic Test Pattern Generation (SOCRATES)

- Schultz, M. H, et al. SOCRATES: a highly efficient automatic test pattern generation system, IEEE Transactions on Computer-Aided Design, Vol. 7, No. 1, pages 126-137, 1988.

- Uses several heuristics to reduce test generation time and makes use of testability analysis to guidance.

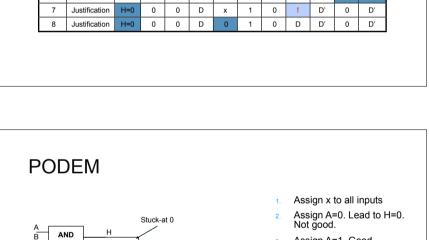

### **Fault Simulation**

Problem and Motivation

Given

- A circuit

- A sequence of test vectors

- A fault model

### Determine

- Fault coverage fraction (or percentage) of modeled faults detected by test vectors

- Set of undetected faults

### Motivation

- Determine test quality and in turn product quality

- Find undetected fault targets to improve tests

### **Fault Simulation**

- Fault simulation consists of a fault free and a faulty circuit simulation.

- First, a fault free simulation takes place to find the fault free output responses for all patterns.

- Second, a series of simulations take place where. For each fault, fault injection is performed, the circuit is modified to become faulty. Then, the faulty circuit is simulated to find the faulty responses.

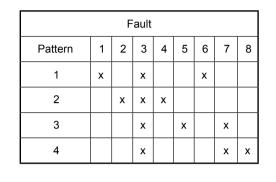

### Test Set Compaction

- ATPG generates too many vectors; faults are covered by several vectors

- Test set compaction tries to reduce number of test vectors without compromising test quality

- Static test set compaction tries to remove vectors after the use of ATPG

- Dynamic test tries to remove vectors during ATPG

| V1         X         X         X         X         X           V2         Image: Constraint of the state of th |                | f <sub>1</sub> | f <sub>2</sub> | f <sub>3</sub> | f <sub>4</sub> | $f_5$ | f <sub>6</sub> | f <sub>7</sub> |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|----------------|----------------|----------------|-------|----------------|----------------|

| V <sub>3</sub> X X X X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | V <sub>1</sub> | х              |                | х              |                | х     |                |                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | V <sub>2</sub> |                |                |                |                |       | х              | х              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | V <sub>3</sub> | х              |                |                |                | х     |                | х              |

| V <sub>4</sub> X X X X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $V_4$          |                | х              | х              | х              | х     |                |                |

### Fault Table - Analysis

Fault simulator may provide fault table (fault dictionary)

### **Commercial ATPG Tools**

- Commercial ATPG tools are often for combinational circuits

- Commercial tools usually make use of a random test generation for 60-80% of the faults (easy to detect) and deterministic test generation for the remaining part (hard to detect)

- Examples of commercial ATPG tools:

- Encounter Test Cadence

- TetraMax Synopsis

- FastScan, FlexTest Mentor Graphics

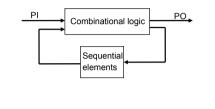

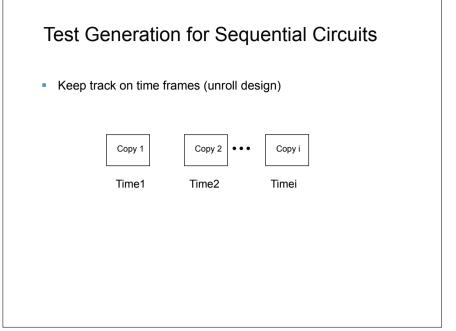

### Test Generation for Sequential Circuits

- Most real circuits are sequential

- A major problem is that the output depends not only on inputs but also on current state

### Summery

- Electronics

- Manufacturing

- Test, diagnosis, and verification

- Cost, defects, fault models, and quality of test

- Test generation Test Generation

- Exhaustive Test Generation

- Deterministic Test Generation

- Random Test Generation

- (Pseudo-random Test Generation)

- Fault Simulation and test set compaction

- On next lecture we will answer the question: How is it possible to use combinational ATPG when real circuits are sequential.

### Introduction to structured VLSI design Design for Test (DfT) - Part 1

Erik Larsson EIT, Lund University