# EITF20: Computer Architecture Part6.1.1: Course Summary

Liang Liu liang.liu@eit.lth.se

Lund University / EITF20/ Liang Liu 2015

## The art of designing computers is based on engineering principles and quantitative performance evaluation

## **Computer Architecture**

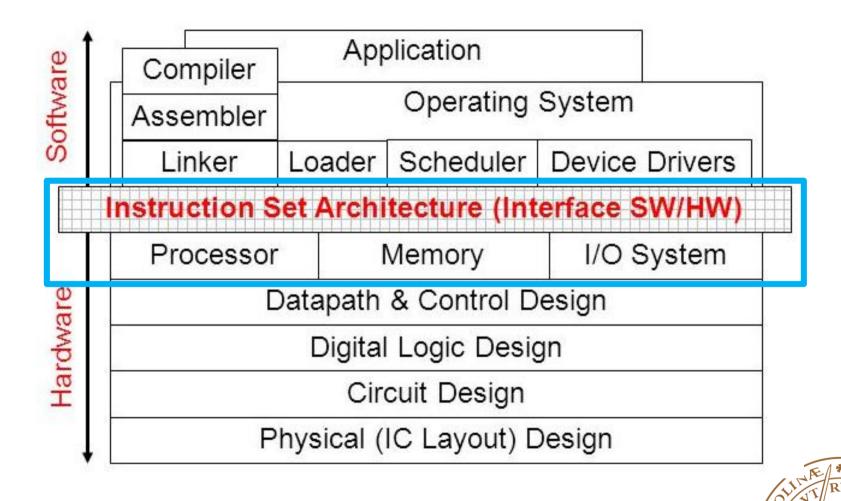

Computer architecture is a set of disciplines that describe the functionality, organization and implementation of computer systems.

ISA: Instruction-set architecture

Computer orginization: micro architecture

Specific implementation

## **Computer abstraction levels**

VM.CA

## What computer architecture?

#### Design and analysis

- ISA

- Orgnization (microarchitecture)

- Implementation

#### **D**To meet requirements of

- Functionality (application, standards...)

- Price

- Performance

- Power

- Reliability

- Dependability

- Compatability

- •

## Outline

- Performance

- Pipeline

- Memory Hierarchy

- I/O, Storage System

## What is Performance?

| Plane      | DC to Paris | Speed     |

|------------|-------------|-----------|

| Boeing 747 | 6.5 h       | 980 km/h  |

| Concorde   | 3 h         | 2160 km/h |

#### □ Time to complete a task (T<sub>exe</sub>)

• Execution time, response time, latency

#### Task per day, hour...

- Total amount of tasks for given time

- Thoughput, bandwidth

- Speed of Concorde vs Boeing 747

- Throughput of Boeing 747 vs Concorde

#### Performance

$$Performance(X) = \frac{1}{T_{exe}(X)}$$

"X is n times faster than Y" means:

$$\frac{T_{exe}(Y)}{T_{exe}(X)} = \frac{Performance(X)}{Performance(Y)} = n$$

#### Performance

Application〈Answers/monthProgramming〈Response time (seconds)language〈Operations/secondCompilerInstruction set〈Instruction set〈MIPS/MFLOPSData-path control〈Megabytes/secondFunctional unitsTransistors, wires, pins<</td>

MIPS = millions of instructions per second MFLOPS = millions of FP operations per second

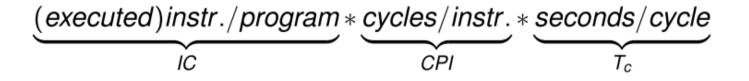

## Aspect of CPU performance

CPUtime = Execution time = seconds/program =

|              | IC | CPI | $T_c$ |

|--------------|----|-----|-------|

| Program      | Х  |     |       |

| Compiler     | Х  | (X) |       |

| Instr. Set   | Х  | Х   |       |

| Organization |    | Х   | Х     |

| Technology   |    |     | Х     |

## **Quantitative Principles**

#### This is intro to design and analysis

- Take advantage of parallelism

ILP, DLP, TLP, ...

- Principle of locality

- □ 90% of execution time in only 10% of the code

- Focus on the common case

- In makeing a design trade-off, favor the frquent case ove the infrequent case

- Amdahl's Law

- □ The performance improvement gained from uisng faster mode is limited by the fraction of the time the faster mode can be used

- The Processor Performance Equation

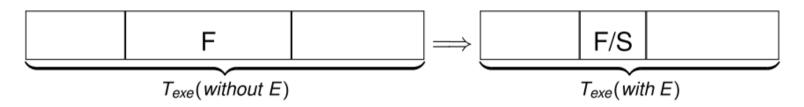

### Amdahl's Law

Enhancement E accelerates a fraction F of a program by a factor S

Speedup due to enhancement E:  $Speedup(E) = \frac{T_{exe}(without E)}{T_{exe}(with E)} = \frac{Performance(with E)}{Performance(without E)}$

$$T_{exe}(with E) = T_{exe}(without E) * [(1 - F) + F/S]$$

Speedup(E) =

$$\frac{T_{exe}(without E)}{T_{exe}(with E)} = \frac{1}{(1-F)+F/S}$$

# Outline

#### Performance

- **D** Pipeline

- Memory Hierarchy

- □ I/O, Storage System

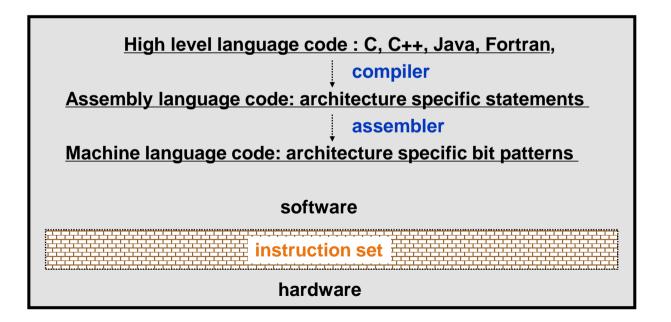

## **Interface Design**

#### A good interface

- Lasts through many implementations (portability, compatibility)

- Can be used in many different ways (generality)

- Provides sufficient functionality to higher levels

- Permits an efficient implementation at lower levels

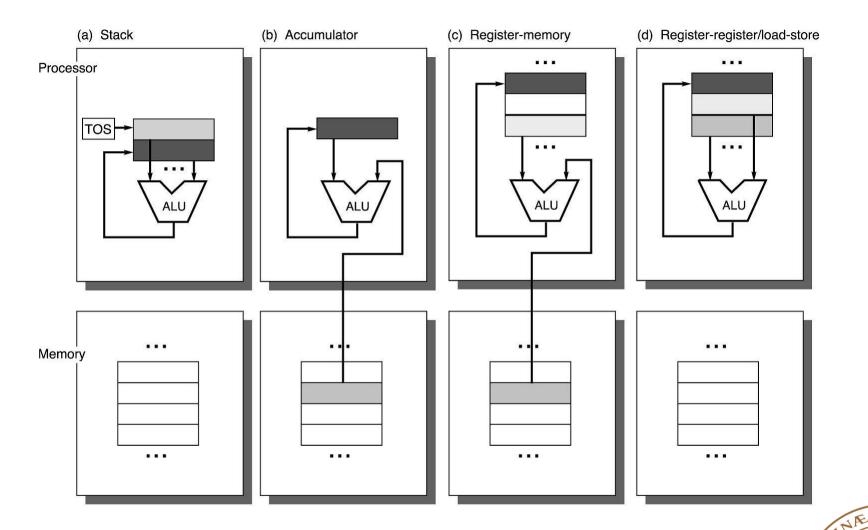

## **ISA Classification**

#### What's needed in an instruction set?

- Addressing

- Operands

- Operations

- Control Flow

#### Classification of instruction sets

- Register model

- The number of operands for instructions

- Addressing modes

- The operations provided in the instruction set

- Type and size of operands

- Control flow instructions

- Encoding

## **ISA Design Issues**

#### Where are operands stored?

registers, memory, stack, accumulator

#### How many explicit operands are there?

• 0, 1, 2, or 3

#### How is the operand location specified?

register, immediate, indirect, ...

#### What type & size of operands are supported?

byte, int, float, double, string, vector. . .

#### What operations are supported?

add, sub, mul, move, compare . . .

#### **How is the operation flow controlled?**

• branches, jumps, procedure calls . . .

#### What is the encoding format

• fixed, variable, hybrid...

## **ISA Classes: Where are operands stored**

VM·CARO,

# Memory Addressing Mode

Addressing Mode 1. Register direct 2. Immediate 3. Displacement 4. Register indirect 5. Indexed 6. Direct 7. Memory Indirect 8. Auto-increment 9. Auto-decrement 10. Scaled

Example Add R4, R3 Add R4, #3 Add R4, 100(R1) Add R4, (R1) Add R4, (R1 + R2) Add R4, (1000) Add R4, @(R3) Add R4, (R2)+

Add R4, (R2)-

Add R4, 100(R2)[R3]

Action R4 < - R4 + R3R4 < -R4 + 3R4 <- R4 + M[100 + R1] R4 <- R4 + M[R1] R4 < -R4 + M[R1 + R2]R4 <- R4 + M[1000] R4 <- R4 + M[M[R3]] R4 < -R4 + M[R2]R2 <- R2 + d R4 < -R4 + M[R2]R2 <- R2 - d R4 <- R4 + M[100 + R2 + R3\*d]

### **Instruction format**

#### Variable instruction format

- Compact code but the instruction decoding is more complex and thus slower

- Examples: VAX, Intel 80x86 (1-17 byte)

| Operation  | Address     | Address | <br>Address | Address |

|------------|-------------|---------|-------------|---------|

| # operands | specifier 1 | field 1 | specifier x | field x |

#### Fixed instruction format

- Easy and fast to decode but gives large code size

- Examples: Alpha, ARM, MIPS (4byte), PowerPC, SPARC

| Operation | Address | Address | Address |  |

|-----------|---------|---------|---------|--|

|           | field 1 | field 2 | field 3 |  |

## **Example: RISC-CICS**

#### RISC (Reduced Instruction Set Computing)

- Simple instructions

- MIPS, ARM, ...

- Easier to design, build

- Less power

- Larger code size (IC), but in total (byte)?

- Easier for compiler, but for optimization?

#### CISC (Complex Instruction Set Computing)

- Complex instructions

- VAX, Intel 80x86 (now RISC-like internally), ...

#### http://cs.stanford.edu/people/eroberts/courses/soco/proj ects/risc/risccisc/

## Outline

Performance

#### **D** Pipeline

Memory Hierarchy

□ I/O, Storage System

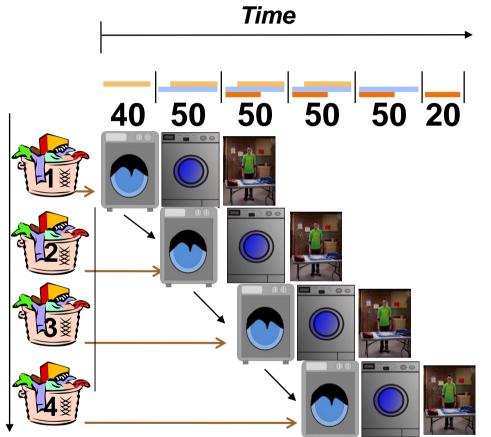

## **Pipeline Facts**

# Multiple tasks operating simultaneously

Pipelining doesn't help latency of single task, it helps throughput of entire workload

Pipeline rate limited by slowest pipeline stage

**Unbalanced** lengths of pipe stages reduces speedup

■Potential speedup ∝ Number of pipe stages

Laundries

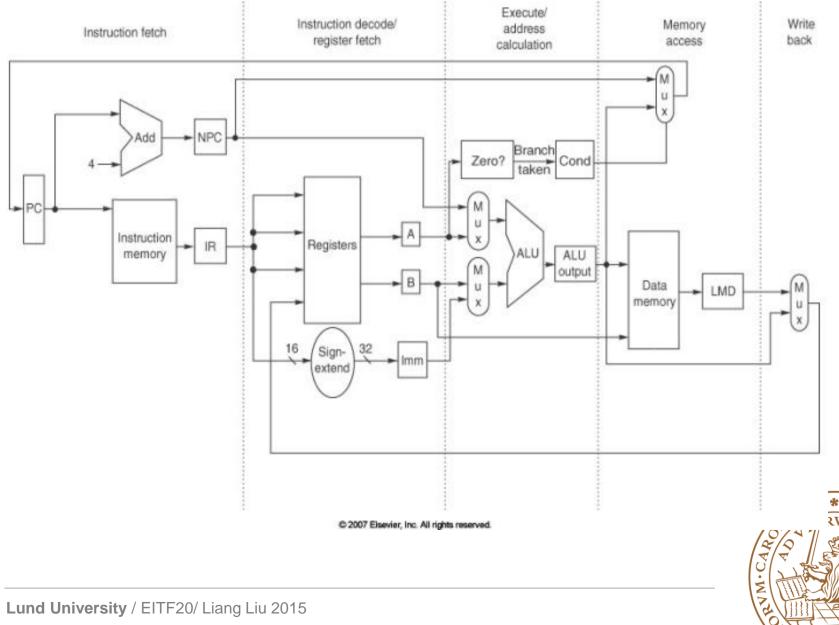

## **One core – the MIPS data-path**

SIG

## **Dependencies**

#### Data dependent: if

- Instruction *i* produces a result used by instr. *j*, or

- Instruction *j* is data dependent on instruction k and instr. k is data dependent on instr. *i*

Name dependent: two instructions use same name (register or memory address) but do not exchange data

Anti-dependence (WAR if hazard in HW)

ADDDF2,F0,F2; Must execute before LDLDF0,0(R1)

Output dependence (WAW if hazard in HW)

ADDDF0,F2,F2; Must execute before LDLDF0,0(R1)

## **Control dependencies**

# Determines order between an instruction and a branch instruction

| Example:                                                  |

|-----------------------------------------------------------|

| if Test1 then { S1 }                                      |

| if Test2 then { S2 }                                      |

| S1 is control dependent on Test1                          |

| S2 is control dependent on Test2; but <i>not</i> on Test1 |

|                                                           |

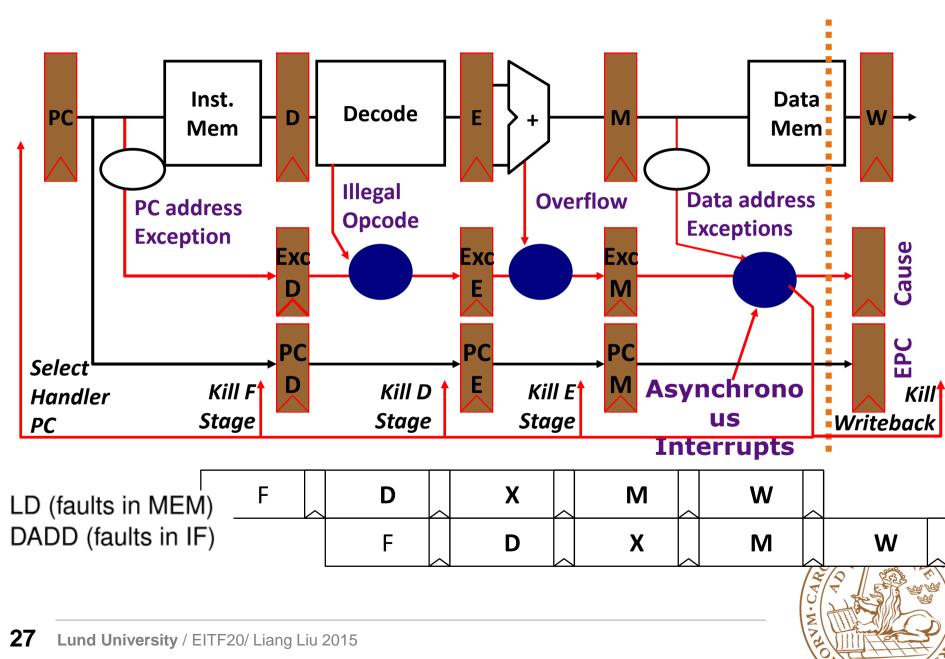

# **Summary pipeline - method**

| Dependency         | Hazard   | Method                      |

|--------------------|----------|-----------------------------|

| Data               | RAW      | Forwarding, Scheduling,     |

| Name               | WAR, WAW | Register Renaming           |

| Control            | Control  | Branch Prediction,          |

|                    |          | Speculation, Delayed branch |

| Precise exceptions |          | in-order commit             |

| ILP                |          | Scheduling,                 |

|                    |          | Loop unrolling              |

# **Solution for simple MIPS**

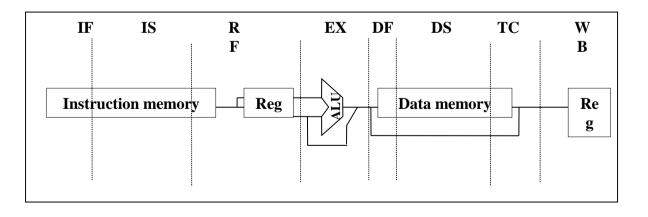

# **Deeper pipeline**

#### Implications of deeper pipeline

- load latency: 2 cycles

- branch latency: 3 cycles (incl. one delay slot) ⇒ High demands on the compiler

- Bypassing (forwarding) from more stages

- More instructions "in flight" in pipeline

- Faster clock, larger latencies, more stalls

Performance equation: CPI \* Tc must be lower for the longer pipeline to make it worthwhile

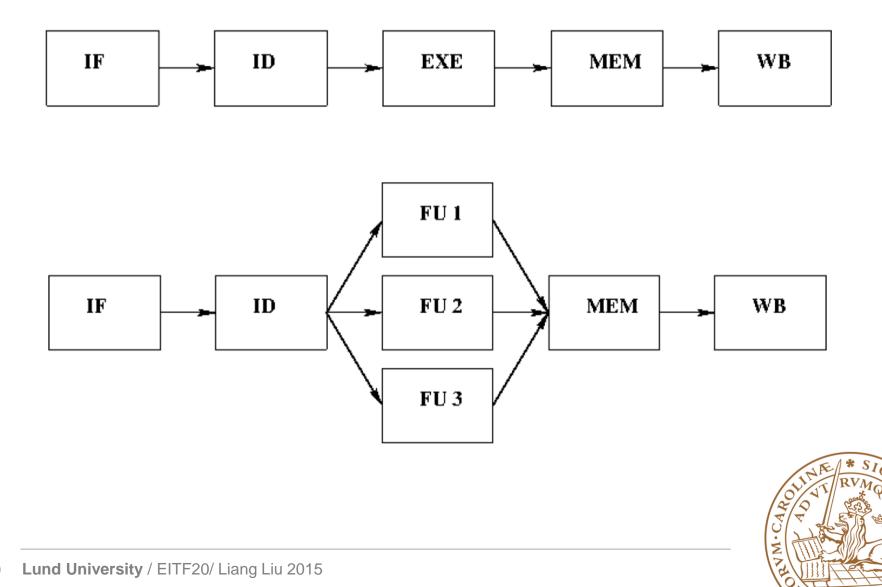

# **Pipeline**

# **Pipeline hazard**

#### RAW hazards:

- Normal bypassing from MEM and WB stages

- Stall in ID stage if any of the source operands is destination operand in any of the FP functional units

#### WAR hazards?

There are no WAR-hazards since the operands are read (in ID) before the EX-stages in the pipeline

#### WAW hazard

| DIV.D     | F0,F2,F3  | FP divide 24 cycles  |  |  |  |  |

|-----------|-----------|----------------------|--|--|--|--|

| <br>SUB D | F0 F8 F10 | FP subtract 3 cycles |  |  |  |  |

| SUB.D     | F0,F8,F10 | FP subtract 3 cyc    |  |  |  |  |

- SUB finishes before DIV which will overwrite the result from SUB!

- are eliminated by stalling SUB until DIV reaches MEM stage

- When WAW hazard is a problem?

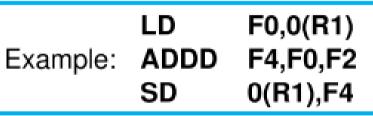

## Scheduling

| loop: | LD<br>ADDD<br>SD<br>DADDUI<br>BNE | F0, 0(R1)<br>F4, F0, F2<br>F4, 0(R1)<br>R1, R1, #-8<br>R1,R2, loop | ; F0 = array element<br>; Add scalar constant<br>; Save result<br>; decrement array ptr.<br>; reiterate if R1 != R2 |

|-------|-----------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

|       | DIVE                              | 111,112, 100p                                                      |                                                                                                                     |

#### Loop unrolling

#### Scheduling

とう

|    |       |        |                      | Loop: | L.D    | F0,0(R1)    |

|----|-------|--------|----------------------|-------|--------|-------------|

| 1  | loop: | LD     | F0, 0(R1)            | LOOP. |        |             |

| 2  |       | ADDD   | F4, F0, F2           |       | L.D    | F6,-8(R1)   |

| 3  |       | SD     | F4, 0(R1)            |       | L.D    | F10,-16(R1) |

| 4  |       | LD     | F6, <i>-8</i> (R1)   |       | L.D    | F14,-24(R1) |

| 5  |       | ADDD   | F8, F6, F2           |       | ADD.D  | F4,F0,F2    |

| 6  |       | SD     | F8, <i>-8</i> (R1)   |       | ADD.D  | F8,F6,F2    |

| 7  |       | LD     | F10, <i>-16</i> (R1) |       | ADD.D  | F12,F10,F2  |

| 8  |       | ADDD   | F12, F10, F2         |       | ADD.D  | F16,F14,F2  |

| 9  |       | SD     | F12, <i>-16</i> (R1) |       | S.D    | F4,0(R1)    |

| 10 |       | LD     | F14, <i>-24</i> (R1) |       | S.D    | F8,-8(R1)   |

| 11 |       | ADDD   | F16, F14, F2         |       | DADDUI | R1,R1,#-32  |

| 12 |       | SD     | F16, <i>-24</i> (R1) |       | S.D    | F12 16(D1)  |

| 13 |       | DADDUI | R1, R1, <b>#-32</b>  |       | S.D    | F16,8(R1)   |

| 14 |       | BNE    | R1, R2, loop         |       | BNE    | R1,R2,Loop  |

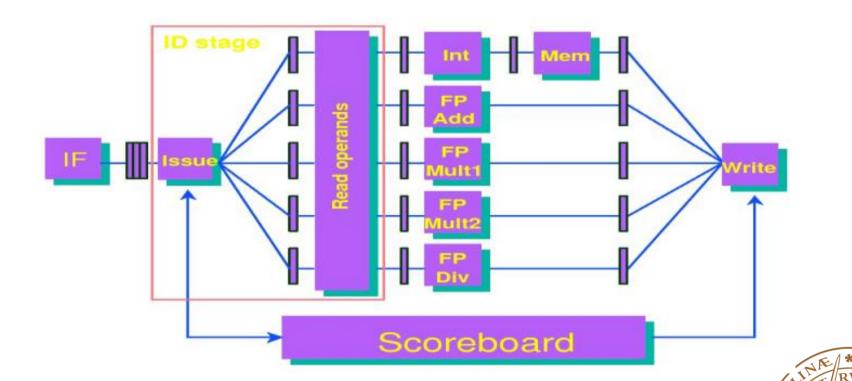

## **Scoreboard pipeline**

Issue: decode and check for structural & WAW hazards

- **Read operands:** wait until no data hazards, then read operands

- All data hazards are handled by the scoreboard

# **Scoreboard functionality**

#### **Issue:** An instruction is issued if:

- The needed functional unit is free (there is no **structural hazard**)

- No functional unit has a destination operand equal to the destination of the instruction (resolves WAW hazards)

- **Read:** Wait until no data hazards, then read operands

- Performed in parallel for all functional units

- Resolves RAW hazards dynamically

- **EX:** Normal execution

- Notify the scoreboard when ready

- **Write:** The instruction can update destination if:

- All earlier instructions have read their operands (resolves WAR hazards)

#### **Scoreboard example**

| Instruc   | tion s | <u>tatus</u> |      |       | Read | Exec.  | Write  |        |        |     |     |

|-----------|--------|--------------|------|-------|------|--------|--------|--------|--------|-----|-----|

| Instructi | on     | i            | k    | Issue | ops  | compl. | result |        |        |     |     |

| LD        | F6     | 34+          | R2   |       |      |        |        | 1      |        |     |     |

| LD        | F2     | 45+          | R3   |       |      |        |        |        |        |     |     |

| MULTD     | FO     | F2           | F4   |       |      |        |        |        |        |     |     |

| SUBD      | F8     | F6           | F2   |       |      |        |        |        |        |     |     |

| DIVD      | F10    | F0           | F6   |       |      |        |        |        |        |     |     |

| ADDD      | F6     | F8           | F2   |       |      |        |        |        |        |     |     |

|           |        |              |      |       |      |        |        | -      |        |     |     |

| Functio   | onal u | nit state    | IS   |       | dest | src 1  | src 2  | FUsrc1 | FUsrc2 | Fj? | Fk? |

|           | Time   | Name         | Busy | Ор    | Fi   | Fj     | Fk     | Qj     | Qk     | Rj  | Rk  |

|           |        | Integer      | No   |       |      |        |        |        |        |     |     |

|           |        | Mult1        | No   |       |      |        |        |        |        |     |     |

|           |        | Mult2        | No   |       |      |        |        |        |        |     |     |

|           |        | Add          | No   |       |      |        |        |        |        |     |     |

|           |        | Divide       | No   |       |      |        |        |        |        |     |     |

|           |        |              |      |       |      |        |        |        |        |     |     |

| Register  | result | status       |      |       |      |        |        |        |        |     |     |

|           |        |              | FO   | F2    | F4   | F6     | F8     | F10    |        | F30 |     |

|           |        | FU           |      |       |      |        |        |        |        |     | 1   |

| Clock:    | 0      |              | L    |       |      |        |        |        |        |     | •   |

|           |        |              |      |       |      |        |        |        |        |     |     |

|           |        |              |      |       |      |        |        |        |        |     |     |

VM·CARO

0

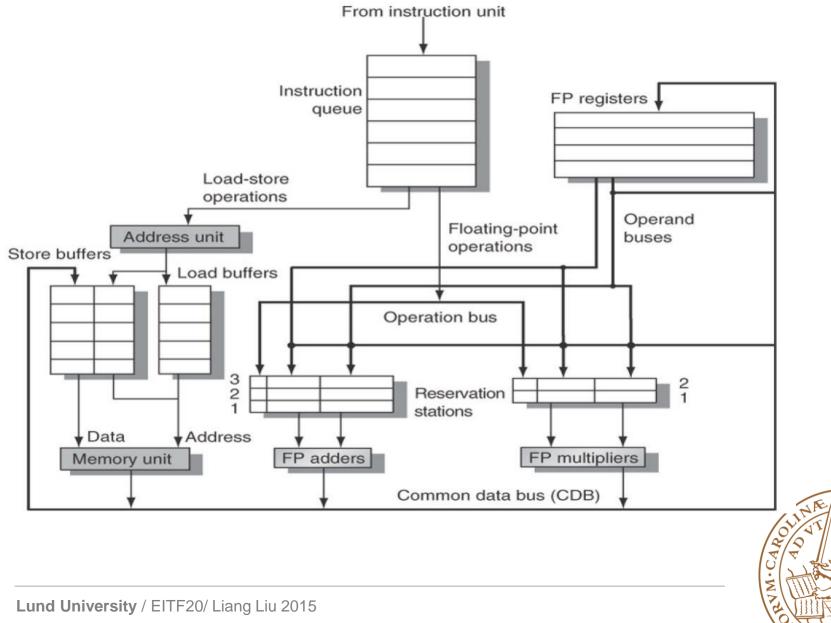

## **Tomasulo orgnizations**

SIG \*

0

#### **Reservation stations**

- Op:Operation to perform (e.g., + or –)

- □ Vj, Vk: Value (instead of reg specifier) of Source operands

- Qj, Qk: Reservation stations (instead of FU) producing source registers (value to be written)

- Note: Qj,Qk=0 => ready

- V and Q filed are mutual exclusive

- Busy: Indicates reservation station or FU is busy

- Register result status—Indicates which RS will write each register

- Blank when no pending instructions that will write that register

| Functional u | src 1 | src 2 | RS for j | RS for k |    |    |    |

|--------------|-------|-------|----------|----------|----|----|----|

| Time         | Name  | Busy  | Ор       | Vj       | Vk | Qj | Qk |

|              | Add1  | No    |          |          |    |    |    |

|              | Add2  | No    |          |          |    |    | I  |

|              | Add3  | No    |          |          |    |    |    |

|              | Mult1 | No    |          |          |    |    |    |

|              | Mult2 | No    |          |          |    |    |    |

# Three stages of Tomasulo algorithm

- Issue get instruction from instruction Queue

- If matching reservation station free (no structural hazard)

- Instruction is issued together with its operands values or RS point (register rename, handle WAR, WAW)

- **Execution** operate on operands (EX)

- When both operands are ready, then execute (handle RAW)

- If not ready, watch Common Data Bus (CDB) for operands (snooping)

- Write result finish execution (WB)

- Write on CDB to all awaiting RS, regs (forwarding)

- Mark reservation station available

- Data Bus

- Normal Bus: data + destination

- Common Data Bus: data + source (snooping)

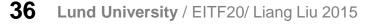

### **Tomasulo extended to support speculation**

## **Summary pipeline - implementation**

| Problem    | Simple     | Scoreboard          | Tomasulo     | Tomasulo +<br>Speculation |

|------------|------------|---------------------|--------------|---------------------------|

|            | Static Sch | Dynamic Scheduling  |              |                           |

| RAW        | forwarding | wait (Read) CDB     |              | CDB                       |

|            | stall      |                     | stall        | stall                     |

| WAR        | -          | wait (Write)        | Reg. rename  | Reg. rename               |

| WAW        | -          | wait (Issue)        | Reg. rename  | Reg. rename               |

| Exceptions | precise    | ?                   | ?            | precise, ROB              |

| Issue      | in-order   | in-order in-order   |              | in-order                  |

| Execution  | in-order   | out-of-order        | out-of-order | out-of-order              |

| Completion | in-order   | out-of-order        | out-of-order | in-order                  |

| Structural | -          | many FU many FU,    |              | many FU,                  |

| hazard     |            | stall               | CDB, stall   | CDB, stall                |

| Control    | Delayed    | Branch Branch Br. p |              | Br. pred,                 |

| hazard     | br., stall |                     |              | speculation               |

VM.C

## Outline

Performance

### Pipeline

### Memory Hierarchy

□ I/O, Storage System

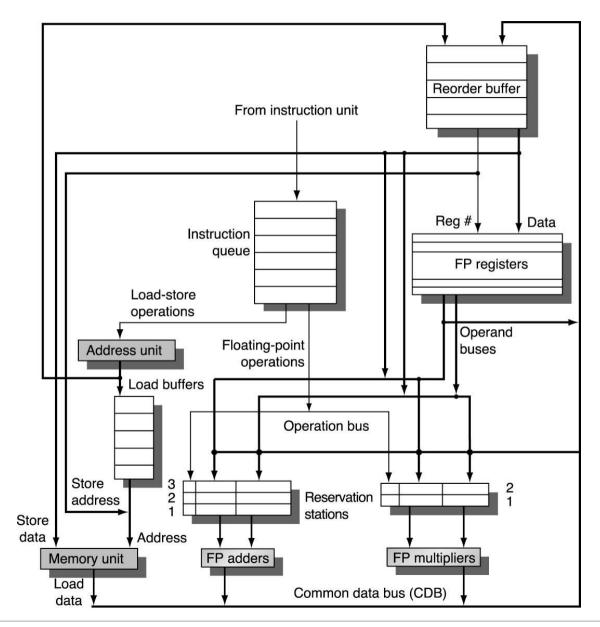

# Memory tricks (techniques)

| Use a hierarchy |           |             |                |              |  |

|-----------------|-----------|-------------|----------------|--------------|--|

| CPU             | superfast | Registers   |                | instructions |  |

|                 | FAST      | Cache       |                |              |  |

|                 |           |             | cache memory   | (HW)         |  |

| Memory          | CHEAP     | Main memory |                |              |  |

|                 |           |             | virtual memory | (SW)         |  |

|                 | BIG       | Disk        |                |              |  |

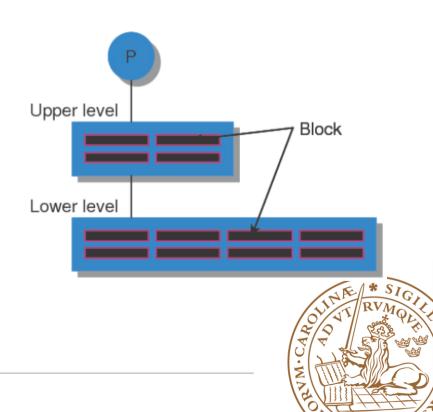

# Levels of memory hierarchy

# Four memory hierarchy questions

Q1: Where can a block be placed in the upper level? (Block placement)

- Q2: How is a block found if it is in the upper level?

- (Block identification)

- Q3: Which block should be replaced on a miss?

- (Block replacement)

- **Q4:** What happens on a write?

- (Write strategy)

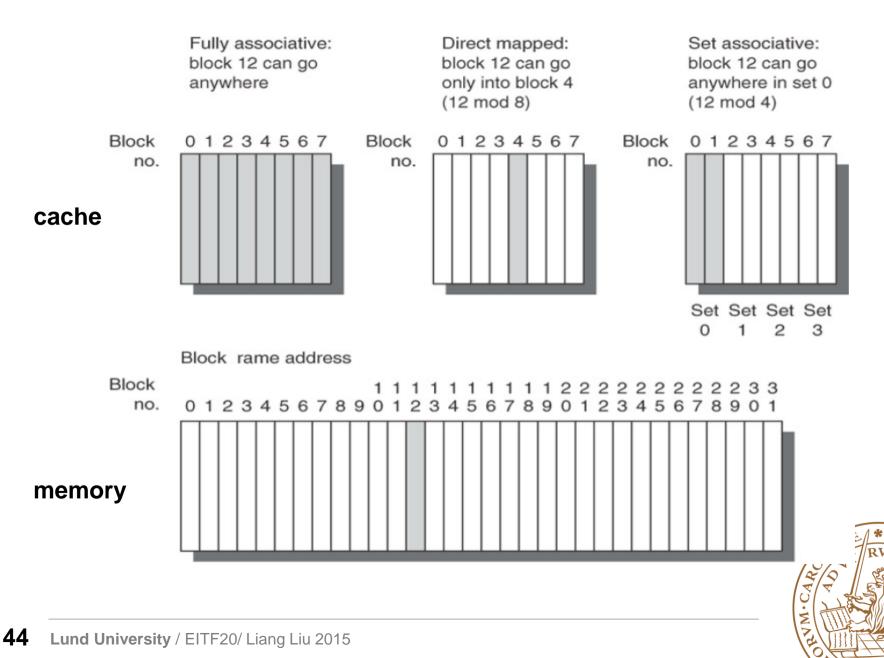

### **Block placement**

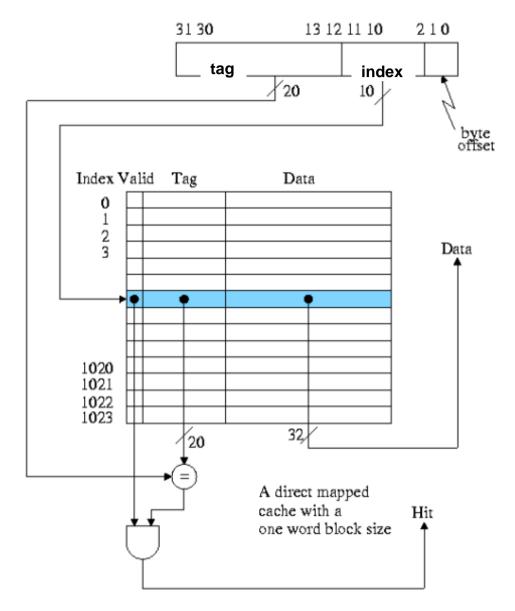

### **Block identification**

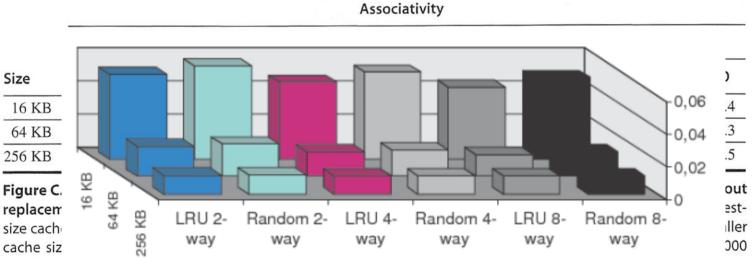

### Which block should be replaced on a Cache miss?

Direct mapped caches don't need a block replacement policy

#### Primary strategies:

- Random (easiest to implement)

- LRU Least Recently Used (best, hard to implement)

- FIFO Oldest (used to approximate LRU)

benchmarks. Five are from SPECInt2000 (gap, gcc, gzip, mct, and peri) and five are from SPECIp2000 (applu, art, equake, lucas, and swim). We will use this computer and these benchmarks in most figures in this appendix.

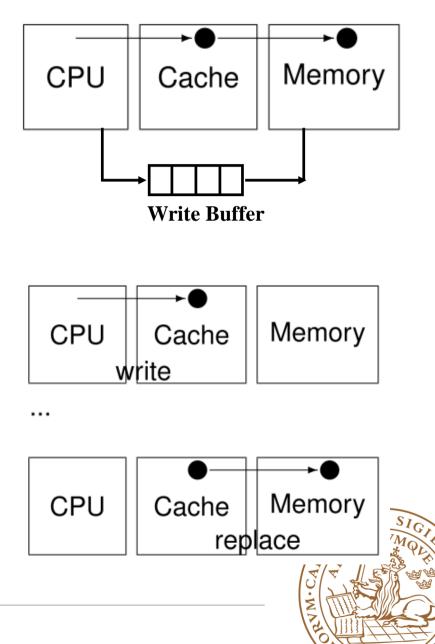

# **Cache write (hit)**

### Write through:

- The information is written to both the block in the cache and to the block in the lower-level memory

- Is always combined with write buffers so that the CPU doesn't have to wait for the lower level memory

#### Write back:

- The information is written only to the block in the cache

- Copy a modified cache block to main memory only when replaced

- Is the block clean or modified? (dirty bit, several write to the same block)

### **Cache performance**

$CPU \text{ execution Time} = \\ IC * (CPI_{execution} + \frac{mem \ accesses}{instruction} * miss \ rate * miss \ penalty) * T_C$

#### Three ways to increase performance:

- Reduce miss rate

- Reduce miss penalty

- Reduce hit time (improves T<sub>c</sub>)

Average memory access time = *hit time* + *miss rate* \* *miss penalty*

### **Cache optimizations**

|               | Hit<br>time | Band-<br>width | Miss<br>penalty | Miss<br>rate | HW<br>complexity        |

|---------------|-------------|----------------|-----------------|--------------|-------------------------|

| Simple        | +           |                |                 | -            | 0                       |

| Addr. transl. | +           |                |                 |              | 1                       |

| Way-predict   | +           |                |                 |              | 1                       |

| Trace         | +           |                |                 |              | 3                       |

| Pipelined     | -           | +              |                 |              | 1                       |

| Banked        |             | +              |                 |              | 1                       |

| Nonblocking   |             | +              | +               |              | 3                       |

| Early start   |             |                | +               |              | 2                       |

| Merging write |             |                | +               |              | 1                       |

| Multilevel    |             |                | +               |              | 2                       |

| Read priority |             |                | +               |              | 1                       |

| Prefetch      |             |                | +               | +            | 2-3                     |

| Victim        |             |                | +               | +            | 2                       |

| Compiler      |             |                |                 | +            | 0                       |

| Larger block  |             |                | -               | +            | 0                       |

| Larger cache  | -           |                |                 | +            | 1                       |

| Associativity | -           |                |                 | +            | · □ > · 4 酉 > · 4 回 > · |

NAL WALK

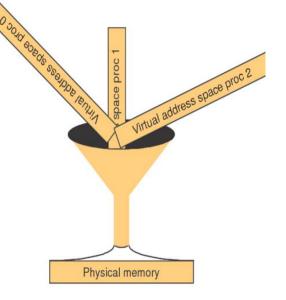

# **Virtual memory benifits**

#### Using physical memory efficiently

- Allowing more than physical memory addressing

- Enables programs to begin before loading fully

- Programmers used to use overlays and manually control loading/unloading

### Using physical memory simply

- Virtual memory simplifies memory management

- Programmer can think in terms of a large, linear address space

### Using physical memory safely

- Virtual memory protests process' address spaces

- Processes cannot interfere with each other, because they operate in different address space

- User processes cannot access priviledged information

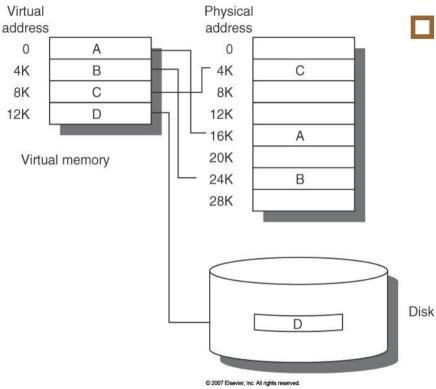

# Virtual memory concept

### Is part of memory hierarchy

- The virtual address space is divided into **pages** (blocks in Cache)

- The physical address space is divided into page frames

- A miss is called a page fault

- Pages not in main memory are stored on disk

### The CPU uses virtual addresses

We need an address translation (memory mapping) mechanism

### Page placement

#### Where can a page be placed in main memory?

- Cache access: ~ ns

- Memory access: ~ 100 ns

- Disk access: ~ 10, 000, 000 ns

### $\implies$ HIGH miss penalty

#### The high miss penalty makes it

- Necessary to minimize miss rate

- Possible to use software solutions to implement a fully associative address mapping

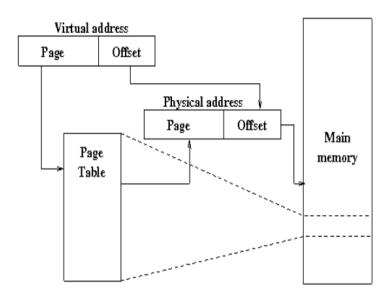

# Page identification: address mapping

Contains Real Page Number

Miscellaneous control information

- valid bit,

- dirty bit,

- replacement information,

- access control

### **4Byte per page table entry**

Page table will have

2<sup>20\*</sup>4=2<sup>22</sup>=4MByte

- Generally stored in the main memory

- 64 bit virtual address,16 KB pages:

2<sup>64</sup>/2<sup>14</sup>\*4=2<sup>52</sup>=2<sup>12</sup>TByte

- One page table per program (100 program?)

- Solutions

- Multi-level page table

- Inverted page table

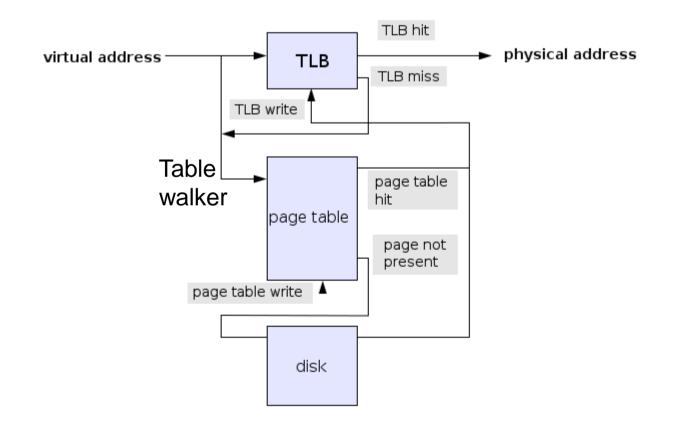

# Page identification (TLB)

- How do we avoid two (or more) memory references for each original memory reference?

- Cache address translations Translation Look-aside Buffer (TLB)

54

## **Summary memory hierarchy**

| Hide CPU - memory performance gap<br>Memory hierarchy with several levels<br>Principle of locality |                                                                                                   |  |  |  |

|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--|--|--|

| Cache memories:                                                                                    | Virtual memory:                                                                                   |  |  |  |

| Fast, small - Close to CPU                                                                         | Slow, big - Close to disk                                                                         |  |  |  |

| Hardware                                                                                           | <ul> <li>Software</li> </ul>                                                                      |  |  |  |

| TLB                                                                                                | • TLB                                                                                             |  |  |  |

| CPU performance equation                                                                           | Page-table                                                                                        |  |  |  |

| <ul> <li>Average memory access<br/>time</li> </ul>                                                 | <ul> <li>Very high miss penalty<br/>miss rate must be low</li> </ul>                              |  |  |  |

| <ul> <li>Optimizations</li> </ul>                                                                  | <ul> <li>Also facilitates: relocation;<br/>memory protection; and<br/>multiprogramming</li> </ul> |  |  |  |

| Same 4 design questions - Different answers                                                        |                                                                                                   |  |  |  |

## Outline

- Performance

- **D** Pipeline

- Memory Hierarchy

- I/O, Storage System

### I/O technologies

# The techniques for I/O have evolved (and sometimes unevolved):

- <u>Direct control</u>: CPU controls device by reading/writing data lines directly

- <u>Polled I/O</u>: CPU communicates with hardware via built-in controller; busy-waits (sampling) for completion of commands

- <u>Driven I/O</u>: CPU issues command to device, gets interrupt on completion

- <u>Direct memory access</u>: CPU commands device, which transfers data directly to/from main memory (DMA controller may be separate module, or on device).

- <u>I/O channels</u>: device has specialized processor, interpreting main CPU only when it is truly necessary. CPU asks device to execute entire I/O program

### HDD vs. SSD

# **Reliability / Availability – Dependability**

#### Definitions:

- Reliability Is anything broken?

- Availability Is the system available for the user?

- Dependability Is the system doing what it is supposed to do?

#### Why is this an issue?

- Small disks and large disks cost the same / byte

- An array of N small disks can achieve higher bandwidth than one large disk

- However, the reliability is 1/N of the reliability of a single disk

# Redundant Array of Inexpensive (Independent) Disks

|    | RAID level                  | Failures<br>tolerated | Overhead 8<br>data disks | comment             |

|----|-----------------------------|-----------------------|--------------------------|---------------------|

| 0  | striped                     | 0                     | 0                        | JBOD, common        |

| 1  | mirrored                    | 1-8                   | 8                        | high overhead       |

| 2  | ECC                         | 1                     | 4                        | not used            |

| 3  | bit parity                  | 1                     | 1                        | synchronized drives |

| 4  | block parity                | 1                     | 1                        |                     |

| 5  | block parity<br>distributed | 1                     | 1                        | common              |

| 6  | row-diagonal<br>dual parity | 2                     | 2                        | high availability   |

| 01 | mirrored stripes            | 1-8                   | 8                        |                     |

| 10 | striped mirrors             | 1-8                   | 8                        |                     |

N7

# **Thanks and Good Luck!**